сл

о

00

о

QD 41

Изобретение относится к измерительной технике и может быть использовано для измерения погрешности хода часов.

Целью изобретения является расширение функциональных возможностей устройства за счет измерений погреш- ;ности хода часов с любым стандартным |периодом колебаний баланса.

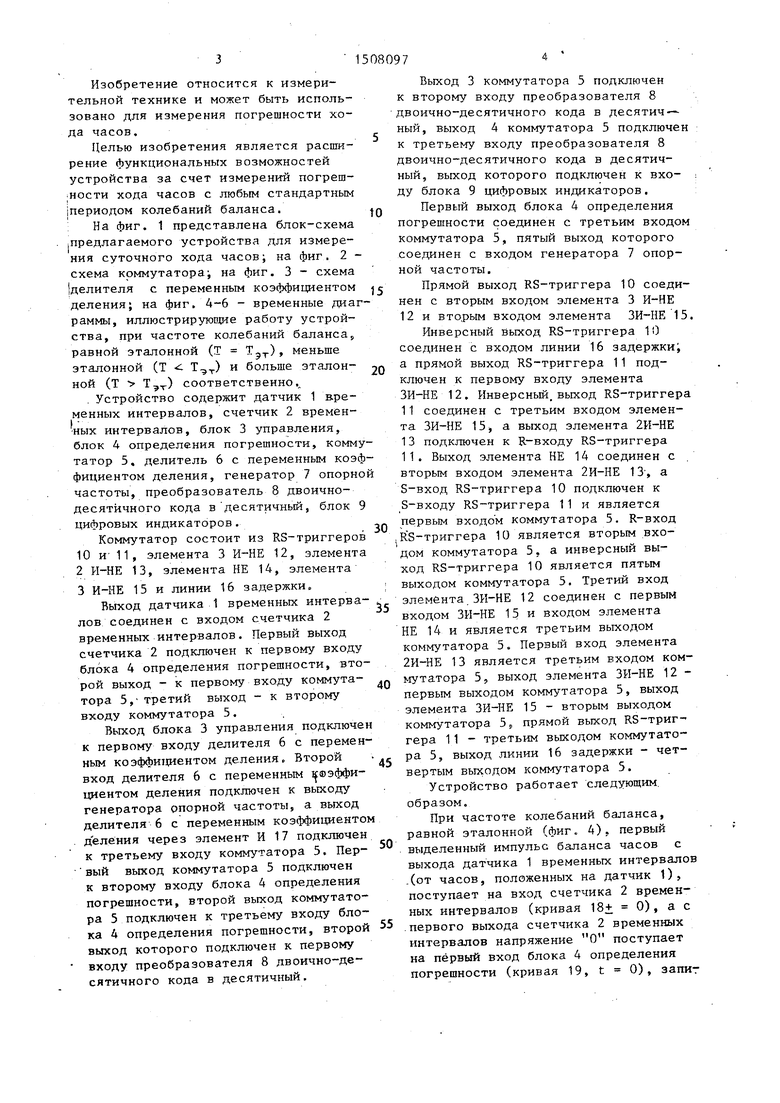

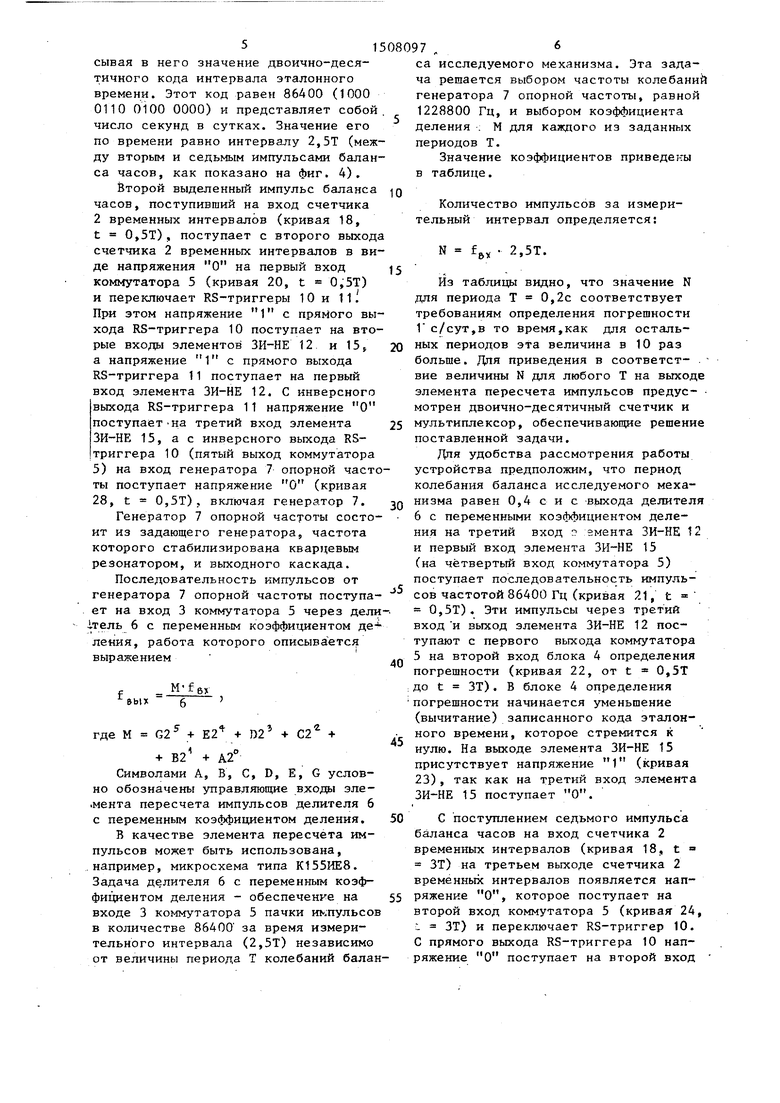

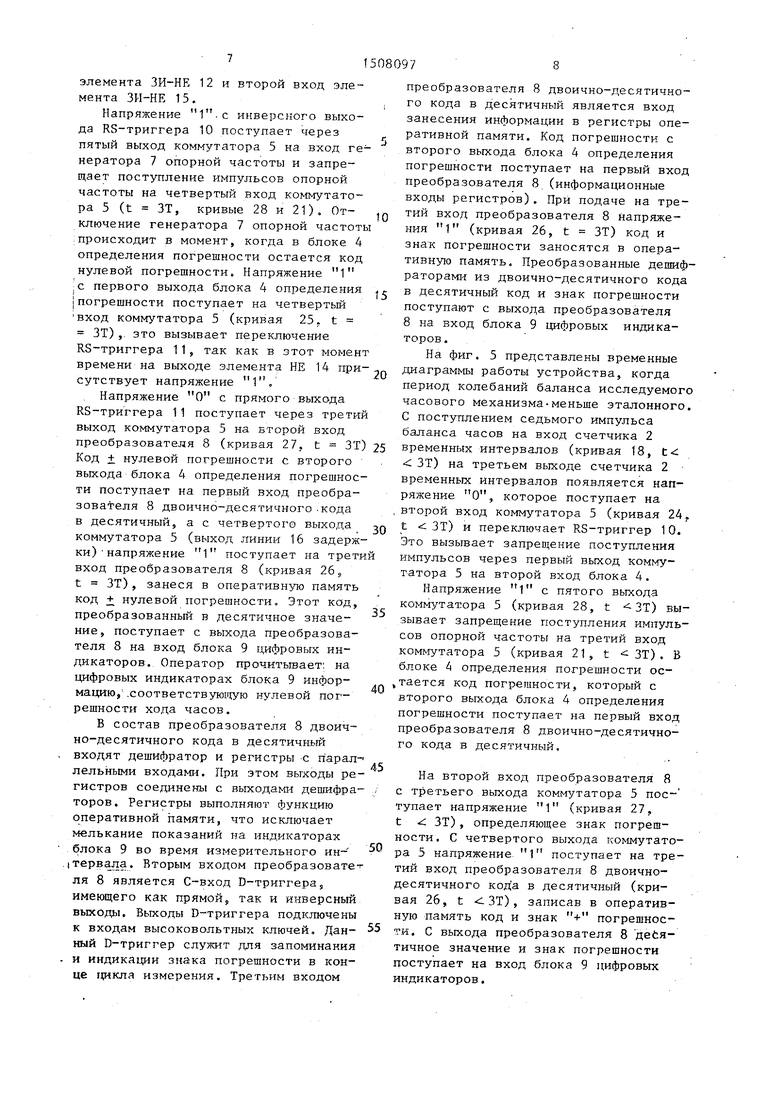

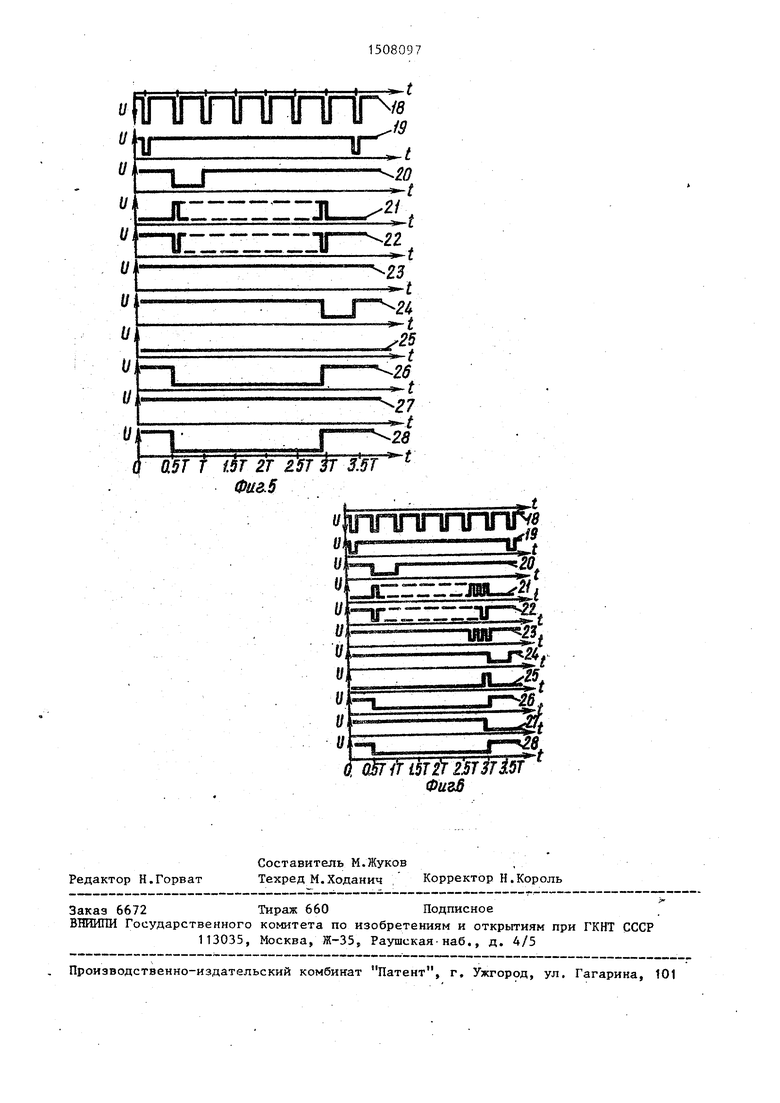

: На фиг. 1 представлена блок-схема Предлагаемого устройства для измерения суточного хода часов; на фиг. 2 - схема коммутатораi на фиг. 3 - схема {делителя с переменным коэффициентом деления; на фиг. 4-6 - временные диаграммы, иллюстрирующие работу устройства, при частоте колебаний баланса., равной эталонной (Т ), меньше эталонной (Т .) и больше эталонной (Т Т,) соответственно.

. Устройство содержит датчик 1 временных интервалов, счетчик 2 времен- ных интервалов, блок 3 управления, блок 4 определения погрешности, коммутатор 5, делитель 6 с переменным коэффициентом деления, генератор 7 опорно частоты, преобразователь 8 двоично- десятичного кода в десятичный, блок 9 цифровых индикаторов.

Коммутатор состоит из RS-триггеров 10 и- 11, элемента 3 И-НЕ 12, элемента

2И-НЕ 13, элемента НЕ 14, элемента

3И-НЕ 15 и линии 16 задержки.

Вьпсод датчика 1 временных интерна- лов соединен с входом счетчика 2 временных интервалов. Первый выход счетчика 2 подключен к первому входу блсэка 4 определения погрешности, второй выход - к первому входу коммута- тора 5, третий выход - к второму входу коммутатора 5.

Выход блока 3 управления подключен к первому входу делителя 6 с переменным коэффитщентом деления. Второй вход делителя 6 с переменным Фэффи- циентом деления подключен к выходу генератора опорной частоты, а выход делителя 6 с переменным коэффициентом . деления через элемент И 17 подключен к третьему входу коммутатора 5. Пер вый выход коммутатора 5 подключен к второму входу блока 4 определения погрешности, второй выход коммутатора 5 подключен к третьему входу блока 4 определения погрешности, второй выход которого подключен к первому входу преобразователя 8 двоично-десятичного кода в десятичный.

.

.

20

IQ

с й

;

д, 55

30

50

Выход 3 коммутатора 5 подключен к второму входу преобразователя 8 двоично-десятичного кода в десятич- ный, выход 4 коммутатора 5 подключен к третьему входу преобразователя 8 двоично-десятичного кода в десятичный, выход которого подключен к входу блока 9 цифровых индикаторов.

Первый выход блока 4 определения погрешности соединен с третьим входом коммутатора 5, пятый выход которого соединен с входом генератора 7 опорной частоты.

Прямой выход RS-триггера 10 соединен с вторым входом элемента 3 И-НЕ

12и вторым входом элемента ЗИ-НЕ 15. Инверсный выход RS-триггера 10

соединен с входом линии 16 задержки; а прямой выход RS-триггера 11 подключен к первому входу элемента ЗИ-НЕ 12. Инверсный, выход RS-триггера 11 соединен с третьим входом элемента ЗИ-НЕ 15, а выход элемента 2И-НЕ

13подключен к R-входу RS-триггера 11. Выход элемента НЕ 14 соединен с вторьм входом элемента 2И-НЕ 13, а S-вход RS-триггера 10 подключен к S-входу RS-триггера 11 и является первым входом коммутатора 5. R-вход

iR S-триггера 10 является вторым вхо- дом коммутатора 5. а инверсный выход RS-триггера 10 является пятым выходом коммутатора 5. Третий вход элемента ЗИ-НЕ 12 соединен с первым входом ЗИ-НЕ 15 и входом элемента НЕ 14 и является третьим выходом коммутатора 5. Первый вход элемента 2И-НЕ 13 является третьим входом коммутатора 5, выход элемента ЗИ-НЕ 12 - первым выходом коммутатора 5, выход элемента ЗИ-НЕ 15 - вторым выходом коммутатора 5 прямой выход RS-триггера 11 - третьим выходом коммутатора 5, выход линии 16 задержки - четвертым выходом коммутатора 5.

Устройство работает следуюшим. образом.

При частоте колебаний баланса, равной эталонной (фиг 4). первый выделенный импульс, баланса часов с выхода датчика 1 временных интервалов ,(от часов, положенных на датчик 1), поступает на вход счетчика 2 временных интервалов (кривая 18+ 0), ас .первого выхода счетчика 2 временных интервалов напряжение О поступает на первый вход блока 4 определения погрешности (кривая 19, t 0), запит

сывая в него значение двоично-десятичного кода интервала эталонного времени. Этот код равен 86ДОО (1000 0110 0100 0000) и представляет собой число секунд в сутках. Значение его по времени равно интервалу 2,5Т (между вторым и седьмым импульсами баланса часов, как показано на фиг. 4).

Второй выделенный импульс баланса часов, поступивший на вход счетчика 2 временных интервалов (кривая 18, t 0,5Т), поступает с второго выхода счетчика 2 временных интервалов в виде напряжения О на первый вход коммутатора 5 (кривая 20, t 0,5Т) и переключает RS-триггеры 10 и 11. При этом напряжение 1 с прямого выхода RS-триггера 10 поступает на вторые входы элементов ЗИ-НЕ 12 и 15, а напряжение 1 с прямого выхода RS-триггера 11 поступает на первый вход элемента ЗИ-НЕ 12. С инверсного выхода RS-триггера 11 напряжение О поступает на третий вход элемента ЗИ-НЕ 15, ас инверсного выхода RS- триггера 10 (пятый выход коммутатора 5) на вход генератора 7 опорной частоты поступает напряжение О (кривая 28, t 0,5Т), включая генератор 7.

Генератор 7 опорной частоты состоит из задающего генератора, частота которого стабилизирована кварцевым резонатором, и выходного каскада.

Последовательность импульсов от генератора 7 опорной частоты поступает на вход 3 коммутатора 5 через дели 1тель 6 с переменным коэффициентом деления, работа которого описывается выражением

BblV

где М G2Е2

П2

С2 -ь

+ В2 + А2

Символами А, В, С, D, Е, G условно обозначены управляющие входы эле- мента пересчета импульсов делителя 6 с переменным коэффициентом деления,

В качестве элемента пересчета импульсов может быть использована, .например, микросхема типа К155ИЕ8. Задача делителя 6 с переменным коэффициентом деления - обеспечение на входе 3 коммутатора 5 пачки и пyльcoв в количестве 86400 за время измерительного интервала (2,5Т) независимо от величины периода Т колебаний балан

са исследуемого механизма. Эта задача решается выбором частоты колебаний генератора 7 опорной частоты, равной 1228800 Гц, и выбором коэффициента деления ; М для каждого из заданнь х периодов Т.

Значение коэффициентов приведены в таблице.

Количество импульсов за измерительный интервал определяется:

N

-6Х

2,5Т.

5

0

5

0

5

0

5

0

5

Иэ таблицы видно, что значение N для периода Т 0,2с соответствует требованиям определения погрешности Г с/сут,в то время,как для остальных периодов эта величина в 10 раз больше. Для приведения в соответст- . - вие величины N для любого Т на выходе элемента пересчета импульсов предусмотрен двоично-десятичный счетчик и мультиплексор, обеспечивающие решение поставленной задачи.

Для удобства рассмотрения работы устройства предположим, что период колебания баланса исследуемого механизма равен 0,4 си с вьпсода делителя 6 с переменными коэффициентом деления на третий вход гмента ЗИ-НЕ 12 и первый вход элемента ЗИ-НЕ 15 (на четвертый вход коммутатора 5) поступает последовательность импульсов частотой 86400 Гц (кривая 21, t 0,5Т). Эти импульсы через третий вход и выход элемента ЗИ-НЕ 12 поступают с первого выхода коммутатора 5 на второй вход блока 4 определения погрешности (кривая 22, от t 0,5Т ;до t ЗТ). В блоке 4 определения погрешности начинается уменьшение (вычитание) записанного кода эталонного времени, которое стремится к нулю. На выходе элемента ЗИ-НЕ 15 присутствует напряжение 1 (кривая 23), так как на третий вход элемента ЗИ-НЕ 15 поступает О.

С поступлением седьмого импульса баланса часов на вход счетчика 2 временных интервалов (кривая 18, t ЗТ) на третьем вьгходе счетчика 2 временных интервалов появляется напряжение О, которое поступает на второй вход коммутатора 5 (кривая 24, - ЗТ) и переключает RS-триггер 10. С прямого выхода RS-триггера 10 напряжение О поступает на второй вход

элемента ЗИ-НЕ 12 мента ЗИ-НЕ 15.

Напряжение 1. да RS-триггера 10

и второй вход эле15

20

с инверсного выхо- поступает через пятый выход коммутатора 5 на вход генератора 7 опорной частоты и запрещает поступление импульсов опорной частоты на четвертый вход коммутатора 5 (t ЗТ, кривые 28 и 21), От- д ключение генератора 7 опорной частоты происходит в момент, когда в блоке 4 определения погрешности остается код нулевой погрешности. Напряжение 1 :С первого выхода блока 4 определения j погрешности поступает на четвертый ВХОД коммутатора 5 (кривая 25. t ЗТ) ,. это вызывает переключение RS-триггера 11, так как в этот момент времени на выходе элемента НЕ 14 присутствует напряжение 1,

Напряжение О с прямого выхода RS-триггера 11 поступает через третий выход коммутатора 5 на второй вход преобразователя 8 (кривая 27. t ЗТ) 25 Код + нулевой погрешности с второго выхода блока 4 определения погрешности поступает на первый вход преобразователя 8 двоично-десятичного.кода в десятичный, а с четвертого выхода п коммутатора 5 (выход линии 16 задержки) напряжение 1 поступает на третий вход преобразователя 8 (кривая 26, t ЗТ), занеся в оперативную память код + нулевой погрешности. Этот код, преобразованный в десятичное значение, поступает с выхода преобразователя 8 на вход блока 9 цифровых индикаторов.. Оператор прочитьгоает; на цифровых индикаторах блока 9 информацию, .соответствуки ю нулевой погрешности хода часов,

В состав преобразователя 8 двоично-десятичного кода в десятичный входят дешифратор и регистры -с п арал-- лельными входами. При этом выходы регистров соединены с выходами дешифраторов. Регистры выполняют функцию оперативной памяти, что исключает мелькание показаний на индикаторах ,блока 9 во время измерительного ин (Тервала. Вторым входом преобразовате-г

ля 8 является С-вход В-триггерЗя имеющего как прямой, так и инверсный выходы. Выходы D-триггера подключены к входам высоковольтных ключей. Данный D-триггер служит для запоминания и индикации знака погрешности в конце гщкла измерения. Третьим входом

35

40

45

./ 50

55

15

20

д25 п й

35

40

45

50

55

преобразователя 8 двоично-десятичного кода в десятичный является вход занесения информации в регистры оперативной памяти. Код погрешности с второго выхода блока 4 определения погрешности поступает на первый вход преобразователя 8 (информационные входы регистров). При подаче на третий вход преобразователя 8 напряжения 1 (кривая 26, t ЗТ) код и знак погрешности заносятся в оперативную память. Преобразованные дешифраторами из двоично-десятичного кода в десятичный код и знак погрешности поступают с выхода преобразователя 8 на вход блока 9 цифровых индикаторов.

На фиг. 5 представлены временные диаграммы работы устройства, когда период колебаний баланса исследуемого часового механизма-меньше эталонного. С поступлением седьмого импульса баланса часов на вход счетчика 2 временных интервалов (кривая 18, t ЗТ) на третьем выходе счетчика 2 временных интервалов появляется напряжение О, которое поступает на второй вход коммутатора 5 (кривая 24. t ЗТ) и переключает RS-триггер 10. Это вызывает запрещение поступления импульсов через первый выход коммутатора 5 на второй вход блока 4.

Напряжение 1 с пятого выхода коммутатора 5 (кривая 28, t - ЗТ) вызывает запрещение поступления импульсов опорной частоты на третий вход коммутатора 5 (кривая 21, t ЗТ). В блоке 4 определения погрешности ос- ,тается код погрешности, который с второго выхода блока 4 определения погрешности поступает на первый вход преобразователя 8 двоично-десятичного кода в десятичный.

На второй вход преобразователя 8 с третьего выхода коммутатора 5 пос- тупает напряжение 1 (кривая 27, t «г: ЗТ) , определяющее знак погрешности, С четвертого выхода коммутатора 5 напряжение 1 поступает на третий вход преобразователя 8 двоично- десятичного код а в десятичный (кривая 26, t iЗТ) , записав в оперативную память код и знак + погрешности. С вькода преобразователя 8 дейя- тичное значение и знак погрешности поступает на вход блока 9 цифровых индикаторов.

Оператор прочитывает на цифровых индикаторах блока 9 числовое значение погрешности хода часов со знаком +V

На фиг. 6 приведены временные диаг раммы работы устройства, когда период колебания баланса исследуемого часового механизма больше эталонного. В этом случае нулевой код в блоке А опр гделения погрешности появляется раньше поступления седьмого импульса баланса часов. В момент появления нулевого кода в блоке 4 определения погрешности на первом выходе блока 4 определения погрешности появляется напряжение 1 (кривая 25, t ЗТ) , которое поступает чере вход коммутатора 5 на первый вход элемента 2 И- НЕ 13. Импульс опорной частоты своим отрицательным перепадом (кривая 21, t ЗТ) переводит элемент НЕ 14 в состояние 1.

На выходе элемента 2И-НЕ 13 появляется напряжение О, которое переключает R S-триггер 11 . Напряжение О на прямом выходе RS-триггера 11 запрещает прохождение импульсов опорной частоты через элемент ЗИ-НЕ 12, На первом выходе коммутатора 5 присутствует напряжение 1 (кривая 22, t ЗТ). Напряжение 1 на инверсном выходе RS-триггера 11 разрешает про - хождение импульсов опорной частоты через логический элемент ЗИ-НЕ 15. Эти импульсы опорной частоты с второго выхода коммутатора 3 (кривая 23, t ЗТ) поступают на третий вход блока 4 определения погрешности, записывая код погрешности. С поступлением седьмого импульса баланса часов на входе счетчика 2 временных интервалов (кривая 18, t ЗТ) на третьем выходе счетчика 2 временных интервалов появляется напряжение О, которое поступает на второй вход коммутатора 5 (кривая 24, t ЗТ) и переключает RS-триггер 10. Напряжение О с прямого выхода RS-триггера 10 поступает на вторые входы элементов 3PI-HE 12 и 15. Это вызывает прекращение импульсов опорной частоты с второго выхода коммутатора 5 на третий вход блока 4 (кривая 23, t ЗТ). С инверсного выхода RS-триггера 10 напряжение 1 поступает через пятый

коммутатора 5 на вход генерато ра 7 опорной частоты (кривая 26, t j ЗТ). Это вызывает прекращение пос- . тупления импульсов опорной частоты

0

5

0

5

0

5

на четвертый вход KOhtM raropa 5 (крн-- вая 21, t ЗТ).

Записанный в блоке 4 определения погрешности код погрешности поступает с второго выхода блока 4 определения погрешности на первый вход преобразователя 8 двоично-десятичного кода в десятичный. На второй вход преобразователя 8 с третьего выхода - тора 5 поступает напряжение О (кривая 27, t ЗТ). С четвертого выхода когймутатора 5 напряжение 1 поступз- ет на третий вход преобразователя 8 двоично-десятичного кода в десятичный (кривая 26, t ЗТ), записывая в one- ративнуто память код и знак - погрешности. Десятичное значение кода н знак погрешности с выхода преобразователя 8 поступают на вход блока 9 цифровых индикаторов.

Оператор прочитывает на цифровых индикаторах блока 9 числовое значение погрешности хода часов со знаком -.

Восьмой импульс баланса часов соответствует первому .импульсу нового цикла работы устройства.

Таким образом, введение де.т5ителя 6 с переменным козфф1гцпентом Ae;j:e- ния и блока 3 },шравл ния и дополдчк-- тельных связей позволяет расширить область применения устройства дл:я измерения суточного хода часов на часовые механизмы с любьм стандартным периодом колебаний баланса о

Формула и 3 о б р е т

к к я

40

45

50

55

Устройство для измерения суточного хода часов, содержащее датчик временньгх интервалов,счетчик временных интервалов, коммутатор, блок определения погрешности, генератор опорной частоты, преобразователь двоично-десятичного кода в десятичный и блок )диф- ровых индикаторов, причем выход датчика временных интервалов соединен с входом счетчика BpeMeKHbD--: иктервалов,, перВБШ выход которого подключен к первом входу блока огфеделения погрешности, а второй и третий выходы подсоединены с первому и втором}; входам коммутатора, соответственно,, первый и второй выходы коммутатора сое дннены соответственно со вторьгм - и третьим входами блока определения погрешности, первый выход которого подключен к тpeтьe fy входу

тора, а второй - к первому входу преобразователя двоично-десятичного кода в десятичный, второй и третий входы которого соединены соответственно с третьим и четвертым выходами коммутатора, выход подключен к входу блока цифровых индикаторов., а вход генератора опорной частоты соединен с пятым выходом коммутатора, о т ли - чающееся тем, что, с целью расширения функциональных возможнос

тей за счет измерения погрешности хода часов с лю бым стандартньгм периодом колебаний баланса, в него введены делитель с переменным коэффидаентом деления и блок управления, при этом вьпсод генератора опорной частоты соединен с информационным входом делите- 4ля, управляющий вход которого подклю- чен к выходу блока управления, а выход - к четвертому входу коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения суточного хода часов | 1985 |

|

SU1273870A1 |

| Устройство для определения мгновенного суточного хода механических часов | 1987 |

|

SU1509824A1 |

| Устройство для измерения суточного хода часов | 1988 |

|

SU1613998A1 |

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Измеритель переходных характеристик | 1985 |

|

SU1287120A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения погрешности хода часов в условиях часовых мастерских при наладке нестандартного оборудования. Цель - расширение функциональных возможностей устройства за счет измерений погрешности хода часов с любым стандартным периодом колебаний баланса. Устройство содержит датчик 1 временных интервалов, счетчик 2 временных интервалов, блок 3 управления, блок 4 определения погрешности, коммутатор 5, делитель 6 с переменным коэффициентом деления, генератор 7 опорной частоты, преобразователь 8 двоично-десятичного кода в десятичный и блок 9 цифровых индикаторов. Введение делителя 6 с переменным коэффициентом деления и блока 3 управления позволяет измерять мгновенный суточный ход для часов с любым стандартным периодом колебаний баланса. 6 ил.

Т, с Г 0,2 1 0,33 I 0,36 Г 0,4 Т 0,5Г 0,6

. ™ - «в-1Т--Г- « .п -- ™

М

54

50

4 / 2

54 5

45

36

30

3

Фив2

Фиг4

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ СУТОЧНОГО ХОДА ЧАСОВ | 0 |

|

SU244196A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для измерения суточного хода часов | 1985 |

|

SU1273870A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-15—Публикация

1987-08-10—Подача