(54) УСТРОЙСТВО СОПРЯЖЕНИЯ ДЛЯ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ

СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

| Устройство для сопряжения однородной вычислительной системы | 1978 |

|

SU769523A1 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU885989A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

| Устройство для подключения ЭВМ к системной шине | 1986 |

|

SU1361571A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1986 |

|

SU1365090A2 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU951287A2 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения однородной вычислительной системы | 1983 |

|

SU1117625A1 |

1 ,

Изобретение относится к вычисли- тельной технике и предназначено для сопряжения вычислительных машин в единую однородную вычислительную систему.

Известны устройства для сопряжения распределенных вычислительных систем, содержащие блок коммутации, блок управления, блок настройки и блок передачи И

Недостатком этих устройств является низкое быстродействие, обусловленное необходимостью перезаписи настро-. ечной информации всякий раз, когда связанная с ним микро-ЭВМ принимает участие в обмене.

Наиболее близкое к предлагаемому устройство для сопряжения однородной вычислительной система содержит блок коммутации, блок настройки, состоящий из регистра кода настрОйки, дешифратора кода настройки и первого элемента ИЛИ, блок передачи, состоящий из регистра обмена и второго элемента ИЛИ, дешифратор Адреса регистра, регистр синхронизации, третий элемент ИЛИ, регистр обобщенного безусловного перехода, блок прерывания,; регистр состояния, первые и вторые информационные и управляющие входывыходы устройства и третий информационный вход-выход устройства соединены соответственно с первыми, вторыми, третьими, четвертыми и пятыми входами-выходами блока коммутации, третий информационный вход-выход устройства соединен также с первьм входом регистра кода, настройки, входом дешифратора адреса регистра, вхо10дом-выходом регистра обмена, входамивыходами регистра состряния, блока прерывания, регистра обобщенного безусловного перехода и вторым входом регистра синхронизации, информационный выход блока коммутации соединен

15 с первым входом регистра обмена, вторым информационным входом регистра обобщенного безусловного перехода, ; вторым входом регистра кода настрой

20 ки, управляющий выход блока коммутации соединен со вторыми входами первого, второго и третьего элементов ИЛИ,С первым входе регистра состояния и входом блока прерыв ания, управ25ляющий вход настройки блока коммутации соединен с выходом дешифратора кода настройки, вход .которого соединен с выходом регистра кода настройки, вход системных сигналов блока

30 коммутации соединен с пятым выходом

дешифратора адреса регистра, nepabtft, второй, третий и четвертый выходы которого соединены соответственно с первыми входами первого, второго и третьего элементов ИЛИ и регистЕ а синхронизации, выходы первого, второго и третьего элементов ИЛИ соединены соответственно с управлянхцими входами регистра кода настройки, регистра обмена и регистра обобщенного безусловного перехода и первым, вторы и третьим входами регистра состояния

Для решения задачи однородная вычислительнаш система или структура разбивается на ряд подсистем. Степен участия элементарной машины в работе подсистемы может быть различной, в случае, когда микро-ЭВМ элементарной машины является принимающей, передающей, принимающей и транзитной, принимающей и передаклцей, она не может участвовать в работе никакой другой подсистемы. Если элементарная машина является транзитной с изменением направления передачи информации, то она также не может участвовать в работе никакой другой подсистема. В случае, если элементарная машшна является транзитной без изменения направления передачи, то ее микро-ЭВМ может участвовать в работе другой подсистемы, если устройство для сопряжения позволяет подсоединяться к свободным направлениям передачи информации 2 .

Недостатком данного устройства для сопряжения является низкая пропускная способность, так как оно не может коммутировать одновременно два независимых пути передачи информации, а также низкая надежность изза отсутствия аппаратной защиты регистра кода настройки со стороны микро-ЭВМ .

Цель изобретения - повышение быстродействия и увеличение надежности устройства.

Поставленная цель достигается тем что в устройство, содержащее блок коммутации, блок настройки, включаюший дешифратор кода настройки, регистр кода настройки и первый элемент ИЛИ, регистр синхронизации, блок прерывания, дешифратор адреса регистра, регистр обобщеНнох-о безусловного перехода, регистр состояний, элемент ИЛИ и блок передачи, включающий элемент ИЛИ и регист:р обмена, причем первые, вторые, третьи и четвертые информационные и управляющие входы-выходы блока коммутации являются соответственно первыми, вторыми, третьими и четвертыми информационными и управляющими входами-выходами устройства, пятый информационный вход-выход блока коммутации соединен с входом дешифратора адреса регистра, первым входом регистра синхронизации, входомвыходом регистра обмена, входом-выходом регистра обобщенного безусловного перехода, входом-выходом регистра состояния, входом-выходом блока прерывания, с первым информационным входом регистра кода настройки и пятым информационным входом-выходом устройства, выход регистра синхронизации соединен со входом синхронизации блока коммутации, информационный выход которого соединен со вторым информационным входом регистра

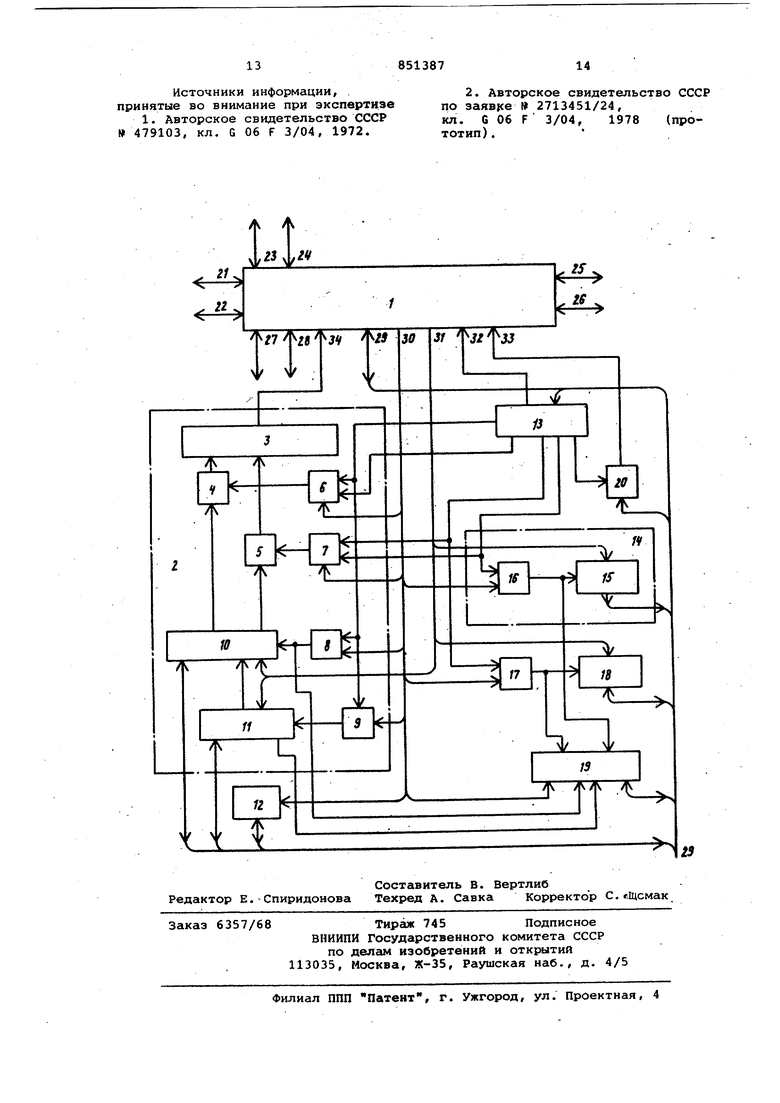

0 15 20 25 кода настройки, информационным входом регистра обмена и информационным вхозцом регистра обобщенного безусловного перехода, выход дешифратора кода настройки соединен с управляквдим входом настройки блока коммутации, управляющий выход которого соединен с первыми входами элемента ИЛИ, первого элемента ИЛИ блока настройки, элемента ИЛИ блока передачи, первым управляющим входом регистра состояния и входом блока прерывания, вход системных сигналов блока коммутации соединен с первым выходом дешифратора адреса регистра, второй, третий и четвертый выходы которого соединены соответственно со вторыми входами первого элемента ИЛИ блока настройки, элемента ИЛИ блока передачи и элемента ИЛИ, пятый выход дешифратора адреса регистра соединен со вторым входом регистра синхронизации, выходы первого элемента ИЛИ блока настройки, элемента ИЛИ блока передачи и элемен5та ИЛИ соединешл соответственно с управляющими входами регистра настройки, регистра обмена и регистра обобщенногсбезусловного перехода и со вторым, третьим и четвертым управляющими входами регистра состояния, в блок настройки введены регистр блокировки настройки, две группы элементов И и три элемента ИЛИ, причем первые входы второго, третьего и четвертого элементов ИЛИ соединены с управляющим выходом блока коммутации, вторые входы второго и третьего эле5 50 55 ментов ИЛИ соединены со вторым выходом дешифратора адреса регистра, третий и четвертый выходы которого соединены соответственно со вторым и третьим входами четвертого, элемента ИЛИ, а шестой выход - с третьим входом второго элемента ИЛИ, выход которого соединен с управляющим входом элемента И первой группы, информационные входы которых соединены с первой группой выходов регистра кода настрбйки/ а выходы - с первой группой входов дешифратора кода настройки, вторая группа входов которого соединейа с выходами элементов И второй группы, управляющие входы кото0 65 рых соединены с выходом четвертого элемента ИЛИ, а информационные входысо второй группой выходов регистра кода настройки, вход блокировки настройки которого соединен с первым выходом регистра блокировки настройки/ второй выход которого соединен с пятым управляющим входом регистра сост яния, управлякадий вход регистра блокировки настройки соединен с выходом третьего элемента ИЛИ, а первый и второй информационные входы - соответственно с пятым информационным входом-выходом устройства и информационным выходе блока коммутации. На чертеже представлена блок-схема устройства. Устройство содержит блок 1 коммутации, блок 2 настройки, состоящий из дешифратора 3 кода настройки, эле ментов И 4 и 5 первой и второй групп второго, четвертого, первого и третьего элементов ИЛИ 6, 1, 8 и 9, регистра 10 кода настройки и регистра 11 блокировки настройки, блок 12 прерываний, дешифратор 13 адреса регистра, блок 14 передачи, состоящий из регистра 15 обмена и элемента ИЛИ 16, элемента ИЛИ 17, регистр 18 обобщенного безусловного перехода, регистр 19 состояния,.регистр 20 синхронизации, первый информационный вход-выход (шина) 21 устройства, первый управлягаций вход-выход (шина) 22 устройства, второй информационный вход-выход (шина) .23 устройства, второй управляющий.вход-выход (шина) 24 устройства, третий информационный вход-выход (шина) 25 устройства,, третий управляющий вход-выход (шина) 26 устройства, четвертый информационный вход-выход (шина) 27 устройства, четвертый управляющий вход-выход (шина) 28 устройства, пятый информационный вход-выход (шина) 29 устройства, управляющий выход (шина) 30 блока коммутации, информационный выход (шина) 31 блока коммутации, вход системных сигналов (шина) 32 блока коммутации, вход синхронизации (шина) 33 блока коммутации, управляюдий вход настрой ки (шина) 34 блока коммутации. В вычислительной системе или стру туре, построенной с использованием устройства для сопряжения, выполняет ся следующий набор -системных операций настройка, обмен, обобщенный безусловный переход, обобщенный условный переход. Для реализации операций настройки и обобщенного условного перехода требуются одномерные связи между микроЭВМ (устройствами для сопряжения), входящими в вычислительную систему или структуру, а для реализации операций обмена и обобщенного безусловного перехода требуются двумерные св зи.. Переход от одномерных к двухмерным связям осуществляется с помощью информации, записанной в регистре кода настройки под воздействием управляющих сигналов I поступающих либо иЭ микро-ЭВМ данной элементарной машины либо из соседних микро-ЭВМ однородной вычислительной систет ы или структуры. Для 3toro регистр кода настройки функционсшьно разделен на две части, в первой части записывается соединительная функция одномерных связей и признаки начала и конца подсисте л, а во второй части - соединительная функция двухмерных связей. Устройство для сопряжения работает следующим образом. 1. Операция настройки. Операция настройки позволяет выделить подсистему из группы микро-ЭВМ для решения всей или части задачи, настроить микро-ЭВМ подсистбмл на прием и передачу информации только внутри подсистемы, на прием и трансляцию принятой информации или только на. трансляцию информации. Настройка подсистемы осуществляется из какой-либо одной микро-ЭВМ. Операция настройки заключается в занесении необходимой Информации в регистр 10 кода настройки и регистр 11 блокировки настройки устройства. В исходном состоянии в.блоке 1 коммутации осуществлена перекрестная коммутация противоположных информационных входов-выходов устройства, т.е. первый информационный вход-выход 21 соединен с третьим информационным входом-выходом 25, второй информационный вход-выход 23 соединен с четвертым информационным входом-выходом 27 устройства. Перед тем как приступить к настройке микро-ЭВМ считывает по шине 29 содержимое регистра 19 состояния и определяет занятие направления передачи информации. Настройка начинается в случае, если свободно хотя бы одно направление передачи информации. Настраивающая микро-ЭВМ начинает процесс настройки подсистемы с занесения информации в регистр 10 и регистр 11 своего устройства для сопряжения. Из микро-ЭВМ по шине 29 в дешифратор 13 поступает адрес регистра 10 кода настройки, на втором выходе дешифратора 13 появляется сигнал, который через элемент ИЛИ 8 поступает на управляющий вход регистра 10, разрешая запись слова настройки по первому информационному входу регистра 10. Одновременно с этим сигнал со второго выхода дешифратора 13 через элемент ИЛИ 9 и через элемент ИЛИ 6 поступает соответственно на управляющие входы регистра 11, разрешая запись информации в регистр 11 с шины 29, и на вход элементов И 4, подготавливая их для прохождения настроечной информации выходов регистра 10 через дешифратор 3 по управляющему входу настройки 34 блока кокмутации. Так как настройка идет последовательно, то в блоке 1 происходит под.. ключение шины 29 устройства к одной из четырех шин 21, 23, 25 или 27 и подключение входа 32 системных сигналов блока коммутации к одной иэ шин 22, 24, 26 или 28. В регистр 11 по шине 20 заносится информация, отмечающая занятые напра ления передачи информации. С выхода регистра 11 на вход регистра 19 состояния поступает информация о занятых направлениях коммутации входоввыходов. Со второго выхода регистра 11 информация поступает на вход блока бло кировки регистра 10, запрещая переко мутацию ранее занятых входов-выходов устройства. После того как микро-ЭВМ настроил свое устройство для сопряжения, она переходит к последовательной настрой ке остальных устройств для сопряжения подсистемы. Настраивакядая микроЭВМ выбирает из своей оперативной па мяти настроечную информацию для второго устройства для сопряжения и опя пересылает ее по адресу регистра 10 по шине 29, но на.этот раз настроечная информация не заносится в регист ры 10 и 11, а поступает по шине 29 в блок 11 коммутации. Дешифратор 13 ад реса регистра при этом вырабатывает по шине 32 сигнал системной настройки, который поступает в блок 1 коммутации. Направление передачи определяется кодом, записанным в регистр 10, который через открытые элементы И 4 поступает в дешифратор 3, с выхода которого по шинам 34.в блок 1 поступают управляющие сигналы. Настроечное слово проходит по шинам 21, 23, 25 или 27, а сигнал настройки по шинам 22, 24, 26 или 28 на соответствующие входы настраиваемого устройства сопряжения. В настраиваемом устройстве для сопряжения настроечное слово из блока 1 коммутации поступает -на второй информационный вход регистра 10 по шине 31, а управляющий сигнал с наст ройки поступает из блока 1 коммутации по шине 30 через элемент ИЛИ 8 н управляющий вход регистра 10, разрешая запись настроечного слова в этот регистр. Одновременно с этим сигнал настройки с выхода элемента ИЛИ 8 поступает на вход регистра 19, устанавливая его соответствующий разряд в единицу. Сигнал настройки поступает также через элемент ИЛИ 9 на управляющий вход-регистра 11, разрешая запись в него информации, отмечающей занятые направления передачи информации . . С первого выхода регистра 11 на вход регистра 19 состояния поступает информация о занятых направлениях коммутации входов-выходов. Сигнал настройки поступает также на входы элементов И 4, разрешая прохождение настроечной информации с первых выходов регистра 10 в дешифратор 3, подготавливая тем самым блок 1 коммутации для прохождения настроечной информации для следующего блока для сопряжения. После того как устройство получает настроечное, слово связанная с ним микро-ЭВМ переходит на режим работы по прерыванию. Это осуществляется следующим образом . Сигнал настройки по шине 30 поступает на вход блока 12 прерывания, подготавливая его к работе. Когда настроено последнее устрой-ство подсистемы, т. е. когда настроечное слово, содержащее признак конца подсистемы, занесено в регистр 10 соответствующего устройства, на выходе дешифратора 3 появляется сигнал окончания настройки, который с выхода блока 1 по шине 30 поступает в блок 12, с выхода которого по шине 29 -поступает сигнал запроса прерывания. Если микро-ЭВМ отвечает по шине 29 сигналом готовности, то из блока 12 считывается соответствующий адрес команды прерывания, который по шине 29 поступает в микро-ЭВМ. 2. Обобщенный условный переход (ОУП). Для синхронизации всех микро-ЭВМ подсистемы сразу же после операции настройки выполняется системная операция ОУП, после выполнения которой все микро-ЭВМ переходят к выполнению параллельной программы. Операция ОУП выполняется следующим образом. Микро-ЭВМ, завершившая свою работу по программе (подпрограмме) параллельной ветви, устанавливает регистр 20 синхронизации в единичное состояние. С выхода регистра 20 по шине 33 сигнал системной синхронизации поступает в блок 1 коммутации. Сигнал с шестого выхода дешифратора 13 через. элемент ИЛИ 6 поступает на вход элементов И 4, разрешая прохождение настроечной информации из регистра 10 . в дешифратор 3, которая соответствует комглутации одномерных связей в подсистеме, как бы выстраивая все элементарные машины подсистег ш в линейку. В тот момент, когда все регистры 20 устройств подсистемы устанавливаются в единичное состояние, в блоках 1 вырабатывается сигнал обобщенного условия, который поступает с выхода блока коммутации и по шине 30 заносится в соответствукадий разряд регистра 19. Одновременно этот сигнал поступает в блок 12 прерывания, с выхода которого по шине 29 в микро-ЭВМ поступает запрос на прерывание, и если 1 шкро-ЭВМ ответит по шине 29 сигналом готовности, то из блока 12 считывается соответствующий адрес команды прерывания, который по шине 29 поступает в микро-ЭВМ. Из регистра 19 считывается информация по шине 2Э в микро-ЭВМ, которая анализирует разряды регистра 19 и определив, что выполняется команда ОУП, переходит к следующему этапу параллельных вычислений.

Обычно операция ОУП выполняемся перед операцией обмена, синхронизируя все микро-ЭВМ подсистемы.

Системная операция обмена наиболее часто выполняется при параллельной работе всех микро-ЭВМ. При этом осуществляется трансляционный режим .обмена, т. е. одна микро-ЭВМ передает, а остальные принимают. Микро-ЭВМ, в прогрс1мме которой предусмотрено выполнение этой операции, осуществляет следующие действия; посылает по шинам 29 в дешифратор 13 адрес регистра 15 обмена, при этом по шине 20 в блок 1 коммутации поступает сигнгш системного обмена, этот сигнгш в передающей микро-ЭВМ с четвертого выхода дешифратора 13, а в принимающих микро-ЭВМ с выхода 30 блока 1 коммутации поступает через элемент ИЛИ 7 на входы элементов И 5, разрешая прохо;кдение настроечной информации с выходов регистра 10 в дешифратор 3, тем самым коммутируя двумерные соединения шин информационных входов-выходов 21, 23, 25 и 27 и управляющих входов-выходов 22, 24, 26, 28 устройств.

При считывании информационное слово из оперативной памяти микро-ЭВМ по шине 29 поступает на вход блока 1 коммутации и с его выходов по шинам 21, 23, 25 и 27 совместно с сигналом системного обмена на шинах 22, 24, 26, 28 поступает на входы-выходы принимающих устройств для сопряжения. В принимающих устройствах сигнал системного обмена поступает с шин 22, 24, 26 и 28 через блок 1 по шине 30 на вход элемента ИЛИ 16, разрешая запись в регистр 15 информационного СЛО на, выдаваемого по шине 31 через блок коммутации с шин 21, 23, 25 или 21, Одновременно с этим сигнал системного обмена по шине 30 поступает в соответствующий разряд регистра 19 состояния и в блок 12 прерывания, с выхода которого по шине 29 в микро-ЭВМ выдается сигнал запроса прерывания. При этом все микро-ЭВМ подсисте1 1ы переходят по прерыванию на обслуживание устройства для сопряжения. Из регистра 19 считывается информация по шине 29 в микро-ЭВМ, которая анализирует разряды регистра 19 и определив, что выполняется операция обмена, считывает по шине 29 из регистра 15 обмена информационное слово в регистр общего aзнaчeния микро-ЭВМ.

После выполнения операции обмена все микро-ЭВМ выполняют операцию ОУП и все микро-ЭВМ подсистемы переходят к следующему этапу.параллельной работы.

.4. Обобщенный безусловный переход (ОБУП). Операция ОБУП выполняется после операции ОУП, т. е. все микроЭВМ переходят к следующему этапу параллельных вычислений.

Управление дальнейшим ходом параллельных вычислений берет на себя одна из микро-ЭВМ подсистемы. При этом по шине 29 в дешифратор 13 поступает адрес регистра 18 обобщенного безусловного перехода и на первом и четвертом выходах дешифратора 13 появляется сигнал системного обощенного беусловного перехода. С четвертого вцхда дешифратора 13 сигнал поступает через элемент ИЛИ 17 на управляющий вход регистра 18 в соответствующий разряд регистра 19 -состояния и через элемент ИЛИ 7 на входы элементов И 5 разрешая прохождение настроечной информации с выЯодов, регистра 10 в дешифратор 3, тем самым коммутируя двумерные соединения между шинами информационных входов-выходов 21, 23 25 и 27 и управляющих входов-выходов 22, 24, 26, 28 устройства. С первого выхода дешифратора 13 сигнал по шине 32 поступит в блок 1 коммутации. По шине 29 информационное слово записывается в регистр 18, а также через блок 1 коммутации поступает на шины

21,23/ 25, 27 устройства.

В принимающих устройствах для сопряжения сигнал системного обобщенного безусловного перехода поступает с шин 22, 24, 26, 28 через блок 1 коммутации по шине 30 в блок 12 прерывания, с выхода которого по шине 29 в микро-Э-ВМ поступает сигнал запроса прерывания. Кроме того, сигнал перехода по шине 30 поступает через элемент ИЛИ 8 на входы элементов И 5 разрешая прохождение настроечной информации со второго выхода регистра 10 в дешифратор 3, тем самым коммутируя двумерные соединения между шинами .информационных- входов-выходов 21, 23, 25, 27 и уп|эавляющих входов-выходов

22,24, 26, 28 устройства. Сигнал перехода поступает также в соответствующий разряд регистра 19 и на вход элемента ИЛИ 17, разрешая запись в регистр 18 обобщенного безусловного перехода, информационное слово по шине 31 через блок 1 коммутации с шин 21, 23, 25, 27.

Все микро-ЭВМ подсистемы переходят по прерыванию на обслуживание устройства для сопряжения. Из регистра 19 считывается информация по шине 29 в микро-ЭВМ,которая анализирует разряды регистра 19, определяет, что выполняется операция ОБУП, и по шине 29 из регистра 18 микро-ЭШ считывае ся информационное слово, которое вос принимается как адрес, либо команда. И все микро-ЭВМ переходят на полную ветвь параллельных вычислений. Однородная вычислительная система или структура, построенная с использованием предлагаемого устройства для сопряжения, предназначена для решения сложных сильно связанных задач по параллельным алгоритмам. Производительность однородной вычислительной системы (структуры) зависит от скорости выполнения системных операций. Таким образом, устройство позволя ет повысить производительность однородной вычислительной системы (струк туры) за счет уменьшения времени выполнения системных операций, а также повысить надежность устройства. Повышение надежности устойства св зано с тем, что существует аппаратна защита содержимого регистра настройки от случайных воздействий со стбро ны микро-ЭВМ за счет наличия регистра блокировки настройки. Формула изобретения Устройство сопряжения для однородной вычислительной системы, содержащее блок коммутации, блок настройки, включающий дааифратор кода настройки, регистр кода настройки и первый элемент ИЛИ, регистр синхронизации, блок прерывания, дешифратор адреса регист ра, регистр обобщенного безусловного перехода, регистр состояния, элемент ИЛИ и блок передачи, включающий элемент ИЛИ и регистр обмена, причем первые, вторые, третьи и четвертые информационные и управляющие входывыходы блока коммутации являются соот ветственно первыми, вторыми, третьими и четвертыми информационными и управляющими входами-выходами устройства, йятый информационный вход-выход блока коммутации соединен с входом дешиф- ратора адреса регистра, первым входом регистра синхронизации, входомвыходом регистра обмена, входом-выходом регистра обобщенного безусловного перехода, вхсздом-выходом регистра состояния, входом-выходом блока прерывания, с первым информационным входом регистра кода настройки и пятым информационным входом-выходом устройства, выход регистра синхронизации соединен со входом синхронизации блока коммутации, информационный выход .которого соединен -со вторым информационным входом регистра кода настройки, информационным входом регистра обмена и информационным входом регистра обобщенного безусловного перехода, выход дешифратора кода настройки соединен с управляющим входом настройки блока коммутации, управляющий выход которого соединен с первыми входами элемента ИЛИ, первого элемента ИЛИ блока настройки, элемента ИЛИ блока передачи, первым управляющим входом регистра состояния и. входом блока прерывания, вход системных сигналов блока коммутации соединен с первым выходом дешифратора адреса регистра, второй, третий и четвертый выходы которого соединены соответственно со вторыми входами первого элемента ИЛИ блока настройки, элемента ИЛИ блока передачи и элемента ИЛИ, пятый выход дешифратора сшреса регистра соединен со вторым входом регистра синхронизации, выходы первого элемента ИЛИ блока настройки, элемента ИЛИ блока передачи и элемента ИЛИ соединены соответственно с управляющими входами регистра настройки , регистра обмена и регистра обобщенного безусловного перехода и со вторым, третьим и четвертым управляющими входами регистра состояния, отличающееся тем, что, с целью повышения пропускной способности устройства, в блок настройки введены регистр блокировки настройки, две группы элементов И и три элемента ИЛИ, причем первые входы второго, третьего и четвертого элементов ИЛИ соединены с управляющим выходом блока коммутации, вторые входы второго и третьего элементов ИЛИ соединены со вторым выходом дешифратора адреса регистра, третий и четвертый выходы которого соединены соответственно со вторым и третьим входами четвертого элемента ИЛИ, а шестой выход - с третьим входом второго элемента ИЛИ, выход которого соединен с управляющим входом элементов И первой группы, информационные входы которых соединены с первой группой выходов регистра настройки, а выходы с первой группой входов дешифратора кода настройки, вторая группа входов которого соединена с выходами элементов И второй группы, управляющие входы которых соединены с выходом четвертого элемента ИЛИ, а информационные входы - со второй группой выходов регистра кода настройки, вход блокировки настройки которого соединен с первым выходом регистра блокировки настройки, второй выход которого соединен с пятым управляющим входом pe-i гистра состояния, управляющий вход регистра блокировки настройки соединен с выходом третьего элемента ИЛИ, а первый и второй информационные входы - соответственно с пятым информационным входом-выходом устройства и информационным выходом блока коммутации.

13851387

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-07-30—Публикация

1979-10-02—Подача