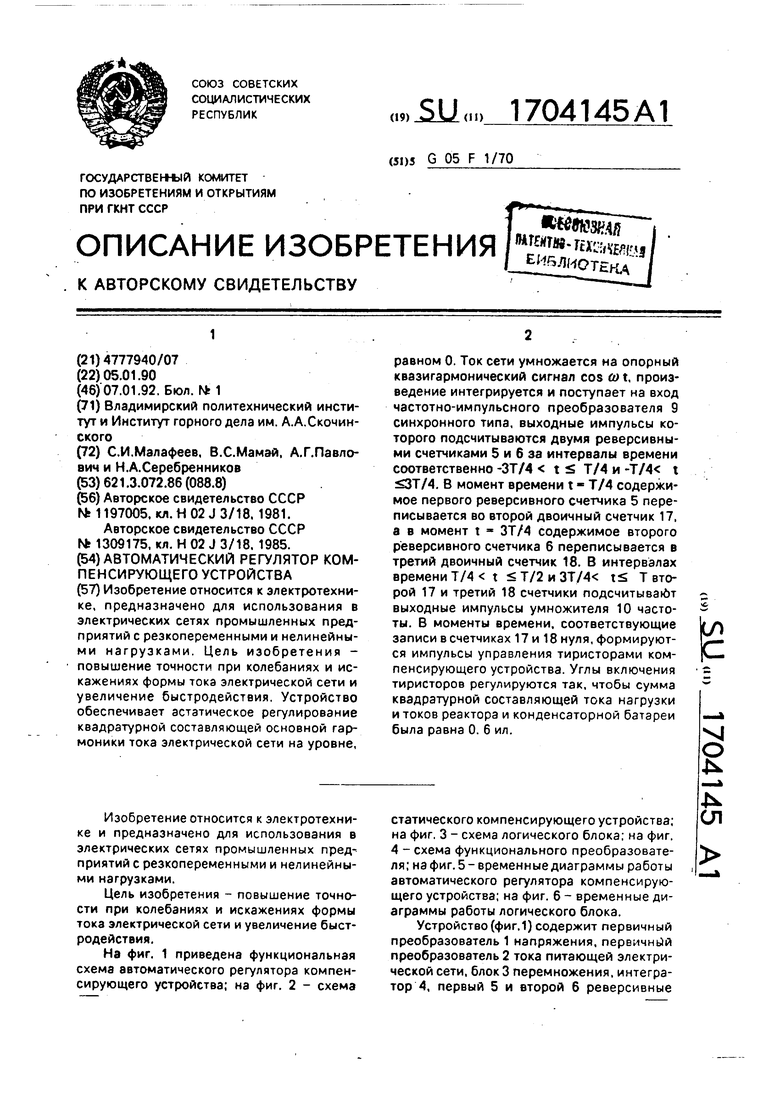

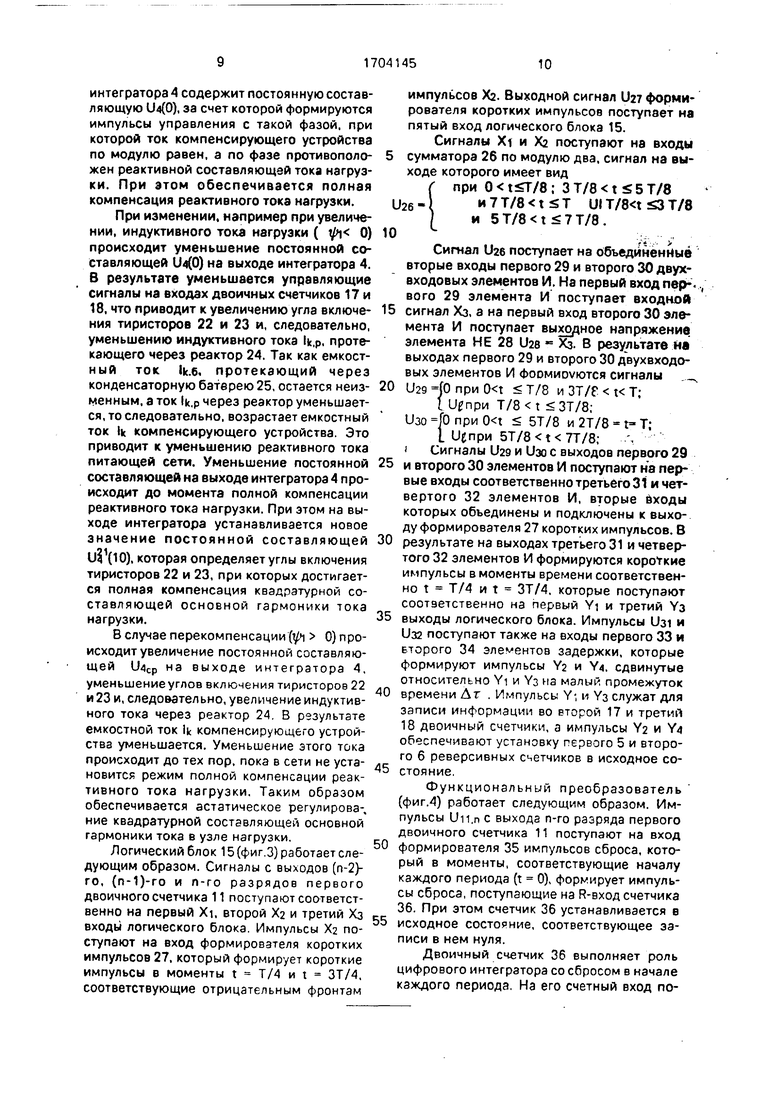

счетчики, фильтр 7 нижних частот, нуль-орган 8, частотно-импульсный преобразователь 9 синхронного типа, умножитель 10 частоты, первый двоичный счетчик 11, функциональный преобразователь 12, первый 13 и второй 14 трехвходовые элементы И, логический блок 15, элемент НЕ 16, второй 17 и третий 18 двоичные счетчики, триггер 19, первый 20 и второй 21 импульсные усилители.

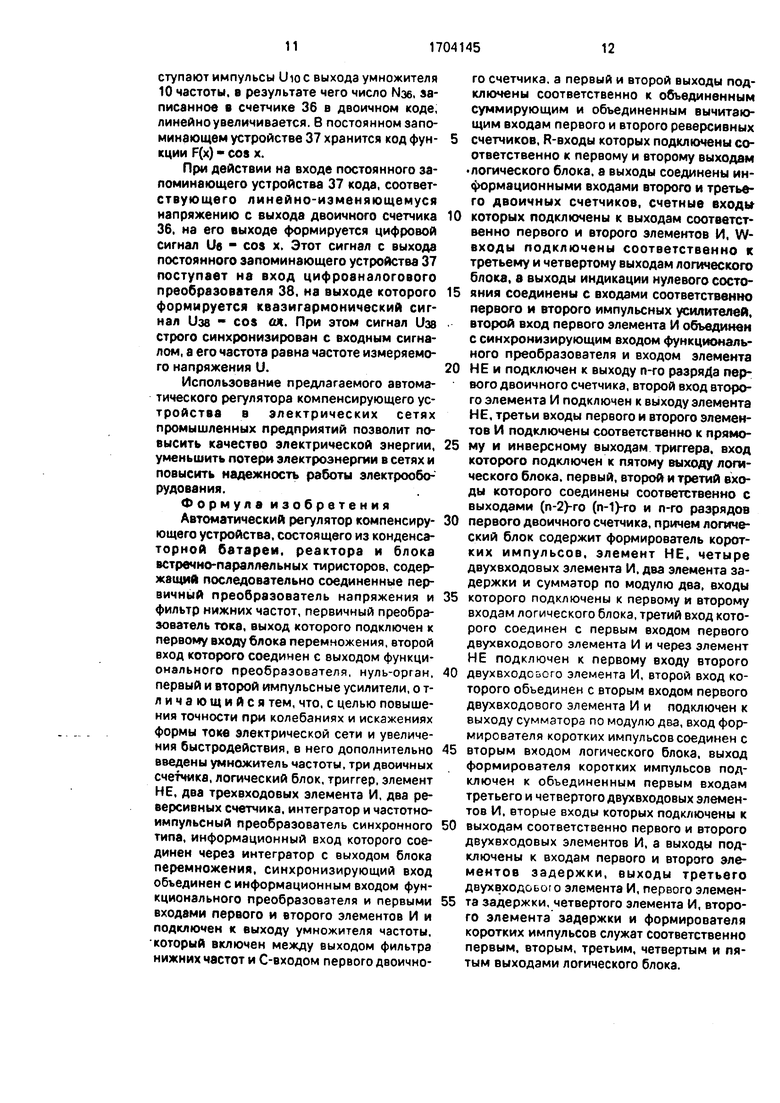

Статическое компенсирующее устройство (фиг.2) включает первый 22 и второй 23 тиристоры, реактор 24 и конденсаторную батарею 25.

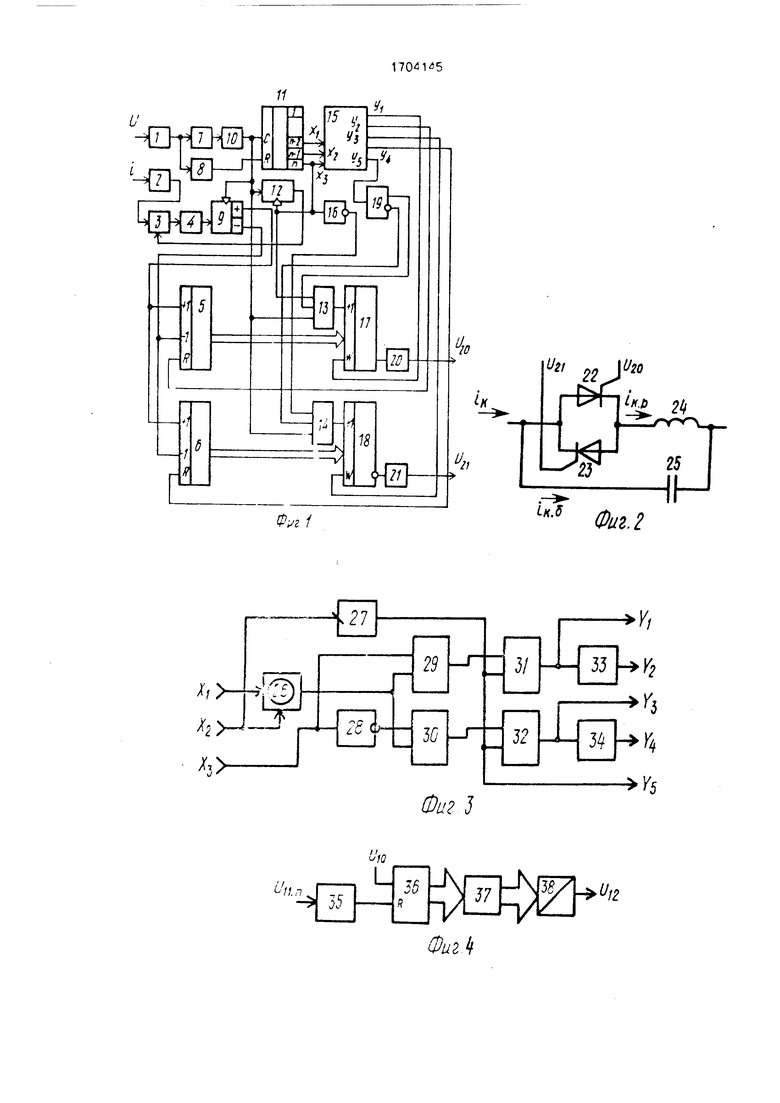

Логический блок 15 (фиг.З) содержит сумматор 26 по модулю два, формирователь 27 коротких импульсов, элемент НЕ 28, двухвходовые элементы И 29-32; первый 33 и второй 34 элементы задержки.

Функциональный преобразователь 12 (фиг.4) содержит формирователь 35 импульсов сброса, счетчик 36, постоянное запоминающее устройство 37, хранящее коды функции, цифроаналоговый преобразователь 38.

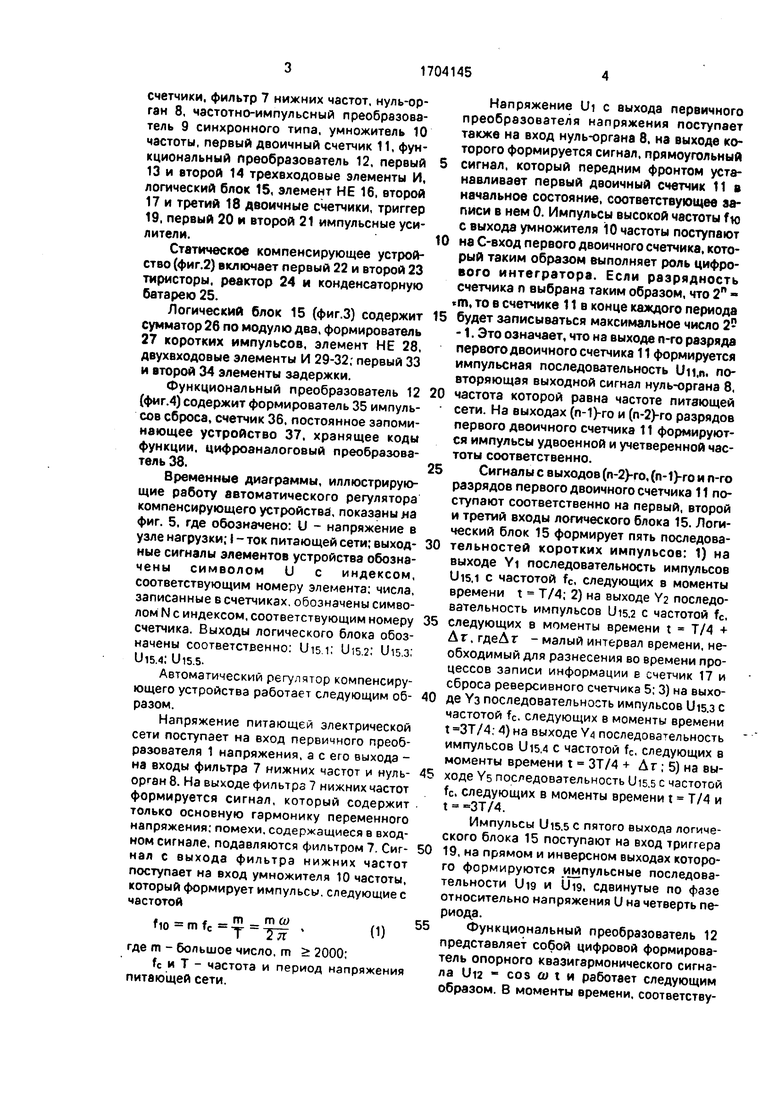

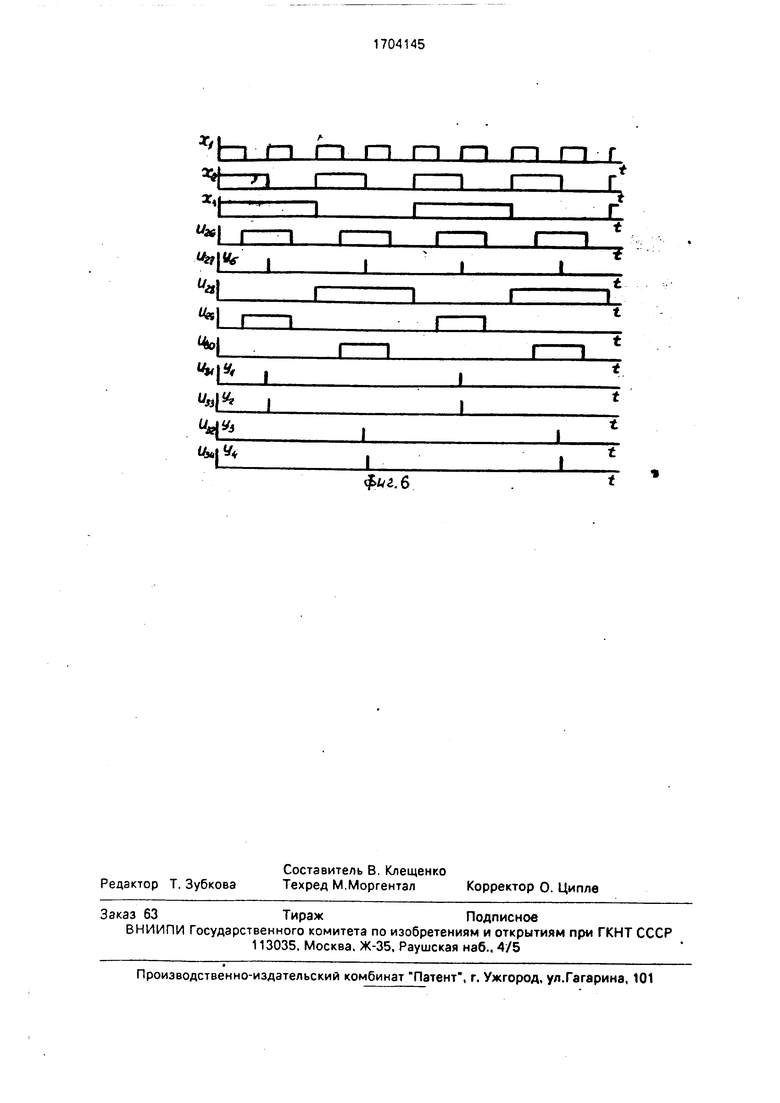

Временные диаграммы, иллюстрирующие работу автоматического регулятора компенсирующего устройства, показаны на фиг. 5, где обозначено: U - напряжение в узле нагрузки; I - ток питающей сети; выходные сигналы элементов устройства обозначены символом U с индексом, соответствующим номеру элемента; числа, записанные в счетчиках, обозначены символом N с индексом, соответствующим номеру счетчика. Выходы логического блока обозначены соответственно: Uis.i; 1)15.2: Uis.3;

U 15.4, U 15.5.

Автоматический регулятор компенсирующего устройства работает следующим образом.

Напряжение питающей электрической сети поступает на вход первичного преобразователя 1 напряжения, а с его выхода - на входы фильтра 7 нижних частот и нуль- орган 8. На выходе фильтра 7 нижних частот формируется сигнал, который содержит только основную гармонику переменного напряжения; помехи, содержащиеся в входном сигнале, подавляются фильтром 7. Сигнал с выхода фильтра нижних частот поступает на вход умножителя 10 частоты, который формирует импульсы, следующие с частотой

f, .(1)

где m - большое число, m 2000;

fc и Т - частота и период напряжения питающей сети.

Напряжение Ui с выхода первичного преобразователя напряжения поступает также на вход нуль-органа 8, на выходе которого формируется сигнал, прямоугольный

сигнал, который передним фронтом устанавливает первый двоичный счетчик 11 в начальное состояние, соответствующее записи в нем 0. Импульсы высокой частоты f ю с выхода умножителя 10 частоты поступают

на С-вход первого двоичного счетчика, который таким образом выполняет роль цифрового интегратора. Если разрядность счетчика п выбрана таким образом, что 2 - .т, то в счетчике 11 в конце каждого периода

будет записываться максимальное число 2- -1. Это означает, что на выходе n-го разряда первого двоичного счетчика 11 формируется импульсная последовательность Un.n. повторяющая выходной сигнал нуль-органа 8,

частота которой равна частоте питающей сети. На выходах (п-1)-го и (п-2)-го разрядов первого двоичного счетчика 11 формируются импульсы удвоенной и учетверенной частоты соответственно.

Сигналы с выходов (п-2)-го, (п-1)-го и п-го разрядов первого двоичного счетчика 11 поступают соответственно на первый, второй и третий входы логического блока 15. Логический блок 15 формирует пять последовательностей коротких импульсов; 1) на выходе YI последовательность импульсов U 15,1 с частотой fc, следующих в моменты времени t Т/4; 2) на выходе Y2 последовательность импульсов U 15.2 с частотой fc,

следующих в моменты времени t Т/4 + Дг, гдеДг - малый интервал времени, необходимый для разнесения во времени процессов записи информации в счетчик 17 и сброса реверсивного счетчика 5; 3) на выходе Уз последовательность импульсов Uis.3 с частотой fc. следующих в моменты времени t ЗТ/4; 4) на выходе Уз последовательность импульсов U 15.4 с частотой fc, следующих в моменты времени t ЗТ/4 + Дг; 5) на выходе YS последовательность Uis.s с частотой fc, следующих в моменты времени t Т/4 и t -3T/4.

Импульсы U 15.5 с пятого выхода логического блока 15 поступают на вход триггера

19, на прямом и инверсном выходах которого формируются импульсные последовательности U19 и U19, сдвинутые по фазе относительно напряжения U на четверть периода.

Функциональный преобразователь 12 представляет собой цифровой формирователь опорного квазигармонического сигнала U12 cos (о и работает следующим образом. В моменты времени, соответствующие положительным и отрицательным фронтам импульсов Un,n, поступающих с выхода п-го разряда первого двоичного счетчика 11 на управляющий вход функционального преобразователя 12, т.е. в моменты, соответствующие началу (t « 0) каждого периода напряжения, функциональный преобразователь устанавливается сигналом Un,n в начальное состояние. Далее функциональный преобразователь 12 выполняет преобразование количества импульсов Uio. поступающих с выхода умножителя 10 частоты на его информационный вход, в квазигармонический сигнал U12. который строго синхронизирован с напряжением сети, а частота совпадает с частотой сети fc. Несинусоидальный ток

00

I 2 lMisln(IOH +VO-(2) i 1

где I - номер гармоники;

IMI - амплитуда 1-й гармоники тока: $ - фазовый сдвиг 1-й гармоники тока, преобразуется с помощью первичного преобразователя 2 тока в напряжение .

Сигналы U2 с выхода первичного преобразователя тока 2 и сигнал Ui2 с выхода функционального преобразователя 12 поступают на входы блока 3 перемножения, на выходе которого формируется сигнал Уз. среднее за период Т основной гармоники значение которого равно

1 т °°

U3cp 2Y / 2 ( +VO- 1 о 1

cosun d t

KM IMI

sin W

(3)

где «2 - коэффициент передсчи первичного преобразователя 2 тока, и пропорционально реактивной составляющей тока сети.

Сигнал Уз поступает на вход интегратора 4. Так как напряжение 1)з представляет собой сумму постоянной составляющей 1)зср и гармоник Уз. то выходной сигнал интегратора 4 также можно представить в виде суммы постоянной составляющей 1М(0), отражающей начальные условия, линейно- изменяющегося напряжения LMcp(t) и высших гармоник U4.

Следовательно, при наличии квадратурной составляющей основной гармоники тока сигнал на выходе интегратора 4 возрастает со скоростью, пропорциональной этой составляющей. Знак выходного сигнала интегратора 4 определяется знаком фазового сдвига основной гармоники тока относительно напряжения U. При V 1 О среднее значение напряжения на входе интегратора 4 равно 0, и, следовательно,среднее значение его выходного сигнала не изменяется.

Выходной сигнал 1М интегратора А поступает на вход частотно-импульсного пре- 5 образователя 9 синхронного типа. Среднее значение его выходной частоты пропорционально входному напряжению из и частоте fio тактовых импульсов Uio, поступающих с выхода умножителя 10 частоты.

0 Если напряжение U 0, то выходные импульсы частотно-импульсного преобразователя 9 формируются на его первом выходе (+), если П4 0. то на втором выходе (-). Импульсы с первого и второго выходов час5 тотно-импульсного преобразователя 9 поступают соответственно на объединенные суммирующие и объединенные вычитающие входы первого 5 и второго б реверсивных счетчиков.

0 Первый 5 и второй б реверсивные счетчики устанавливаются выходными импульсами Ui5.2 и Uis,4 логического блока 15 в состояние, соответствующее записи в них нуля один раз за период в моменты соответ5 ственно t - Т/4 и t - ЗТ/4.

Импульсы (Jg и IV с первого и второго выходов частотно-импульсного преобразователя 9 синхронного типа подсчитываются первым 5 и вторым 6 дво0 ичными счетчиками. При этом в каждом счетчике подсчет импульсов осуществляется в течение одного периода Т сетевого на- пряжения, после чего производится установка счетчиков в исходное состояние.

5 В результате в момент времени t Т/4 в первом двоичном счетчике 5 записывается число NS:

N5 K9U4(-3T/4)m + K9K4K42 MimA

0 -, Т sin VI .(4) где KU - коэффициент передачи интегратора:

Kg - коэффициент передачи частотно- импульсного преобразователя.

5 Аналогично во втором реверсивном счетчике 6 в момент времени t ЗТ/4 записывается число NG.

Числа N s и Ne, записываемые в первом 5 и втором б реверсивных счетчиках, пред0 ставляютсг в двоично-дополнительном коде. При этом знак записанного числа определяется значением старшего разряда счетчика: положительному значению соответствует 0, отрицательному 1. При отстаю5 щем токе (VI 0) в первом 5 и втором 6 счетчиках записываются отрицательные числа.

В моменты времени t - Т/4 и t ЗТ/4 выходными импульсами Uis.i и Ui5.3 логического блока 15 осуществляется запись содержимого соответственно первого 5 и второго 6 реверсивных счетчиков во второй 17 и третий 18 двоичные счетчики. Счетные входы второго 17 и третьего 18 двоичных счетчиков подключены к выходам соответственно первого 13 и второго 14 трехвходовых элементов И, на объединенные третьи входы которых поступают выходные импульсы Uю умножителя 10 частоты. Первый и вто- рой входы первого элемента И 13 подключены соответственно к выходу п-го разряда первого двоичного счетчика 11 и прямому выходу триггера 15. Поэтому на суммирующий вход второго двоичного счетчика 17 в течение интервала времени Т/4 t Т/2 поступают импульсы Uio с выхода умножителя частоты. В результате в интервале времени Т/4 t Т/2 происходит увеличение числа, записанного в момент t Т/4 во вто- ром двоичном счетчике 17 в соответствии с выражением

Ni7-N5 + fio(t-T/4)(5)

При достижении числом, записанным во втором двоичном счетчике 17. нулевого значения в момент времени t ti происходит формирование на выходе индикации нулевого состояния второго двоичного счетчика 17 импульса управления тиристо- ром, который через первый импульсный уси- литель 20 поступает на управляющий электрод первого тиристора 22.

Аналогичным образом в интервале времени ЗТ/4 t Т происходит формирование импульса управления вторым тиристором 23.

Определим статистическую характеристику устройства в виде зависимости угла включения тиристоров от выходного напряжения интегратора 4 в установившемся ре- жиме, т.е. при 1 0. Для этого подставим в уравнение (5) выражения (1). (4) и, положив VI 0, t ti, N1 0, получим

KgU4(-3T/4)m + Ј(t,-I)0 (6)

Решив уравнение (6) относительно угла включения тиристора

сп 2 л/Т ti , получим

1

СП 2л -К9и4(-ЗТ/4).(7)

Из уравнения (7) следует, что угол включения тиристоров изменяется от л/2 при

U4(-3T/4)-0 до Л при U4(-3T/4)-l Kg-При

этом следует учитывать, что формирование импульсов управления тиристорами происходит только при отстающем токе (у 0) и U4(-3T/4) 0. При U4{-3T/4) 0 число NIS.

записываемое во втором двоичном счетчике 17, всегда положительно, поэтому формирование импульса управления невозможно.

Аналогичным образом определяется зависимость угла включения второго тиристора 23 в момент времени 1з от напряжения управления U4(T/4):

«j 2 Л 3/4 - K9U4074).

Таким образом, в предлагаемом регуляторе компенсирующего устройства регулирование осуществляется в зависимости от значения квадратурной составляющей основной гармоники IMI sin ifi . При этом за счет интегрирования сигнала, пропорционального произведению тока сети на опорный квазигармонический сигнал cos u)t за период Т сети, управляющие сигналы NS и Ne, формируемые на выходах первого 5 и второго б реверсивных счетчиков, не зависят от искажений формы измеряемого тока. Так как измерения сигналов управления производятся в течение одного периода сети и заканчиваются в моменты времени t - Т/4 и t - ЗТ/4, а формирование импульсов управления тиристорами производится, в интервалах соответственно t4 t 5 Т/2 и ЗТ/4 t S Т. то следовательно, регулятор имеет предельно высокое быстродействие: суммарное время измерения и формирования импульса управления не превышает одного периода Т сети.

Другим важным достоинством предлагаемого технического решения является инвариантность углов включения тиристоров по отношению к изменениям частоты питающей сети.

Компенсация квадратурной составляющей основной гармоники тока нагрузки происходит следующим образом. Основную гармонику тока питающей электрической сети можно представить в виде суммы 3 составляющих

I - la + Ip + Ik,

где la - синфазная составляющая, la IMCOS y sinuH;

IP - квадратурная составляющая основной гармоники, Ip - Msln COStUf

Ik - ток компенсирующего устройства.

Ток компенсирующего устройства, в свою очередь, является суммой двух составляющих: нерегулируемого тока конденсаторной батареи 25, опережающего напряжение на 90 эл.град.

lK..6 cos он;

и регулируемого тиристорами тока реактора 24, основная гармоника которого равна

U.p- I p cos on;

В исходном состоянии в установившемся режиме при Vi 0 напряжение на выходе

интегратора 4 содержит постоянную составляющую U4(0), за счет которой формируются импульсы управления с такой фазой, при которой ток компенсирующего устройства по модулю равен, а по фазе противоположен реактивной составляющей тока нагрузки. При этом обеспечивается полная компенсация реактивного тока нагрузки.

При изменении, например при увеличении, индуктивного тока нагрузки ( ty 0) происходит уменьшение постоянной составляющей (0) на выходе интегратора 4. В результате уменьшается управляющие сигналы на входах двоичных счетчиков 17 и 18, что приводит к увеличению угла включения тиристоров 22 и 23 и, следовательно, уменьшению индуктивного тока Ik.p. протекающего через реактор 24. Так как емкост- ный ток lk.6, протекающий через конденсаторную батерею 25, остается неизменным, а ток Ik.p через реактор уменьшается, то следовательно, возрастает емкостный ток Ik компенсирующего устройства. Это приводит к уменьшению реактивного тока питающей сети. Уменьшение постоянной составляющей на выходе интегратора 4 происходит до момента полной компенсации реактивного тока нагрузки. При этом на выходе интегратора устанавливается новое значение постоянной составляющей

и31(Ю). которая определяет углы включения тиристоров 22 и 23, при которых достигается полная компенсация квадратурной составляющей основной гармоники тока нагрузки.

В случае перекомпенсации tyi 0) происходит увеличение постоянной составляющей U4cp на выходе интегратора 4, уменьшение углов включения тиристоров 22 и 23 и, следовательно, увеличение индуктивного тока через реактор 24. В результате емкостной ток Ik компенсирующего устройства уменьшается. Уменьшение этого тока происходит до тех пор, пока в сети не установится режим полной компенсации реактивного тока нагрузки. Таким образом обеспечивается астатическое регулирова-, ние квадратурной составляющей основной гармоники тока в узле нагрузки.

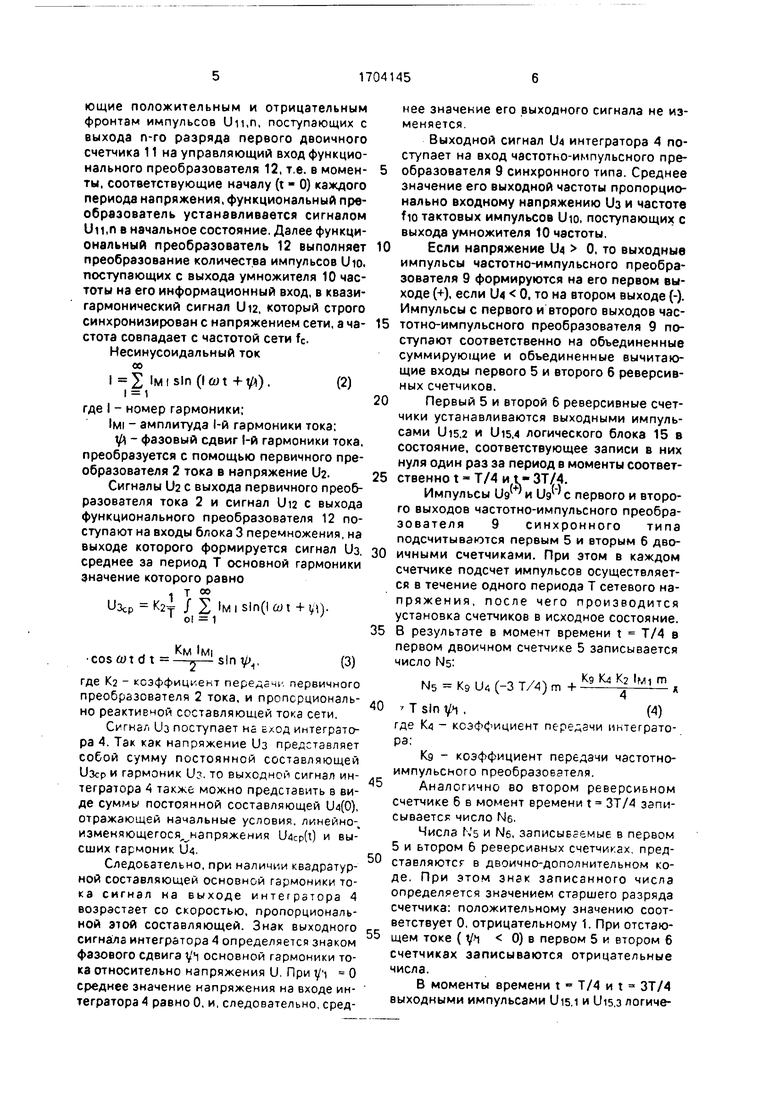

Логический блок 15 (фиг.З) работает следующим образом. Сигналы с выходов (п-2}- го, (п-1)-го и п-го разрядов первого двоичного счетчика 11 поступают соответственно на первый Xi, второй Х2 и третий Хз входы логического блока. Импульсы Xz поступают на вход формирователя коротких импульсов 27, который формирует короткие импульсы в моменты t Т/4 и t ЗТ/4. соответствующие отрицательным фронтам

импульсов Хг. Выходной сигнал 1)27 формирователя коротких импульсов поступает на пятый вход логического блока 15.

Сигналы Х| и Ха поступают на входы

сумматора 26 по модулю два, сигнал на выходе которого имеет вид

( при 3T/8 tS5T/8 26-lM7T/8 tST UIT/8 t2S3T/8 / и .

L.j- ,

Сигнал U26 поступает на объединенные вторые входы первого 29 и второго 30 двух- входовых элементов И. На первый вход пер-.,, вого 29 элемента И поступает входной

сигнал Хз, а на первый вход второго 30 элемента И поступает выходное напряжение элемента НЕ 28 U28 Хз. В результате на выходах первого 29 и второго 30 двухвходо- вых элементов И ФООМИОУЮТСЯ сигналы .

U29 0 при Т/8 и 3T/f t Т;

3T/8; изо(ОприО т 5Т/8 и2Т/8

I иепри 5Т/8 t 7T/8; .- , Сигналы U29 и изо с выходов первого 29

и второго 30 элементов И поступают на первые входы соответственно третьего 31 и четвертого 32 элементов И, вторые входы которых объединены и подключены к выходу формирователя 27 коротких импульсов. В

результате на выходах третьего 31 и четвертого 32 элементов И формируются короткие импульсы в моменты времени соответственно t Т/4 и t ЗТ/4, которые поступают соответственно на первый YI и третий Уз

выходы логического блока. Импульсы 11з1 и Кз2 поступают также на входы первого 33 и второго 34 элементов задержки, которые формируют импульсы Y2 и Y4, сдвинутые относительно YI и Уз на малый промежуток

времени А г . Импульсы Y-, и УЗ служат для записи информации во второй 17 и третий 18 двоичный счетчики, а импульсы Y2 и Y4 обеспечивают установку первого 5 и второго б реверсивных счетчиков в исходное состояние.

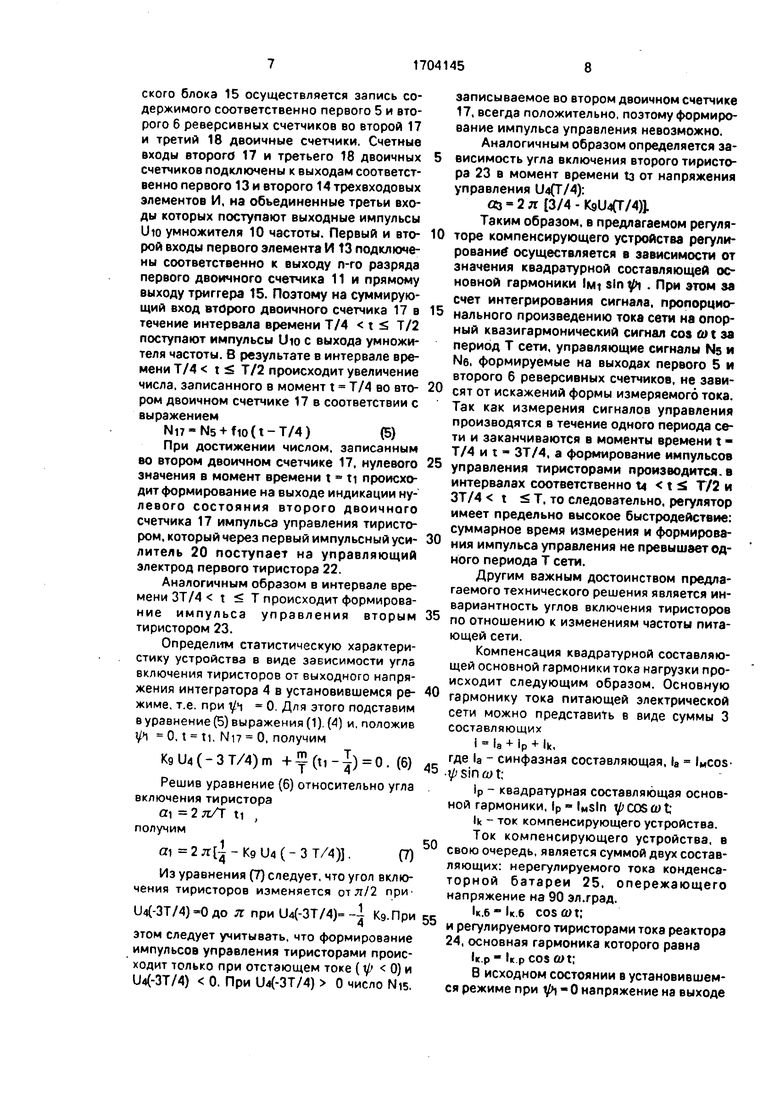

Функциональный преобразователь (фиг.4) работает следующим образом. Импульсы Uii,n с выхода n-го разряда первого двоичного счетчика 11 поступают на вход

формирователя 35 импульсов сброса, который в моменты, соответствующие началу каждого периода (t 0), формирует импульсы сброса, поступающие на R-вход счетчика 36. При этом счетчик 36 устанавливается в

исходное состояние, соответствующее записи в нем нуля.

Двоичный счетчик 36 выполняет роль цифрового интегратора со сбросом в начале каждого периода. На его счетный вход поступают импульсы Uio с выхода умножителя 10 частоты, в результате чего число Мзе, записанное в счетчике 36 в двоичном коде, линейно увеличивается. В постоянном запоминающем устройстве 37 хранится код функции F(x) - cos x.

При действии на входе постоянного запоминающего устройства 37 кода, соответствующего линейно-изменяющемуся напряжению с выхода двоичного счетчика 36, на его выходе формируется цифровой сигнал Ue cos x. Этот сигнал с выхода постоянного запоминающего устройства 37 поступает на вход цифроаналогового преобразователя 38, на выходе которого формируется квазигармонический сигнал DM - cos ox. При этом сигнал Uae строго синхронизирован с входным сигналом, а его частота равна частоте измеряемого напряжения U.

Использование предлагаемого автоматического регулятора компенсирующего устройства в электрических сетях промышленных предприятий позволит повысить качество электрической энергии, уменьшить потери электроэнергии в сетях и повысить надежность работы электрооборудования.

Формула изобретения

Автоматический регулятор компенсирующего устройства, состоящего из конденсаторной батареи, реактора и блока встречно-параллельных тиристоров, содержащий последовательно соединенные первичный преобразователь напряжения и фильтр нижних частот, первичный преобразователь тока, выход которого подключен к первому входу блока перемножения, второй вход которого соединен с выходом функционального преобразователя, нуль-орган, первый и второй импульсные усилители, о т- личающийся тем, что, с целью повышения точности при колебаниях и искажениях формы токе электрической сети и увеличения быстродействия, в него дополнительно введены умножитель частоты, три двоичных счетчика, логический блок, триггер, элемент НЕ, два трехвходовых элемента И, два реверсивных счетчика, интегратор и частотно- импульсный преобразователь синхронного типа, информационный вход которого соединен через интегратор с выходом блока перемножения, синхронизирующий вход объединен с информационным входом функционального преобразователя и первыми входами первого и второго элементов И и подключен к выходу умножителя частоты, который включен между выходом фильтра нижних частот и С-входом первого двоичного счетчика, а первый и второй выходы подключены соответственно к объединенным суммирующим и объединенным вычитающим входам первого и второго реверсивных

счетчиков, R-входы которых подключены соответственно к первому и второму выходам логического блока, а выходы соединены информационными входами второго и третьего двоичных счетчиков, счетные входы

которых подключены к выходам соответственно первого и второго элементов И, W- входы подключены соответственно к третьему и четвертому выходам логического блока, а выходы индикации нулевого состояния соединены с входами соответственно первого и второго импульсных усилителей,

второй вход первого элемента И объединен с синхронизирующим входом функционального преобразователя и входом элемента

НЕ и подключен к выходу n-го разряда первого двоичного счетчика, второй вход второго элемента И подключен к выходу элемента НЕ, третьи входы первого и второго элементов И подключены соответственно к прямому и инверсному выходам триггера, вход которого подключен к пятому выходу логического блока, первый, второй и третий входы которого соединены соответственно с выходами (п-2)-го (п-1)-го и n-го разрядов

первого двоичного счетчика, причем логический блок содержит формирователь коротких импульсов, элемент НЕ, четыре двухвходовых элемента И, два элемента задержки и сумматор по модулю два, входы

которого подключены к первому и второму входам логического блока, третий вход которого соединен с первым входом первого двухвходового элемента И и через элемент НЕ подключен к первому входу второго

двухвходо&ого элемента И, второй вход которого объединен с вторым входом первого двухвходового элемента И и подключен к выходу сумматора по модулю два, вход формирователя коротких импульсов соединен с

вторым входом логического блока, выход формирователя коротких импульсов подключен к объединенным первым входам третьего и четвертого двухвходовых элементов И. вторые входы которых подключены к

выходам соответственно первого и второго двухвходовых элементов И, а выходы подключены к входам первого и второго элементов задержки, выходы третьего двухвходового элемента И, первого элемента задержки, четвертого элемента И, второго элемента задержки и формирователя коротких импульсов служат соответственно первым, вторым, третьим, четвертым и пятым выходами логического блока.

1Щ

52

St.

К

Ч

№ CtHj

J

Щ ZZ n

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор компенсирующего устройства | 1990 |

|

SU1721705A2 |

| Регулятор статического компенсирующего устройства | 1988 |

|

SU1584032A1 |

| Измерительный преобразователь составляющих основной гармоники переменного тока | 1989 |

|

SU1689862A2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ УПРАВЛЕНИЯ ДЛЯ ТИРИСТОРА | 1991 |

|

RU2009601C1 |

| Регулятор конденсаторной батареи | 1989 |

|

SU1697067A1 |

| Устройство для компенсации реактивной мощности | 1986 |

|

SU1347118A1 |

| Преобразователь синфазной и квадратурной составляющих основной гармоники переменного тока | 1990 |

|

SU1712893A2 |

| Устройство для управления статическим тиристорным компенсатором | 1985 |

|

SU1309175A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АКТИВНОЙ И РЕАКТИВНОЙ СОСТАВЛЯЮЩИХ ТОКА | 1990 |

|

RU2018138C1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2373624C1 |

Изобретение относится к электротехнике, предназначено для использования в электрических сетях промышленных предприятий с резкопеременными и нелинейными нагрузками. Цель изобретения - повышение точности при колебаниях и искажениях формы тока электрической сети и увеличение быстродействия. Устройство обеспечивает астатическое регулирование квадратурной составляющей основной гармоники тока электрической сети на уровне, Изобретение относится к электротехнике и предназначено для использования в электрических сетях промышленных предприятий с резкопеременными и нелинейными нагрузками. Цель изобретения - повышение точности при колебаниях и искажениях формы тока электрической сети и увеличение быстродействия. На фиг. 1 приведена функциональная схема автоматического регулятора компенсирующего устройства; на фиг. 2 - схема равном 0. Ток сети умножается на опорный квазигармонический сигнал cos со t, произведение интегрируется и поступает на вход частотно-импульсного преобразователя 9 синхронного типа, выходные импульсы которого подсчитываются двумя реверсивными счетчиками 5 и 6 за интервалы времени соответственно -ЗТ/4 t Ј Т/4 и -Т/4 t ЗТ/4. В момент времени t - Т/4 содержимое первого реверсивного счетчика 5 переписывается во второй двоичный счетчик 17, а в момент t - ЗТ/4 содержимое второго реверсивного счетчика 6 переписывается в третий двоичный счетчик 18. В интервалах времени Т/4 t Т/2 и ЗТ/4 tS Т второй 17 и третий 18 счетчики подсчитывают выходные импульсы умножителя 10 частоты. В моменты времени, соответствующие записи в счетчиках 17 и 18 нуля, формируются импульсы управления тиристорами компенсирующего устройства. Углы включения тиристоров регулируются так, чтобы сумма квадратурной составляющей тока нагрузки и токов реактора и конденсаторной батареи была равна 0. 6 ил. статического компенсирующего устройства; на фиг. 3 - схема логического блока; на фиг. 4 - схема функционального преобразователя; на фиг. 5 - временные диаграммы работы автоматического регулятора компенсирующего устройства; на фиг. 6 - временные диаграммы работы логического блока. Устройство(фиг.1) содержит первичный преобразователь 1 напряжения, первичный преобразователь 2 тока питающей электрической сети, блок 3 перемножения, интегратор 4, первый 5 и второй 6 реверсивные Ј Ы О Ј ел

и ° ЬшШШш

(/, Ь

«a L а« ц

2Tt

гп п г

| Устройство для управления статическим компенсатором | 1984 |

|

SU1197005A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления статическим тиристорным компенсатором | 1985 |

|

SU1309175A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-01-07—Публикация

1990-01-05—Подача