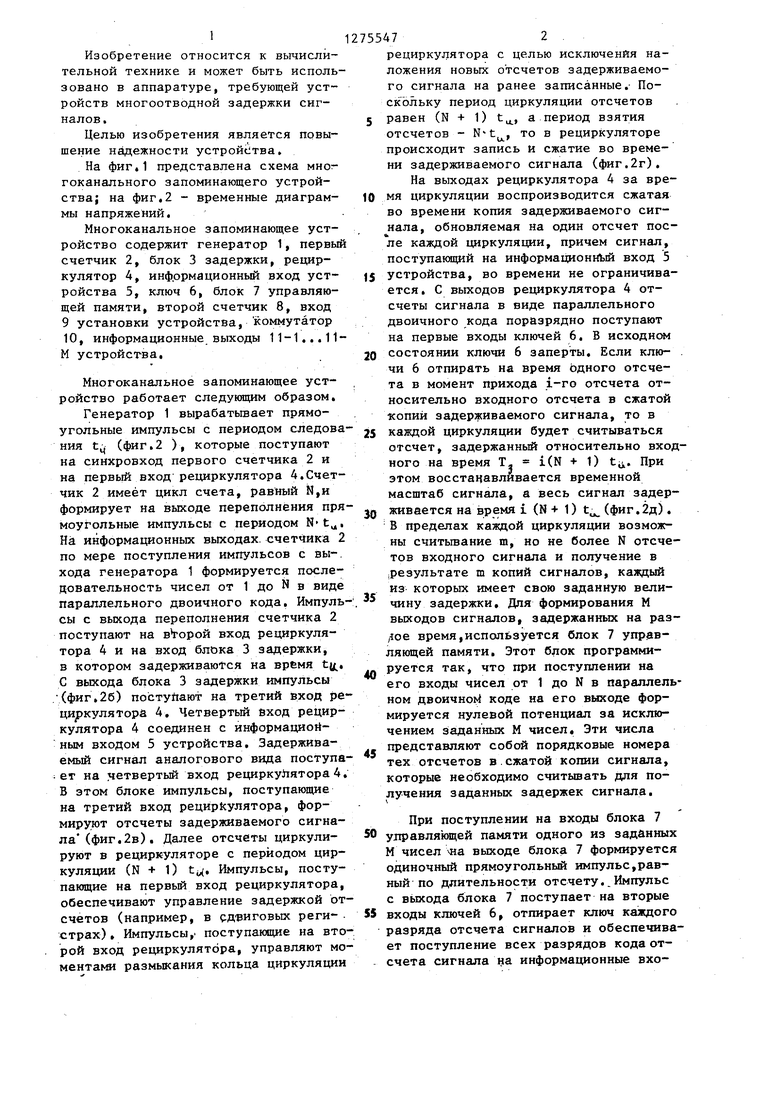

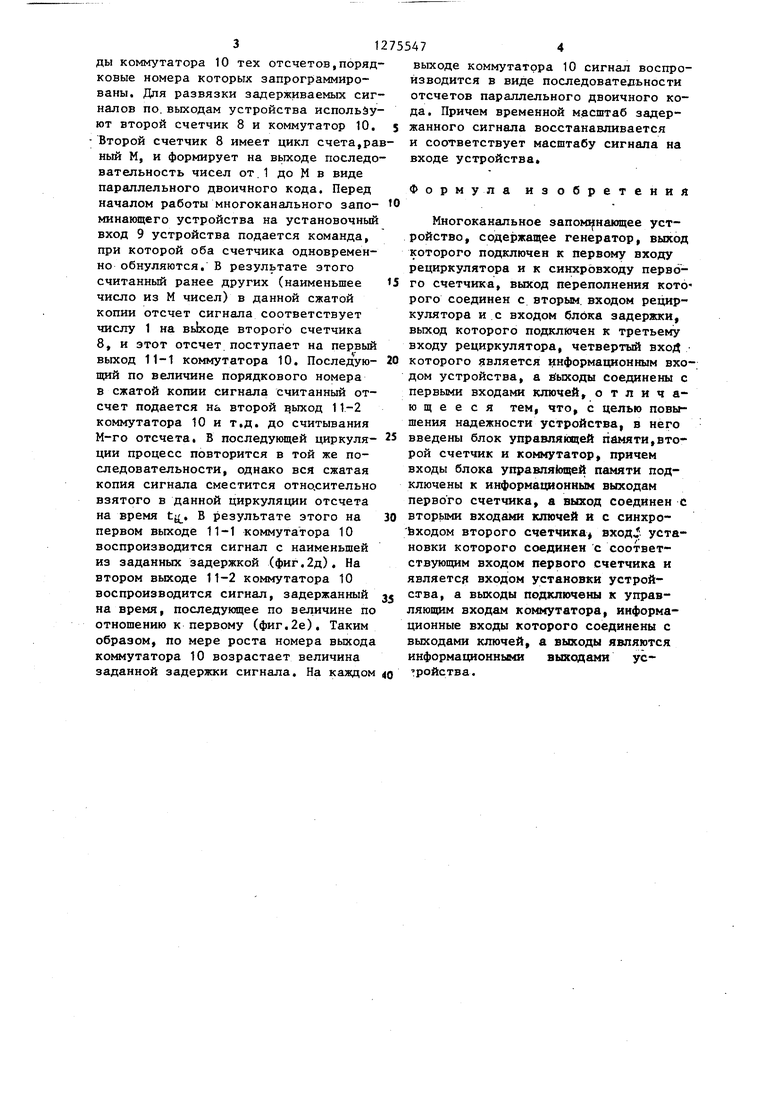

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре, требующей устройств многоотводной задержки сигналов. Целью изобретения является повышение надежности устройства. На фиг,1 представлена схема мно:гоканального запоминаклцего устройства; на фиг,2 - временные диаграммы напряжений. Многоканальное запоминающее устройство содержит генератор 1, первый счетчик 2, блок 3 задержки, рециркулятор 4, инф.ормационный вход устройства 5, ключ 6, блок 7 управляющей памяти, второй счетчик 8, вход 9 установки устройства, коммутатор 10, информационные выходы 11-1,,,11М устройства. Многоканальное запоминающее устройство работает следующим образом. Генератор 1 вырабатьшает прямоугольные импульсы с периодом следова ния t (фиг,2 ), которые поступают на синхровход первого счетчика 2 и на первый вход рециркулятора 4,Счетчик 2 имеет цикл счета, равный И,и формирует на выходе переполнения пря моугольные импульсы с периодом N-t,, На информационных выходах, счетчика 2 по мере поступления импульсов с вы-, хода генератора 1 формируется последовательность чисел от 1 до N в виде параллельного двоичного кода, Импуль сы с выхода переполнения счетчика 2 поступают на вход рециркулятора 4 и на вход блока 3 задержки, в котором задерживаю-гся на время tj, С выхода блока 3 задержки импульсы (фиг,2б) поступают на третий вход ре циркулятора 4, Четвертый йход рециркулятора 4 соединен с информациойным входом 5 устройства. Задерживаемый сигнал аналогового вида поступа - ет на 1етвертый вход рециркуЛтятора 4, В этом блоке импульсы, поступающие на третий вход рециркулятора, формируют отсчеты задерживаемого сигнала (фиг, 2в). Далее отсчеты циркулируют в рециркуляторе с периодом циркуляции (N + 1) tjx. Импульсы, поступающие на первьй вход рециркулятора, обеспечивают управление задержкой от счетов (например, в рдриговьпс регистрах) , Импульсы, поступающие на вто рой вход рециркулятора, управляют мо мента размыкания кольца циркуляции 472 редиркулятора с целью исключения наложения новых отсчетов задерживаемого сигнала на ранее записанные,- ПоС1со.льку период циркуляции отсчетов равен (N + 1) t, а период взятия отсчетов - Nt, то в рециркуляторе происходит запись и сжатие во времени задерживаемого сигнала (фиг.2г). На выходах рециркулятора 4 за время циркуляции воспроизводится сжатая во времени копия задерживаемого сигнала, обновляемая на один отсчет после каждой циркуляции, причем сигнал, поступакиций на информационНЬй вход 5 устройства, во времени не ограничивается , С выходов рециркулятора 4 отсчеты сигнала в виде параллельного двоичного кода поразрядно поступают на первые входы ключей 6, В исходно состоянии ключи 6 заперты. Если ключи 6 отпирать на время одного отсчета в момент прихода i-ro отсчета относительно входного отсчета в сжатой копий задерживаемого сигнала, то в каждой циркуляции будет считываться отсчет, задержанный относительно входного на время Т, i(N + 1) t. При этом восстанавливается временной масштаб сигнала, а весь сигнал задерживеется на время i (N + 1) t (фиг, 2д), В пределах каждой циркуляции возможны считьшание т, но не более N отсчетов входного сигнала и получение в .результате m копий сигналов, каждый из которых имеет свою заданную величину задержки. Для формирования М выходов сигналов, задержанных на раздое время,используется блок 7 управляющей памяти. Этот блок программируется так, что при поступлении на его входы чисел от 1 до N в параллельном двоичноь коде на его выходе формируется нулевой потенциал за исключением заданных М чисел. Эти числа представляют собой порядковые номера тех отсчетов в.сжатой копии сигнала, которые необходимо считывать для поучения заданных задержек сигнала. При поступлении на входы блока 7 правляющей памяти одного из заданных чисел на выходе блока 7 формируется диночный прямоугольный импульс,равый по длительности отсчету,.Импульс вькода блока 7 поступает на вторые ходы ключей 6, отпирает ключ каждого азряда отсчета сигналов и обеспечиват поступление всех разрядов кода отчета сигнала на информационные входы коммутатора 10 тех отсчетов,порядковые номера которых запрограммированы. Для развязки задерживаемых сигналов по. выходам устройства испольЗуют второй счетчик 8 и коммутатор 10. Второй счетчик 8 имеет цикл счета,раный М, и формирует на вьпсоде последовательность чисел от.1 до W в виде параллельного двоичного кода. Перед началом работы многоканального запоминающего устройства на установочный вход 9 устройства подается команда, при которой оба счетчика одновременно обнуляются. В результате этого считанный ранее других (наименьшее число из М чисел) в данной сжатой копии отсчет сигнала соответствует числу 1 на вьЬсоде второго счетчика 8, и этот отсчет поступает на первый выход 11-1 коммутатора 10. Последующий по величине порядкового номера в сжатой копии сигнала считанный отсчет подается нь второй ыход 11-2 коммутатора 10 и т.д. до считывания М-го отсчета. В последующей циркуляции процесс повторится в той же последовательности, однако вся сжатая копия сигнала сместится относительно взятого в данной циркуляции отсчета на время tj. В результате этого на первом выходе 11-1 коммутатора 10 воспроизводится сигнал с наименьшей из заданных задержкой (фиг.2д). На втором выходе 11-2 коммутатора 10 воспроизводится сигнал, задержанный на время, последующее по величине по отношению к первому (фиг.2е). Таким образом, по мере роста номера выхода коммутатора 10 возрастает величина заданной задержки сигнала. На каждом

выходе коммутатора 10 сигнал воспроизводится в виде последовательности отсчетов параллельного двоичного кода. Причем временной масштаб задержанного сигнала восстанавливается и соответствует масштабу сигнала на входе устройства.

Формула изобретения

Многоканальное запом1 нающее устройство, содержащее генератор, выход которого подключен к первому входу рециркулятора и к синхрЬвходу первого счетчика, выход переполнения которого соединен с вторым, входом рециркулятора и с входом блока задержки, выход которого подключен к третьему входу рециркулятора, четвертый вхоД которого является информационным входом устройства, а выходы соединены с первыми входами ключей, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок управляющей памяти,второй счетчик и коммутатор, причем входы блока управля1ощей памяти подключены к информационным выходам первого счетчика, а выход соединен с вторь1ми входами ключей и с синхроЬходом второго счетчика вход установки которого соединен с соответствующим входом первого счетчика и является входом установки устройства, а выходы подключены к управляющим входам коммутатора, информационные входы которого соединены с выходами ключей, а выходы являются информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное запоминающее устройство | 1983 |

|

SU1150662A1 |

| Запоминающее устройство | 1987 |

|

SU1424059A1 |

| Запоминающее устройство | 1982 |

|

SU1056271A1 |

| Блок управляемой задержки | 1986 |

|

SU1424058A1 |

| Многоканальное запоминающее устройство | 1985 |

|

SU1259338A1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1983 |

|

SU1107135A1 |

| Многоканальное запоминающее устройство | 1984 |

|

SU1257707A1 |

| Аналого-цифровой фазовращатель | 1988 |

|

SU1584082A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1990 |

|

RU2022485C1 |

| Аналого-цифровое устройство задержки | 1986 |

|

SU1356220A1 |

Изобретение относится к вычислительной технике « может быть использовано в аппаратуре,требующей многоотводной задержки сигналов. Целью изобретения является повышение надежности устройства. Устройство содержит генератор 1, первый 2 и второй 8 счетчик, блок 3 задержки, рецйркулятор 4, ключи 6, блок 7 управляющей памяти, коммутатор 10. Повышение надежности устройства достигается за счет уменьшения аппаратурных затрат в цепях управления и коммутации.2 ил. (Л

| Тренажер пловцов | 1978 |

|

SU842926A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Многоканальное запоминающее устройство | 1983 |

|

SU1150662A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-07—Публикация

1985-02-20—Подача