Изобретение относится к радиотехнике.

Цель изобретения - повышение помехоустойчивости.

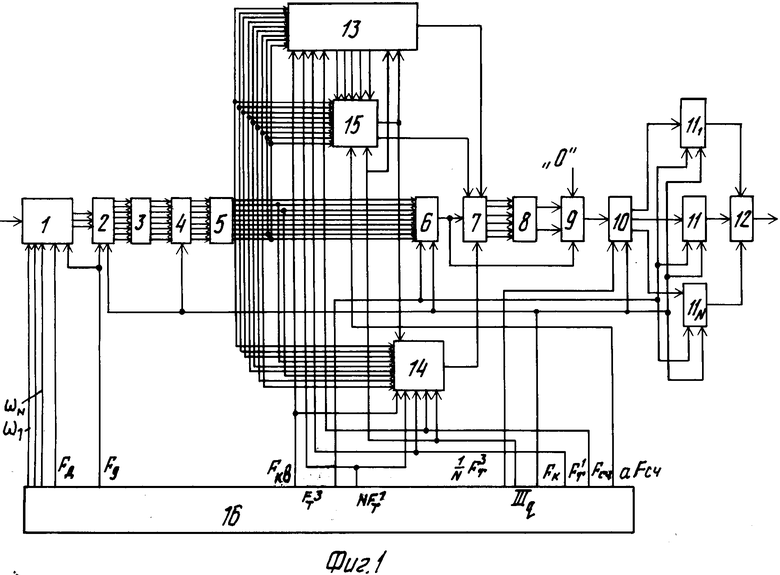

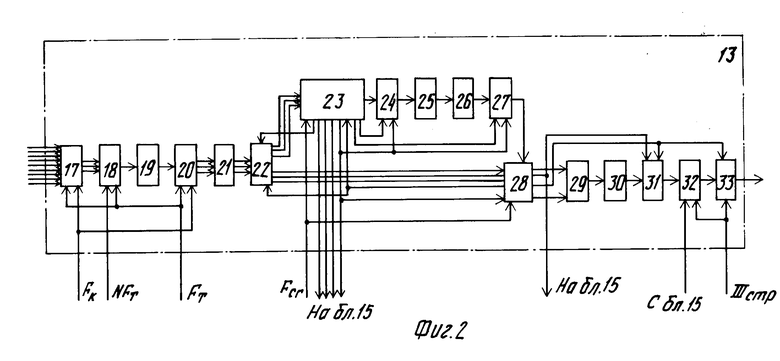

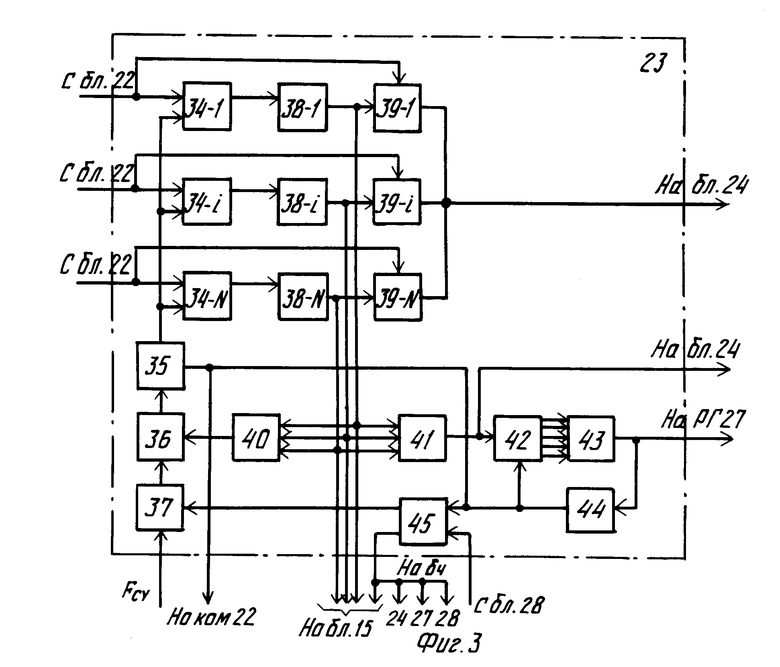

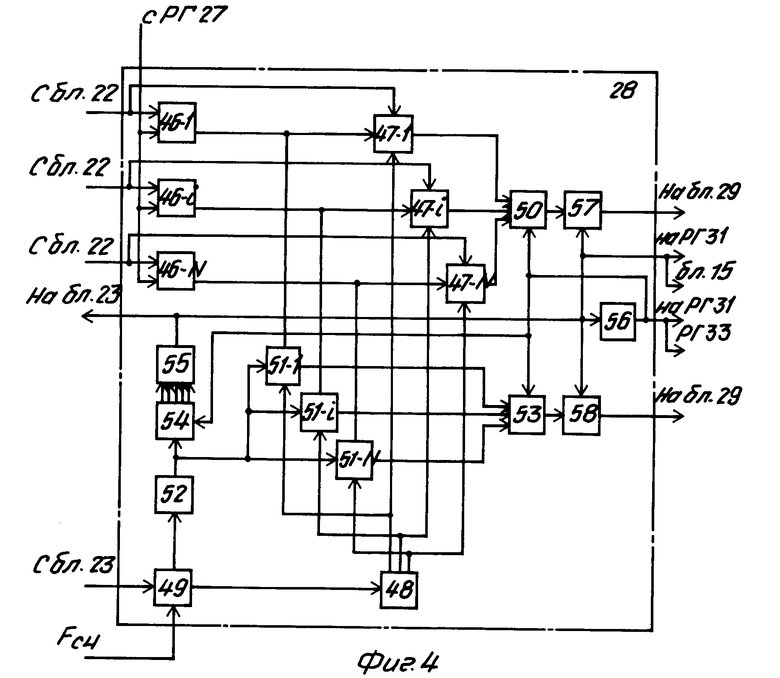

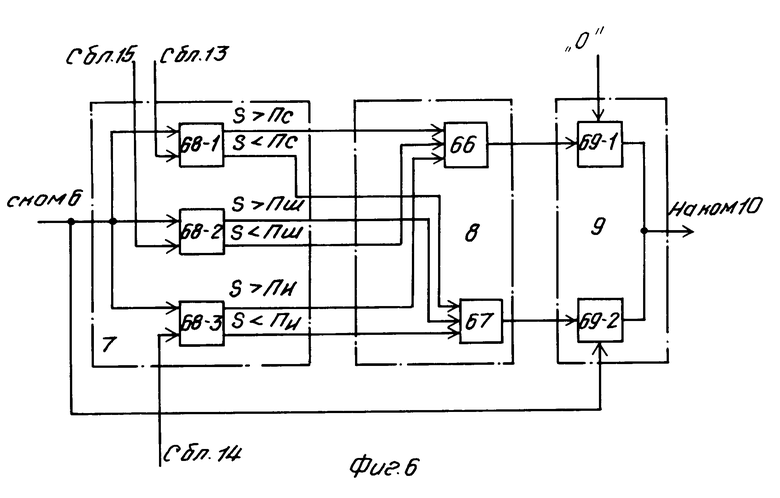

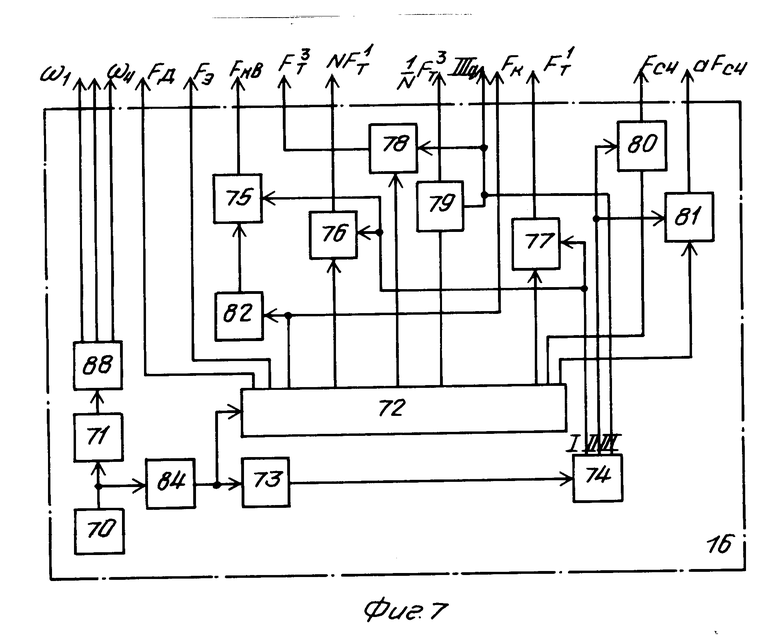

На фиг. 1 приведена структурная схема цифрового согласованного фильтра сигналов с дискретной частотной манипуляцией; на фиг. 2 - схема блока формирования порога; на фиг. 3 - структурная схема блока выбора N/2 минимальных чисел; на фиг. 4 - структурная схема блока выбора минимальных чисел; на фиг. 5 - схема третьего блока формирования порога; на фиг. 6 - схема последовательно соединенных порогового блока, блока дешифраторов и второго блока ключей; на фиг. 7 - схема блока синхронизации.

Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией содержит частотный рециркулятор 1, первый компаратор 2, первый блок памяти 3, первый блок ключей 4, второй блок памяти 5, второй коммутатор 6, пороговый блок 7, блок 8 дешифраторов, второй блок ключей 9, третий коммутатор 10, N- сумматоров-накопителей 11, блок 12 выбора максимального числа, первый, второй и третий блоки 13-15 формирования порогов, блок 16 синхронизации.

Первый блок 13 формирования порога содержит первый коммутатор 17, первый сумматор 18, первый делитель 19, второй коммутатор 20, блок 21 памяти, третий коммутатор 22, блок 23 выбора N/2 минимальных чисел, второй сумматор 24, второй делитель 25, первый умножитель 26, первый регистр 27, блок 28 выбора минимальных чисел, делитель 29 с переменным коэффициентом деления, второй умножитель 30, второй регистр 31, сумматор 32, третий регистр 33.

Блок 22 выбора N/2 минимальных чисел содержит N компараторов 34, первый счетчик 35, первые ключи 36, вторые ключи 37, первый формирователь 38 импульса, третьи ключи 39, схему ИЛИ-НЕ 40, схему ИЛИ 41, второй счетчик 42, дешифратор 43, второй формирователь 44 импульса, триггер 45.

Блок 28 выбора минимальных чисел содержит N компараторов 46, первые ключи 47, формирователь 48 стробов, вторые ключи 49, сумматор 50, третьи ключи 51, первый элемент задержки 52, первый счетчик 53, второй счетчик 54, дешифратор 55, второй элемент задержки 56, четвертый и пятый ключи 57 и 58.

Третий блок 15 формирования порога содержит блок 59 ключей, блок 60 выделения N/2 минимальных чисел, сумматор 61, делитель 62, умножитель 63, первый и второй регистры 64 и 65.

Последовательно соединенные пороговый блок 7, блок 8 и второй блок ключей 9 содержит элемент И 67, первый, второй и третий компараторы 68-1, 68-2 и 68-3, первые и вторые ключи 69-1, 69-2.

Блок 16 синхронизации содержит задающий генератор 70, первый, второй и третий делители частоты 71, 72, 73, формирователь 74 стробов, первые, вторые, третьи, четвертые, пятые, шестые, седьмые ключи 75-81, элемент 82 задержки, формирователь 83 опорных частот, формирователь 84 импульсов.

Устройство работает следующим образом.

Входной сигнал в виде аддитивной смеси полезного сигнала и шумов поступает на вход частотного рециркулятора 1. Значения огибающей с выхода всех N каналов частотного рециркулятора 1 в цифровой форме одновременно с частотой Fэ следования элементов сигнала через первый коммутатор 2 подаются в буферный первый блок памяти 3. Числа, снятые в каждый момент отсчета с частотного рециркулятора 1, записываются в один столбец первого блока памяти 3, при этом отсчеты снимаются с отдельного выхода частотного рециркулятора 1, заносятся в одну постоянную строку, характеризуя одну частоту сигнала.

Когда будут заполнены все N столбцов буферного первого блока памяти 3, первый коммутатор 2 импульсной последовательностью Fк = Fэ/N будет приведен в исходное состояние, а из первого блока памяти 3 при помощи первого блока ключей 4 все числа будут перезаписаны во второй блок памяти 5 с тем, чтобы входной сигнал мог обрабатываться в реальном темпе времени. За время Тк = 1/Fк = N τэ двоичные числа из второго блока памяти 5 должны быть обработаны и он должен быть готов для новой загрузки.

Из второго блока памяти 5 двоичные числа используются для предварительного формирования порогов с целью режекции помех для последующего формирования отклика согласованного фильтра. На первом этапе обработки формируются пороги режекции помех. Для этого с выходов второго блока памяти 5 двоичные числа подаются одновременно на первый блок 13 по результатам анализа узкополосных помех Пу, на второй блок 14 - по результатам анализа импульсных помех П и на третий блок 15 - по результатам анализа уровня шумов Пш.

Сущность формирования порога Пу по результатам анализа узкополосных помех заключается в следующем. Поскольку каждая узкополосная помеха влияет на уровень отсчетов в одном или двух смежных фильтров частотного рециркулятора 1 в течение достаточно длительного времени t > > τэ , ее влияние проявится в уровне отсчетов в одной (или двух смежных) строке второго блока памяти 5.

Поэтому для режекции помех порог формируется следующим образом. Вычисляется среднее значение отсчетов Aiср в каждой строке второго блока памяти 5. Из всех средних выбирается N/2 наименьших. При этом считается, что этим самым отобраны строки без узкополосных помех. Эти N/2 наименьших средних усредняются на N/2, берутся с коэффициентом γу1 , учитывающим возможное превышение помехи над сигналом, и по этому предварительному порогу Пу.пр= 2 A

A /N отбраковываются все средние Aiср по строкам - те из них, которые превышают предварительный порог, отбрасываются, а те средние значения, которые меньше предварительного порога, принимаются для формирования порога. Для этого они суммируются, усредняются, т.е. делятся на число средних, не превышающих предварительный порог, берутся с весом γу2 и подаются на вход сумматора, на другой вход которого поступает двоичное число, характеризующее уровень шумов. Выходное число с выхода сумматора и является порогом Пу.

/N отбраковываются все средние Aiср по строкам - те из них, которые превышают предварительный порог, отбрасываются, а те средние значения, которые меньше предварительного порога, принимаются для формирования порога. Для этого они суммируются, усредняются, т.е. делятся на число средних, не превышающих предварительный порог, берутся с весом γу2 и подаются на вход сумматора, на другой вход которого поступает двоичное число, характеризующее уровень шумов. Выходное число с выхода сумматора и является порогом Пу.

Все описанные операции выполняются первым блоком 13 в следующем порядке. Первый коммутатор 17 подключает ячейки i-й строки второго блока памяти 5 к выходам первого сумматора 18, в котором двоичные числа суммируются, усредняются первым делителем 19 на N/2 и через синхронно работающий второй коммутатор 20 среднее по i-й строке значение A =

= Aj/Nподается в i-ю ячейку блока памяти 21. После завершения опроса всех строк второго блока памяти 5 и заполнения ячеек блока 21 третьим коммутатором 22 все средние значения Aiср одновременно подаются на вход блока 23. Блок 23 последовательно выбирают N/2 наименьших средних чисел, которые подаются на вход второго сумматора 24. Сумма N/2 наименьших средних подается на второй делитель 25, с выхода которого через первый умножитель 26 с весом γу1 подается на вход первого регистра 27, выход которого соединен с опорным входом блока 28. Число с выхода первого регистра 27 представляет собой промежуточный порог (взвешенное среднее N/2 средних), который служит для дальнейшей обработки средних из блока 21.

Aj/Nподается в i-ю ячейку блока памяти 21. После завершения опроса всех строк второго блока памяти 5 и заполнения ячеек блока 21 третьим коммутатором 22 все средние значения Aiср одновременно подаются на вход блока 23. Блок 23 последовательно выбирают N/2 наименьших средних чисел, которые подаются на вход второго сумматора 24. Сумма N/2 наименьших средних подается на второй делитель 25, с выхода которого через первый умножитель 26 с весом γу1 подается на вход первого регистра 27, выход которого соединен с опорным входом блока 28. Число с выхода первого регистра 27 представляет собой промежуточный порог (взвешенное среднее N/2 средних), который служит для дальнейшей обработки средних из блока 21.

Когда формирование предварительного порога заканчивается, все средние с выхода блока 21 подключаются на вход блока 28. В блоке 28 происходит режекция, т. е. исключение из обработки при формировании порога Пу тех средних вычисленных по строкам, которые превышают величину предварительного порога. Средние значения, не превышающие его, т.е. характеризующие строки, не пораженные узкополосными помехами, накапливаются в блоке 28, с выхода которого поступают на один вход делителя 29, на установочный вход которого поступает число М, равное числу средних, не превышающих предварительный порог. Частное, не усредненное по М значение, с выхода делителя 29, взятое с весом γу2второго умножителя 30, поступает на вход второго регистра 31, где запоминается и хранится до того времени, когда во втором блоке 15 будет сформирован этот порог. Значения числа с выхода второго регистра 31 и числа с выхода второго блока 15 при этом суммируются в сумматоре 32 и с его выхода как окончательное значение порога Пу подаются на третий регистр 33.

Значения средних Aiсрподаются на входы компараторов 34-1...34-N, на вторые входы которых подается с выхода первого счетчика 35, запоминаемого счетными импульсами, прошедшими через первые и вторые ключи 36 и 37. По мере увеличения числа на счетчике (в исходном состоянии оно было равно 0) на одном из компараторов произойдет превышение этого числа значением Aiср. На выходе того же компаратора произойдет смена потенциала на выходах, которая первым формирователем импульса 38 превратится в относительно кратковременный импульс, который открывает соответствующий третий ключ 39 и число Aiср, подаваемое на сигнальный вход ключа, проходит на выход блока 23. Импульс с первого формирователя 38 через схему ИЛИ-НЕ 40 закрывает первый ключ 36, чтобы прекратить поступление счетных импульсов и исключить практически одновременное срабатывание двух или нескольких компараторов 34. Эти же импульсы через схему ИЛИ 41 заполняют второй счетчик 42 для определения числа сработавших компараторов. Когда это число достигнет N/2, на дешифраторе 43 появится перепад потенциала, который через второй формирователь импульса 44 сбросит показания первого счетчика 35 и второго счетчика 42, переведет триггер 45 в состояние, которое посредством второго ключа 37 прекратит поступление счетных импульсов и прекратит работу блока 23.

Средние по строкам Aiср с третьего компаратора 22 подаются на первые входы компараторов 46 (46-1...46-N), на другие входы которых подается число с выхода первого регистра 27, играющие роль порога. В зависимости от соотношения величины чисел Aiср и порога компаратора 46 установятся в различные состояния. Все одноименные выходы компараторов 46 соединены с первыми управляющими входами первых ключей 47, сигнальные входы которых соединены с входами соответствующих компараторов. На вторые управляющие входы первых ключей 47 подаются стробы с формирователя 48, который запускается счетными импульсами, проходящими через второй ключ 49. На управляющий вход второго ключа 49 подается разрешающий потенциал с триггера 45 блока 23 после окончания вычисления предварительного порога. Стробами с формирователя 48 поочередно опрашиваются первые ключи 47, и там, где числа Aiср не превышают порог и на первых входах первых ключей 47 существует разрешающий потенциал с выхода компаратора, через открывающие ключи числа Aiср проходят для накопления на сумматор 50. Аналогично через третьи ключи 51, управляемые по двум входам, проходят счетные импульсы, задержанные первым элементом задержки 52. Число прошедших через третьи ключи 51 счетных импульсов, определяемое числом находящихся в соответствующем положении компараторов 46, подсчитывается первым счетчиком 53, а общее число счетных импульсов подсчитывается вторым счетчиком 54. Когда все каналы будут опрошены и второй счетчик 54 накопит число Aiср, на выходе дешифратора 55 проявится перепад потенциала, который открывает ключи 57 и 58 для выдачи содержимого сумматора 50 (делимое) и содержимого первого счетчика 53 (делитель), которые поступают на выходы блока 28. Перепад потенциала подается на управление записью второго регистра 31, на третий блок 15, на третий коммутатор 22 и триггер 45 блока 23 для установки их в исходное состояние. С выхода второго элемента задержки 56 период потенциала подается на сброс второго счетчика 54, на считывание с второго регистра 31 и для управления записью на третий регистр 33.

Третий блок 15 работает следующим образом.

Сигнальные входы блоков ключей 59-1...59-N соединены с выходами второго блока памяти 5 так, что на каждый блок ключей 59-i заведены выходы ячеек одной i-й строки матрицы. В состав каждого блока 59 входят N ключей по числу ячеек в строке. На управляющие входы блока ключей 59-i заведены выходы блока 60, управляемые импульсами с выходов первого формирователя 38 блока 23. Управление производится так, что в первой же строке с минимальным средним значением Aiср импульс с первого формирователя 38-i через блок 60, блок ключей 59-i и выходы ячеек I-й строки второго блока памяти 5 подключаются по входам блока 60-i выбора, который работает совершенно аналогично блоку 23. Когда будет выбрано N/2 минимальных чисел из i-й строки второго блока памяти 5, прекращается доступ счетных импульсов, ключи 59-i закрываются, минимальные числа проходят на суммирование в сумматор 61. Когда блок 23 выбирает следующее минимальное среднее в строке, заведомо не пораженной узкополосной помехой, снова передается управление блоку 60 третьего блока 15, открывается следующий блок ключей 59 и еще N/2 минимальных чисел будут накоплены в сумматоре 61. Таким образом из каждой строки с минимальным средним, заведомо не содержащей помех, выбирается по N/2 минимальных чисел, заведомо не содержащих полезного сигнала и характеризующих только уровень шумов на входе СФ. Всего будет накоплено (N/2)2 отсчетов шума, это позволяет сформулировать статистически достоверную оценку уровня шума.

Число из сумматора 61 усредняется делителем 62 и взятое с весом γш в умножителе 63 записывается в первый регистр 64 в качестве порога Пш. Когда в первом и втором блоках 13 и 14 заканчивается формирование чисел и запись их во вторые регистры 31 и 31-1, на входы управления считыванием всех этих регистров (31, 31-1 и 64) поступает сигнал управления. Число с выхода второго регистра 64 подается на входы сумматоров 32 и 32-1, на вторые входы которых поступают соответственно числа с вторых регистров 31 и 31-1. Числа с выхода сумматоров, представляющие собой окончательное значение порогов Пн и Писоответственно, подаются на запись и третьи регистры 33 и 33-1. Этим заканчивается второй этап работы согласованного фильтра - формирование всех трех пороговых значений: порог по результатам анализа узкополосных помех Пу, порог по результатам анализа импульсных помех Пи и порог по результатам анализа уровня шумов Пш.

На следующем этапе производится режекция помех и формирование отклика СФ. Пороги с выхода первого, второго и третьего блоков 13, 14 и 15 подаются на опорные входы порогового блока 7. Вторым коммутатором 6 с ячеек второго блока памяти 5 на вход порогового блока 7 подаются по одиночке числа, характеризующие отсчеты входного сигнала. Эти числа подаются на объединенные сигнальные входы первого, второго и третьего компараторов 68-1, 68-2, 68-3 и на сигнальный вход ключа 69-2. На опорный вход первого компаратора 68-1 подается с первого блока 13 порог Пу, на второй компаратор 68-2 - порог Пш с третьего блока 15, а на третий компаратор 68-3 - порог Пи с второго блока 14. Выходы первого и третьего компараторов (S < П) 68-1 и 68-3 и выход (S > П) второго компаратора 68-2 заведены на входы трехвходовой схемы И 67 в блоке 8, выход которой соединен с управляющим входом второго ключа 69-2, на сигнальный вход которого подается входной сигнал с второго коммутатора 6. Если этот сигнал удовлетворяет перечисленным выше условиям, т.е. превышает порог Пш и, наоборот, не превышает пороги Пу и Пи, он проходит на выход второго блока 9 ключей. Выходы первого и третьего компараторов (S > П) 68-1 и 68-3 и выход (S < П) второго компаратора 68-2 соединены с входами схемы ИЛИ 66, выход которой соединен с управляющим входом первого ключа 69-1, поэтому если сигнал на входе порогового блока 7 удовлетворяет хотя бы одному из этих условий, на выход второго блока ключей 9 проходит двоичное число 0, подаваемое на сигнальный вход первого ключа 69-1. Таким образом, для формирования отклика СФ не используются шумовые отсчеты и режектированные отсчеты, характеризующие помехи в полосе сигнала.

Сигнал с выхода второго блока ключей 9 поступает на вход третьего коммутатора 10, выходы которого соединены с входом N сумматоров-накопителей 11. Третий коммутатор 10 тактируется в N раз медленнее второго коммутатора 6. Входы второго коммутатора 6 соединены с ячейками второго блока памяти 5 в порядке диагоналей, включающих ячейки, номера которых соответствуют порядку следования частот в сигнале с соответствующим циклическим сдвигом номеров ячеек. Поэтому пока второй коммутатор 6 на вход порогового блока 7 подает сигналы с ячеек одной диагонали, третий коммутатор 10 подключен к входу одного из N сумматора-накопителя 11. Затем второй коммутатор 6 начинает опрашивать ячейки другой диагонали, и сигналы из этих N ячеек подаются для накопления в другой из N сумматоров-накопителей 11. N сумматоров-накопителей 11 формируют непосредственно отклик СФ. Когда будут опрошены все N х N ячеек второго блока памяти 5, сформируются суммы во всех N сумматорах-накопителях 11, блок 12 выбирает из этих сумм наибольшую, являющуюся откликом согласованного фильтра.

Работа всех узлов согласованного фильтра синхронизируется управляющими сигналами с выхода блока 16. Колебания с задающего генератора 70 через делитель частоты поступают на формирователь 83, который предназначен для генерирования сетки частот, обеспечивающей работу частотного рециркулятора 1. На выходе формирователя 84 образуется импульсная последовательность, которая поступает на второй и третий делители частоты 72 и 73. С выхода третьего делителя 73 импульсная последовательность поступает на формирователь 74. Стробы с его выхода задают временные режимы узлов согласованного фильтра, определяя время формирования средних Aiср, время формирования порогов Пу, Пи и Пш и время режекции помех и формирования отклика СФ. Стробы управляют работой всех ключей, через которые импульсные последовательности с выхода второго делителя 72 подаются на узлы согласованного фильтра. Требуемые соотношения между частотой импульсов в последовательностях определяются вторым делителем частоты 72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Цифровой согласованный фильтр | 1988 |

|

SU1653174A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Устройство компенсации сигнала дефектов киноленты | 1987 |

|

SU1494247A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Цифровой синтезатор частот | 1984 |

|

SU1188845A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

Использование: в радиотехнике. Сущность изобретения: цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией содержит частотный рециркулятор, первый, второй, третий коммутаторы первый, второй блоки памяти, первый, второй блоки ключей, пороговый блок, блок дешифраторов, N сумматоров-накопителей, блок выбора максимального числа, первый, второй, третий блоки формирования порогов, блок синхронизации. Первый блок формирования порога содержит первый, второй, третий коммутаторы, блок выбора N/2 минимальных чисел, первый, второй сумматоры, первый, второй делители, первый, второй умножители, первый, второй, третий регистры, блок выбора минимальных чисел, делитель с переменным коэффициентом деления, блок памяти, сумматор выбора N/2. Блок минимальных чисел содержит N компараторов, первый, второй счетчики, первые, вторые, третьи ключи, первый, второй формирователи импульса, элемент ИЛИ-НЕ, элемент ИЛИ, дешифратор, триггер. Блок выбора минимальных чисел содержит N компараторов, первые, вторые, третьи ключи, формирователь стробов, сумматор, первый, второй элементы задержки, первый, второй счетчики, дешифратор, четвертый и пятый ключи. Третий блок формирования порогов содержит блок ключей, блок выделения N/2 минимальных чисел, сумматор, делитель, умножитель, первый и второй регистры. Последовательно соединенные пороговый блок, блок дешифраторов и второй блок ключей содержат элемент ИЛИ, элемент И, первый, второй и третий компараторы, первые и вторые ключи. Блок синхронизации содержит задающий генератор, первый, второй, третий делители частоты, формирователь стробов, первые, вторые, ...седьмые ключи, элемент задержки, формирователь опорных частот, формирователь импульсов. Согласованный фильтр за счет анализа сигналов в частотно-временной плоскости в полосе фильтра позволяет формирователь пороги режекции, не зависящие от уровня входных помех, узкополосных и импульсных помех, и повысить помехоустойчивость фильтра. 2 з.п. ф-лы, 7 ил.

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-10-30—Публикация

1990-06-18—Подача