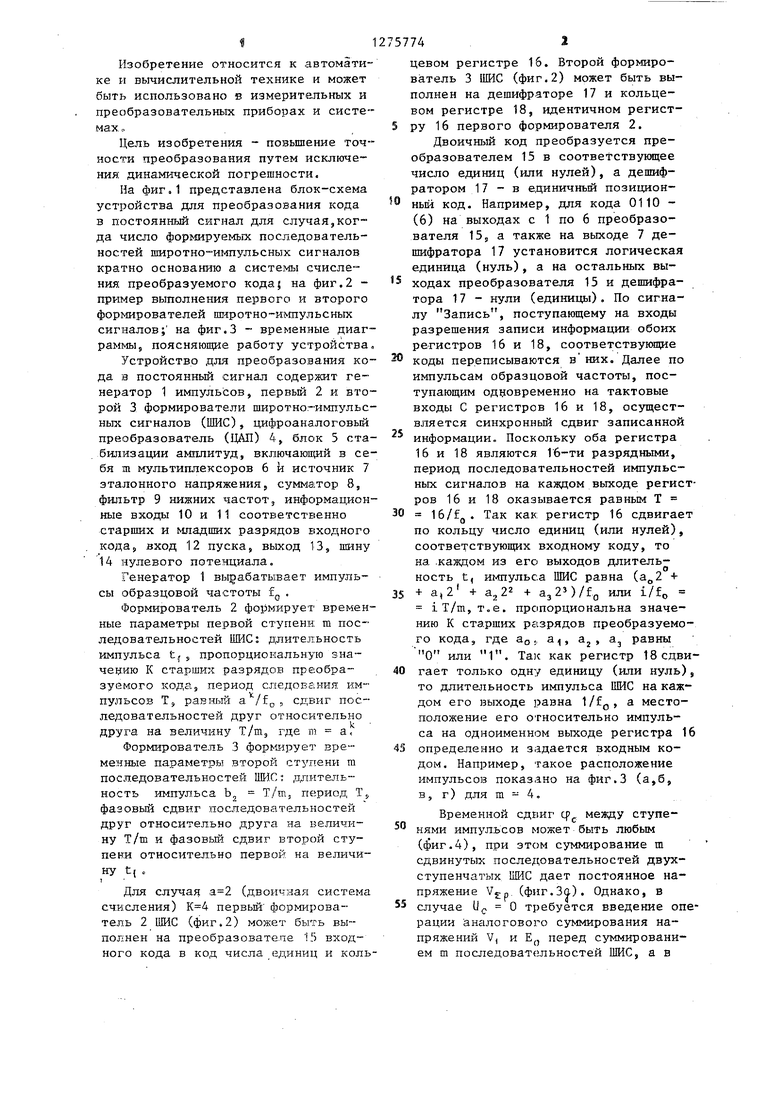

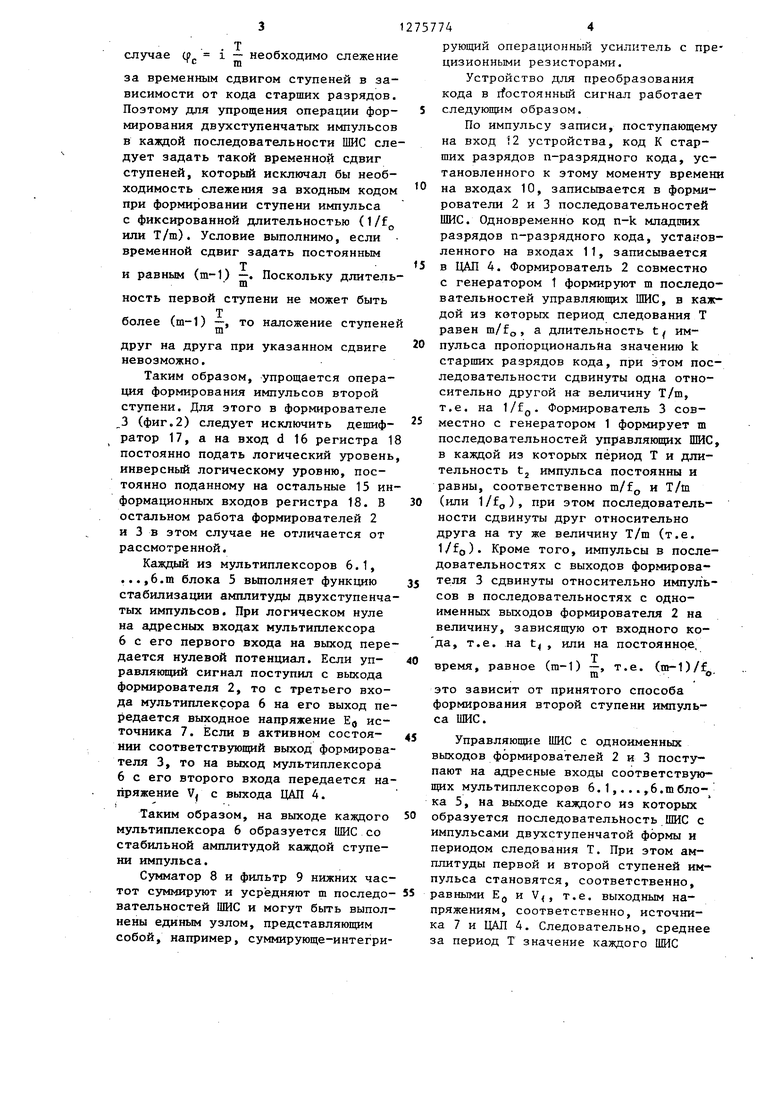

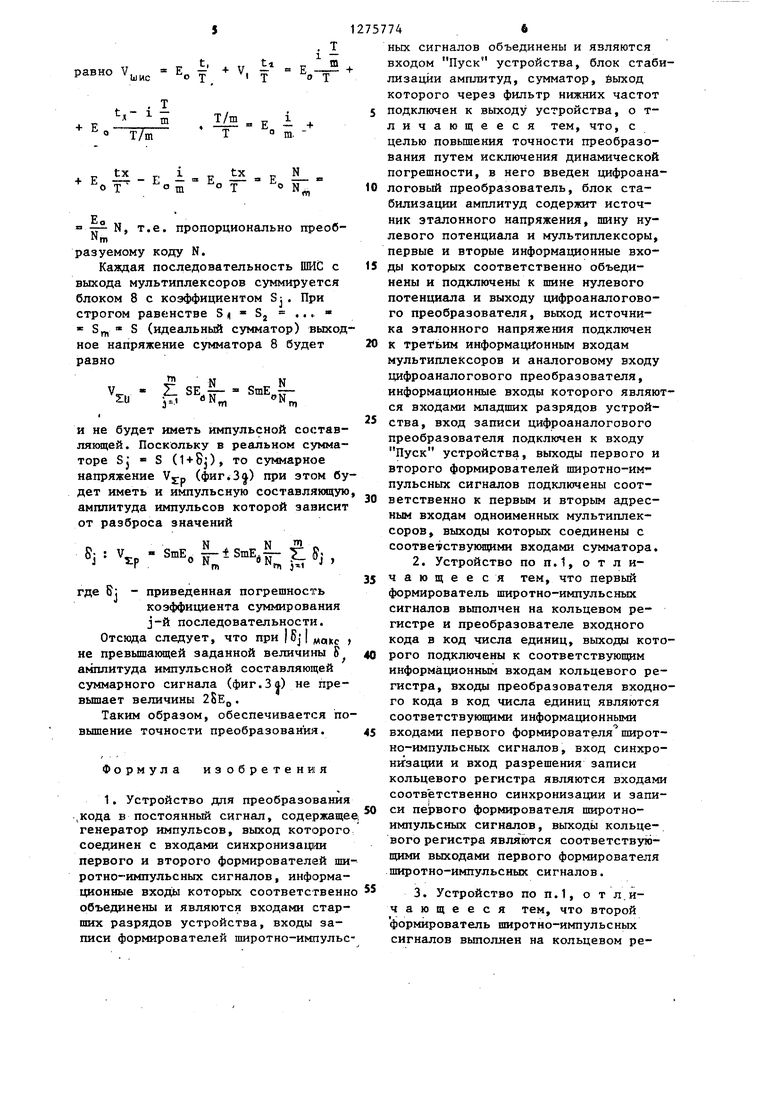

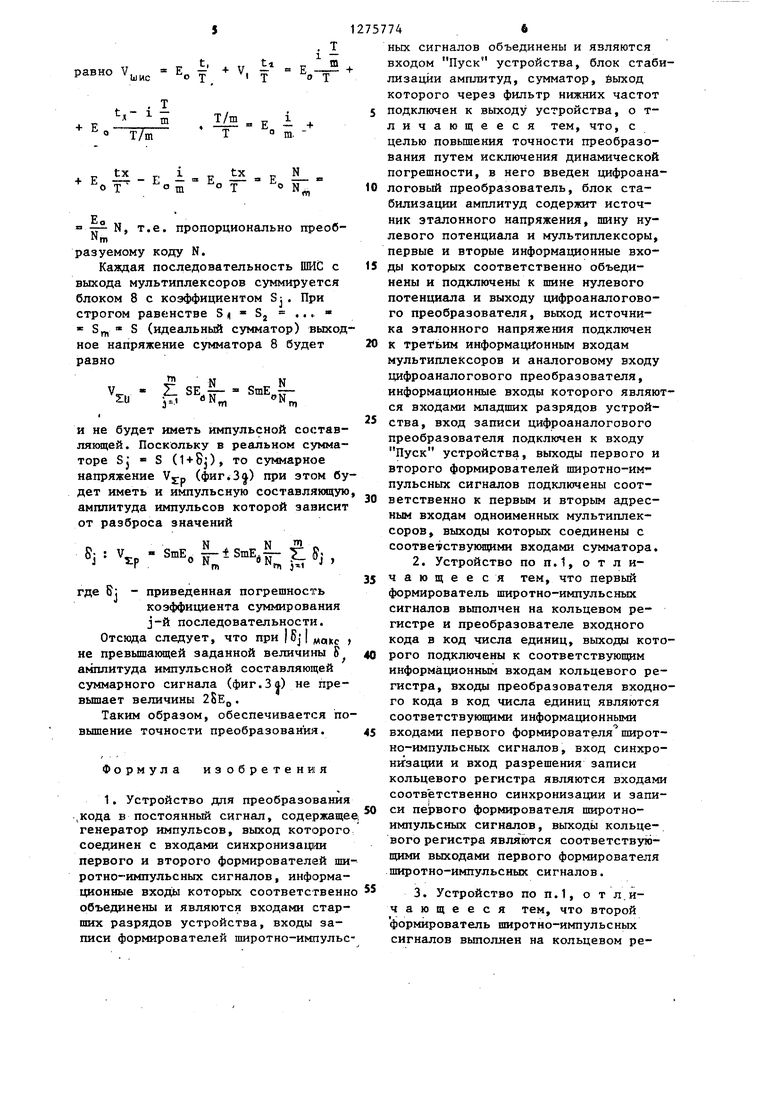

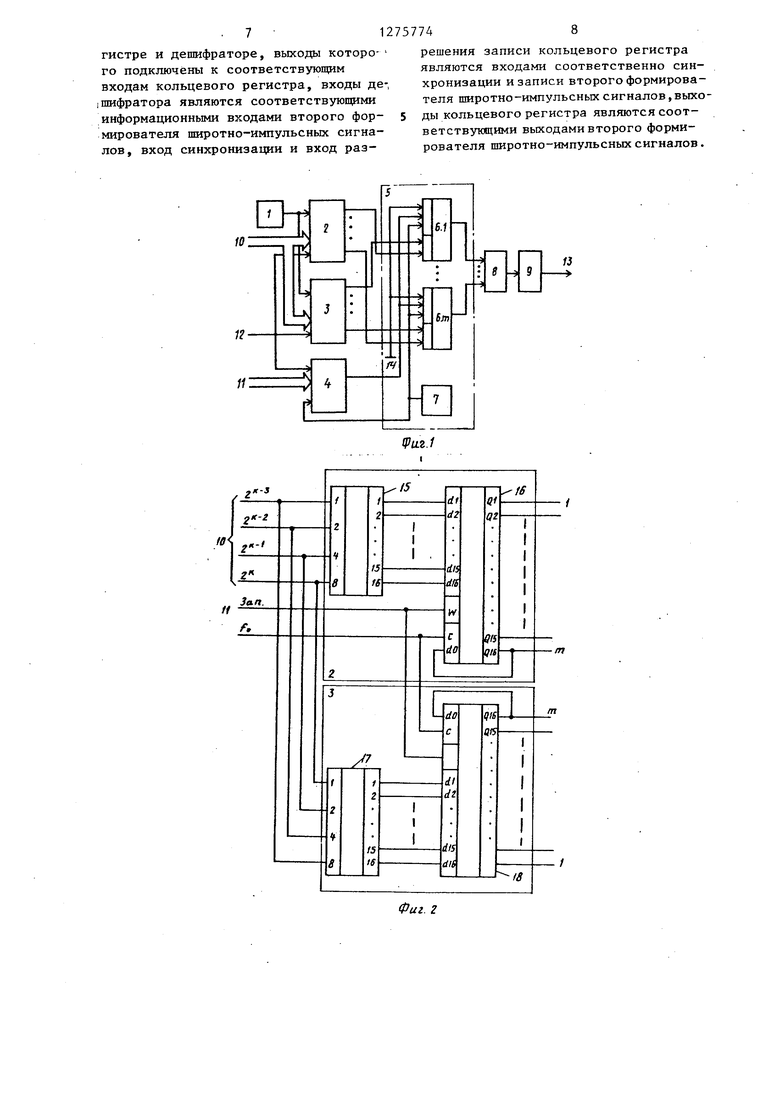

Изобретение относится к автоматике и вычислительной технике и может быть использовано в измерительных и преобразовательных приборах и системах о Цель изобретения - повышение точности преобразования путем исключения динамической погрешности. На фиг,1 представлена блок-схема устройства для преобразования кода в постоянный сигнал для случая,ког да число формируемых последовательностей широтно-импульсных сигналов кратно основанию а системы счисления, преобразуемого кода; на фиг.2 пример выполнения первого и второго формирователей широтно-импульсных сигналов; на фиг.З - временные диаг раммы, поясняющие работу устройства Устройство для преобразования ко да в постоянный сигнал содержит генератор 1 импульсов, первый 2 и вто рой 3 формирователи широтно-импульс ных сигналов (ШИС), цифроана.логовьй преобразователь (1Ш1) 4, блок 5 ста , билизации амплитуд, включаюп1;ий в се бя ш мультиплексоров 6 и источник 7 зталонного напряжения, сумматор 8, фш:ьтр 9 нижних частот, информацион ные входы 10 и 11 соответственно старших и младших разрядов входного кода, вход 12 пуска, выход 13, пшну 14 нулевого потенциала. Генератор 1 вырабатывает импульсы образцовой частоты fg . Формирователь 2 формирует времен ные параметры первой ступени m последовательностей ШИС: длительность импульса tj 5 пропорциональную значевию К старших разрядов преобразуемого кода, период следования импульсов Т, равшзгл , сдвиг последовательностей друг относительно друга на величину Т/т, где m а. Формирователь 3 формирует временные параметры второй стзпени m последовательностей ШИС: длительность импульса Ь, Т/т, период Т., фазовый сдвиг последовательностей друг относительно друга на величину Т/т и фазовый сдвиг второй ступени относительно первой на величину t( . 1 Для случая (двоичная система счисления) первый формирователь 2 ШИС (фиг.2) может быть выполнен на преобразователе 15 входного кода в код числа единиц и коль 74 . 2 цевом регистре 16, Второй формирователь 3 ШИС (фиг.2) может быть выполнен на дешифраторе 17 и кольцевом регистре 18, идентичном регистру 16 первого формирователя 2. Двоичш 1й код преобразуется преобразователем 15 в соответствукицее число единиц (или нулей), а дешифратором 17 - в единичный позиционный код. Например, для кода 0110 (6) на выходах с 1 по 6 преобразователя 15, а также на выходе 7 дешифратора 17 установится логическая единица (нуль), а на остальных выходах преобразователя 15 и дешифратора 17 - нули (единицы). По сигналу Запись, поступающему на входы разрешения записи информации обоих регистров 16 и 18, соответствующие коды переписываются в них. Далее по импульсам образцовой частоты, поступающим одновременно на тактовые входы С регистров 16 и 18, осуществляется синхронный сдвиг записанной информации. Поскольку оба регистра 16 и 18 являются 16-ти разрядными, период последовательностей импульсных сигналов на каждом выходе регистров 16 и 18 оказывается равным Т 16/fg. Так как регистр 16 сдвигает по кольцу число единиц (или нулей), соответствующих входному коду, то на .каждом из его выходов длительность t, импульса ШИС равна (а„2 + + а,2 + а,,22 + или i/f il/m, т.е. пропорциональна значению К старших разрядов преобразуемого кода, где ад., а, а,,, а равны О или 1. Та)с как регистр 18сдвигает только одну единицу (или нуль), то длительность импульса ШИС на каждом его выходе равна l/f, а местоположение его относительно импульса на одноименном выходе регистра 16 определенно и задается входным кодом. Например, такое расположение импульсов показано на фнг.З (а,б, в, г) для m - 4. Временной сдвиг ср между ступенями импульсов может быть любым (.4), при зтом суммирование m сдвинутых последовательностей двухступенчатых ШИС дает постоянное напряжение Vj-p. (фиг.За). Однако, в случае U,., О требуется введение операции аналогового суммирования напряжений V, и Е(, перед суммированием m последоват(шьностей ШИС, а в (р„ i - необходимо слежение случае С m за временным сдвигом ступеней в висимости от кода старших разрядов. Поэтому для упрощения операции формирования двухступенчатых импульсов в каждой последовательности ШИС сле дует задать такой временной сдвиг ступеней, который исключал бы необходимость слежения за входным кодом при формировании ступени импульса с фиксированной длительностью (1/f или Т/т). Условие выполнимо, если временной сдвиг задать постоянным равным (т-1) -. Поскольку длитель m ность первой ступени не может быть более (т-1) -, то наложение ступене друг на друга при указанном сдвиге невозможно. Таким образом, упрощается операция формирования импульсов второй ступени. Для этого в формирователе 3 (фиг.2) следует исключить дешифратор 17, а на вход d 16 регистра 1 постоянно подать логический уровень инверсный логическому уровню, постоянно поданному на остальные 15 ин формационных входов регистра 18. В остальном работа формирователей 2 и 3 в этом случае не отличается от рассмотренной. Каждый из мультиплексоров 6.1, ...,6.т блока 5 выполняет функцию стабилизации амплитуды двухступенча тых импульсов. При логическом нуле на адресных входах мультиплексора 6 с его первого входа на выход пере дается нулевой потенциал. Если управляющий сигнал поступил с выхода формирователя 2, то с третьего входа мультиплексора 6 на его выход пе редается выходное напряжение Е источника 7. Если в активном состоянии соответствующий выход формирова теля 3, то на выход мультиплексора 6 с его второго входа передается на Г1ряжение Vj с выхода ЦАП 4. t Таким образом, на выходе каждого мультиплексора 6 образуется ШИС со стабильной амплитудой каждой ступени импульса. Сумматор 8 и фильтр 9 нижних час тот суммируют и усредняют m последо вательностей ШИС и могут быть выпол нены единым узлом, представляющим собой, например, суммирующе-интегри за744рующий операционньш усилитель с прецизионными резисторами. Устройство для преобразования кода в г остоянный сигнал работает следующим образом. По импульсу записи, поступающему на вход 12 устройства, код К старших разрядов п-разрядного кода, установленного к этому моменту времени на входах 10, записывается в формирователи 2 и 3 последовательностей ШИС. Одновременно код n-k младших разрядов п-разрядного кода, уста1 овленного на входах 11, записывается в ЦАП 4. Формирователь 2 совместно с генератором 1 формируют m последовательностей управляющих ШИС, в каждой из которых период следования Т равен m/fo, а длительность t импульса пропорциональна значению k старших разрядов кода, при этом последовательности сдвинуты одна относительно другой на- величину Т/т, т.е. на l/fg. Формирователь 3 совместно с генератором 1 формирует m последовательностей управляющих ШИС, в каждой из которых период Т и длительность tj импульса постоянны и равны, соответственно m/f и Т/ш (или l/fg), при этом последовательности сдвинуты друг относительно друга на ту же величину Т/ш (т.е. l/fg). Кроме того, импульсы в последовательностях с выходов формирователя 3 сдвинуты относительно импульсов в последовательностях с одноименных выходов формирователя 2 на величину, зависящую от входного кода, т.е. на t , или на постоянное, (т-1) I т.е. (т-1)/ время, равное это зависит от принятого способа формирования второй ступени импульса ШИС. Управляющие ШИС с одноименных выходов формирователей 2 и 3 поступают на адресные входы соответствуюих мультиплексоров 6. 1,. .. ,6.тблока 5, на выходе каждого из которых образуется последовательность ШИС с импульсами двухступенчатой формы и периодом следования Т. При этом амплитуды первой и второй ступеней импульса становятся, соответственно, авными Eg и V(, т.е. выходным напряжениям, соответственно, источниа 7 и ЦАП 4. Следовательно, среднее за период Т значение каждого ШИС Е -t- V. равно V т.е. пропорционально преобразуемому коду N. Каждая последовательность ШИС с выхода мультиплексоров суммируется блоком 8 с коэффициентом S:. При строгом равенстве S к - S ..„ S « S (идеальный сумматор) выход ное напряжение сумматора 8 будет равно и не будет иметь импульсной составлякицей. Поскольку в реальном сумматоре Sj « S (1 + 8р, то суммарное напряжение Vj-p () при этом бу дет иметь и импульсную составляющую амплитуда импульсов которой зависит от разброса значений IS;, 5j р где Bj приведенная погрешность коэффициента суммирования j-й последовательности. Отсюда следует, что пpи|fij,ane не превышающей заданной величины S амплитуда импульсной составляющей суммарного сигнала (фиг.За) не превышает величины 28Е(,. Таким образом, обеспечивается по вышение точности преобразования. Формула изобретения 1. Устройство для преобразовани кода в постоянный сигнал, содержащ генератор импульсов, выход которог соединен с входами синхронизации первого и второго формирователей ши ротно-импульсных сигналов, информа ционные входы которых соответствен объединены и являются входами стар ших разрядов устройства, входы записи формирователей широтно-импуль 746 ных сигналов объединены и являются входом Пуск устройства, блок стабилизации амплитуд, сумматор, йыход которого через фильтр нижних частот подключен к выходу устройства, о тличающееся тем, что, с целью повьш1ения точности преобразования путем исключения динамической погрешности, в него введен цифроаналоговый преобразователь, блок стабилизации амплитуд содержит источник эталонного напряжения, шику нулевого потенциала и мультиплексоры, первые и вторые информационные входы которых соответственно объединены и подключены к шине нулевого потенциала и выходу цифроаналогового преобразователя, выход источника эталонного напряжения подключен к третьим информационным входам мультиплексоров и аналоговому входу цифроаналогового преобразователя, информационные входы которого являются входами мпадших разрядов устройства, вход записи цифроаналогового преобразователя подключен к входу Пуск устройства, выходы первого и второго формирователей широтно-импульсных сигналов подключены соответственно к первым и вторым адресным входам одноименных мультиплексоров, выходы которых соединены с соответствующими входами сумматора. 2. Устройство по П.1, о т л ичающееся тем, что первый формирователь широтно-импульсных сигналов выполнен на кольцевом регистре и преобразователе входного кода в код числа единиц, выходы которого подключены к соответствуюшрм информационным входам кольцевого регистра, входы преобразователя входного кода в код числа единиц являются соответствующими информационными входами первого формирователя широтно-импульсных сигналов, вход синхронизации и вход разрешения записи кольцевого регистра являются входами соответственно синхронизации и записи первого формирователя широтноимпульсных сигналов, выходы кольцевого регистра являются соответствующими выходами первого формирователя широтно-импульсных сигналов. 3. Устройство по П.1, о т л.ичающееся тем, что второй формирователь широтно-импульсных сигналов выполнен на кольцевом ре. 7 1 гистре и дешифраторе, выходы которого подключены к соответствующим входам кольцевого регистра, входы де ,шифратора являются соответствующими информационными входами второго фор мирователя широтно-импульсных сигналов, вход синхронизации и вход раз74решения записи кольцевого регистра являются входами соответственно синхронизации и записи второго формирователя широтно-импульсных сигналов, выходы кольцевого регистра являются соответствующими выходами второго формирователя широтно-импульсных сигналов.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования кода в постоянный сигнал | 1985 |

|

SU1270896A2 |

| Способ преобразования кода в постоянный сигнал | 1981 |

|

SU1005296A2 |

| Способ преобразования кода в постоянный сигнал | 1979 |

|

SU940294A1 |

| Способ преобразования кода в постоянный сигнал и устройство для его осуществления | 1987 |

|

SU1547068A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1642585A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Способ преобразования кода в постоянныйСигНАл | 1979 |

|

SU836791A1 |

| Способ преобразования кода в постоянный сигнал | 1985 |

|

SU1275773A2 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в измерительных и преобразовательных приборах обеспечивает повышение точности преобразования. Устройство содержит генератор импульсов, два формирователя широтно-импульсных сигналов, блок стабилизации амплитуд, .сумматор и фильтр нижних частот. Введение цифроаналогового преобразователя и выполнение блока стабилизации амплитуд на мультиплексорах и источнике эталонного напряжения позволяет уменьшить погрешность преобразования. о S 2 э.п. ф-лы, 3 ил.

| Способ преобразования кода в постоянныйСигНАл | 1979 |

|

SU836791A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-07—Публикация

1985-03-11—Подача