Изобретение относится к электроизмерительной технике и предназначено для использованиявсоставе

информационно-измерительной системы контроля параметров электроэнергии промышленной сети.

Известен преобразователь активной мощности в цифровой код, содержащий калиброванный резистор, фиксатор уровня, источник опорного напряжения, аналоговый коммутатор, преобразователь напряжения в код, шесть регистров, сумматор, умножитель, два постоянных запоминающих устройства, формирователь импульсов, генератор опорной частоты, два счетчика, элемент задержки, элемент И и формирователь управляющих сигналов 1.

Не,цостатком известного устройства является низкая точность преобразования.

Наиболее близким по технической сущности к предлагаемому изобретению является преобразователь активной мощности в цифровой код, содержащий калиброванный резистор, фиксатор уровня, источник опорного напряжения, первый и второй аналоговые коммутаторы, первый и второй преобразователи напряжения в код, регистры, сумматор, умножитель, постоянные запоминающие устройства, формирователь импульсов, генератор опорной частоты, счетчики, элемент задержки, элемент И, формирователь управляющих сигналов, делитель напряжения, мультиплексор, многовходовый элемент ИЛИ-НЕ, первый и второй элементы И 2.

В реальной промышленной сети по причинам всевозможных коммутационных переключений, срабатывания средств автоматики, нелинейного характера и резких колебаний нагрузки у потребителя электроэнергии и т.д, имеют место импульсные помехи, искажающие синусоидальную форму электрического сигнала с многократным превышением его амплитуды и широким диапазоном изменения длительности импульсных искажений.

Кроме того, благодаря перечисленным выше коммутационным явлениям, нелинейному и комплексному характеру нагрузки Р(1И) p(lii) { ТЖГ иначе О , - Mi-iaui где Jii и Г|2 математические ожидания ii и Ii2. При равных равномерных распределениях абсолютных случайных составляющих погрешностей фиксатора уровня и преобрапотребителя электроэнергии, а также за счет ярко выраженных паразитных частотных свойств электросети (индуктивности, взаимоиндуктивности и емкости фазных и линейных подключений, т.п.) наблюдается широкий спектр гармоник, от первой (50 Гц) до сотой, в сети, что приводит к искажению формы сигнала (треугольная, колоколообразная), особенно в случае переходных процессов, например режим пусковых токов.

При этом за время до нескольких секунд уровень напряжения или тока в сети может в несколько раз превышать соответствующий уровень в нормальном установившемся режиме, до которого возвращается напряжение или ток по завершении переходного процесса.

Для работы с данным измеряемым сигналом прототип содержит два преобразователя напряжения в код.

Первый из них осуществляет обработку входного сигнала при масштабе, не превышающем амплитуду номинального значения синусоидальной или несинусоидальной формы, а второй - при превышении данной амплитуды.

Исходя из этих соображений схема прототипа содержит два примерно идентичных канала измерений входного сигнала: аналоговые коммутаторы, преобразователи напряжения в код, делитель напряжения.

Точность преобразования активной мощности в код в схеме прототипа определяется, в основном, метрологическими параметрами фиксатора уровня, а также преобразователей напряжения в код, т.е. их быстродействием и точностью, так как согласно теореме Котельникова,чем выше частота дискретизации, тем точнее можно преобразовать входной сигнал со значительными искажениями, используя метод цифровой обработки мгновенных значений для измерения активной мощности.

При равномерном распределении абсолютной случайной погрешности преобразователей в пределах ±Ai2i и ±Ai22 коды NI-II и Ni2i соответствуют значениям входного тока (1и ± Ai2i) и (Ii2 ± Д122) с плотностями распределения вероятностей если 111 если III i2i iii Ih -Г Д121 , (1) |21 iii 1и +AI21 ,(2) зователей на соответствующих уровнях входных напряжений в пределах ± Au2i и ±Ди22 композицией этих распределений в обоих случаях является распределение Симпеона в пределах ± 2 Ди21 и ± 2 А U22 соответственно. Таким образом, коды Null соответствуют значениям вход2 Au2l-Uii +uii 4 Au2i Цц +2 Au2i - UH P(uii) 4 AlJ21 иначе 0 , 2 Au22 Ui2 + ui2 4 A U22 U|2+2AU22-U,2 p(ui2). 4 Au22 иначе 0, где Uii и Ui2 - математические ожидания uii и ui2 соответственно. Математическое ожидание произведения мгновенных значений тока и напряжения UI1 ill в Н-й точке их выборки и его дисперсия при независимости их преобразований с помощью преобразователя, т.е. когда входной сигнал не превышает масштаб последнего: , Uii +2Au21 III +2Al21 M UMili //.X U|i-2Au21 tli-2Al21 xuii IH P ( uii ) p (til ) d uii d iii Uii 111 1 (5) U|i+2Au21 Ili+2Al21 D uiilii .X Uli-2Au21 Iii-2Ai21 X ( UH 111 - M UH IH ) 2 p ( UH ) p ( ili ) X X d UH d IH I (UiH A I2i H IH A U21 + + |AI21 AU21). В случае превышения входным сигналом масштаба первого преобразователя работает второй преобразователь. При этом, аналогично рассуждая, получим математическое ожидание и дисперсию. М ut2 Ii21 Ui2 Ii2;(7) ( XAU22 +|AJ22 AU22 J Суммарная дисперсия результата преобразования входных тока и напряжения, с целью вычисления активной мощности за период Тх Dr Тх2{Е D{uii 2 .. (9) Н 112 1 гдеТх-Сп+т) АТх. Следовательно, суммарное среднеквадратическое значение atz случайных со, если если , если НОГО напряжения (Уц ±2Au22) и (Ui2 ± 2 Au22) с плотностями распределения вероятностей:Uii -2 Au2i Uii , ii uii : UH -t- 2 Au2i Ul2 - 2 AU22 , , , y, -b 2 AU22 , ставляющих погрешностей прототипа определяется выражением а. /|АТх/u(t)l(t)dt Е (Л1 Дl2t -t„A 1) + f;(Цг и 1ч I /u(.)P(Od, пренебрегая влиянием произведений Au2ix Ai2i и Au22 Al22 ввиду их малости. Случайная составляющая погрешности, характеризующаяся тем, что вероятность совпадения Au2i Au22 и Ai2i Al22 для двух однотипных преобразователей весьма низка, практически невозможна. Эта разница определяется технологическим разбросом, старением элементов, т.п., что объясняется сложной внутренней структурой АЦП, используемых как преобразователи. Эти различия приводят к тому, что случайные погрешности преобразователей изменяются неодинаково. Таким образом, недостатком прототипа является то, что в переходных режимах и при коммутационных явлениях в промышленной сети общая погрешность преобразования активной мощности в код возрастает за счет различных интервалов изменения случайных погрешностей преобразователей, что выражается в различии пр15делов AU21 и AU22, Al21 И Ai22. Кроме этого, наличие разброса параметров преобразователей вызывает аддитивную составляющую погрешности преобразования: ДТхЕ ()(uj+Au2)-u}lj. гJ 1 5дд2 ijTjTf; - /u(t)l(t)dt

где Д12 и Au2 - различие аддитивных погрешностей преобразователей, причем принята для первого из них аддитивная погрешность равной нулю.

После несложных преобразователей (11) получим:

д Urm Ai2 +Irm А U2/.o

Д U™Ucos o

считая, что отклонение входного сигнала от масштаба преобразователя 5 содержит m точек дискретизации на период, проявляется только в одной полуволна периода Тх, а средние значения за это время напряжения и тока равны Urm и Irm, причем о сдвиг фаз между ними,

Таким образом, недостатком прототипа является низкая точность преобразования активной моа ности сигналов переходных процессов и импульсных отклонений в промышленной электросети.

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь активной мощности в цифровой код, содержащий первый калиброванный резистор, фиксатор уровня, источник опорного напряжения, первый и второй аналоговые коммутаторы, преобразователь напряжения в код, шесть регистров, сумматор, умножитель, первый и второй постоянные запоминающие блоки, формирователь импульсов, генератор опорной частоты, первый и второй счетчики, элемент задержки, элемент И, формирователь управляющих сигналов, мультиплексор и делитель напряжения, причем вход фиксатора уровня соединен со входной шиной напряжения, первый вывод первого калиброванного резистора соединен со входной шиной тока, входом формирователя импульсов и первыми входами аналоговых коммутаторов, выход первого аналогового коммутатора подключен к информационному входу преобразователя напряжения в код, первый выход источника опорного напряжения подключен ко второму входу первого аналогового коммутатора, выход фиксатора уровня соединен с третьим входом первого и вторым входом второго аналогового коммутаторов, выход мультиплексора подключен к входу первого регистра, первый выход первого регистра через элемент И подключен ко входам выбора ремчима и переноса первого канала сумматора, а вторые выходы - ко вторым входам первого канала сумматора, первый вход первого канала сумматора соединен с земляной шиной, а выходы - со входами третьего регистра, выходы старших разрядов сумматора соединены также со входами второго регистра и входами второго канала умножителя, подключенными также к выходам четвертого регистра, входы первого.канала умножителя соединены с выходами второго регистра и постоянных запоминающих блоков, а выходы - со входами четвертого, пятого регистров и входами третьего канала сумматора, входы второго канала которого подключены к выходам третьего регистра, выход генератора опорной частоты соединен со входом синхронизации формирователя импульсов, входом записи первого регистра и входом первого счетчика, выходы

разрядов которого подключены ко входам

шестого регистра, а вход сброса в нуль ко входу второго счетчика и через элемент

задержки ко входу записи шестого регистра

и выходу формирователя импульсов, входы

первого и второго постоянных запоминающих блоков подключены, соответственно, к выходам пятого и шестого регистров, первый вход формирователя управляющих сигналов соединен с выходом генератора

опорной частоты, выходы первого и второго счетчиков подключены к первой и второй группам входов формирователя управляющих сигналов, выходная шина управления которого подключена к входу управлений

первого аналогового коммутатора, входу управления второго аналогового коммутатора, входу управления фиксатора уровня, тактовому входу преобразователя напряжения в код, первому входу элемента И, входам записи второго, третьего, четвертого, пятого регистров и умножителя, входам разрешения считывания второго и четвертого регистрое, входам управления сумматора и постоянных Запоминающих блоков, входам

сброса третьего и пятого регистров, входам выбора каналов сумматора, а также входам управления регистром произведения умножителя, кроме того, вь1ходы мультиплексора подключены ко входам первого регистра,

введены первый и второй компараторы, элемент ИЛИ и второй калиброванный резистор, причем первые входы компараторов соединены с выходом второго аналогового коммутатора, а их вторые входы - с соответствующими выходами источника опорного напряжения, выходы компараторов подключены ко входам элемента ИЛИ, выход которого соединен с адресным зхор,оы мультиплексора и вторым управляющим

входом первого аналогового коммутатора, третий и четвертый управляющие входы которого подключены к соответствующим выводам выходной шины формирователя управляющих сигналов, кроме того, управляющие входы компараторов подключены к

управляющему входу преобразователя напряжения в код, а второй вывод первого калиброванного резистора подключен через второй калиброванный резистор к земляной шине и к четвертому входу первого аналогового коммутатора, пятый вход которого соединен с выходом делителя напряжения, выход фиксатора уровня подключен ко входу делителя напряжения, выход преобразователя напряжения в код соединен со старшими разрядами первых входов и младшими разрядами вторых входов мультиплексора, а его младшие разряды первых входов и старшие разряды вторых подключены к земляной шине.

Выявленные по сравнению с прототипом новые элементы известны из различных источников информации. Так,в частном случае реализации первый и второй компараторы построены на 597СА2 (бКо. 347.190 ТУ).

В качестве элемента ИЛИ использована микросхема К555ЛЛ1 (Б.Ко.348.289 ТУ5).

Решений с подобным сочетанием известных элементов не обнаружено.

Существенность отличий решения заключается в том, что полученная новая взаимосвязь известных элементов заявляемого преобразователя позволила повысить точность преобразования в 2 раза. Это, в свою очередь, приводит к экономии электроэнергии за счет более точного учета расходуемой электроэнергии при использовании предлагаемого преобразователя активной мощности в цифровой код. Таким образом, решение обладает новизной и соответствует критерию существенные отличия.

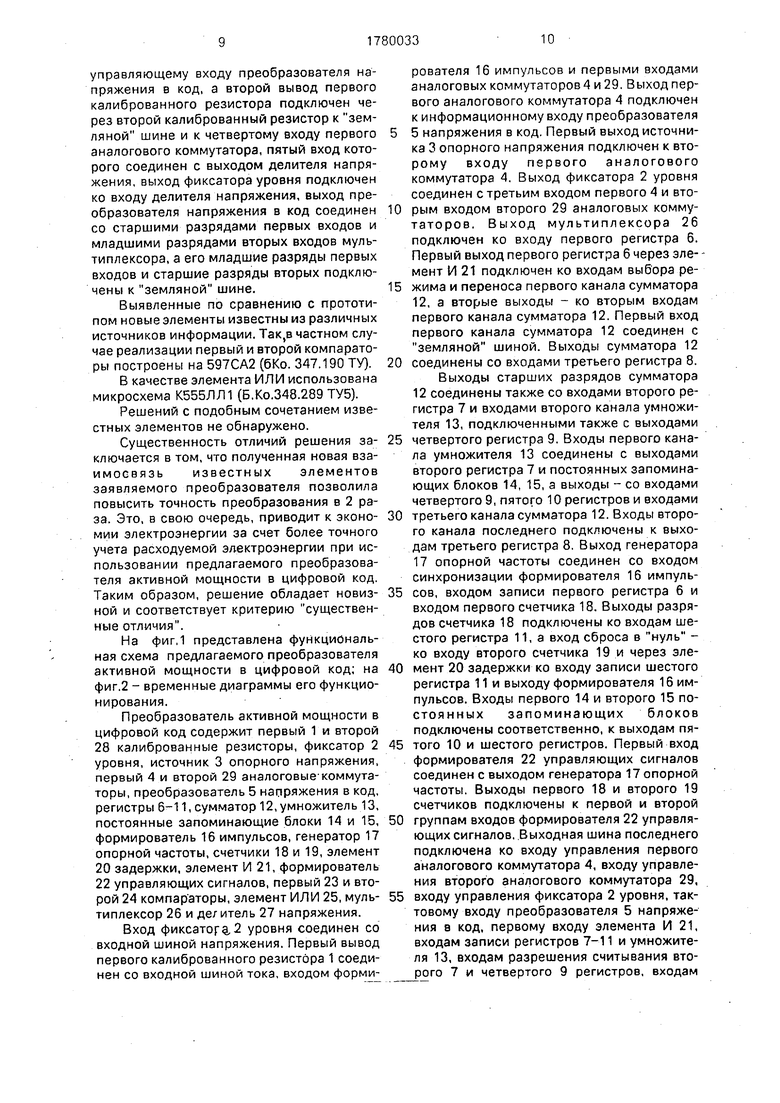

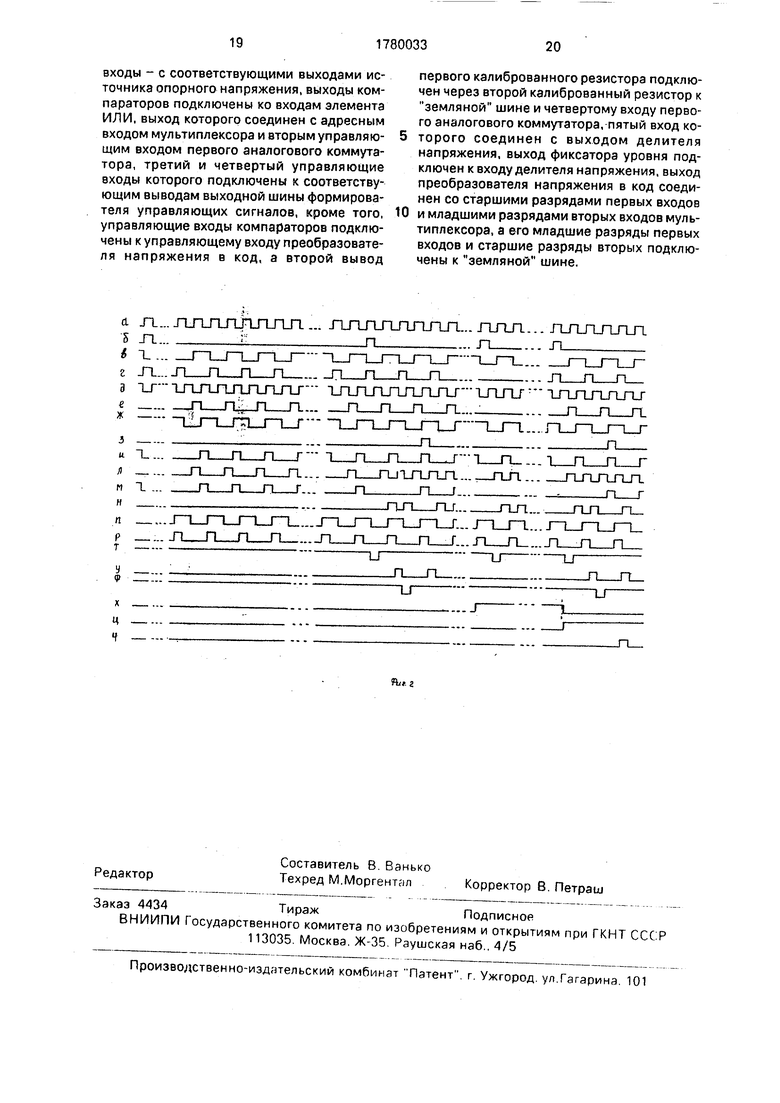

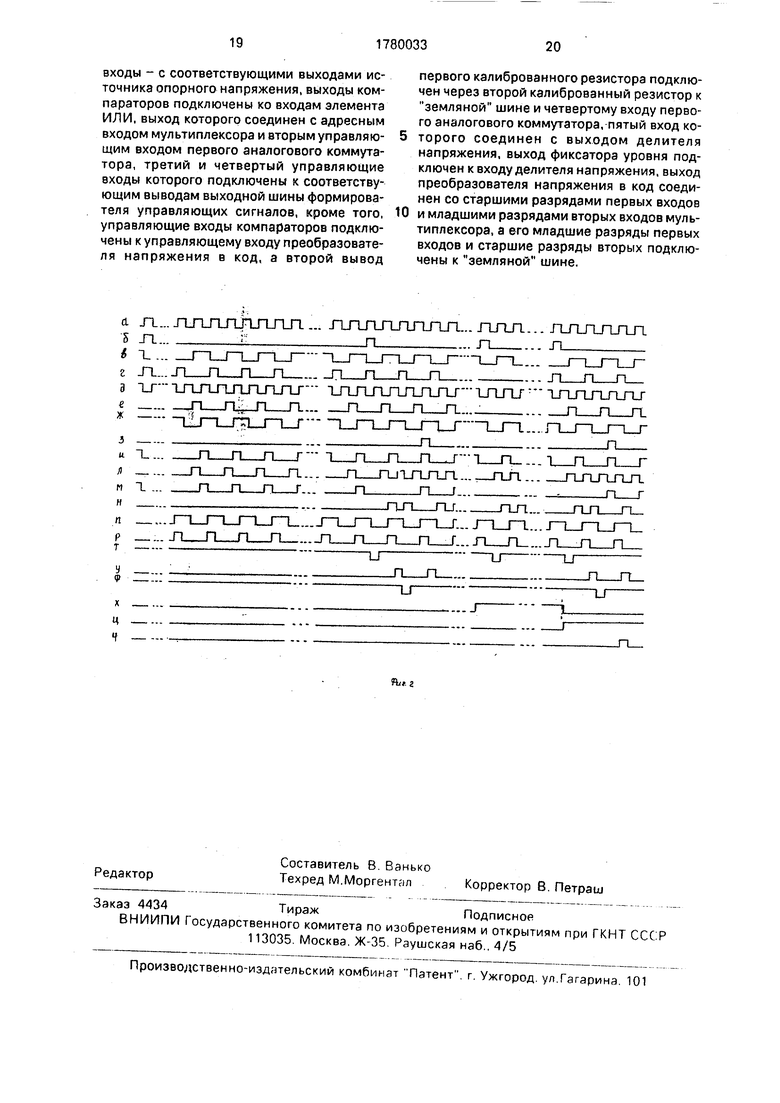

На фиг,1 представлена функциональная схема предлагаемого преобразователя активной мощности в цифровой код; на фиг.2 - временные диаграммы его функционирования.

Преобразователь активной мощности в цифровой код содержит первый 1 и второй 28 калиброванные резисторы, фиксатор 2 уровня, источник 3 опорного напряжения, первый 4 и второй 29 аналоговые-коммутаторы, преобразователь 5 напряжения в код, регистры 6-11, сумматор 12, умножитель 13, постоянные запоминающие блоки 14 и 15, формирователь 16 импульсов, генератор 17 опорной частоты, счетчики 18 и 19, элемент 20 задержки, элемент И 21, формирователь 22 управляющих сигналов, первый 23 и второй 24 компараторы, элемент ИЛИ 25, мультиплексор 26 и де/ итель 27 напряжения.

Вход фиксатог 2 уровня соединен со входной шиной напряжения. Первый вывод первого калиброванного резистора 1 соединен со входной шиной тока, входом формирователя 16 импульсов и первыми входами аналоговых коммутаторов4 и 29. Выход первого аналогового коммутатора 4 подключен к информационному входу преобразователя 5 5 напряжения в код. Первый выход источника 3 опорного напряжения подключен к второму входу первого аналогового коммутатора 4. Выход фиксатора 2 уровня соединен с третьим входом первого 4 и вто0 рым входом второго 29 аналоговых коммутаторов. Выход мультиплексора 26 подключен ко входу первого регистра 6. Первый выход первого регистра 6 через эле- мент И 21 подключен ко входам выбора режима и переноса первого канала сумматора 12, а вторые выходы - ко вторым входам первого канала сумматора 12. Первый вход первого канала сумматора 12 соединен с земляной шиной. Выходы сумматора 12

0 соединены со входами третьего регистра 8. Выходы старших разрядов сумматора 12 соединены также со входами второго регистра 7 и входами второго канала умножителя 13, подключенными также с выходами

5 четвертого регистра 9. Входы первого канала умножителя 13 соединены с выходами второго регистра 7 и постоянных запоминающих блоков 14, 15, а выходы - со входами четвертого 9, пятого 10 регистров и входами

0 третьего канала сумматора 12. Входы второго канала последнего подключены к выходам третьего регистра 8. Выход генератора 17 опорной частоты соединен со входом синхронизации формирователя 16 импульсов, входом записи первого регистра 6 и входом первого счетчика 18. Выходы разрядов счетчика 18 подключены ко входам шестого регистра 11, а вход сброса в нуль ко входу второго счетчика 19 и через элемент 20 задержки ко входу записи шестого регистра 11 и выходу формирователя 16 импульсов. Входы первого 14 и второго 15 постоянных запоминающих блоков подключены соответственно, к выходам пятого 10 и шестого регистров. Первый вход формирователя 22 управляющих сигналов соединен с выходом генератора 17 опорной частоты. Выходы первого 18 и второго 19 счетчиков подключены к первой и второй

0 группам входов формирователя 22 управляющих сигналов. .Выходная шина последнего подключена ко входу управления первого аналогового коммутатора 4, входу управления второго аналогового коммутатора 29.

5 входу управления фиксатора 2 уровня, тактовому входу преобразователя 5 напряжения в код, первому входу элемента И 21, входам записи регистров 7-11 и умножителя 13, входам разрешения считывания второго 7 и четвертого 9 регистров, входам

управления сумматора 12 и постоянных запоминающих блоков - 14, 15, входам сброса третьего 8 и пятого 10 регистров, входам выбора каналов сумматора 12, а также входам управления регистром произведения умножителя 13.

Первые входы компараторов 23 и 24 соединены с выходом второго аналогового коммутатора 29, а их вторые входы - с соответствующими выходами источника 3 опорного напряжения. Выходы компараторов 23 и 24 подключены ко входам элемента ИЛИ 25, выход которого соединен с адресным входом мультиплексора 26 и вторым управляющим входом первого аналогового коммутатора 4. Третий и четвертый управляющие входы последнего подключены к соответствующим выводам выходной шины формирователя 22 управляющих сигналов. Управляющие входы компараторов 23, 24 подключены к упаравляющему входу преобразователя 5 напряжения в код.

Второй вывод первого калиброванного резистора 1 подключен через второй калиброванный резистор 28 к земляной шине и к четвертому входу первого аналоговго коммутатора 4, пятый вход которого соединен с выходом делителя 27 напряжения. Выход фиксатора 2 уровня подключен ко входу делителя 27 напряжения. Выход преобразователя 5 напряжения в код соединен со старшими разрядами первых входов и младшими разрядами вторых входов мультиплексора 26, а его младшие разряды первых входов и старшие разряды вторых входов подключены к земляной шине.

В конкретном реализованном преобразователе фиксатор 2 уровня построен по схеме, приведенной в книге Воробьев Н.В., Вернер В.Д. Элементная база и схемотехника средства сопряжения. - М.: Высшая школа, 1984, с,22, рис. 1.18. Источник3 опорного напряжения построен по схеме из той же книги (с ,58, рис,2.47) с добавлением двух резисторных делителей на его выходе, для обеспечения трех значений опорных напряжений на трех выходах источника 3.

Аналоговые коммутаторы 4,29 и преобразозатель 5 напряжения в код построены, соответственно, по схемам (см. книгу Воробьева Н.В. и Вернера В.Д., с.19, рис.1.14 и статью Климашаускаса К.Ю., Марцинкявичуса А,-И.К., Сташиса И.В. Быстродействующий восьмиразрядный АЦП К1107ПВ2, Электронная промышленность, Мг 7, 1985, рис.1, с.31).

Регистры 6-11 представляют собой регистры памяти с буферными устройствами на выходах, позволяющими отключать выходы регистров от внешних цепей (см. книгу Горбунова В.Л., Панфилова Д.И., Пресиухина Д.Л. Основы построения микроЭВМ. М.: Высшая школа, 1984, с.110, рис.3.5). Сумматор 12 и умножитель 13 построены, аналогично как у прототипа, соответственно на микросхемах КР 1802ИМ1 (6К0.348.629-11ТУ) и КР1802ВРЗ (6К0.348.629-07ТУ).

Постоянные запоминающие устройства

14 и 15 построены по схеме описанной в книге Алексеенко А.Г., Шагурина И.И. Микросхемотехника. - М.: Радио и связь, 1982, рис.7.17, С.269.

Формирователь 16 импульсов построен, как у прототипа, на триггере Шмитта с выходом, подключенным к D-входу триггера, R- и С-входы которого соединены с входом синхронизации формирователя, а прямой выход является выходом последнего.

Счетчики 18, 19 и элемент И 21 построены на микросхемах Е555ИЕ7 (б.Ко.348.289. ТУЗ) и К555ЛИ1 (бКо.348.289 ТУ1).

Формирователь 22 управляющих сигналов вместе с обозначениями его входов и выходов аналогичен используемому в прототипе, где подробно описан.

В качестве мультиплексора 26 использована микросхема К555КП11 (бКо.348.28914ТУ).

Предлагаемый преобразователь активной мощности в код работает следующим образом.

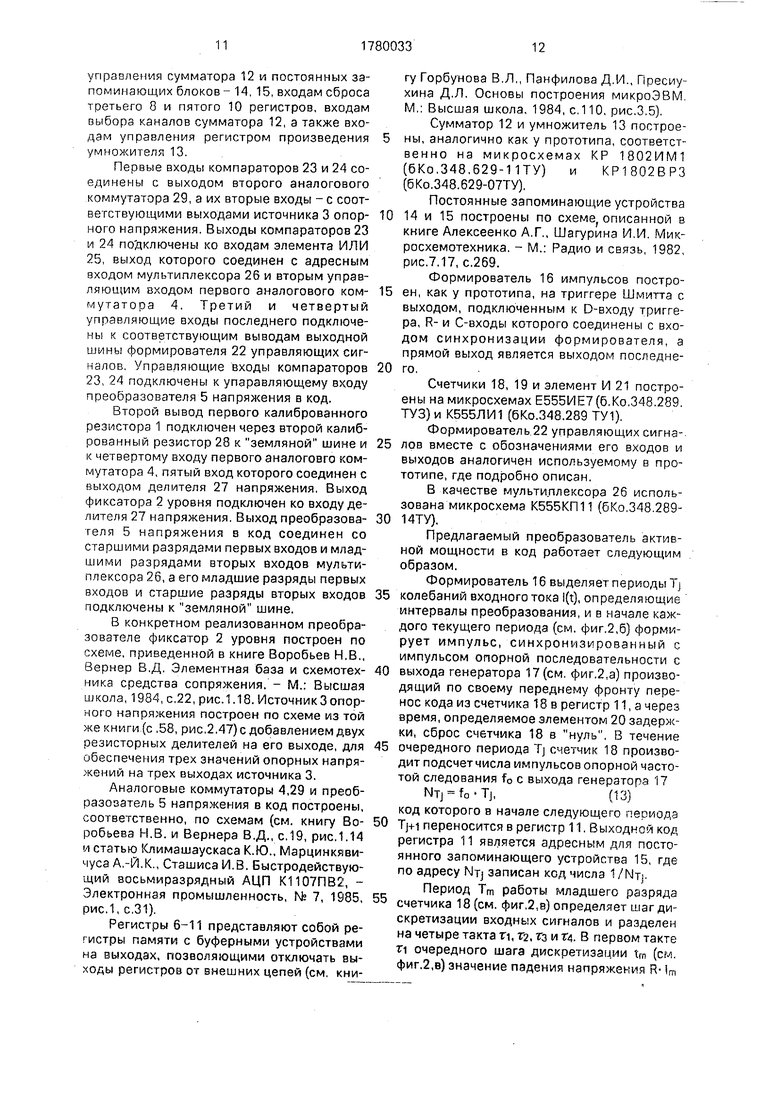

Формирователь 16 выделяет периоды Tj

колебаний входного тока l(t), определяющие интервалы преобразования, и в начале каждого текущего периода (см. фиг.2,6) формирует импульс, синхронизированный с импульсом опорной последовательности с

выхода генератора 17 (см. фиг.2,а) производящий по своему переднему фронту перенос кода из счетчика 18 в регистр 11, а через время, определяемое элементом 20 задержки, сброс счетчика 18 в нуль. В течение

очередного периода Tj счетчик 18 производит подсчет числа импульсов опорной частотой следования fo с выхода генератора 17

NTj fo-Tj,(13)

код которого в начале следующего периода

Tj+1 переносится в регистр 11. Выходной код регистра 11 является адресным для постоянного запоминающего устройства 15, где по адресу NTJ записан код числа 1 . Период Тт работы младшего разряда

счетчика 18 (см. фиг,2,в) определяет шаг дискретизации входных сигналов и разделен на четыре такта п, Т2, тз и Г4. В первом такте Т1 очередного шага дискретизации tm (СР. фиг.2,в) значение падения напряжения R- Im

на калиброванных резисторах 1 и 28, прямо пропорционально значению im входного тока в текущей точке m периода Tj, и значение входного напряжения Um в этой же точке поступает соответственно через аналоговый коммутатор 4 на вход преобразователя

5и на вход фиксатора 2, устанавливаемых формирователем 22 в режим выборки сигнала (см. фиг.2, г,д), где фиксируются. Во втором такте Г2 шага tm преобразователь 5 устанавливается формирователем 22 в режим хранения (см. фиг,2,д) и преобразует напряжение R- im в цифровой прямой код Nim, переносимый по окончании Г2 передним фронтом сигнала с выхода генератора 17 (см, фиг.2,а) через мультиплексор 26 в регистр 6:

N| Kl-lm,.(14)

где Ki - коэффициент пропорциональности.

В третьем такте гз шага tm (см. фиг.2,в) коммутатор 4, управляемый формирователем 22 (см. фиг.2,в), подключает ко входу преобразователя 5 напряжение um с выхода фиксатора 2, а сумматор 12 производит преобразование прямого кода Nim в дополнительный. При этом сумматор 12 установлен в состояние выборки первого канала и разрешения считывания (см. фиг.2, ж,з), а на входы выбора режима и переноса этого канала при инверсном значении Nim поступает 1 знака этого числа, определяющая инвертирование кода сумматора и прибавления к результату инвертирования единицы. В конце Гз результата преобразования сигналом с выхода сумматора (см. фиг.2,и) переносится в регистр 7. При положительном значении Ni его код остается без изменения, так как прямой и дополнительный коды положительного числа совпадают.

В четвертом такте т шага tm преобразователь 5 преобразует напряжение Um в цифровой прямой код числа Num (см. фиг.2,д):

Num KU- Um,(15)

где KU - коэффициент пропорциональности, который по окончании преобразования переносится через мультиплексор 26 в регистр

6(см.фиг.2,а), а во втором такте Т2 следующего шага дискретизации tm+i преобразуется сумматором 12 в дополнительный код (см. фиг.2,в,ж,з). В конце та коды чисел Num и Nim, соответственно, с выходов сумматора 12 и регистра 7, находящихся в состоянии разрешения считывания (см. фиг.2,3,ж) записываются сигналом с выхода формирователя 22 (см. фиг.2,л) в множительное устройство 13, где в течение следующего такта Гз(см. фиг.2,в) перемножаются, после чего результат перемножения под управлением формирователя 22 (см.фиг.2,м,и) заносится в регистр произведения. В первом такте шага дискретизации tm+2 код произведения Nim Num с выхода множительного

5 устройства 13 подается на входы второго канала сумматора 12, установленного формирователем 22 в состояние выборки второго и третьего каналов (см. фиг.2.п), где прибавляется к сумме результатов перемножения значений входных сигналов за (т-1) предшествующие точки их дискретизации в текущем интервале преобразования Tj с выходов регистра 8, после чего результат суммирования сигналов с выхода.

5 формирователя 22 (см. фиг.2,р) заносится в регистр 8. Такой обработке подвергаются значения входных сигналов всех точек дискретизации за интервал Tj, за исключением того, что результат перемножения кодов

0 входных сигналов для последней тонки дискретизации за Tj не записывается в регистр произведения устройства 13, а непосредственно в четвертом такте шага дискретизации ti интервала преобразования

5 складывается сумматором 12 с выходным кодом регистра 8 (см.фиг.2,б,в,м,н,п), после чего результирующий код

п1

NZJ 2: ,-(16)

0m г

преносится в устройство 13 (см. фиг.2,з,л) одновременно с кодом коэффициента коррекции К|сС выходом постоянного запоминающего устройства 14, установленного

5 формирователем 22 (см.фиг.2,т) в режиме разрешения считывания. В течение второго такта Г2 шага t2 в интервале Tj-t-i осуществляется умножение на коэффициент Кк, после чего результат перемножения с выхода

0 устройства 13 (см. фиг.2,м,н), прямо пропорциональный активной энергии

/ l(t).u

(t)dt, (17)

N.J KK-NJ:J KV

где KW - коэффициент пропорциональности, записывается в регистр 9 (см. фиг.2,д).

В начале четвертого такта формирователем 22 осуществляется сброс в О регистра 8 (см. фиг.2,з). В конце этого же такта

коды NWJ с выхода регистра 9 и I/NTI с выхода постоянного запоминающего устройства 15 (см. фиг.2,ф) заносятся в устройство 13, где перемножаются (см. фиг.2,л), после чего результат перемножения, прямо проц порциональный активной мощности, переносится в регистр 9 (см. фиг.2,м,н,у);

At) и(

Npj NWJ/NTJ Кр /l(t) u(t)dt

(1В)

о

Коэффициент коррекции Кк вводится для коррекции дополнительной погрешности, вызываемой изменением температуры окружающей среды и старением элементов. В постоянное запоминающее устройство 14 заблаговременно заносятся возможные значения коэффициента коррекции в заданном температурном диапазоне работы преобразователя. Выбор нужного значения Кк осуществляется следующем образом. Периодически, через определенное число периодов 1(т), счетчик 19 устанавливается в состояние, которое определяет интервал коррекции Тк и обеспечивает подключение источника 3 опорного напряжения Uo к аналоговому входу преобразователя 5 (см, фиг.2,х). В течение интервала Тк опорное напряжение Uo претерпевает те же преобразования, что и входные переменные сигналы R i{t) и u(t), В начале следующего интервала Тк+1 (см. фиг.2,6} регистр 10, выходной код которого определяет адрес обращения к постоянному запоминающему устройству 14, сбрасывается сигналом с формирователя 22 (см. фиг.2,ц) в состояние, определяющее код числа 1 на выходе устройства 14. Результирующий код преобразования Uo за Тк умножается на Кк-1 и 1/NTK, после чего результат преобразования переносится в регистр 10 (см, фиг.2,ч), определяя адрес обращения к устройству 14 до следующего интервала преобразования Uo. . Компараторы 23 и 24, работающие синхронно с преобразователем 5 напряжения в код, контролируют величину текущего входного сигнала, сравнивая его со значениями Uni и Un2. поступающими с выходов источника 3 опорного напряжения: Uni Umax +AU I,.Q Un2 Umln-Au I где Umax И Umin - максимальнее и минимальное значения входного напряжения, определяющие масштаб измерения преобразователя 5 напряжения в цифровой код: Ди - величина отклонения напряжения, зависящая от чувствительности преобразователя 5 и равная величине его младщего разряда (взято из соображений, что значение случайной составляющей погрешности преобразователя 5 и компараторов не превышает половину младшего разряда преобразователя 5). Если значение входного сигнала не превышает масштаб преобразователя 5, то на выходе Элемента ИЛИ 25 устанавливается значение логического нуля, а аналоговый коммутатор 4 подтверждает поступление сигналов с выхода фиксатора 2 уровня и с ервого вывода резистора 1 без изменения, .е. с единичным коэффициентом передачи, При отклонении входного сигнала от масштаба Umax + Д и; Umin - Аи появляется ровень логической единицы на выходе одного из компараторов 23 или 24, контролирующих уровень сигнала с выхода второго аналогового коммутатора 29, что заставляет первый аналоговый коммутатор 4 переключиться и изменить коэффициент передачи того канала (напряжения или тока), где возникло отклонение, взяв сигнал либо с выхода делителя 27 напряжения, либо с точки соединения резисторов 1 и 28. Разрядность кодов на выходе преобразователя 5 напряжения в код в обоих случаях будет разная, т.е. величине его младшего разряда, когда входной сигнал находится в пределах масштаба и вне его, будет соответствовать разная величина напряжения. Рассмотрим случай четырехкратного превышения масштаба преобразователя 5, тогда коэффициент передачи делителя 27 напряжения и делителя на резисторах 1, 28. п 4, что соответствует двум двоичным разрядам (). В зтом случае работа мультиплексора 26 организовывается .таким образом, что, когда на выходе элемента ИЛИ 25 находится уровень нуля (входной сигнал не превышает масштаб Umax + Д и; Umin - Аи), то на выходе мультиплексора 26 устанавливается код вида ICON,(20а) где 1 - код знака, N - код с выхода преобразователя 5, Когда на выходе элемента ИЛИ 25 присутствует уровень (входной сигнал превышает масштаб Umax + и; Umin- и), то на выходе мультиплексора 26 устанавливается код вида INOO.(206) Таким образом, например, в случае применения преобразователя 5 типа К1107ПВ2 имеем на выходе мультиплексора 26 10-разрядную шину. После дальнейших вычислений по алгоритму нахождения значения активной мощности лишние разряды можно убрать путем простого сокращения разрядности кода результата. Суммарное среднеквадратическое значение C7fi случайных составляющих погрешностей предлагаемого устройства определяется выражением 2(ии2Ди2+1и2 Aui2) /r-ATxVТх /u(t)-|(t)dt

с учетом того, что .при изменении масштаба измерения преобразователя 5 его значения абсолютных случайных погрешностей ± Ah и ±Aui не именяются, причем Uii и IH математические ожидания uii и .

Сравнивая выражения (10)и (21), прини-A Ai2i Ali и

мая при этом, что

А U22 АА

Au2i Aui, а также, что площади

отрезков входного сигнала при выдаче кодов мгновенных значений uii и iii преобразователями 5 и 25 (в случае прототипа)

п

2 SUl2Ai22

2 А 121

т.е. SUii

равны, И 1

12 1

m

п

И Xи Д21 Д22 .получим 2 л ,,. 2

И 112 1

Qr.grr 2 2 СГц./

Кроме того, исходя из принципа работы предлагаемого устройства видно, что в данном случае отсутствует составляющая погрешности за счет различия аддитивных систематических погрешностей преобразователей 5 и 25, характерная для прототипа. Таким образом, предлагаемый преобразователь активной мощности в код обладает не менее чем в 2 раза более высокой точностью преобразования сигналов промышленной электросети по сравнению с прототипом.

Формула изобретения Преобразователь активной мощности в цифровой код, содержащий, первый калиброванный резистор, фиксатор уровня, источник опорного напряжения, первый и второй аналоговые коммутаторы, преобразователь напряжения в код, шесть регистров, сумматор, умножитель, первый и второй постоянные запоминающие блоки, формирователь импульсов, генератор опорной частоты, первый и второй счетчики, элемент задержки, элемент И, формирователь управляющих сигналов, мультиплексор и делитель напряжения, причем вход фиксатора уровня соединен с входной шиной напряжения, первый вывод первого калиброванного резистора соединен с входной шиной тока, входом формирователя импульсов и первыми входами аналоговых коммутаторов, выход первого аналогового коммутатора подключен к информационному входу преобразователя напряжения в код, первый выход источника опорного напряжения подключен к второму входу первого аналогового коммутатора, выход фиксатора уровня соединен с третьим входом первого и вторым входом второго аналоговых коммутаторов, выход мультиплексора подключен к входу первого регистра, первый выход первого регистра через элемент И подключен к входам выбора режима и переноса первого канала сумматора, а вторые выходы - к вторым входам первого канала сумматора, первый вход первого канала сумматора соединен с земляной шиной, а выходы - с входами третьего регистра, выходы старших разрядов сумматора соединены также с входами второго регистра и входами второго канала умножителя, подключенными также к выходам четвертого регистра, входы первого канала умножителя соединены с выходами второго регистра и постоянных запоминающих блоков, а выходы -с входами четвертого, пятого регистров и входами третьего канала сумматора, входы второго канала которого подключены к выходам третьего регистра, выход генератора опорной частоты соединен с входом синхронизации формирователя импульсов, входом записи первого

5 регистра и входом первого счетчика, выходы разрядов которого подключены к входам шестого регистра, а вход сброса в нуль - к входу второго счетчика и через элемент задержки к входу записи шестого регистра и

0 выходу формирователя импульсов, входы первого и второго постоянных запоминающих блоков подключены соответственно к выходам пятого и шестого регистров, первый вход формирователя управляющих сигналов соединен с выходом генератора опорной частоты, выходы первого и второго счетчиков подключены к первой и второй группам входов формирователя управляющих сигналов, выходня шина управления которого подключена к входу управления первого аналогового коммутатора, входу управления второго аналогового коммутатора, входу управления фиксатора уровня, тактовому входу преобразователя напряжения в

5 код, первому входу элемента И, входам записи второго, третьего, четвертого, пятого регистров и умножителя, входам резрешения считывания второго и четвертого регистров, входам управления сумматора и

0 постоянных запоминающих блоков, входам сброса третьего и пятого регистров, входам выбора каналов сумматора, а также входам управления регистром произведения умножителя, отличающийся тем, что, с целью

5 повышения точности преобразования устройства, в него введены первый и второй компараторы, элемент ИЛИ и второй калиброванный резистор, причем первые входы компараторов соединены с выходом второго аналогового коммутатора, а их вторые

входы - с соответствующими выходами источника опорного напряжения, выходы компараторов подключены ко входам элемента ИЛИ, выход которого соединен с адресным входом мультиплексора и вторым управляющим входом первого аналогового коммутатора, третий и четвертый управляющие входы которого подключены к соответствующим выводам выходной шины формирователя управляющих сигналов, кроме того, управляющие входы компараторов подключены к управляющему входу преобразователя напряжения в код, а второй вывод

первого калиброванного резистора подключен через второй калиброванный резистор к земляной шине и четвертому входу первого аналогового коммутатора, пятый вход которого соединен с выходом делителя напряжения, выход фиксатора уровня подключен к входу делителя напряжения, выход преобразователя напряжения в код соединен со старшими разрядами первых входов

0 и младшими разрядами вторых входов мультиплексора, а его младшие разряды первых входов и старшие разряды вторых подключены к земляной шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь активной мощности в цифровой код | 1987 |

|

SU1471143A2 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1647893A1 |

| Преобразователь активной мощности в цифровой код | 1987 |

|

SU1451615A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2240649C2 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1758875A1 |

Использование: контроль параметров электроэнергии промышленной сети в составе информационно-измерительных систем. Сущность изобретения: устройство содержит два калиброванных резистора 1 и 28, фиксатор 2 уровня, источник 3 опорного напряжения, два аналоговых коммутатора 4 и 29, преобразователь напряжение - код 5, шесть регистров 6-11, сумматор 12, умножитель 13, два постоянных запоминающих блока 14 и 15, формирователь 16 импульсов, генератор 17 тактовых импульсов, два счетчика 18 и 19, элемент задержки 20. элемент И 21, блок 22 управления, два коммутатора 23 и 24, элемент ИЛИ 25, мультиплексор 26, делитель 27 напряжения. 2 ил.flee вжпзуHumvi/H лмиOS^гСОсVI00о оСА) СА>&

Ji... ЛJ Jl пJnJTЛJT-.. -П... 11 Л-... IJ- TJTJTJTJ-LrLnj-Lr- ЛJ J1JПLЛJTЛJT... rLTLTi... гиглллл. TJlJTJlJlJTJlJbr lJlJlJ- TrLnjTJl-rLr П лл

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-07—Публикация

1989-12-04—Подача