Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления параметрами электрической энергии среднего и большого уровня мощности.

Целью изобретения является расширение динамического и частотного диапазонов преобразования.

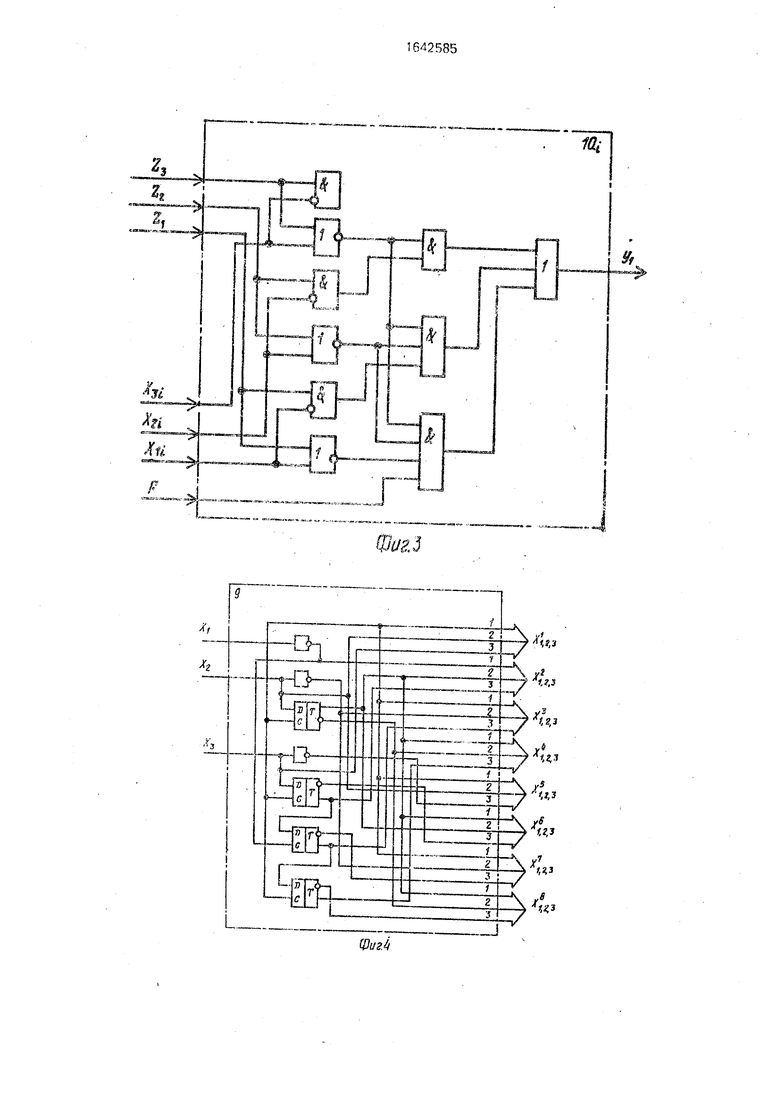

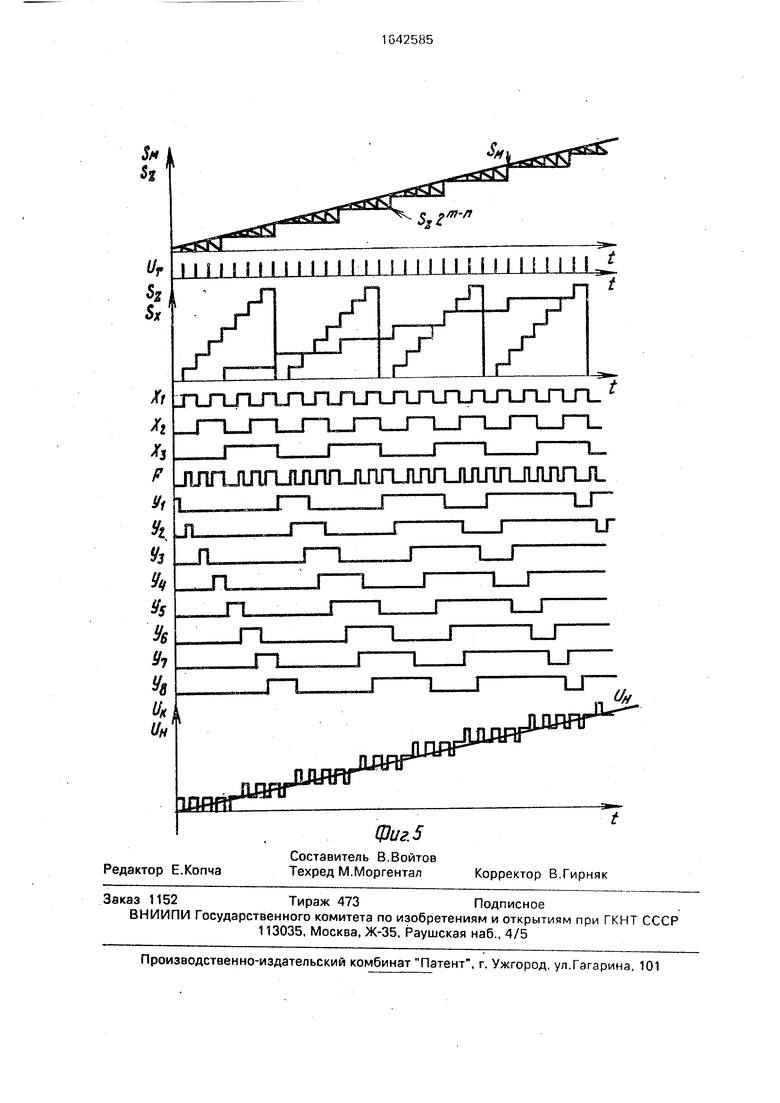

На фиг. 1 изображена структурная электрическая схема цифроаналогового преобразователя; на фиг. 2 - структурная схема преобразователя кода; на фиг.З - структурная схема логического блока; на фиг.4 - структурная схема многоканального регистра сдвига; на фиг.5 - временные диаграммы работы устройства.

Цифроаналоговый преобразователь (фиг. 1) содержит формирователь 1 кода, генератор 2 тактовых импульсов, широтно-импульсный преобразователь 3, делитель 4 частоты, преобразователь 5 кода, ключевые усилители 6.1-6.N, аналоговый сумматор 7, выходную шину 8.

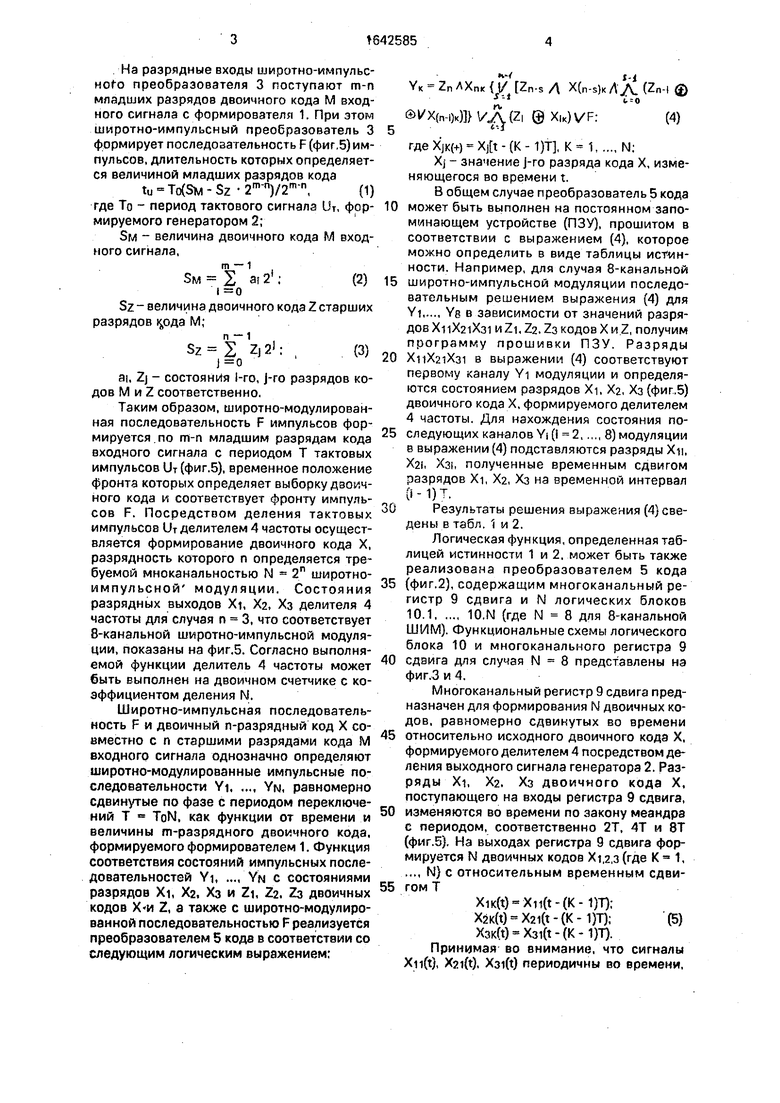

Преобразователь 5 кода (фиг.2) выполнен на многоканальном регистре 9 и N логических блоках 10.1-10.N.

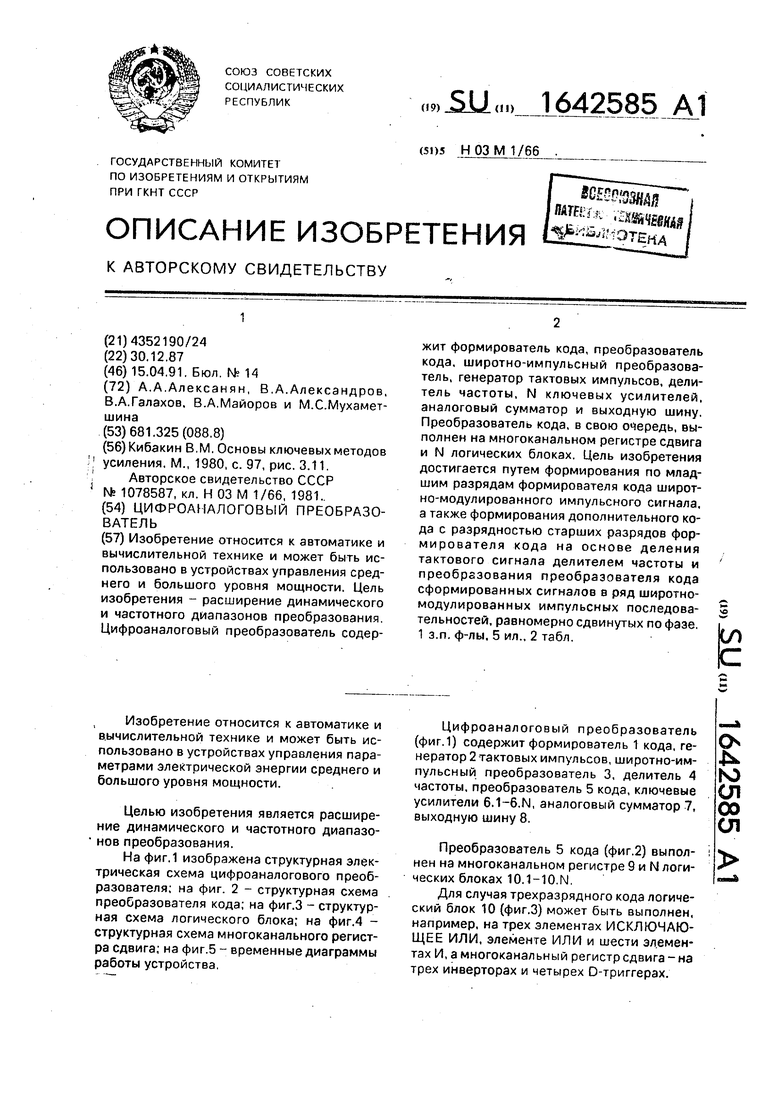

Для случая трехразрядного кода логический блок 10 (фиг.З) может быть выполнен, например, на трех элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, элементе ИЛИ и шести элементах И, а многоканальный регистр сдвига-на трех инверторах и четырех D-триггерах.

О 4 W СП 00

ел

На разрядные входы широтно-импульс- ного преобразователя 3 поступают m-n младших разрядов двоичного кода М входного сигнала с формирователя 1. При этом широтно-импульсный преобразователь 3 формирует последовательность Р(фиг,5) импульсов, длительность которых определяется величиной младших разрядов кода

tu To(SM-Sz -2т-п)/2тЛ(1)

где То - период тактового сигнала UT, формируемого генератором 2;

5м - величина двоичного кода М входного сигнала,

т-1 ,

5м - 2 at 2f;(2)

Sz - величина двоичного кода Z старших разрядов к/эда М;

1Zj2i; ,(3)

at. Zj - состояния 1-го, J-ro разрядов кодов М и Z соответственно.

Таким образом, широтно-модулирован- ная последовательность F импульсов формируется по m-n младшим разрядам кода входного сигнала с периодом Т тактовых импульсов UT (фиг.5), временное положение фронта которых определяет выборку двоичного кода и соответствует фронту импульсов F. Посредством деления тактовых импульсов UT делителем 4 частоты осуществляется формирование двоичного кода X, разрядность которого п определяется требуемой мноканальностью N 2П широтно- импульсной модуляции. Состояния разрядных выходов Xi, Xz, Хз делителя 4 частоты для случая п 3, что соответствует 8-канальной шмротно-импульсной модуляции, показаны на фиг.5. Согласно выполняемой функции делитель 4 частоты может быть выполнен на двоичном счетчике с коэффициентом деления N.

Широтно-импульсная последовательность F и двоичный n-разрядный код X совместно с п старшими разрядами кода М входного сигнала однозначно определяют широтно-модулированные импульсные последовательности YI, .... YN, равномерно сдвинутые по фазе с периодом переключений Т ТоМ, как функции от времени и величины m-разрядного двоичного кода, формируемого формирователем 1. Функция соответствия состояний импульсных последовательностей YI, ..., YN с состояниями разрядов Xi, X2, Хз и Zi, Z2, 2з двоичных кодов Х«и Z, а также с широтно-модулиро- ванной последовательностью F реализуется преобразователем 5 коде в соответствии со следующим логическим выражением:

и.-/

t-i

YK Zn ЛХпк { V Zn-s Л X(n-s)K Л А Ф

®yX(n4)K)(Zi ® XJK)VF:(4)

где X JKW - (К - 1)Т, К 1, ..., N;

Xj - значение j-ro разряда кода X, изменяющегося во времени t.

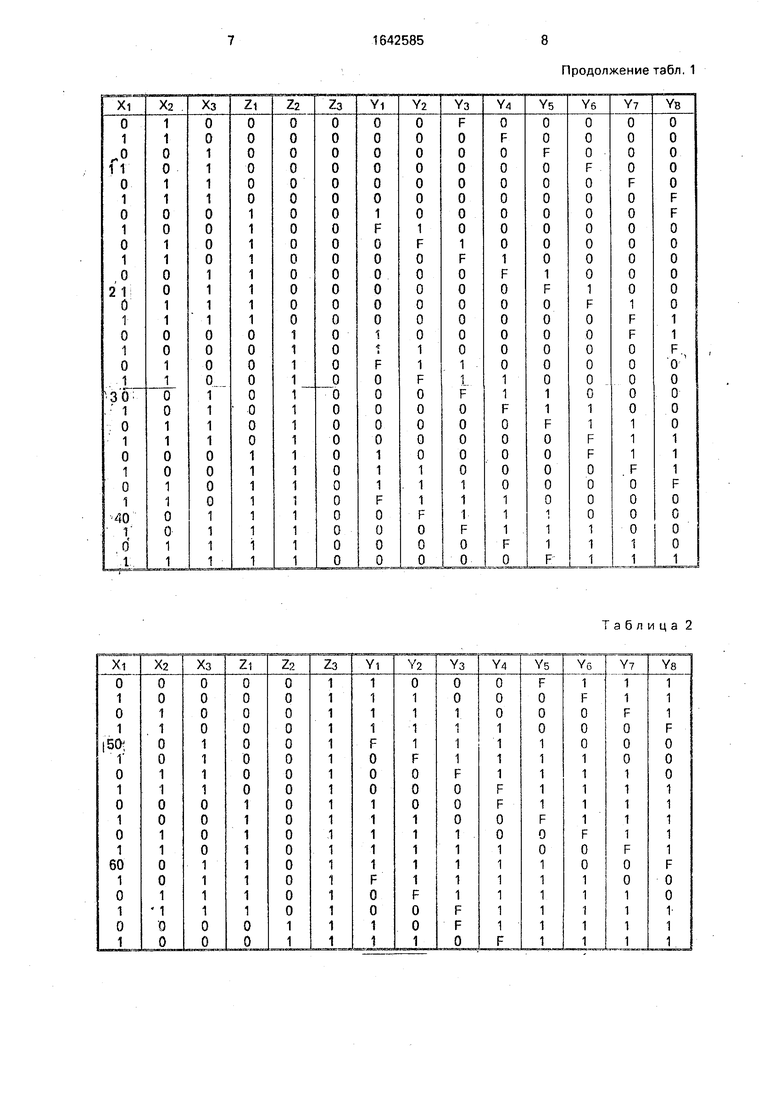

8 общем случае преобразователь 5 кода

0 может быть выполнен на постоянном запоминающем устройстве (ПЗУ), прошитом в соответствии с выражением (4), которое можно определить в виде таблицы истинности. Например, для случая 8-канальной

5 широтно-импульсной модуляции последовательным решением выражения (4) для YIYe в зависимости от значений разрядов ХцХ21Хз1 nZi,Z2,Z3KOflOBXMZ, получим программу прошивки ПЗУ. Разряды

0 ХцХ21Хз1 в выражении (4) соответствуют первому каналу YI модуляции и определяются состоянием разрядов XL Х2, Хз (фиг.5) двоичного кода X, формируемого делителем 4 частоты. Для нахождения состояния по5 следующих каналов Yj(i 28) модуляции

в выражении (4) подставляются разряды Хц, X2I, Хз, полученные временным сдвигом разрядов Xi, X2, Хз на временной интервал

0-1)0 Результаты решения выражения (4) сведены в табл. 1 и 2.

Логическая функция, определенная таблицей истинности 1 и 2. может быть также реализована преобразователем 5 кода

5 (фиг.2), содержащим многоканальный регистр 9 сдвига и N логических блоков

10.1 10.N (где N 8 для 8-канальной

ШИМ). Функциональные схемы логического блока 10 и многоканального регистра 9

0 сдвига для случая N 8 представлены на фиг.З и 4.

Многоканальный регистр 9 сдвига предназначен для формирования N двоичных кодов, равномерно сдвинутых во времени

5 относительно исходного двоичного кода X, формируемого делителем 4 посредством деления выходного сигнала генератора 2. Разряды XL X2. Хз двоичного кода X, поступающего на входы регистра 9 сдвига,

0 изменяются во времени по закону меандра с периодом, соответственно 2Т, 4Т и 8Т (фиг.5). На выходах регистра 9 сдвига формируется N двоичных кодов Xi,2,3 (где К а 1, ..., N} с относительным временным сдви5 гом Т

XiK(t) Xii(t-(K-1)T); X2K(t) X2i(t-(K-1)T);(5)

X3K(t) X3i(t-(K-1)T). Принимая во внимание, что сигналы Xn(t), Xjift), Xai(t) периодичны во времени,

ункцию регистра сдвига можно упростить. ак, для К- 1. 3. 5, 7 непосредственно можо использовать Xn(t), а для К 2, 4, 6, 8 - Гцфмт.д.

Функция, выполняемая логическим 5 блоком 10, определяется выражением (4).

Цифроэналоговый преобразователь работает следующим образом.

Формирователь 1 формирует на разряд- 10 ных выходах m-разрядный двоичный код входного сигнала, изменение которого осуществляется при поступлении на вход синхронизации формирователя выходных импульсов U генератора 2. Младшие разря- 15 ды выходного кода формирователя 1 поступают на m-n разрядные входы широтно-импульсного преобразователя 3, где преобразуются в длительность импульсов tn(1), фронт которых совпадает с 20 фронтом тактовых импульсов Jr. Широтио- модулированная импульсная последовательность F с выхода широтно-импульсного преобразователя 3 подается на один вход преобразователя 5 кода, на другие разряд- 25 ные входы которого поступают код старших разрядов Z формирователя 1 и двоичный код X, сформированный делителем 4 путем деления тактового скгналз генератора 2.

В соответствии с логической функцией 30 {4} по двоичным кодам Z, X и импульсному сигналу F преобразователь коца 5 формирует N импульсных последовательностей, модулированных по закону m-разрядного кода входного сигнала, которые поступают через 35

ключевые усилители 6.1 6.N на входы

аналогового сумматора 7. Суммарное импульсное напряжение UK (фиг.5) большого уровня мощности через фильтрующее звено, входящее в состав сумматора 7 сум- 40 мирующего устройства, поступает по выходной шине 8 в нагрузку, где выделяются полезные низкочастотные составляющие UH входного сигнала. Максимальная величина UM равнй NEo (где Ео - амплитуда выход- 45 ных импульсов ключевых усилителей), что з N рзг больше амплитуды дополнительных высокочастотных составляющих импульсного напряжения. Выбирая частоту переключений суммарного импульсного 50 напряжения в 10 раз больше верхней частоты входного сигнала при использовании фильтрующего звена второго порядка, в устройстве достигается динамический пазон преобразования порядка D/I 4MS+ .

При этом частота переключений отдельных ключевых усилителей в N раз ниже частоты изменения суммарного импульсного напряжения.

Формулаиэобрэтения

1.Цифроаналоговый преобразователь, содержащий формирователь кода, выходы младших разрядов которого подключены к соответствующим информационным входам-- шпротно-ммпульсного преобразователя, вход синхронизации которого соединен с выходом генератора тактовых импульсов, и первый ключевой усилитель, отличающийся тем, что, с целью расширения динамического и частотного диапазонов преобразования, в него введены делитель частоты, преобразователь кода, N-1, где N - число выходов преобразователя кода, ключевых усилителей, и аналоговый сумматор, выход которого является выходной шиной, а входы через соответствующие ключевые усилители подключены к выходам преобразователя кода, первые информационные входы которого соединены с соответствующими выходами стари;их разрядов формирователя кода, вход синхронизации подключен к выходу широтно-импульсного преобразователя, а вторые информационные входы соответственно соединены с выходами делителя частоты, вход которого обьединен с входом синхронизации формирователя кода и подключен к выходу генератора тактовых импульсов.

2.Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что преобразователь кода выполнен на многоканальном регистре сдвига и N логических блоках, выходы которых являются выходами преобразователя кода, входы синхронизации объединены и являются входом синхронизации преобразователя кода, первые информационные входы соответственно объединены и являются первыми информационными входами преобразователя кода, вторыми информационными входами которого являются соответствующие входы многоканального регистра сдвига, выходы которого соответственно подключены к вторым информационным входам логических блоков,

Таблица 1

Продолжение табл. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Широтно-импульсный модулятор | 1988 |

|

SU1621159A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Генератор импульсных последовательностей | 1977 |

|

SU752764A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для преобразования кода в постоянный сигнал | 1985 |

|

SU1275774A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления среднего и большого уровня мощности. Цель изобретения - расширение динамического и частотного диапазонов преобразования. Цифроаналоговый преобразователь содержит формирователь кода, преобразователь кода, широтно-импульсный преобразователь, генератор тактовых импульсов, делитель частоты, N ключевых усилителей, аналоговый сумматор и выходную шину. Преобразователь кода, в свою очередь, выполнен на многоканальном регистре сдвига и N логических блоках. Цель изобретения достигается путем формирования по младшим разрядам формирователя кода широт- но-модулированного импульсного сигнала, а также формирования дополнительного кода с разрядностью старших разрядов формирователя кода на основе деления тактового сигнала делителем частоты и преобразования преобразователя кода сформированных сигналов в ряд широтно- модулированных импульсных последовательностей, равномерно сдвинутых по фазе. 1 з.п. ф-лы, 5 ил., 2 табл. &

Таблица 2

Продолжение табл. 2

S892V91

Л

Ur

h

Sx

illli lllilll..i.-LLUJLIMIiMM J

Xi

h

h

p

t

Уз 9 9s УВ У

У UK VH

LriJTJTJTJTJTJiJTJn

ииҐиШПЛ1ПЛПЛ11ҐТЛШ

Фиг. 5

| Кибакин В,М, Основы ключевых методов усиления | |||

| М., 1980, с | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для усиления | 1983 |

|

SU1078587A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-15—Публикация

1987-12-30—Подача