Изобретение относится к вычислительной технике, в частности к устройствам обработки информации специального назначения, и моясет быть использовано как специализированное вычислительное устройство для научно-исследовательских целей и моделирования дискретных дифференциальных игр, а также для управления некоторыми технологическими процессами в различных отраслях промышленности.

Целью изобретения является расширение класса решаемых задач за счет определения кратчайших путей и ветвей графа.

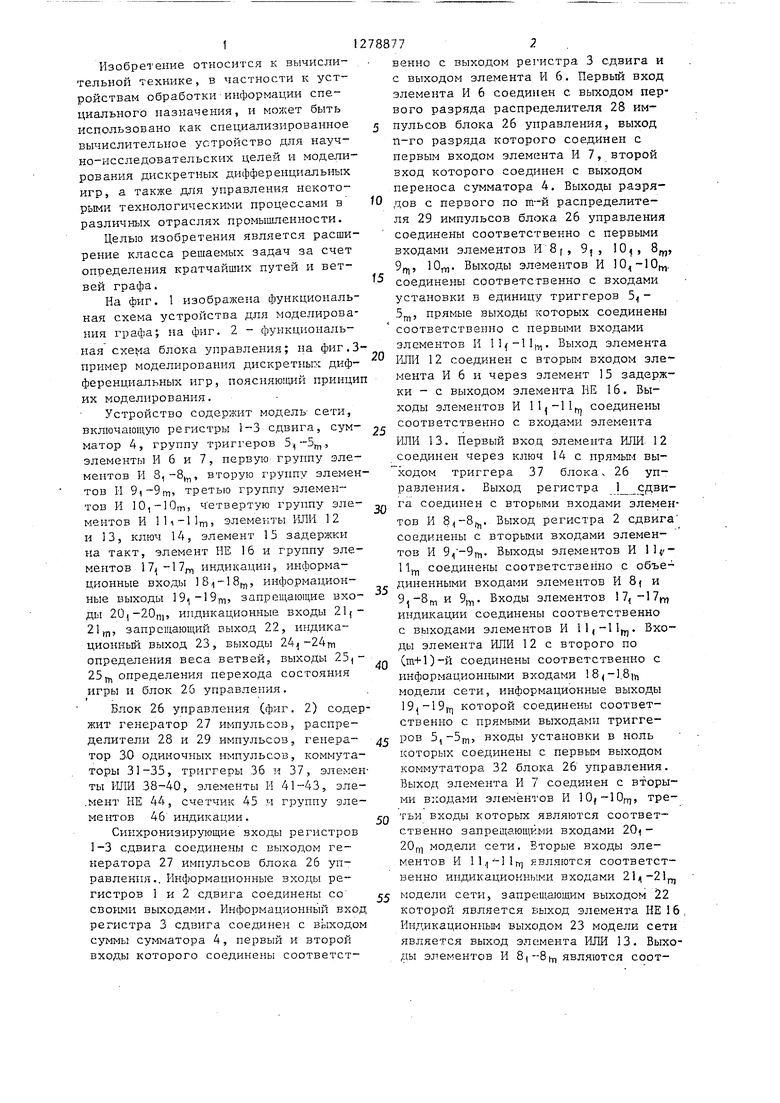

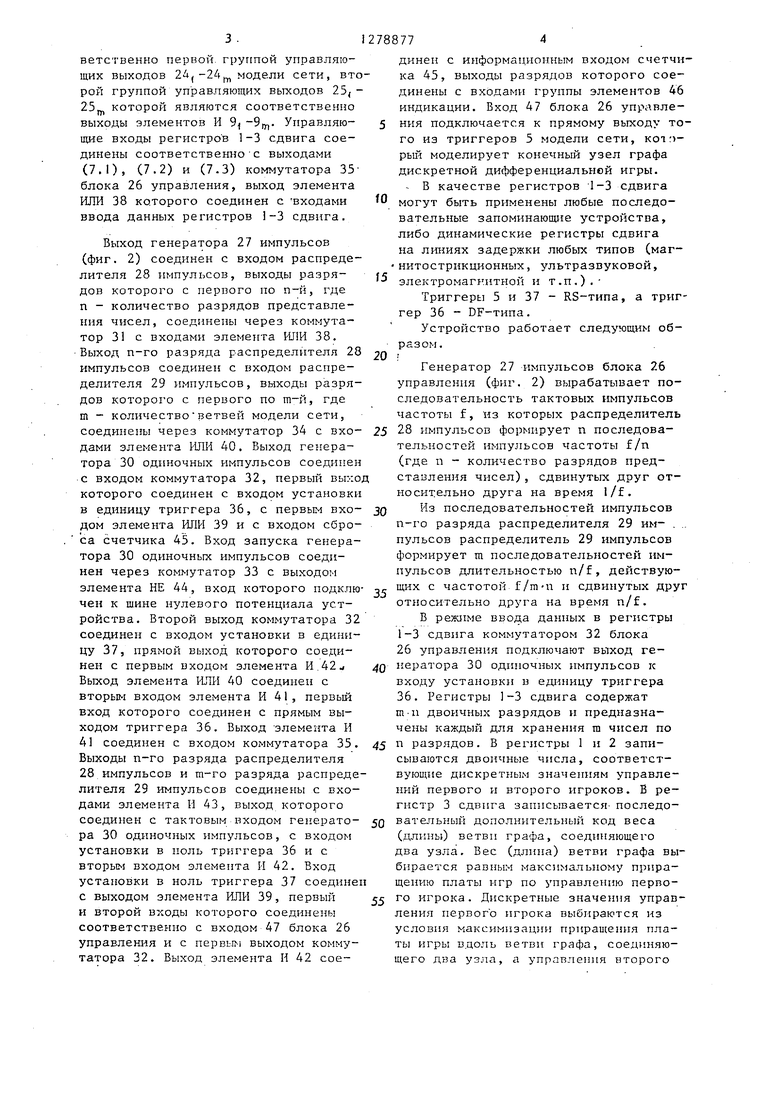

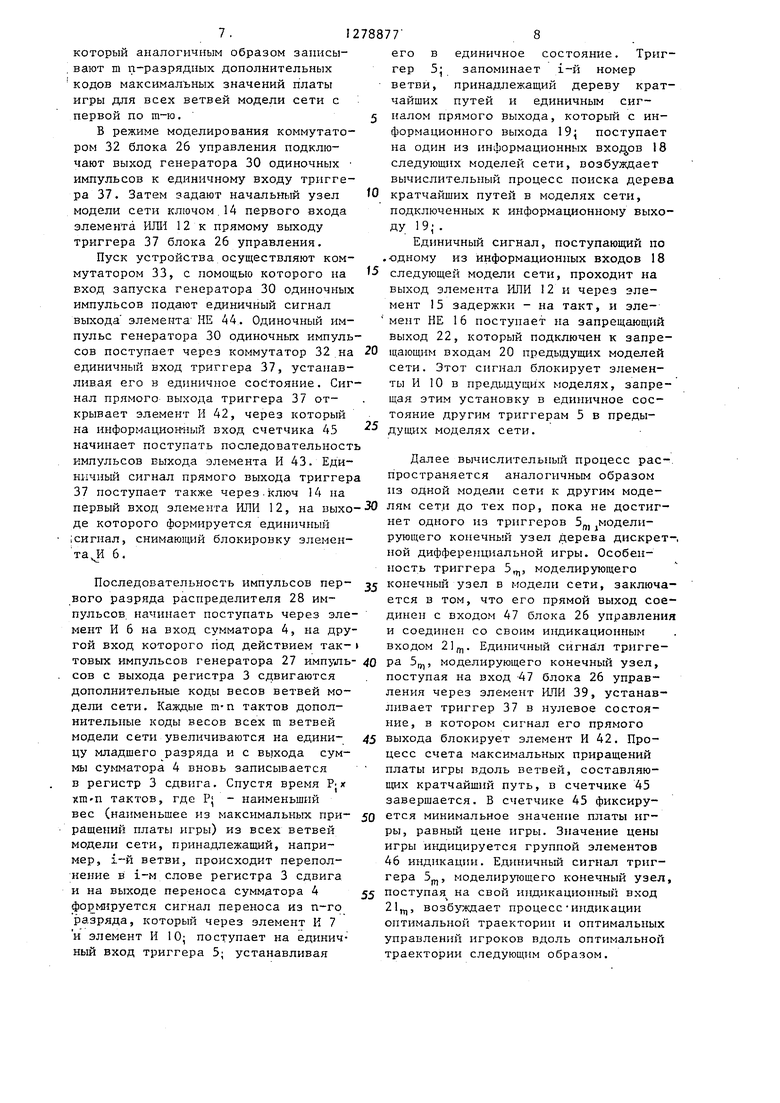

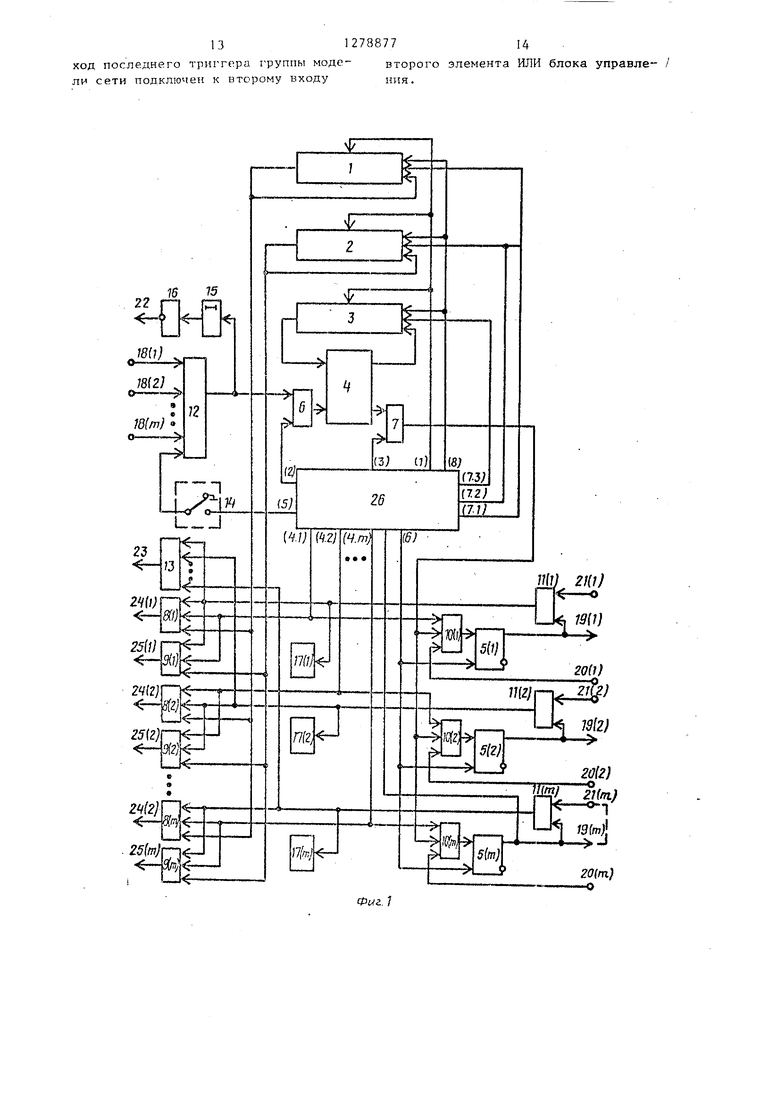

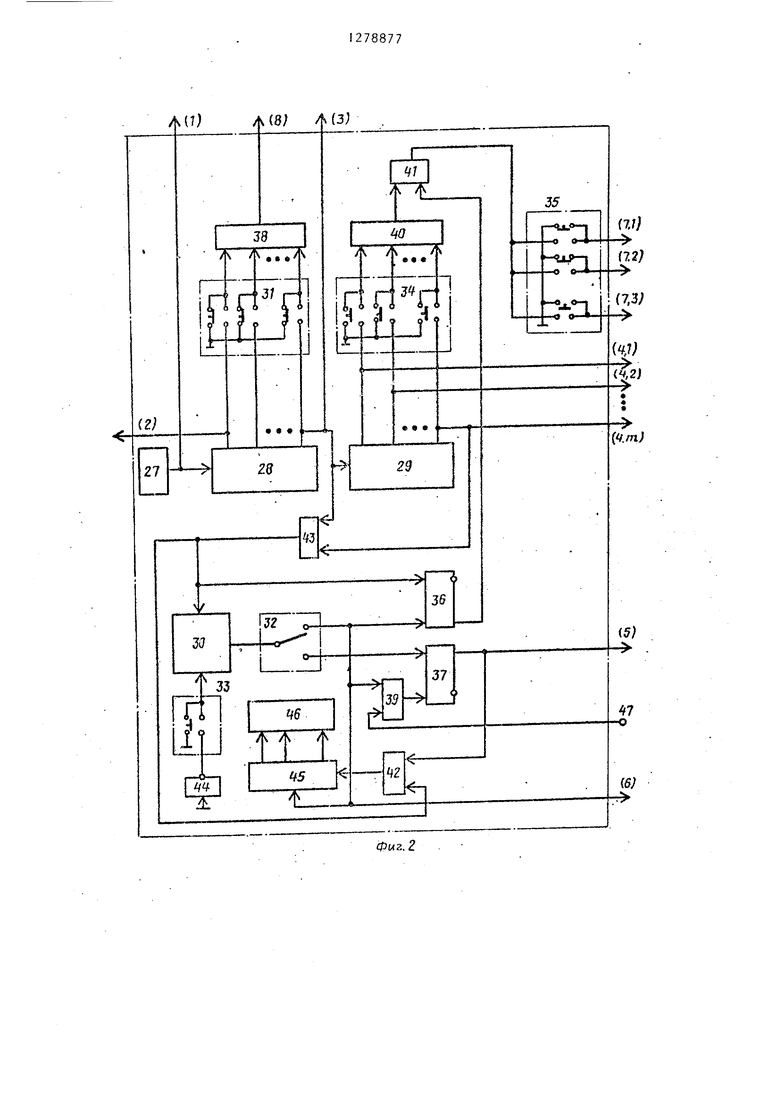

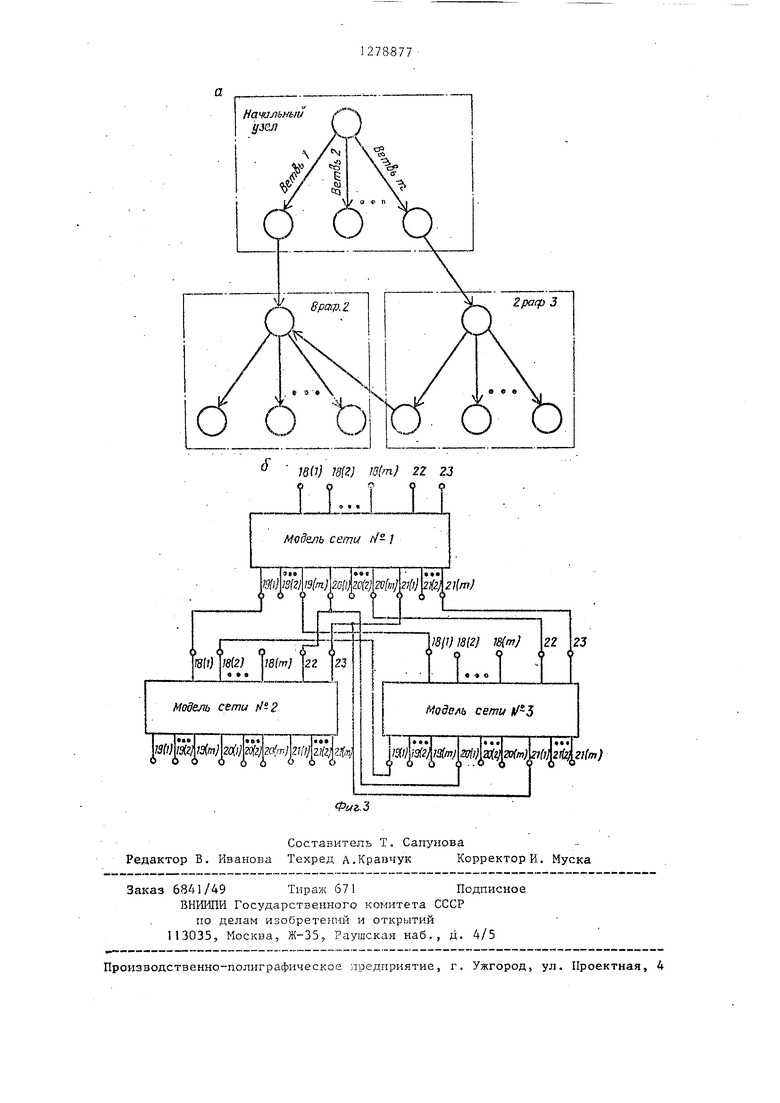

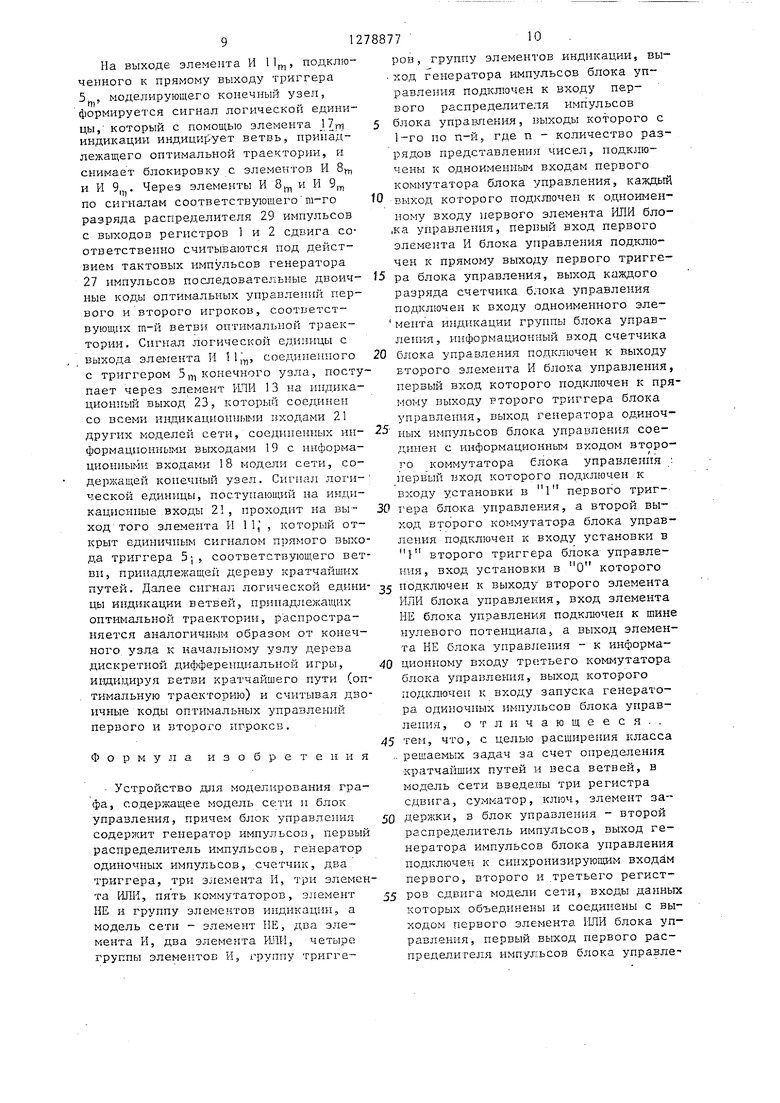

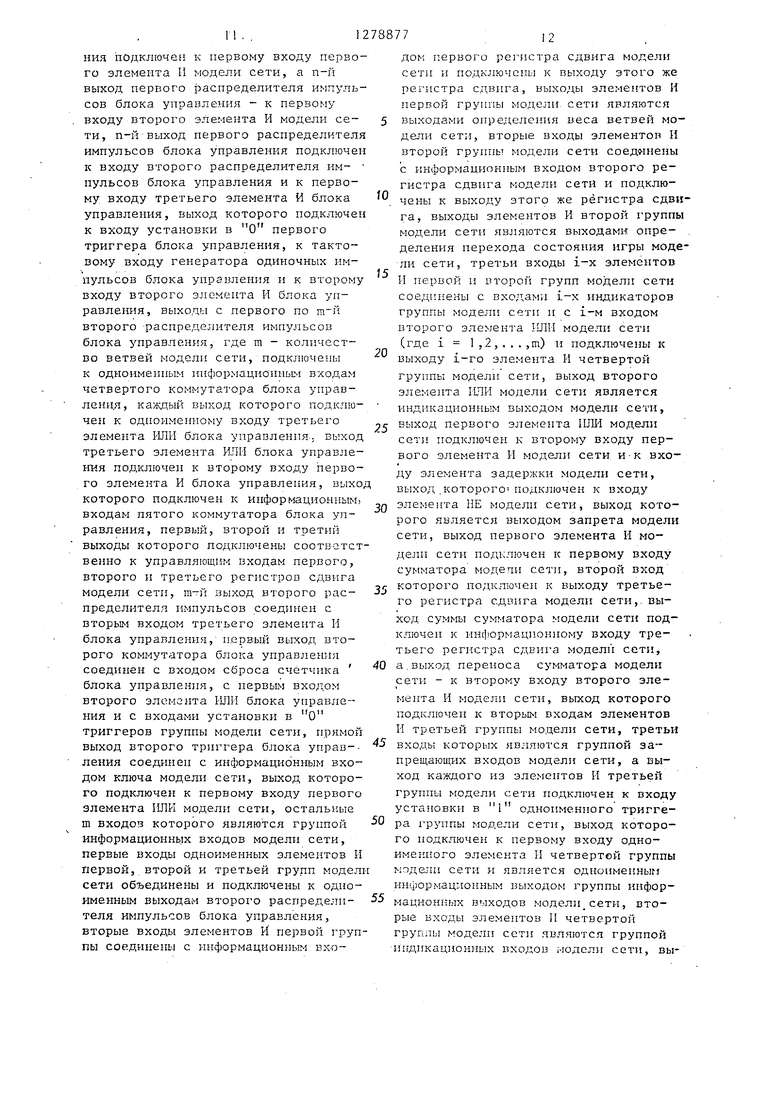

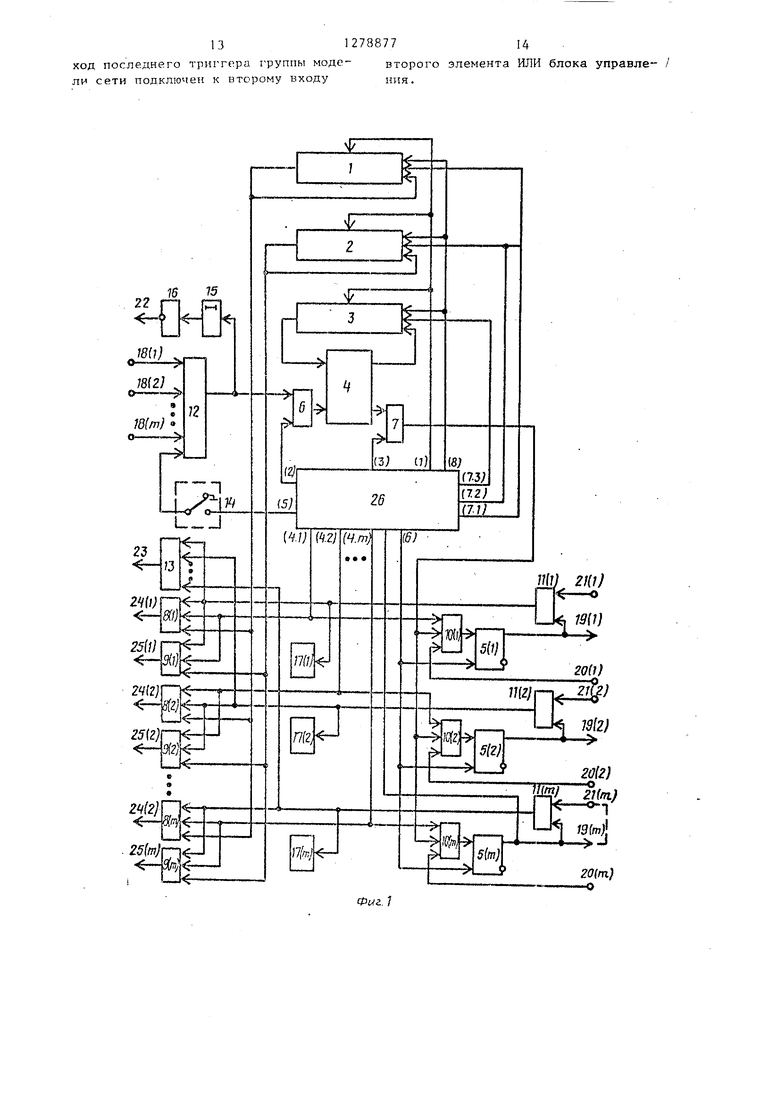

На фиг. 1 изображена функциональная схема устройства для моделирования графа; на фиг, 2 - функциональная блока управления; на фиг , 3 пример моделирования дискретньк дифференциальных игр, ПОЯСНЯЮ1ЦИЙ принци их моделирования.

Устройство содержит модель сети, включающую регистры 1-3 сдвига, сумматор 4, группу триггеров 5,-5, элементы И б и 7, первую группу элементов И 3,-8,, вторую группу элементов И 9i-9iY,, третью группу элементов И 10,-Ют, ч етвертую группу элементов И lb-Птп, элементы i-ШИ 12 и 13, ключ 14, элемент 15 задержки на такт, элемент НЕ 16 и группу элементов индикации, информационные входы 18i-18, информационные выходы 19,1-19гп, запрещающие входы 20,-20,-), индикационные входы 21(- 21JJ,, запрещающий выход 22, индика- ционньй выход 23, выходы определения веса ветвей, выходы 25,- 25 г„ определения перехода состояния игры и блок 2G управления.

Блок 26 управления СФлг. 2) содержит генератор 27 импульсов, распределители 28 и 29 импульсов, генератор 30 одиночных импульсов, коммутаторы 31-35, триггеры 36 и 37, элементы 1-ШИ 38-40, элементы И 41-43, эле- .мент НЕ 44, счетчик 45 и группу элементов 46 индикации.

Синхронизирующие входы регистров 1-3 сдвига соединены с выходом генератора 27 импульсов блока 26 управления,. Информационные входы регистров 1 и 2 сдвига соединены со своими выходами. Информационный вход регистра 3 сдвига соединен с выходом суммы сумматора 4, первый и второй входы которого соединены соответст

5

0

5

0

5

0

0

5

венно с выходом регистра 3 сдвига и с вь1ходом элемента И 6, Первый вход элемента И 6 соединен с выходом первого разряда распределителя 28 импульсов блока 26 управления, выход п-го разряда которого соединен с первым входом элемента И 7, второй вход которого соединен с выходом переноса сумматора 4. Выходы разрядов с первого по т-й распределителя 29 импульсов блока 26 управления соединены соответственно с первыми входами элементов И 8(, 9, 10, 8, 9, Ющ, Выходы элементов И 10,, соединены соответственно с входами установки в единицу триггеров 5f, прямые выходы которых соединены соответственно с первыми входами элементов И П(-11,, Выход элемента ИЛИ 12 соединен с вторьм входом эле- мента И 6 и через элемент 15 задержки - с выходом элемента НЕ 16. Выходы элементов И 1Ц-11 соединены соответственно с входами элемента ИЛИ 13, Первый вход элемента ИЛИ 12 соединен через ключ 4 с прямьи вы- ходом триггера 37 блока. 26 управления. Выход регистра 1сдвига соединен с вторыми входами элементов И 84-8, Выход регистра 2 сдвига соединены с вторыми входами элементов И 9, Выходы элементов И у- 11, соединены соответственно с объединенными входами элементов И 8f и , и 9fy,, Входы элементов 7,-17 индикации соединены соответственно с выходами элементов И 11,-11, Входы элемента ИЛИ 12 с второго по Ст+1)-й соединены соответственно с информационными входами 18(-1.8i}j модели сети, информационные выходы 19,-19fp которой соединены соответственно с прямыми выходами триггеров 5,-5, входы установки в ноль которых соединены с первым выходом коммутатора 32 блока 26 управления. Выход элемента И 7 соединен с вт оры- ми в::одами элемён 1 ов И , третьи входы которых являются соответственно запрещающими входами 20п1 модели сети. Вторые входы элементов И ll llfr| являются соответственно индикационными входами модели сети, запрещающим выходом 22 которой является выход элемента НЕ 16, Индикационньм выходом 23 модели сети является выход элемента ИЛИ 13, Выходы элементов И 8,-81 являются соот3 .

ветс гвенно первой, группой управляющих выходов 2Д(-24 модели сети, второй группой управляющих выходов 25,- 25 которой являются соответственно

выходы элементов И 9 9,. Управляю-9

щие входы регистров 1-3 сдвига соединены соответственнос выходами (7.1), (7.2) и (7.3) коммутатора 35- блока 26 управления, выход элемента ИЛИ 38 которого соединен с входами ввода данных регистров 1-3 сдвига.

Выход генератора 27 импульсов (фиг. 2) соединен с входом распределителя 28 импульсов, выходы разрядов которого с первого по п-й, где п - количество разрядов представления чисел, соединены через коммутатор 31 с входами элемента ИЛИ 38. Выход п-го разряда распределителя 28 импульсов соединен с входоь распределителя 29 импульсов, выходы разрядов которого с первого по т-й, где m - количество ветвей модели сети, соединены через коммутатор 34 с входами элемента ИЛИ 40. Выход генератора 30 одиночных импульсов соединен с входом коммутатора 32, первый выхо которого соединен с входом установки в единицу триггера 36, с первым входом элемента ИЛИ 39 и с входом сброса счетчика 45. Вход запуска генератора 30 одиночных импульсов соединен через коммутатор 33 с выходом элемента НЕ 44, вход которого подключен к шине нулевого потенциала устройства. Второй выход коммутатора 32 соединен с входом установки в единицу 37, прямой выход которого соединен с первым входом элемента И.42./ Выход элемента ИЛИ 40 соединен с вторым входом элемента И 41, первый вход которого соединен с прямым выходом триггера 36. Выход элемента И 41 соединен с входом коммутатора 35. Выходы П -го разряда распределителя 28 импульсов и т-го разряда распределителя 29 импульсов соединены с входами элемента И 43, выход которого соединен с тактовым входом генератора 30 одиночных импульсов, с входом установки в ноль триггера 36 и с вторым входом элемента И 42. Вход установки в ноль триггера 37 соедине с выходом элемента ИЛИ 39, первый и второй входы которого соединены соответственно с входом 47 блока 26 управления и с первым выходом коммутатора 32. Выход элемента И 42 сое

15

0 ; 5

788774

динен с информационным входом счетчи-- ка 45, выходы разрядов которого соединены с входами группы элементов 46 индикации. Вход 47 блока 26 управления подключается к прямому выходу того из триггеров 5 модели сети, кот рый моделирует конечный узел графа дискретной дифференциальной игры.

- В качестве регистров 1-3 сдвига могут быть применены любые последовательные запоминающие устройства, либо динамические регистры сдвига на линиях задержки любых типов (маг- нитострикционных, ультразвуковой, электромагнитрюй и т.п.).Триггеры 5 и 37 - RS-типа, а триггер 36 - DF-типа.

Устройство работает следующим обfO

;

разом.

0

0 ; 5

5

0

5

0

Генератор 27 импульсов блока 26 управления (фиг. 2) вырабатывает последовательность тактовых импульсов частоты f, нз которых распределитель 5 28 импульсов формирует п последовательностей импульсов частоты f/n (где п - количество разрядов представления чисел), сдвинутых друг относительно друга на время 1/f.

Из последовательностей импульсов п-го разряда распределителя 29 им- . ., пульсов распределитель 29 импульсов формирует m последовательностей импульсов длительностью n/f, действующих с частотой f/т-п и сдвинутых друг относительно друга на время n/f.

В режиме ввода данных в регистры 1-3 сдвига коммутатором 32 блока 26 управления подключают выход генератора 30 одиночных импульсов к входу установки в единицу триггера 36. Регистры 1-3 сдвига содержат т-II двоичных разрядов и предназначены каждый для хранения m чисел по п разрядов. В регистры 1 и 2 записываются двоичные числа, соответствующие дискретным значе1П1ям управлений первого и второго игроков. В регистр 3 сдвига записывается- последовательный дополнительный код веса (длины) ветви графа, соединяющего два узла. Вес (длина) ветви графа выбирается равным максимальному приращению платы игр по управлению первого игрока. Дискретные значения управления первого игрока выбираются из условия максимизации прираи(ения платы игры вдоль ветви графа, соединяющего два узла, а управления второго

грока выбираются - из условия обесечения перехода состояния игры вдоль анной ветви графа.

Модель сети,.изображенная на иг. 1, моделирует m направленных ветвей графа, исходящих из одного уза и соединяющие этот узел с m узлаи (фиг. 3). Каждой ветви графа стаится в соответствие три числа - максимальное приращение платы игры, управление первого игрока, управление второго игрока.

С целью моделирования дерева модели ветви коммутируют между собой в соответствии с топологией решаемой задачи, например, информационные выходы 19 одной модели сети подключают к информационным входам 18 других моделей сети, запрещающие выходы 22 и индикационные выходы 23 которых соединяются соответстзенно с запрещающими входами 20 и индикационными входами 2 предыдущей модели сети. Неиспольз ованные информационные входы 18 моделей сети соединяются с шиной лопшеского луля. Пример дерева дискретной дифференциальной игры, изображен на фиг. За, а на фиг. 3 изобралсена моделирующая структура, содержащая три модели сети.

Исходные данною записыв 9,ются в регистры 1-3 сдвига модели сети следующим образом.

Коммутатором 35 блока 26 управления выбирают один из регистров сдвига, например регистр 1 сдвига. Коммутатор 35 подключает выход зле- мента И 4 блока 26 управления, к управляющему входу регистра 1 сдвига,С помощью коммутатора 31 на п направлений устанавливают п-разрядный двоичный код значения управления первого игрока. Коммутатор 31 подключает в единичных разрядах двоичного кода выходы соответствующих разрядов распределителя 28 импульсов к входам элемента ИЧИ 38, на выходе ,.которого формируется последовательный двоичный код.

Затем с помощью коммутатора 34 на m направлений выбирают номер ветви модели сети. Например, если выполняется ввод числа в пятую ветвь модели сети, то выход пятого разряда распределителя 29 импульсов.подключают к входу элемента ИЛИ 40, на выходе которого формируется импульсный сигнал длительн.остыо n/f, сов

20

25

2788776

падающий по фазе с временем сдвига с выхода регистра 1 под действием тактовых импульсов генератора 27 им пульсов п-разрядного двоичного кода

5- датя пятой ветви модели сети. - Ввод п-разрядного последовательного двои.чного кода управления первого игрока в регистр 1 сдвига осуществляет после подачи единичного

О сигнала с выхода элемента НЕ 44 через коммутатор 33 на вход запуска генератора 30 одиночных импульсов, который выдешяет из последовательности импульсов выхода элемента

5 И 43, действующих с частотой f/ni n, одиночный импульс, устанавливающий через коммутатор 32 триггер 36 в единичное состояние на время Ш П/f. Триггер 36 устанавливается в нулевое состояние следующим импульсом последовательности выхода элемента И 43. Триггер 36 в единичном состоянии открывает сигналом прямого выхода элемент И 41, через которьш на управляющий вход регистра 1 сдвига, поступает одиночный импульсный сигнал с выхода элемента ИЛИ 40, зада™ ющий номер ветви модели сети. Под действием тактовых импульсов генера30 тора 27 импульсов блока 26 управле- . ния последовательный двоичный код записывается с выхода элемента ИЛИ 38 последовательно во времени, начиная с младших разрядов, в регистр

35 1 сдвига во время действия на выходе элемента ИЛИ 40 импульса, задающего номер ветв:- модели сети.

Одиночный импульс генератора 30 одиночных импульсов через ко1«-1утатор

40 32 и элемент ИЛИ 39 устанавливает в нулевое состояние триггеры 5f-5, 36 и 37, а также счетчик 45.

Аналогичным образом в регистр 1 сдвига записывают последовательные

45 п-разрядные двоичные коды значений управлений первого игрока для всех ветвей модели сети с первой по m-io. Затем ко Е4утатором 35 подключают выход, элемента И 41 к упрашитюще50 му входу регистра-2 сдвига и таким же образом как в регистр 1 сдвига эацисьшают m двоичных кодов значений управлений второго игрока для всех ветвей модели сети с первой по

55 ш-ю.

После этого коммутатором 35 подключают выход элемента И 41 к управ ляющему входу регистра 3 сдвига, в

который аналогичным образом записывают П1 п-разрядпых дополнительных кодов максимальных значений платы игры для всех ветвей модели сети с первой по т-ю.5

В режиме моделирования коммутатором 32 блока 26 управления подключают выход генератора 30 одиночных импульсов к единичному входу триггера 37. Затем задают начальш-,1й узел 0 модели сети ключом.14 первого входа элемента Hrai 12 к прямому выходу триггера 37 блока 26 управления.

Пуск устройства осуществляют коммутатором 33, с помощью которого на -5 вход запуска генератора 30 одиночных импульсов подают единичный сигнал выхода элемента НЕ А4. Одиночный импульс генератора 30 одиночных импульсов поступает через коммутатор 32 на 20 единичный вход триггера 37, устанавливая его в единичное состояние. Сигнал прямого выхода триггера 37 открывает элемент И 42, через который на информацион-ный вход счетчика 45 начинает поступать последовательность импульсов выхода элемента И 43. Единичный сигнал прямого выхода триггера 37 поступает также через.ключ 14 на первый вход элемента ИЛИ 12, на иыхо- ЗО де которого формируется единичный ;сигнал, снимающий блокировку элемента 6.

Последовательность импульсов пер- вого разряда распределителя 28 импульсов, начинает поступать через элемент И 6 на вход сумматора 4, на другой вход которого под действием так- товых импульсов генератора 27 импуль- 40 сов с выхода регистра 3 сдвигаются дополнительные коды весов ветвей модели сети. Каждые m-n тактов дополнительные коды весов всех га ветвей модели сети увеличиваются на едини- 45 цу младшего разряда и с суммы сумматора 4 вновь записывается в регистр 3 сдвига. Спустя время Pjx хго П тактов, где PJ - наименьший вес (наименьшее из максимальных при- 50 ращений платы игры) из всех ветвей модели сети, принадлежаш ий, например, 1-й ветви, происходит переполнение в i-M слове регистра 3 сдвига и на выходе переноса суммдтора 4 формируется сигнал переноса из п-го разряда, который через элемент И 7 и элемент И 10 поступает на единич- ньш вход триггера 5; устанавливая

его в единичное состояние. Триггер 5j запоминает i-й номер ветви, принадлежащий дереву кратчайших путей и единичным сигналом прямого выхода, который с информационного выхода 19 поступает на один из информационных BXO;J OB 18 следующих моделей сети, возбулэдает вычислительный процесс поиска дерева кратчайших путей в моделях сети, подключенных к информационному выхо- ДУ. 19;.

Единичный сигнал, поступающий по одному из информационных входов 18 следующей модели сети, проходит на выход элемента ИЛИ 12 и через элемент 15 задержки - на такт, и элемент НЕ 16 поступает на запрещающий выход 22, который подключен к запрещающим входам 20 предьздущих моделей сети. Этот сигнал блокирует элементы И 10 в предыдущих моделях, запрещая этим установку в единичное состояние другим триггерам 5 в предыдущих моделях сети.

Далее вычислительный процесс распространяется аналогичным образом из одной модели сети к другим моделям сети до тех пор, пока не достигнет одного из триггеров 5„, модели- рующего конечный узел дерева дискрет ной дифференциальной игры. Особенность триггера 5, моделирующего конечный узел в модели сети, заключается в том, что его прямой выход соединен с входом 47 блока 26 управлени и соединен со своим индикационным входом 21. Единичный сигнйл триггера 5, моделирующего конечный узел, поступая на вход 47 блока 26 управления через элемент ИЛИ 39, устанавливает триггер 37 в нулевое состояние, в котором сигнал его прямого выхода блокирует элемент И 42. Процесс счета максимальных приращений платы игры вдоль ветвей, составляющих кратчайший путь, в счетчике 45 завершается. В счетчике 45 фиксируется минимальное значение платы игры, равный цене игры. Значение цены игры индицируется группой элементов 46 индикации. Единичный сигнал триггера 5, моделирующего конечный узел поступая на свой индикационный вход 2If, возб ждает процесс индикации оптимальной траектории и оптимальных управлений игроков вдоль оптимальной траектории следующим образом.

На выходе элемента И 11, подключенного к прямому выходу триггера 5„. моделирующего конечный узел, формируется сигнал логической единицы, который с помощью элемента j 7|т| индикации индицирует ветвь, нринадлежащего оптимальной траектории, и снимает блокировку с элементов И 8 и И 9,. Через элементы И 8 и И 9 по сигналам соответствующего т-го разряда распределителя 29 импульсов с выходов регистров 1 и 2 сдвига соответственно считы;ваются под действием тактовых импульсов генератора 27 импульсов последовательные двоичные коды оптимальных управлений первого и второго игроков, соответствующих ш-й ветви оптимальной траектории. Сигнал логической единицы с выхода элемента И HJ, соединенного с триггером 5,у, конечного узла, посту пает через элемент 1-ШИ 13 на нндика- ционньш выход 23, который соединен со всеми индикационными входами 21 других моделей сети, соединенных информационными выходами 19 с информационными входами 18 модеота сети, содержащей конечный узел. Сигнал лог ической единицы, поступающий на индикационные входы 21, проходит на выход того элемента И 11,, который открыт единичным сигналом прямого выхода триггера 5;, соответствующего ветви, принадлежащей дереву кратчайщнх

путей. Д.алее сигнал логической едини- 35 подключен к выходу второго элемента цы индикации ветвей, принадлежащих оптимальной траектории, распространяется аналогичным образом от конечного узла к начальному узлу дерева дискретной дифференциальной игры, индицируя ветви кратчайшего пути (оптимальную траекторию) и считы.вая двоичные коды оптимальных управлений первого и второго нгроксв.

40

ИЛИ блока управления, вход элемента НЕ блока управления подключен к шине нулевого потенциала, а выход элемента НЕ блока управления - к информационному входу третьего коммутатора блока управления, выход которого подключен к входу запуска генератора, одиночных импульсов блока управления, отличающееся..

Формула изобретения

- Устройство для моделирования графа, содержащее модель сети и блок управления, причем блок управления содержит генератор нмнульсои, первый распределитель импульсов, генератор одиночных импульсов, счетчик, два триггера, три элемента И, три элемента ИЛИ, пять коммутаторов, элемент НЕ и группу элементов инднкацин, а модель сети - элемент НЕ, два элемента И, два элемента РШИ, четыре группы элементов И, группу тригге

ров, группу элементов индикации, выход генератора импульсов блока уп- равлеггля подключен к входу первого распределителя импульсов блока управления, выходы которого с 1-го но п-й, где п - количество разрядов представления чисел, подключены к одноименным входам первого комь утатора блока управления, каждый выход которого подключен к одноименному входу первого элемента ИЛИ бло- |Ка унравления, первый вход первого элемента И блока управления подключен к прямому выходу первого тригге- 5 ра блока управления, выход каждого разряда счетчика блока управления подключен к входу одноименного эле- мента индикации грунпы блока управления, информационный вход счетчика блока управления подключен к выходу второго элемента И блока управления, первый вход которого подключен к прямому выходу второго триггера блока управления, выход генератора одиночных импульсов блока управления соединен с информационным входом второго коммутатора блока управления : первый вход которого подключен к входу установки в 1 первого триггера блока управления, а второй выход второго коммутатора блока управления подключен к входу установки в 1 второго триггера блока управления, вход установки в О которого

0

5

0

35 подключен к выходу второго элемента

40

ИЛИ блока управления, вход элемента НЕ блока управления подключен к шине нулевого потенциала, а выход элемента НЕ блока управления - к информационному входу третьего коммутатора блока управления, выход которого подключен к входу запуска генератора, одиночных импульсов блока управления, отличающееся..

45 тем, что, с целью расширения класса

.. решаемых задач за счет определения

кратчайщих путей и веса ветвей, в

модель сети введены три регистра

сдвига, су 1матор, ключ, элемент за50 держки, в блок управления - второй распределитель импульсов, выход генератора импульсов блока управления подключен к синхронизирующим входам первого, второго и .третьего регист55 ров сдвига модели сети, входы данных которых объединены и соединены с выходом первого элемента НЛИ блока управления, первый выход первого распределителя импульсов блока управле-

ния подключен к первому входу первого элемента И модели сети, а п-й выход первого распределителя импульсов блока управления - к первому входу второго элемента И модели сети, п-й выход первого распределителя импульсов блока управления подключен к входу второго распределителя им- пульсов блока управления и к первому, входу третьего элемента И блока управления, выход которого подключен к входу установки в О первого триггера блока управления, к тактовому входу генератора одиночных импульсов блока управления и к второму входу второго элемента И блока управления, выходы с первого по второго распределителя импульсогз блока управлен1 я, где m - количество ветвей модели сети, подключены к одноименным информационнььм входам четвертого коммутатора блока управления, каждый выход которого подключен к одноименному входу третьего элемента 1-ШИ блока управления; выход третьего элемента ИЛИ блока управления подключеп к второму входу первого элемента И блока управления, выхо которого подключен к информационным) входам пятого коммутатора блока управления, первый, второй и третий выходы которого подключены соотв-зтст BeiHio к управляющим входам первого, второго и третьего регистров сдвига модели сети, т-й выход второго распределителя импульсов соед1Н ен с вторым входом третьего элемента И блока управления, п.ервый выход второго коммутатора блока управления соединен с входом сброса счетчика блока управления, с первым входом второго элемента 1-ШИ блока управления и с входами установки в О триггеров грунпы модели сети, прямой выход второго триггера блока управ-- ления соединен с информационным входом ключа модели сети, выход которого подключен к первому входу первого элемента 1ШИ модели сети, остальные m входотз которого являются группой информационных входов модели сети, первые входы одноименных элементов И первой,второй и третьей групп модел сети объединены и подключены к одноименным выходам второго распредели- теля импульсов блока управления, вторые входы элементов И первой группы соединены с информационным вхо

O

5

0

дом первого регистра сдвига модели сети и подключены к выходу этого же рег истра сдвпга, выходы элементов И первой гругшы модели сети являются }зыходами определегп1я веса ветвей модели сети, вторые входы элементов И второй группы модели сети соедя1 ены с информационным входом второго регистра сдвгп а модели сети и подключены к выходу этого же регистра сдвига, выходы элементов И второй группы модели сети являются выходами опре- , деления перехода состояния игры модели сети, третьи входы i-x элементов И первой и второй групп модели сети соединены с входами i-x индикаторов группы модели сети и с L-M входом второго 1ШИ модели сети (где i 1,2,...,m) и подключены к выходу i-ro элемента И четвертой группы модели сети, выход второго элемента ГШИ модели сети является индикационным выходом модели сети, 5 выход первого элемента ИЛИ модели сети подключен к второму входу первого элемента И модели сети и-к входу элемента задерлски модели сети, выход .которого подключен к входу элемента НЕ модели сети, выход которого является выходом запрета модели сети, выход первого элемента И модели сети подключен к первому входу сумматора модепи сети, второй вход которого подключен к выходу третьего регистра сдвига модели сети,, выход суммы сумматора модели сети подключен к ин(1)Ормацп-он1юму входу третьего регистра сдвих а модели сети, гг , выход переноса сумматора модели сети - к второму входу второго элемента И модели сети, выход которого подключен к вторым входам элементов И третьей группы модели сети, третьи входы которых являются группой запрещающих входов модели сети, а выход каждого из элемептов И третьей

0

5

0

5

группы модели сети подключен к входу установки в 1 одноименного триггера группы модели сети, выход которого подключен к первому входу одноименного элемента И четвертой группы нэдетп сети и является одноименным ннфop aцюнным выходом группы инфор- мационнь-1х выходов модели сети, вторые входы элементов И четвертой гругшы модели сети являются группой ипдпкаци.онных входов модели сети, вы13127887714

ход последнего триггера группы моде- второго элемента ИЛИ блока управле- / ли сети подключен к второму входу

ння.

второ

ння.

1вП) Wl) 5lm) 21 23

II I II

I I I

Медаль cemLi //- 7

/5Й /9//

fSimMEM

ФОР 969

J8( J8(m} 22 Z3 LlllJ™.™™L.l,

l8inmz) 18(т}

I 1

L

Модель сети fi°-2.

ij.j I iTTl TT 5//МгМт; ЫшгШг. гпШгМщ 00 о A 6 обо

Составитель Т. Сапунова Редактор В. Иванова Техред А.Кравчук Корректор И. Муска

Заказ 6841/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открултий 113035, Москва, Ж-35, Раушская наб., ц. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования графов | 1989 |

|

SU1709346A2 |

| Устройство для решения игровых задач на вычислительных сетях | 1982 |

|

SU1104522A1 |

| Устройство для моделирования графов | 1985 |

|

SU1315993A1 |

| Устройство для моделирования графов | 1986 |

|

SU1399755A1 |

| Устройство для моделирования графов | 1984 |

|

SU1246110A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Устройство для моделирования графов | 1986 |

|

SU1377867A2 |

| Устройство для контроля переходных режимов объекта | 1989 |

|

SU1817062A1 |

| Устройство для моделирования ветви графа | 1986 |

|

SU1348847A1 |

| Программно-временное устройство | 1978 |

|

SU805257A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам обработки информации специального назначения, и может быть использовано как специализированное вычислительное устройство для научно-исследовательских целей и моделирования дискретных дифференциальных игр, а также д.пя управления некоторыми технологическими процессами в различных отраслях нроьшшленности. Це лью изобретения является расширение класса моделируемых дифференциальных игр и упрощение устройства. Усг- ройство содер :ит модель сети и блок управления. Модель сети включает в себя три регистра сдвига, сумматор, группу триггеров, два элемента И, четыре группы элементов И, два элемента ШШ, ключ, элемент задержки на такт, элемент НЕ и группу элементов индикации. Блок управления содержит , генератор импульсов, два распределителя импульсов, генератор одиночных импульсов, пять коммутаторов, два триггера, три элемента ИЛИ, три элемента И, элемент НЕ, счетчик и группу эле ментов И -щикации. -3 -ил. i СЛ ю ч1 00 00 ч

| Авторское свидетельство СССР № 758179, кл, G Об F 15/20, 1980, Авторское свидетельство СССР № П04522, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-04-23—Подача