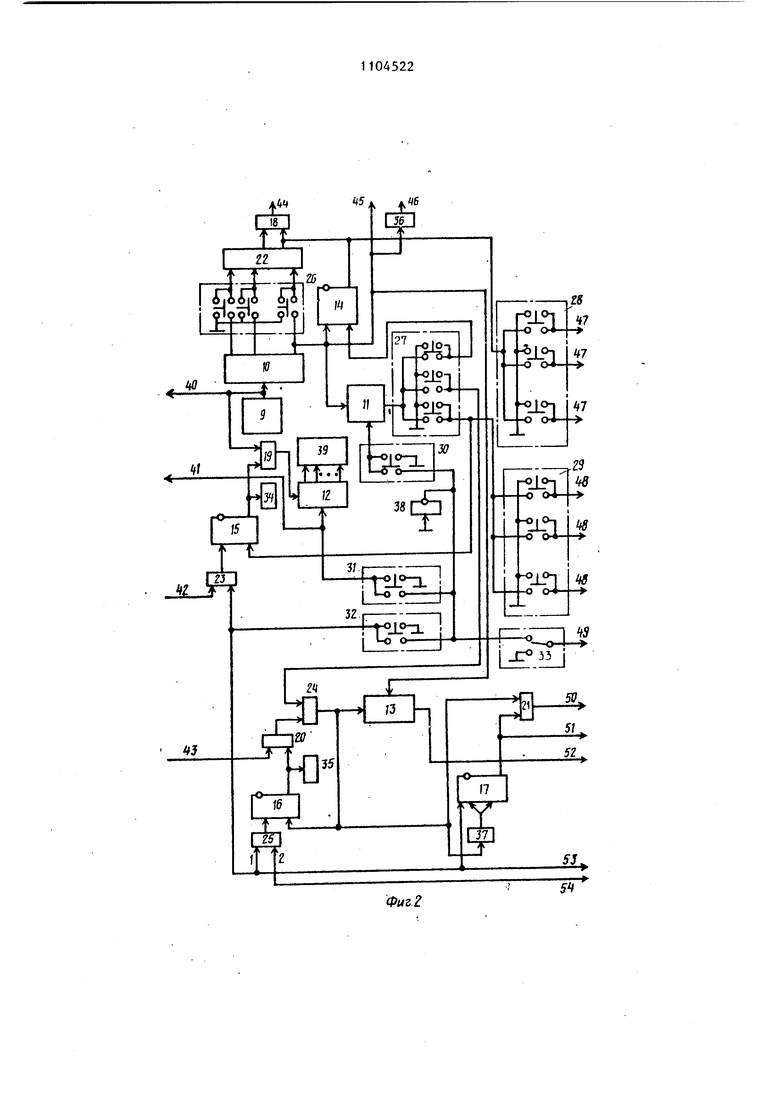

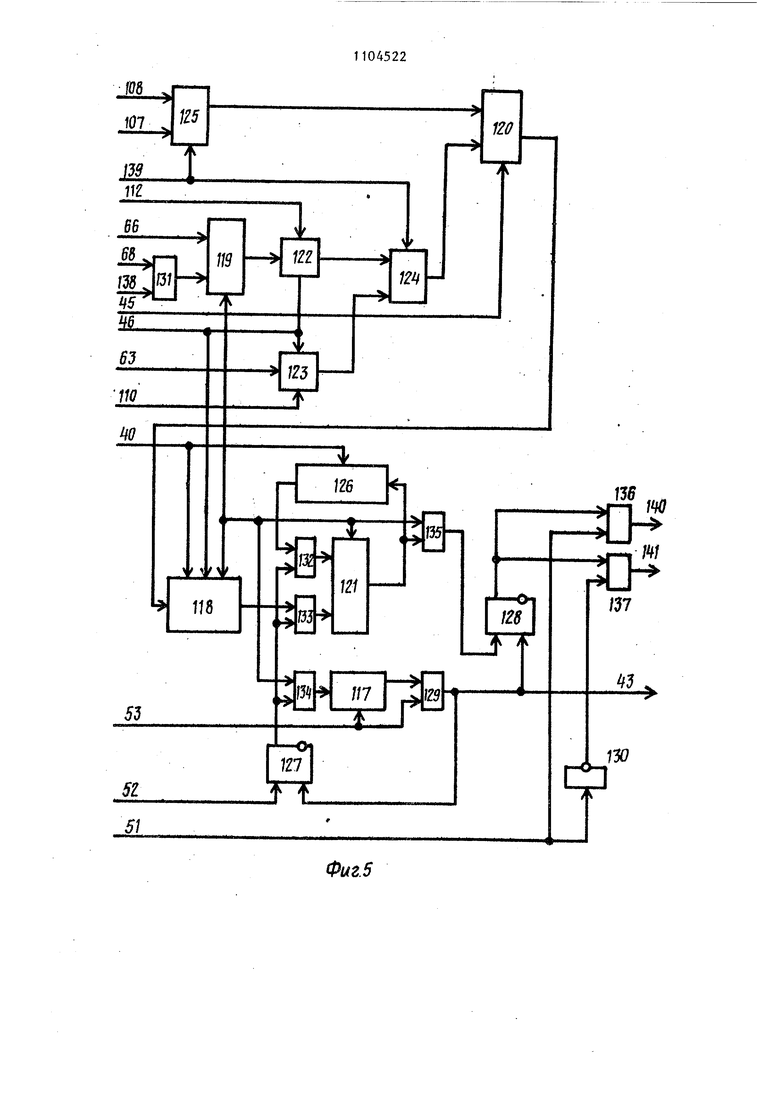

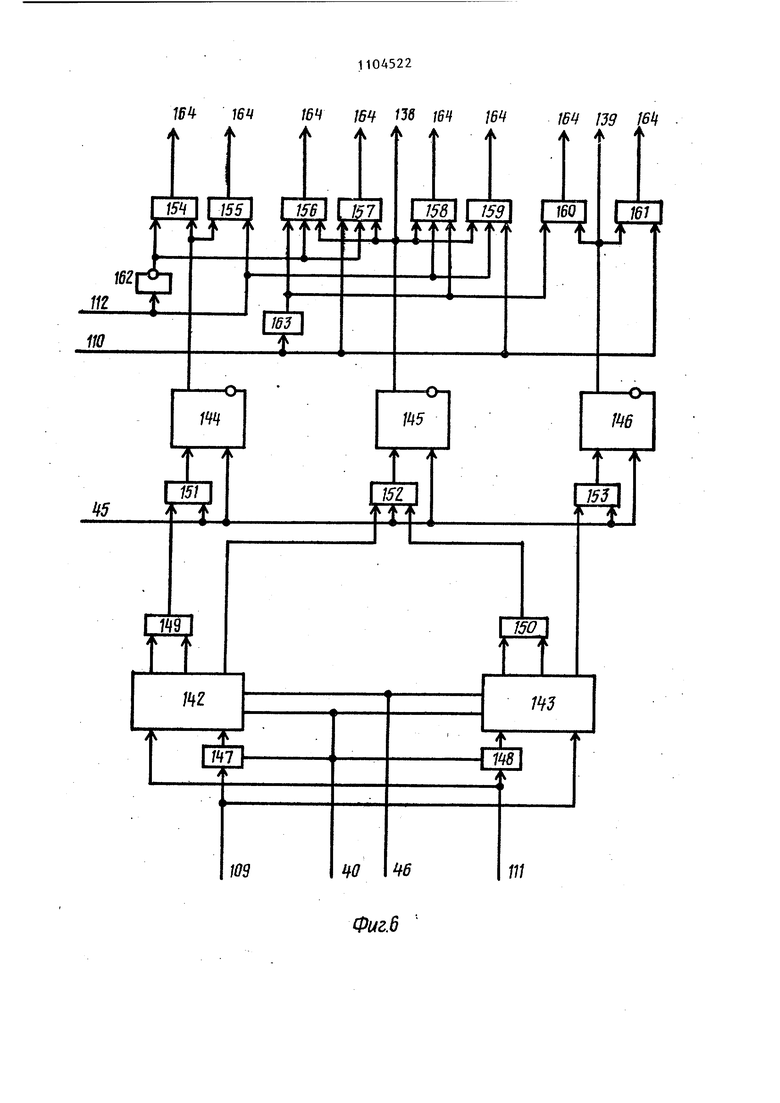

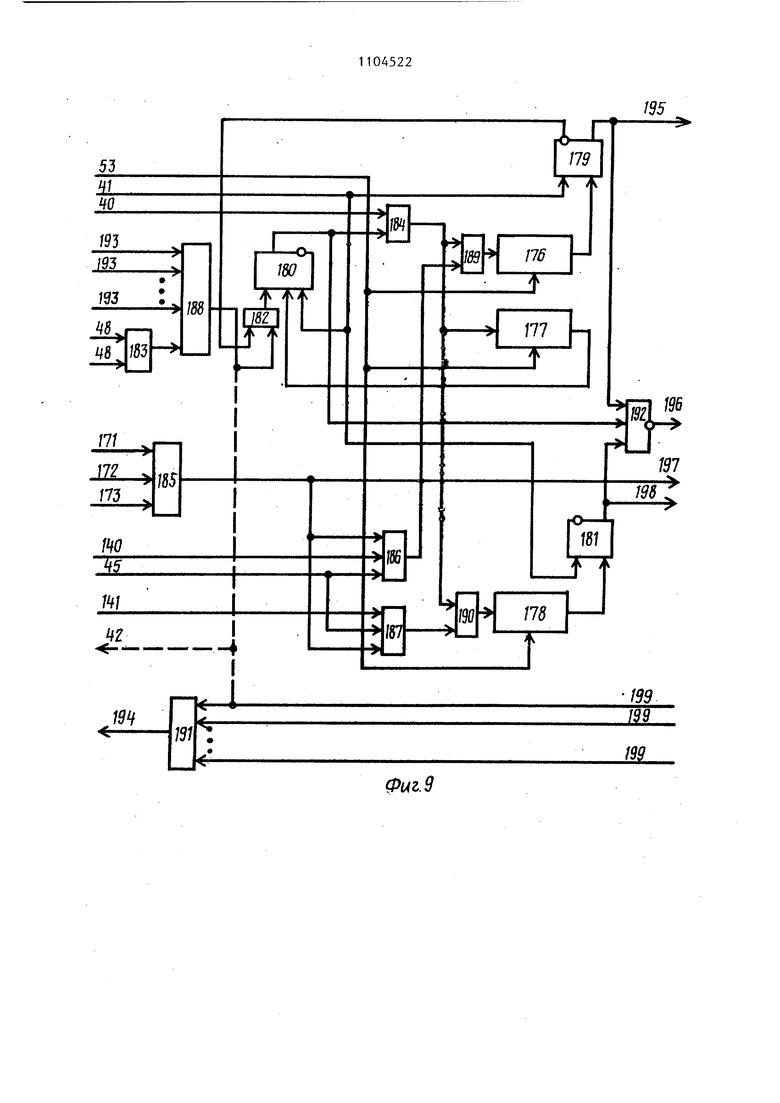

ми схем сравнения и элементов задержки селектора ветви сети и вторь1ми входами третьих элементов И модулей узлов сети, выходы распределителя импульсов блока управления через группу входов первого коммутатора блока управления соединены с соответствующими входами первого элемента ИЛИ блока управления, выход Г1-ГО разряда распределителя импульсов блока управления соединен с тактовым входом генератора одиночных Импульсов, входом синхронизации регистра сдвига блока управления, нулевым входом первого триггера блока управления, входом первого элемента задержки блока управления, входом сброса сумматора блока формирования параметров управления, входами сброса сумматоров, формирователей модуля и нулевыми входами триггеров блока формирования приращений координат, входами сброса сумматоров, первым входом сброса формирователя модуля, первыми входами первого и второго элементов И блока формирования приращений функционала, вторыми входами первого и третьего элементов И, третьим входом второго элемента И и первыми входами триггеров селектора ветви сети, вторыми входами пятого и шестого элементов И каждой модели узла сети, выход первого элемента ИЛИ блока управления соединен с первым входом второго элемента И блока управления, второй вход которого подключен к единичному вьсходу первого триггера блока управшения, входы группы элементов индика ции блока управления соединены с выходами счетчика блока управления, информационный вход которого соединен с выходом первого элемента И блока управления, второй вход которого соединен с входом первого элемента индикации блока управления и подключен к единичному выходу второго триггера блока управления, единичный выход третьего триггера блока управления соединен с входом рторого элемента индикации блока управления и первым входом третьего элемента И блока управления, выход которого соединен с первым входом третьего элемента ИЛИ блока управления, выход которого подключен к информационному входу регистра сдвига блока управления, ёдиничHotr/ входу третьего триггера блока управления, первому входу четвертого элемента И блока управления и через

второй элемент задержки блока управления - к счетному входу четве.ртого триггера блока управления, единичный выход которого соединен с вторым входом четвертого элемента И блока управления, выход генератора одиночных импульсов блока управления соединен с первым входом второго коммутатора блока управления, первый выход которого подключен к единичному входу первого триггера блока управления, второй выход - к второму входу третьего элемента ИЛИ блока управления, а третий выход - к единичному входу второго триггера блока управления и первому входу четвертого коммутатора блока управления, первый вход третьего коммутатора блока управлени подключен к единичному выходу первого триггера блока управления, вход первого коммутатора блока управления и вторые входы второго, третьего, четвертого, пятого, шестого, седьмого и восьмого коммутаторов блока управления соединены с общей шиной устройства, выходы третьего коммутатора блока управления подключены к управляющим входам соответствующих регистров сдвига блока формирования параметров движения и блока формирования параметров управления, выходы четвертого коммутатора блока управления соединены с входами первых элементов И моделей узлов сети, выход пятого коммутатора блока управления подключен к входу запуска генератора одиночных импульсов, вход элемента НЕ блока управления соединен с общей шиной устройства, а выход подключен к первым входам пятого шестого, седьмого и восьмого коммутаторов блока управления, выход шестого коммутатора блока управления соединен с входом сброса счетчика блока управления, нулевыми входами (первых и третьих триггеров моделей узлов и вторыми нулевыми входами вторых триггеров моделей уэлов, нулевыми входами третьих триггеров моделей ветвей, выход сельмого коммутатора блока управления соединен с первыми входами второго и четвертого элментов ИЛИ блока управления, нулевым входом четвертого триггера блока управления , входами управления регистров сдвига блока формирования приращния координат, входом сброса счетчик блока формирования приращений функци нала, первым входом элемента ИЛИ блока формирования приращений функционала, входами сброса счетчиков селектора узла сети, входами сброса счетчиков моделей узлов и нулевыми входами первого и второго триггеров моделей ветвей, выход восьмого коммутатора блока управления соединен с управляющим входом первого формирователя дополнительного кода блока формирования параметров управления, нулевой вход второго триггера блока управления соединен с выходом второго элемента ИЛИ блока управления, второй вход которого Соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента ИЛИ модели конечйого узла сети, второй вход третьего элемента И блока управления соединен с нулевыми входами первого и второго триггеров блока формирования приращений функционала и подключен к выходу элемента РШИ блока формирования приращений функционала, выход второго элемента И блока управления соединен с входами ввода данных регистров сдвига блока формирования параметров движения и блока формирования параметров управления, выход первого элемента задержки блока управления соединен с входами сброса формирователей дополнительного кода блока формирования параметров управления, с входами сброса формирователей дополнительного кода и вторыми входами сброса формирователей модуля блока формирования приращений координат, с входами сброса блоков дополнительного кода и вторым входом сброса формирователя модуля блока формирования приращений функционала и с входами сброса схем сравнения селектора ветви сети, выход четвертого элемента И блока управления соединен с единичным входом первого триггера блока формирования приращений координат и информационным входом первого счетчика селектора узла сети, единичный выход четвертого триггера блока управления подключен к входу управления второго формирователя дополнительного кода блока формирования параметров управления, к первому входу седьмого элемента И и через элемент НЕ - к первому входу третьего элемента И блока формирования приращений функционала, выход регистра сдвига блока управлениясоединен с единичным входом первого триггера блока формирования приращений функционала, второй вход четвертого

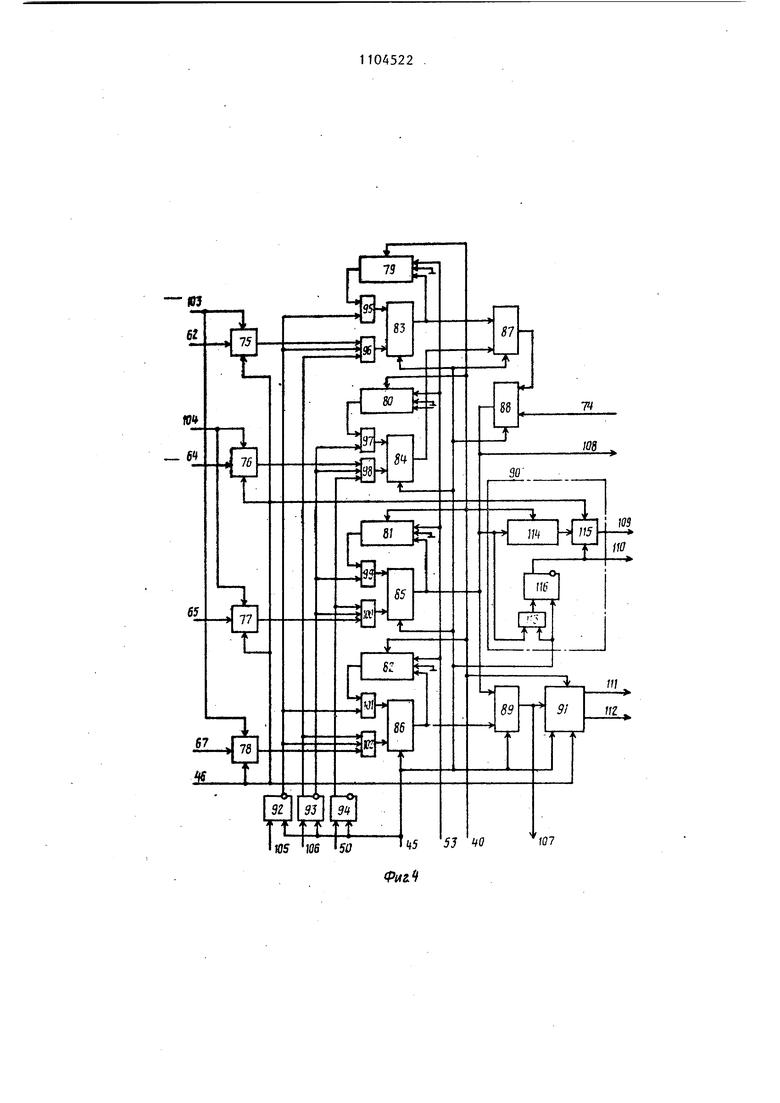

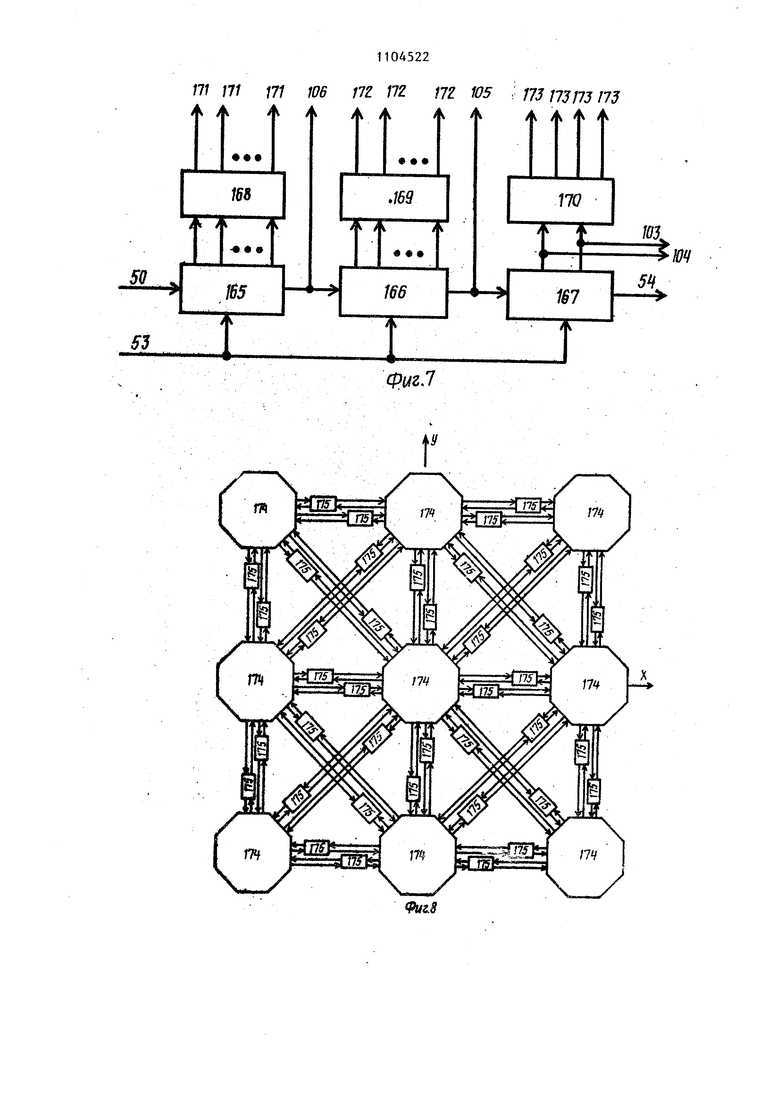

элемента ИЛИ блока управления подключен к выходу третьего счетчика селектора узла сети, выход первого регист.ра сдвига блока формирования параметров движения соединен с информационным входом первого элемента задержки этого же блока и информационным входом первого Ф9рмирователя дополнительного кода блока формирования приращений функционала, вьтходы первого, третьего и четвертого регистров сдвига блока формирования параметров движения соединены со своими информационными входами через соответственно первый, второй и третий элементы задержки этого же блока, выход второго регистра сдвига блока формировани параметров движения соединен со своим информационным входом и информационным входом второго формирователя дополнительного кода блока формирования приращений координат, выходы первого, второго и третьего элементов задержки блока формирования параметров движения соединены соответственно с информационными входами первого, третьего и четвертого формирователей дополнительного кода блока формирования приращений координат, выходы третьего и четвертого регистров блока формирования параметров движения соединены соответственно с первым входом первого сумматора и первым входом четвертого элемента И блока формирования приращений функционала, выход первого регистра сдвига блока формирования параметров управления соединен с его информационным входом и первым информационным входом сумматора блока формирования параметров управления, выход которого подк.шочен к информационному входу второго формирователя дополнительного кода-этого же блока, выход второго регистра сдвига блока формирования параметров управления соединен с его информационным входом первого формирователя дополнительного кода блока формирования параметров управления, выход которого подключен к второму информационному входу сумматора блока формирования параметров управления, выход второго формирователя дополнительнсЭго кода блока формирования параметров управления подключен к первому информационному входу первого сумматора блока формирования приращений координат, информациоггные выходы первого, второго, третьего и четвертого

ормирователей дополнительного кода лока формирования приращений кооринат соединены с первыми входами соответственно первого, второго, третьего и четвертого элементов И блока формирования приращений координат, управляющие входы первого и четвертого формирователей дополнительного кода блока формирования приращений координат соединены с первым выходом третьего счетчика селектора модели узла сети второй выход которого подключен к управляющим входам второго и третьего

формирователей дополнительного кода блока формирования приращений координат, единичный выход первого триггера блока формирования приращений координат соединен с Входами второго и третьего элементов И блока формирования приращений координат, нулевой выход второго триггера блока формирования приращений координат подключен к первому ВХОДУ пятого элемента И, третьему входу второго элемента И, первому входу щестого элемента И и к третьему входу третьего элемента И блока формирования приращений координат, единичный выход второго триггера блока формирования приращений координат соединен с вторыми входами первого и четвертого элементов И бло- ка формирования приращений координат, нулевой выход третьего триггера блока формирования приращений координат подключен к третьим входам первого и четвертого элементов И и первым входам седьмого и восьмого элементов И блока формирования приращений координат, входы седьмого, пятого, шестого и восьмого элементов И блока формирования приращений координат соединены соотве тственно с выходами первого второго, третьего и четвертого регистров сдвига блока формирования приращений координат, входы ввода данных регистров сдвига блока.формирования приращений координат соединены с общей шиной устройства, входы третьего, четвертого, пятого и шестого сумматоров блока формирования приращений координат соединены орответственно с выходами седьмого и первого,пятого и второго, шестого и третьего, восьмого и четвертого элементов И блока формирования приращений координат, выход третьего сумматора блока формирования приращений координат подключен к информационному входу первого регистра сдвига и первому входу второго сумматора блока формирования приращений координат, выход которого соединен с вторым входом первого сумматора, а второй вход - с выходом четвертого сумматора и информационным входом, второго регистра сдвига блока формирования приращений координат, выход пятого сумматора блока формирования приращений координат подключен к информационному входу третьего регистра сдвига и первому входу седьмого сумматора,выход первого сумматора блока формирования приращений координат подключен к информационному входу первого формировате ря модуля блока формирования приращений координат и первому входу второго коммутатора блока формиро-. вания приращений функционала, выход шестого сумматора блока формирования приращений координат соединен с информационным входом четвертого регистра сдвига и вторым входом седьмого сумматора блока формирования приращений координат, выход которого соединен с информационным входом второго формирователя модуля блока формирования приращений координат и вторым входом второго коммутатора блока формирования приращений функционале, первьй выход первого формирователя модуля блока формирования приращений координат подключен через первый элемент задержки селектора ветви сети к второму входу первой схемы сравнения и непосредственно к первому входу второй схемы сравнения селектора ветви сети, второй выход первого формирователя модуля блока формирования приращений координат соединен с управляющим входом первого формирователя дополнительного кода блока формирования приращений функционала, входом второго элемента НЕ селектора ветви сети, третьими входами четвертого и шестого элементов И и вторым входом восьмого элемента И селектора ветви сети, первый выход второго формирователя модуля блока формирования приращений координат подключен к первому входу первой схемы сравнения селектора ветви сети и через второй элемент задержки селектора ветви сети соединен с вторым входом второй схемы сравнения селектора ветви сети, второй выход второго формирователя модуля блока формирования приращений координат соединен с управляющим входом второго формирователя дополнительного кода блока формирования приращений функционала, с входом первого элемента НЕ и вторыми входами второго, пятого и шестого элементов И селектора ветви сети, единичные входы второго и третьего триггеров блока формирования приращений координат соединены соответственно с выходами первого и второго счетчиков селектора узла сети, первьй и второй входы третьего сумматора блока формирования приращений функционала соединены соответственно с выходами первого и второго коммутаторов этого же блока, выход третьего сумматора блока формирования приращений функционала подключен к информационному входу формирователя модуля функционала блока формирования приращений функционала, выход которого соединен с первым входом пятого элемента И блока формирования гфиращений функционала, выход пятого элемента И блока формирования приращений функционала соединен с первым входом второго сумматора блока формирования приращений функцирйапа, выход которого подключен к второму входу второго элемента И и к входу регистра сдвига блока формирования приращений функционала, выход регистра сдвига блока приращений функционала соединен с первым входом щестого элемента И этого же блока, выход которого соединен с вторым входом второго сумматора блока формирования приращений функционала, единичный выход первого триггера блока формирования приращений функционала соединен с вторыми входами первого, пятого и щестого элементов И блока формирования приращений функционала, выход первого элемента И блока формирования приращений функционала соединен с информационным входом счетчика блока формирования приращений функционала, выход которого подключен к второму входу элемента ИЛИ этого же блока, выход второго элемента И блока формирования приращений функционала соединен с единичным входом второго триггера блока формирования приращений функционала, выход которого подключен к вторым входам третьего и седьмого элементов И блока формирования приращений функционала, выход третьего элемента И блока формирования приращений функционала соединен с третьими входами шестых элементов И

моделей узлов и первыми входами третьих элементов И моделей ветвей, выход четвертого элемента И блока фомирования приращений функционала подключен к второму входу первого сумматора блока формирования приращений функционала, выход которого соединен с информационным входом второго формирователя дополнительного кода блок формирования приращений функционала, выход которого подключен к первому входу первого коммутатора блока формрования приращений функционала, второй вход которого соединен с выходом первого формирователя дополнительного кода блока формирования приращений функционала, управляющие входы первого и второго коммутаторов блока формирования приращений функционала подключены к единичному выходу; третьго триггера и первым входам седьмого и восьмого элементов И селектора ветни сети, второй вход четвертого элемента И блока формирования приращений функционала соединен с единичным выходом второго триггера и первыми входами третьего четвертого, пятого и щестого элементов И селектора ветви сети, выход седьмого элемента И блока формирования приращений функционала подключен к третьему входу пятых элементов И моделей узлов и первому входу вторых элементов И модлей ветвей, первый и второй выходы первой и второй схем сравнения селектора ветви сети подключены к первому и второму входам соответственно первого и второго элементов ШШ селектора ветви сети, выходы первого и второго элементов ИЛИ селектора ве1- ви сети подключены соответственно к первым входам первого и второго элементов И селектора ветви сети, третьи выходы первой и второй схем сравнения селектора ветви сети соединены соответственно с вторым входом второго и первым входом третьего элементов И селектора ветви сети, выходы первого, второго и третьего элементов И селектора ветви сети соединены соответственно с вторыми входами первого, второго и третьего триггеров селектора ветви сети, единичцый выход первого триггера селектора ветви сети подключен к первым входам первого и второго элементов И селектора ветви сети, выход первого элемента НЕ селектора ветви сети соединен с вторыми входами первого.

третьего и четвертого элементов И селектора ветви сети, выход второго элемента НЕ селектора ветви сети соединен с третьими входами третьего и пятого элементов И и вторым входом седьмого элемента И селектора ветви сети, выходы первого, второго, треtbero, четвертого, пятого, шестого, седьмого и восьмого элементов И селектора ветви сети соединены с первыми входами первых элементов И соответствующих моделей ветвей, разрядные выходы первого и второго сЧетчиков селектора узла сети соединены с входами первого и второго дешифраторов селектора узла сети, вьзсод переполнения первого и второго счетчиков селектора узла сети соединены соответственно с информационными входами второго и третьего счетчиков селекторд узла сети, первый и второй выходы третьего счетчика селектора узла сети подключены к первому и второму входам третьего дешифратора селектора узла сети, выходы первого, второго и третьего дешифратог ров селектора узла сети соединены соответственно с первыми, вторыми и третьими входами четвертых элементов И соответствующих моделей узлов, выход первого элемента И модели узла соединен с первым входом первого элемента ИЛИ модели узла, выход которого соединен с первым входом второго элемента И модели узла, нулевые выходы первого и третьего триггеров модели узла соединены с вторым и третьим входами второго элемента И Модели узла, выход которого подключен к единичному входу второго триггера модели узла, единичный выход которого соединен с первым входом третьего элемента И и вторым входом элемента ИЛИНЕ модели узла, первый вход которого соединен с единичным выходом первого триггера модели узла и первым входом четвертого элемента И соответствующей модели ветви, выход третьего элемента И модели узла соединен с первыми входами второго и третьего элементов ИЛИ и информационным входом второго счетчика модели узла, выход четвертого элемента И модели узла соединен с первыми входами пятого и шестого элементов ИЛИ модели узла ц вторым входом первого элемента И соответствующих моделей ветвей, выход пя;Того элемента И модёл и узла подключен к второму входу второго элемента ИЛИ

модели узла,, выход которого соединен с информационным входом первого счет чика модели узла, выход первого счетчика модели узла подключен к единичному входу первого триггера модели узла, выход второго счетчика моделя узла подключен к первому входу сброса второго триггера модели узла, выход шестого элемента И модели узла подключен к второму входу третьего элемента ИЛИ модели узла, выход которого соединен с информационным входом третьего счетчика модели узла, выход третьего счетчика модели узла подключен к единичному входу третьего триггера модели узла, единичный выход которогосоединен с третьим входом элемента ИЛИ-2НЕ модели узла и первым входом пятого элемента И соответствующей модели ветви, выход элемента ИЛИ-НЕ модели узла соединен с первым входом шестого элемента И сортветствующей модели ветви, входы с второго по К-и первого элемента ИЛИ модели узла соединены с единичными выходами третьих триггеров соответствующих моделей ветвей ( - число смежных моделей ветвей), входы с второго ПО -и четвертого элемента ИЛИ модели узла со.:дийены с выходами девятых элементов И соответствующих моделей ветвей, выход четвертого элемента ИЛИ модели узла соединен с первым входом девятых элементов И соответствующих моделей ветвей, выход первого элемента И модели ветви соединен с вторыми входами второго и третьего элементов И модели ветви, выходы которых подключены к единичным входам соответственно первого и второго триггеров модели ветви, единичный выход первого триггера модели ветви соединен с вторым входом четвертого и первым входом.седьмого элементов И модели ветви, единичный выход второго триггера модели ветви соединен с вторым входом пятого и первым входЬм восьмого элементов И модели ветви, выходы четвертого и пятого элементов И модели ветви подключены к входам элемента ИЛИ модели ветви, выход которого соединен с вторым входом шестого элемента И модели ветви, выход шестого элемента И модели ветви соединен с единичным входом третьего триггера модели ветви, единичный выход которого подключен к второму входу девятого элемента И модели ветви, выходы седьмого и восьмого элементов И модели ветии соединены соответственно с входами первого и второго элементов индикации модели ветви, выход девятого элемента И модели ветви соединен и вторыми входами седьмого и восьмого элементов И и входом третьего элемента индикации модели ветви.

2. Устройство по п. 1, отличающееся тем, что формирователь модуля содержит регистр сдвига, формирователь дополнительного кода, триггер и элемент И, причем информационный вход формирователя модуля соединен с информационным входом регистра сдвига и первым входом элемента И, второй вход которого

объединенный с нулевым входом триггера, является первым входом сброса формирователя модуля, выход элемента И соединен с единичным входом триггера, единичный выход которого соединен с управляющим входом формирователя дополнительного кода и является вторым выходом формирователя модуля, синхронизирующий вход регистра сдвига является синхронизирующим входом формирователя модуля, информационный выход регистра соединен с информационным входом формирователя дополнительного кода, а вход сброса формирователя дополнительного кода является вторым входом сброса формирователя модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Устройство для моделирования графа | 1985 |

|

SU1278877A1 |

| Устройство для сопряжения электронно-вычислительной машины с табло индикации | 1984 |

|

SU1211739A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

| Устройство для считывания графической информации | 1981 |

|

SU1005104A2 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

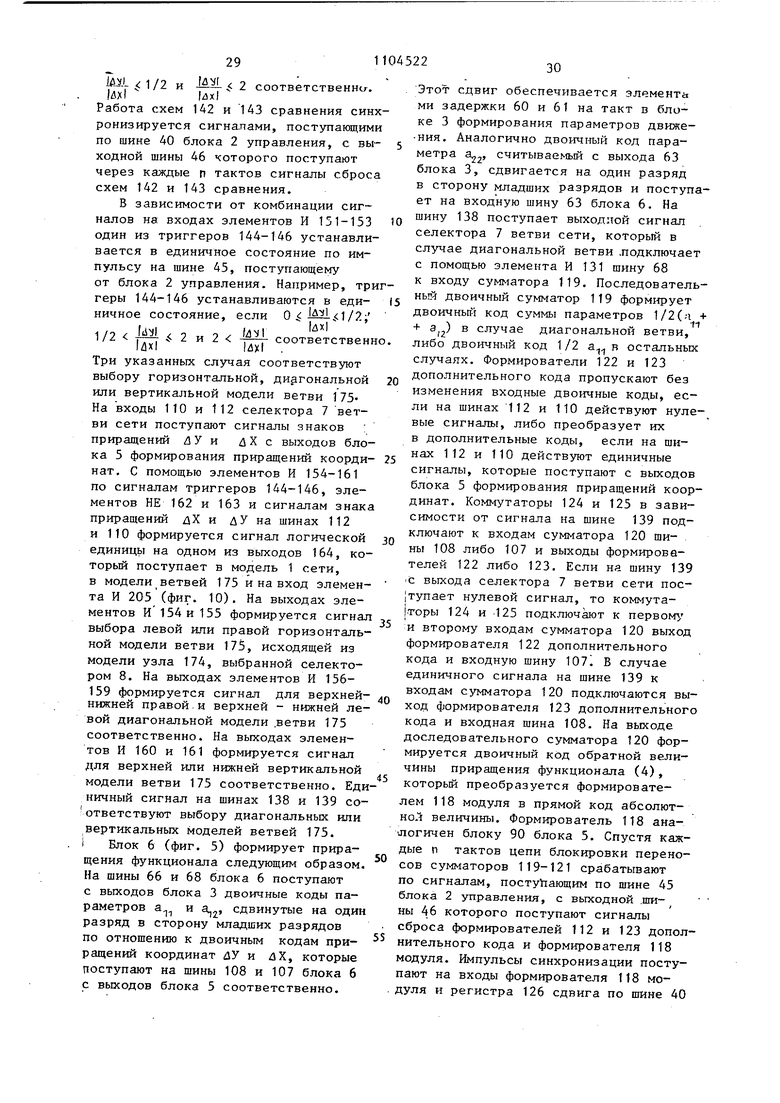

SU1161951A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

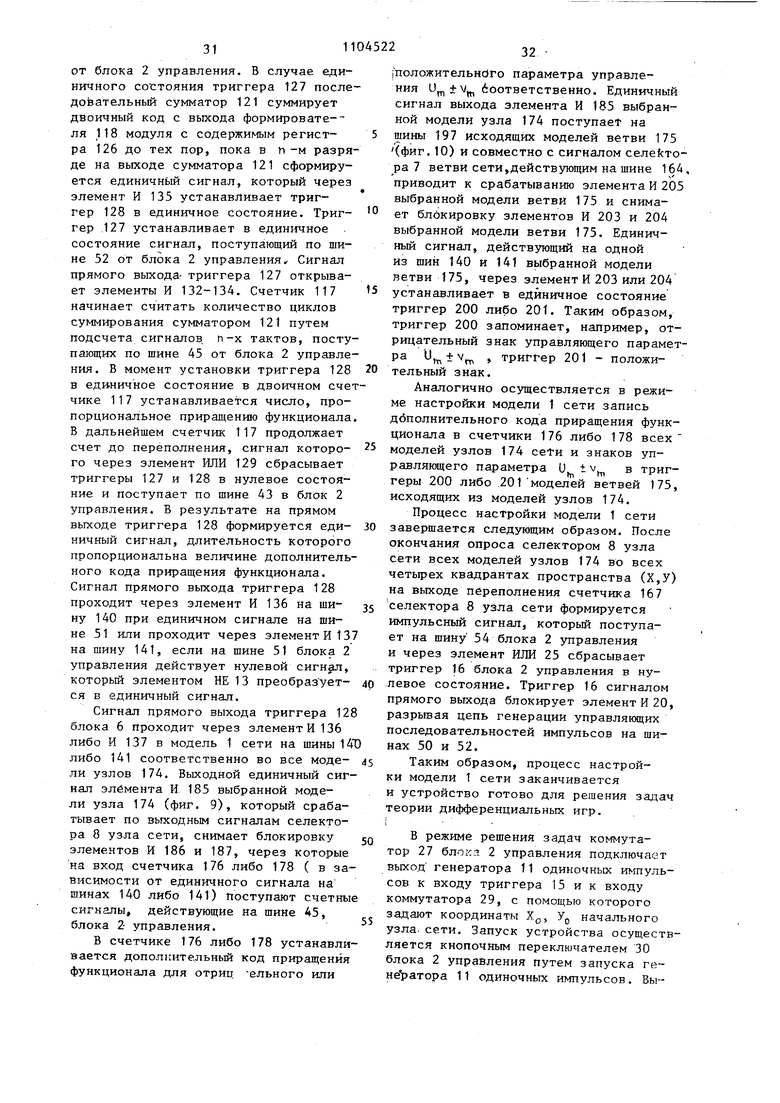

|

SU1509925A2 |

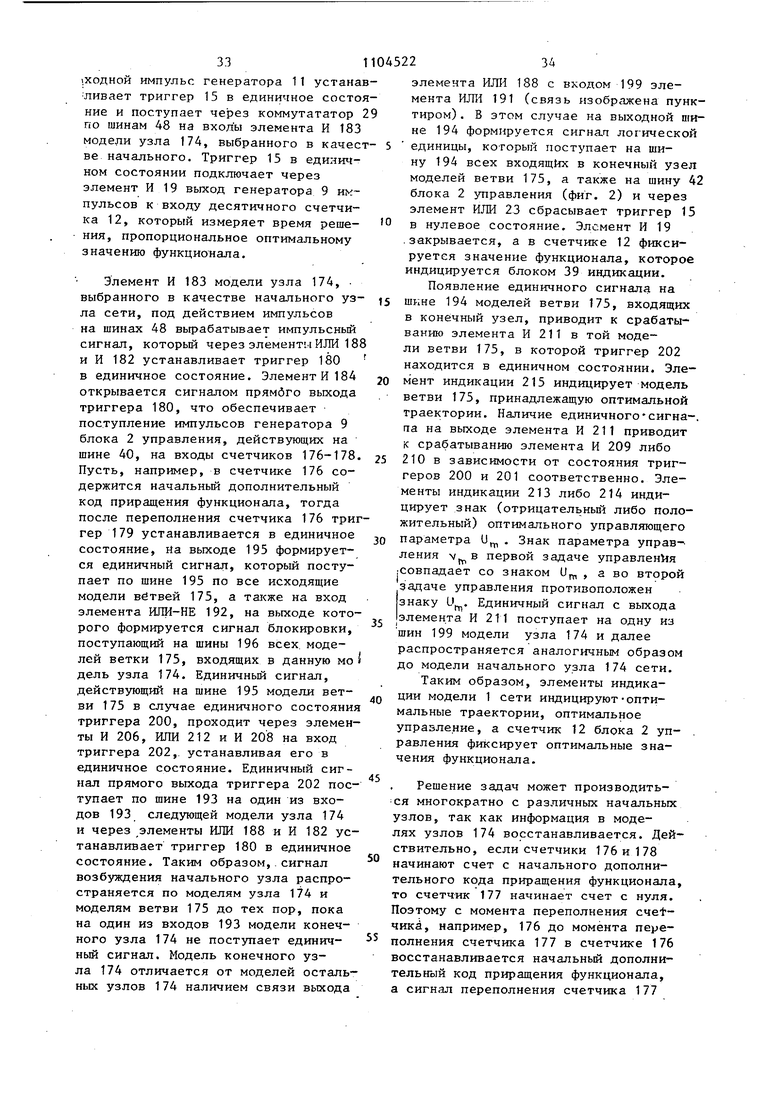

| Устройство для исследования связности сетей | 1972 |

|

SU443394A1 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1128272A2 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1119024A1 |

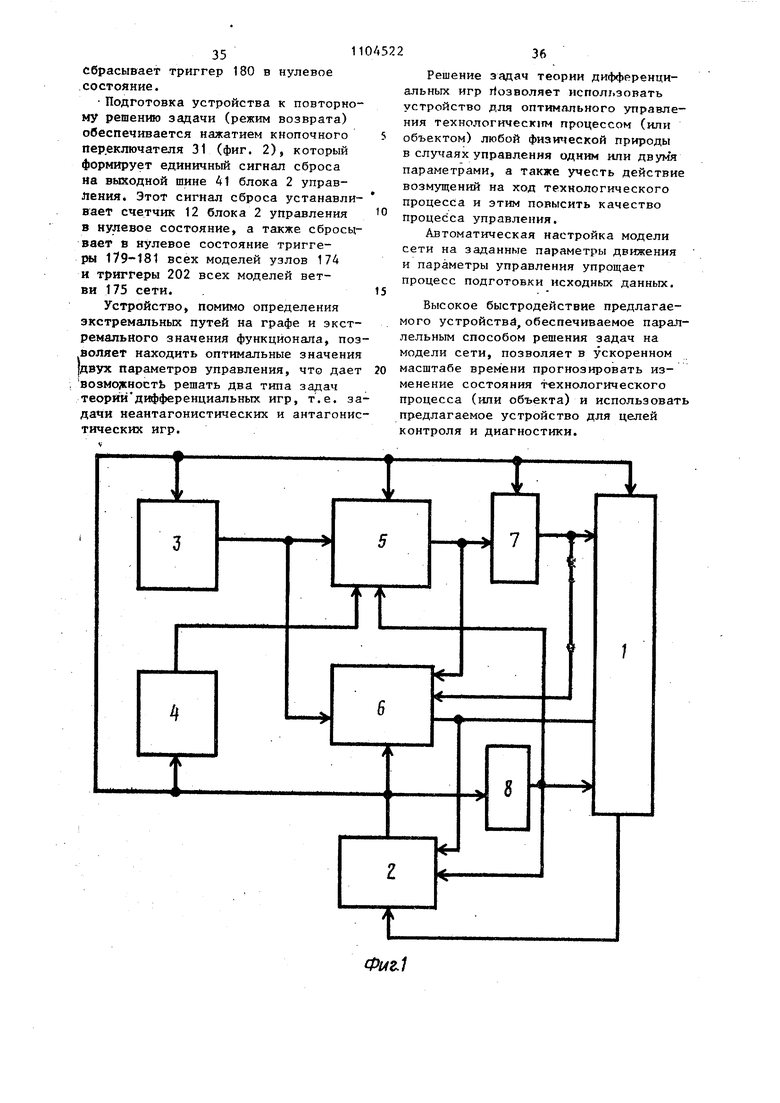

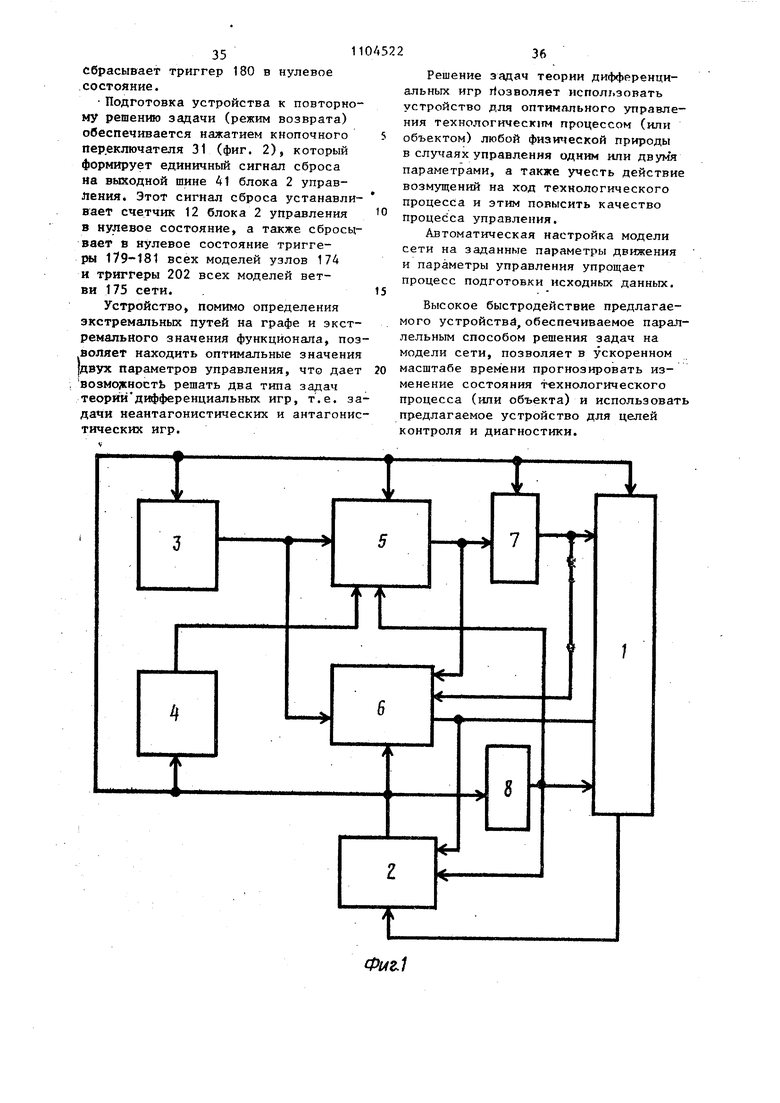

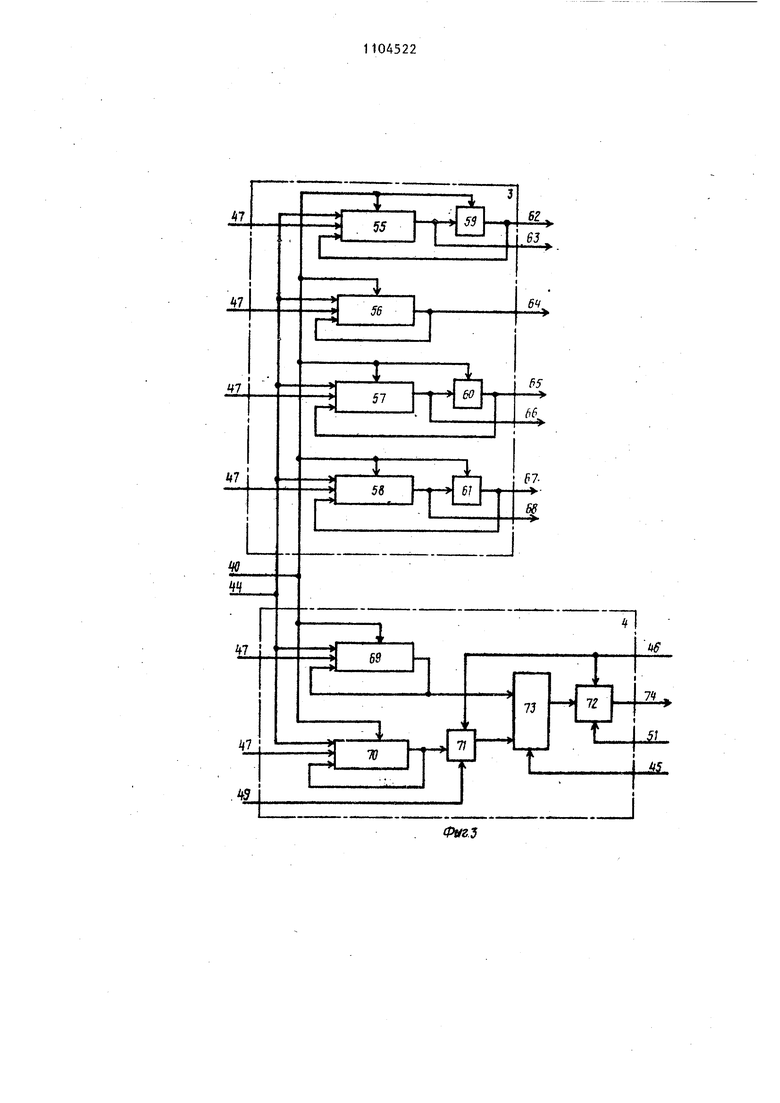

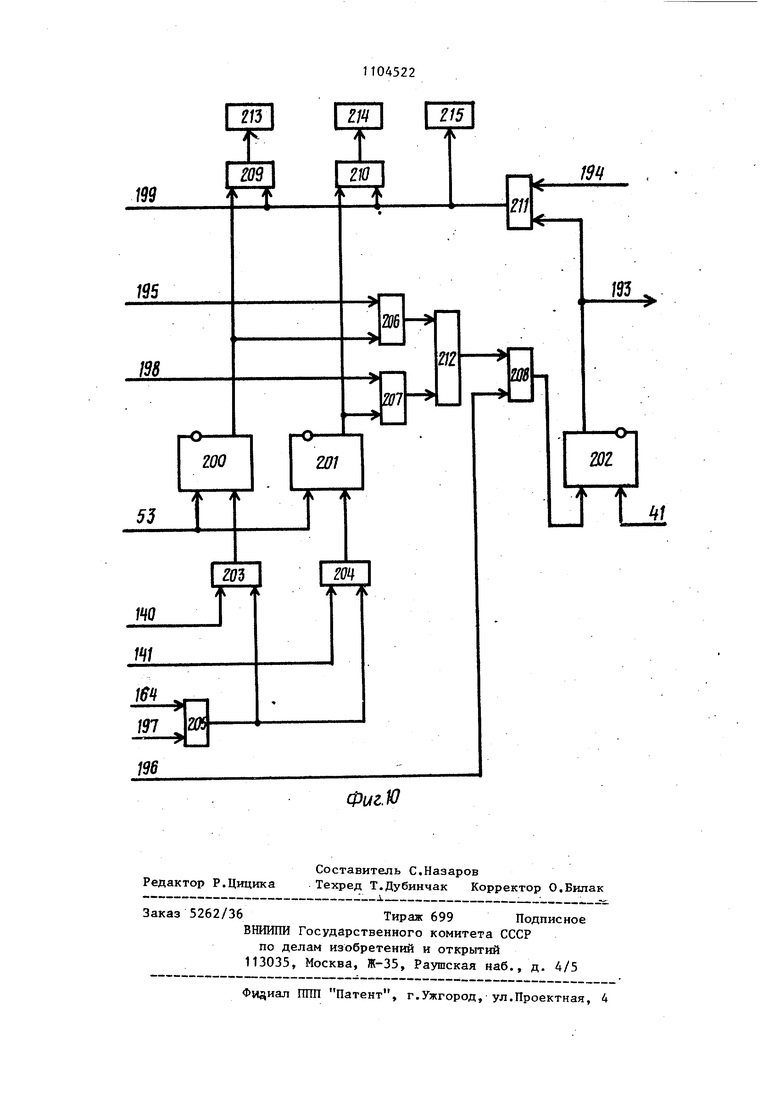

1. УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ИГРОВЫХ ЗАДАЧ НА ВЫЧИСЛИТЕЛЬНЫХ СЕТЯХ, содержащее блок управления, селектор ветви сети,селектор узла сети и модель сети,включающую модели ветвей, о тличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности решения задач теории дифференциальных игр, в него введены блок формирования параметров движения, включающий четыре регистра сдвига и три элемента задержки, блок формирования параметров управления, включающий два регистра сдвига, два формирователя дополнительного кода и сумматор, блок формирования, приращений координат, включающий четыре формирователя дополнительного кода, четыре регистра сдвига, семь сумматоров, два формирователя модуля, три триггера и восемь элементов И, блок формирования приращений функционала, включающий счетчик, формирова.тель модуля, три сумматора, два формирователя дополнительного кода, два коммутатоIn ейышогЕйА ра, регистр сдвига, два триггера, эле мент ИЛИ, элемент НЕ и семь элементов И, селектор ветви сети содержит две схемы сравнения, три триггера, два элемента задержки, два элемента ИЛИ, одиннадцать элементов И и два элемента НЕ, селектор уз.ла сети содержит три счетчика и три дешифратора, модель сети дополнительно содержит модели уэлов, причем модели узлов и модели ветвей соединены согласно топологии сети, модель узла включает три счетчика, три триггера, шесть элементов И, четыре элемента ИЛИ и элемент ИЛИ-НЕ, модель ветви включает три триггера, девять элементов И, элемент ИЛИ и три элемента индикации, (Л блок управления содержит генератор импульсов, распределитель импульсов, генератор одиночных импульсов, счетчик, регистр сдвига, четыре триггера, четыре элемента И, четыре эле.мента ИЛИ, восемь коммутаторов, два элемента индикации, два элемента задержки, элемент НЕ и группу элементов ин4 СП дикации, причем выход генератора импульсов соединен с первым входом ю первого элемента И блока управления, N5 входом распределителя импульсов, синхронизирующими входами регистров сдвига и элементов задержки блока формирования параметров управления, синхронизирующими входами регистров сдвига блока формирования параметров движения, синхронизирующими входами регистров сдвига и формирователей модуля блока формирования приращений координат, синхронизирующими входами регистра сдвига и формирователя модуля блока формирования приращений функционала, синхронизирующими входя

I

Изобретение относится к вычислительной технике, в частности к устройствам для обработки информации специального назначения, и может быть использовано как специализированное вычислительное устройство для научно-исследовательских целей и моделирования, а также для управления некотор ымй технологическими процессами в различных отраслях промьшшенкости.

Известно устройство, позволяющее моделировать сети на основе сеточньрс моделей и решать краевые задачи теории поля. Устройство содержит сеточную модель, блок граничных условий, блок начальных условий и операционный усилитель Cl J.

Недостатком устройства являются его ограниченные функциональные возможности.

Известно устройство, содержащее модели ветвей, блок автоматического формирования топологии, генератор импульсов и блок управления t23.

Недостатком этого устройства является невозможность рещения игровых задач на вычислительных сетях, а также низкие эксплуатационные характеристики, связанные с высокой трудоемкоетью подготовки исходных данных.

Наиболее близким по технической сущности к изобретению является устро

ство для расчета больщих сетей, содержащее блок моделирования ветвей, первый выход которого соединен с входом а первый вход - с выходом блока управления, первый вход которого связан с первым вьтходом внешнего запоминаницего блока, вход и второй выход которого соединены соответственно с вторым выходом и вторым входом блока моделирования ветвей, и блок элементов памяти, входной и выходной логические коммутаторы и блок поиска фрагментов среды, причем выходы блока элементов памяти соединены соответственно с вхрдами входного логического коммутатора, выходы которого подключены соответственно к группе входов блока моделирования ветвей, первая группа выходов которого соединена соответственно с входами блока поиска фрагментов среды, а вторая группа выходов подключена соответственно к группе входов выходного логического коммутатора, выходы которого соединены соответственно с входами блока элементов памяти, а вход подключен к выходу блока поиска фрагментов среды, кроме того, блок поиска ментов среды содержит матрицу запЬминания направлений, узел передачи направлений, счетчик количества сдвигов и реверсивный регистр сдвига, причем первая группа входов матрицы запоминания направлений является группой входов блока, вторая группа входов матрицы запоминания направлений соответственно соединена с выходами реверсивного регистра сдвига, выходы матрищ 1 запоминания направлеНИИ соединены соответственно с группой входов узла передачи направлений первый выход которого соединен с входом реверсивного регистра сдвига, вто рой выход связан с входом счетчика количества сдвигов, а третий выход является выходом блока, выход счетчика количества сдвигов объединен с входом узла передачи направлений 3 Устройство позволяет определять оптимальные пути в неоднородных непр рывных средах, однако не решает игро вые задачи на вычислительных сетях. Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности решения задаг теории дифференциальных игр. Указанная цель достигается тем что в устройство для решения игровых задач на вычислительных сетях, содер жащее блок управления, селектор вет ви сети, селектор узла сети и модель сети, включающую модели ветвей,введены блок формирования параметров движения, включающий четыре регистра сдвига и три элемента задержки, блок формирования параметров управления, включающий два регистра сдвига, два формирователя дополнительного кода и сумматор, блок формирования прират щений координат, включающий четыре формирователя дополнительного кода, четыре регистра сдвига, семь суммато ров, два формирователя модуля, три триггера и восемь элементов И, блок формирования приращений функционала, включающий счетчик, формирователь модуля, три сумматора, два формирова теля дополнительного кода, два комму татора, регистр сдвига, два триггера элемент ИЛИ, элемент НЕ и семь элементов И, селектор ветви сети содер.жит две схемы сравнения, три тригге-/ ра, два элемента задержки, два элемент ИЛИ, одиннадцать элементов И и два элемента НЕ, селектор узла сети содержит три счетчика и три дешиф ратора, модель сети допонительно . содержит модели узлов, причем модели узлов и моделизетвей соединены согласно топологии сети, модель узла ключает три счетчика,, три триггера шесть элементов И, четыре элемента ИЛИ и элемент ИЛИ-НЕ, модель ветви включает три триггера, девять элементов И, элемент ИЛИ и три элемента индикации, блок управления содержит генератор импульсов, распределитель имаульсов,генератор одиночных импульсов, счетчик, регистр сдвига, четыре триггера, четьфе элемента И, четыре элемента ИЛИ, восемь коммутаторов, два элемента индикации, два элемента задержки, элемент НЕ и группу элементов индикации, причем выход генератора импульсов соединен с первым входом первого элемента И блока управления, входом распределителя импульсов, синхронизирующими входами регистров сдвига и элементов задержки блока формирования параметров управления, синхронизирующими входами регистров сдвига блока формирования параметров движения, синхронизирующими входами регистров сдвига и формирователей модуля блока формирования приращений координат, синхронизирующими входами регистра сдвига и формирователя модуля блока формирования приращений функционала, синхронизирующими входами схем сравнения и элементов задержки селектора ветви сети и вторыми входами третьих элементов И модулей узлов сети, выходы распределителя импульсов блока управления через группу входов первого коммутатора блока управления соединены с соответствующими входами первого элемента ИЛИ блока управления, выход п-го разряда распределителя импульсов блока управления соединен с тактовым входом генератора одиночных импульсов, ВХОДОМ синхронизации регистра сдвига блока управления, нулевым входом первого триггера блока управления, входом первого элемента задержки блока управления, входом сброса сумматора блока формирования параметров управления, входами сброса сумматоров, формирователей модуля и нулевыми входами триггеров блока формирования приращений координат, входами сброса сумматора, первым входом сброса формрфователя модуля, первыми входами первого и второго элементов И блока формирования приращений функционала, вторыми входами первого и третьего элементов И, третьим входом второго элемента И и первыми входами триггеров ветви сети, втopы и входаселектораи шестого элементов И кажми пятого дой модели узла сети, выход первого элемента ИЛИ блока управления соеди.нен с первым входом второго элемента И блока управления, второй вход которого подключен к единичному выходу первого триггера блока управления, входы группы элементов индикации блока управления соединены с выходами счетчика блока управления, информационный вход которого соединен с выходом первого элемента И блока управления, второй вход которо го соединен с входом первого элемента индикации блока управления и подключен к единичному выходу второго триггера блока уп ра вления, единичный выход третьего триггера блока управления соединен с входом второго элемента индикации блока управления и первым входом третьего элемента И блока управления, выход которого соединен с первым входом третьего элемента ИЛИ блока управления, выход которого подключен к информационному входу регистра сдвига блока управления, единичному входу третьего триггера блока управления, первому входу четвертого элемента И блока управлесния и через второй элемент задержки блока управления - к счетному входу четверто 7о триггера блока управления единичный выход которого соединен с вторым входом четвертого элемента И блока управления, выход генератора одиночных импульсов блока управления соединен с первым входом второго ком мутатора блока управления, первый выход которого подключен к единичному входу первого триггера блока упра ления, второй выход - к -второму входу третьего элемента ИЛИ блока управ ления, а третий выход - к единичному входу второго триггера блока управле ния и первому входу четвертого коммутатора блока управления, первый вход третьего коммутатора блока управления подключен к единичному ВЫХОДУ первого триггера блока управления, вход первого коммутатора блока управления и вторые входы второго третьего, четвертого, пятого, шестого, седьмого и восьмого коммутаторов блока управления соединены с общей шиной устройства, выходы третьего коммутатора блока управления подключены к управляющим входам соответствующих регистров сдвига блока формирования параметров движения и блока формирования параметров управления, выходы четвертого коммутатора блока управления соединены с входами первых элементов И моделей узлов сети, выход пятого коммутатора блока управления подключен к входу запуска генератора одиночных импульсов, вход элемента НЕ блока управления соединен с общей шиной устройства, а выход подключен к первым входам пятого, шестого, седьмого и восьмого коммутаторов блока управления, выход шестого коммутатора блока управления соединен с входом сброса счетчика блока управления, нулевыми входами первых и третьих триггеров моделей узлов и вторыми нулевыми входами вторых триггеров моделей узлов, нулевыми входами третьих триггеров моделей ветвей, выход седьмого коммутатора блока управления соединен с первыми входами второго и четвертого элементов ИЛИ блока управления, нулевым входом четвертого триггера блока управления, входами управления регистров сдвига блока формирования приращения координат, входом сброса счетчика блока формирования приращений функционала, первым входом элемента ИЛИ блока формирования приращений функционала, входами сброса счетчиков селектора узла сети, входами сброса счетчиков моделей узлов и нулевыми входами первого и второго триггеров моделей ветвей, выход восьмого коммутатора блока управления соединен с управляющим входом первого формирователя дополнительного кода блока формирования параметров управ- пения, нулевой вход второго триггера блока управления соединен с выходом второго элемента ИЛИ блока управления, второй вход которого соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента ИЛИ модели конечного узла сети, второй вход третьего элемента И блока управления соединен с нулевыми входами первого и второго триггеров блока формирования приращений функционала и подключен к выходу элемента ИЛИ блока формирования приращений функционала, выход второго элемента И блока управления соединен с входами ввода данных регистров сдвига блока формирования параметров движения и блока формирования параметров управления, выход первого элемента задержки блока управления соединен с входами сброса формирователей дополнительного кода блока формирова ния параметров управления, с входами сброса формирователей .дополнитель него кода и вторыми входами сброса формирователей модуля блока формирования приращений координат, с входами сброса блоков дополнительного кода и вторым входом сброса формирователя модуля блока формирования приращений функционала .и с входами сброса схем сравнения селектбра ветви сети, выход четвертого элемента И блока управления соединен с еди яичным входом первого триггера блока формирования приращений координат и информационным входом первого счет чика селектора узла сети, единичный выход четвертого триггера блока управления подключен к входу управления второго формирователя дополнител ного кода блока формирования парамет ров управления, к первому входу седь мого элемента И и через элемент НЕ к первому входу третьего элемента И блока формирования приращений функци онала, выход регистра сдвига блока управления соединен с единичным входом первого триггера блока формирования приращений функционала, второй вход четвертого элемента ИЛИ блока управления подключен к выходу третьего счетчика селектора узла сет выход первого регистра сдвига блока формирования параметров движения соединен с информационным входом пер вого элемента задержки этого же блока и информационным входом первого формирователя дополнительного кода блока формирования прираздений функционала, выходы первого, третьего и четвертого регистров сдвига блока формирования параметров движения соединены со своими информационными входами через соответственно первый, второй, и третий элементы задержки этого же блока, выход второго регист ра сдвига блока формирования парамет ров движения соединен со своим инфор мационным входом и информационным входом второго формирователя дополнительного кода блока формирования приращений координат, выходы первого, второго и третьего элементов задержки блока формирования параметров движения соединены соответственно с информационными входами первого, третьего и четвертого формирователей дополнительного кода блока формирования приращений координат, выходы третьего и четвертого регистров блока формирования параметров движения соединены соответственно с первым входом первого сумматора и первым, входом четвертого элемента И блока формирования приращений функционала, выход первого регистра сдвига блока формирования параметров управления соединен с его информационным входом и первым информационным входом сумматора блока формирования параметров управления, выход которого подключен и информационному входу второго формирователя дополнительного кода этого же блока, выход второго регистра сдвига блока формирования параметров управления соединен с его информационным входом и информационным входом первого формирователя дополнительного кода блока формирования параметров управления, выход которого подключен к второму информационному входу сумматора блока формирования параметров управления, выход второго формирователя дополнительного кода блока формирования параметров управления подключен к первому информационному входу первого сумматора блока формирования приращений координат, информационные выходы первого, второго, третьего и четвертого формирователей дополнительного кода блока формирования приращений координат соединены с первыми входами соответственно первого, второго, третьего и четвертого элементов И блока формирования приращений координат, управляющие входы первого и четвертого формирователей дополнительного кода блока формирования приращений координат соединены с первым выходом третьего счетчика селектора модели узла сети, второй выход которого подключен к управляющим входам второго и третьего формирователей дополнительного кода блока формирования приращений координат, единичный выход первого триггера блока формирования приращений координат соединен с вторыми входами второго и третьего элементов И блока формирования приращений координат, нулевой выход второго триггера блока фор ирования приращений координат подключен к первому входу пятого элемента И, третьему входу втор&го элемента И, первому входу шестого элемента И и третьему входу третьего злемента И блока формирования приращений координат, единичный выход второго триггера блока формирования при ращений координат соединен с вторыми входами первого и четвертого элементов И блока формирования приращений координат, нулевой выход третьего триггера блока формирования приращений координат подключен к третьим входам первого и четвертого элементов И и первым входам седьмого и вос мого элементов И блока формирования приращений координат, вторые входы седьмого, пятого, шестого и восьмого элементов И блока формирования приращений координат соединены соответственно с выходами первого, второго, третьего и четвертого регистров сдви га блока формирования приращений координат , входы ввода данньпс регистров сдвига блока формирования приращений координат соединены с общей шиной устройства, входы третьего, четвертого, пятого и шестого суммато ров блока формирования приращений координат соединены соответственно с выходами седьмого и первого, пятого и второго, шестого и третьего, восьмого и четвертого элементов И блока формирования пррфащений коорди нат, выход третьего сумматора блока формирования приращений координат подключен к информационному входу первого регистра сдвига и первому входу второго сумматора блока формирования приращений координат, выход которого соединен с вторым входом первого сумматора, а второй вход - с выходом четвертого сумматора и инфор мационным входом второго регистра сдвига блока формирования приращений координат, выход пятого .сумматора блока формирования приращений координат подключен к информационному входу третьего регистра сдвига и пер вому входу седьмого сумматора, выход первого сумматора блока формирования приращений координат подключен к информационному входу первого формирователя модуля блока формирования при ращений координат и первому входу BTOporok коммутатора блока формирования приращений функционала, выход шестого сумматора блока формирования приращений координат соединен с информационным входом четвертого регис