г

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах для оптимизации и в системах опти- мального управления технологическими объектами в различных отраслях промьшшенности.

Цел-ью изобретения - является повышение точности решения.

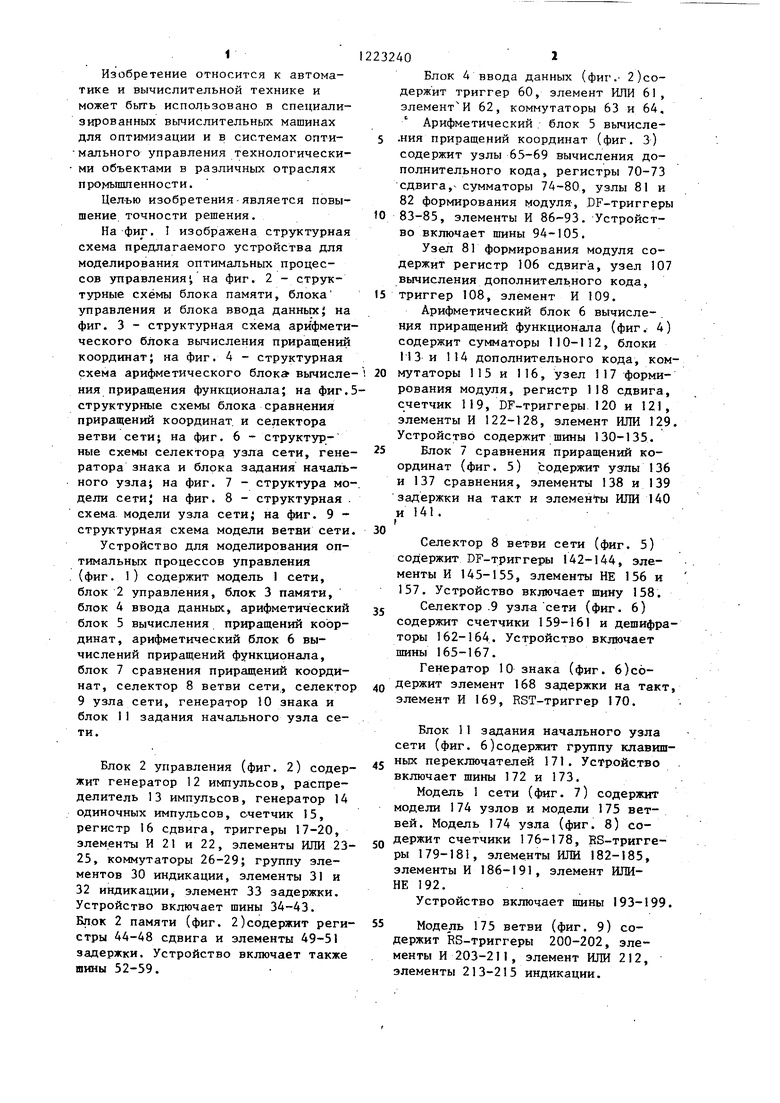

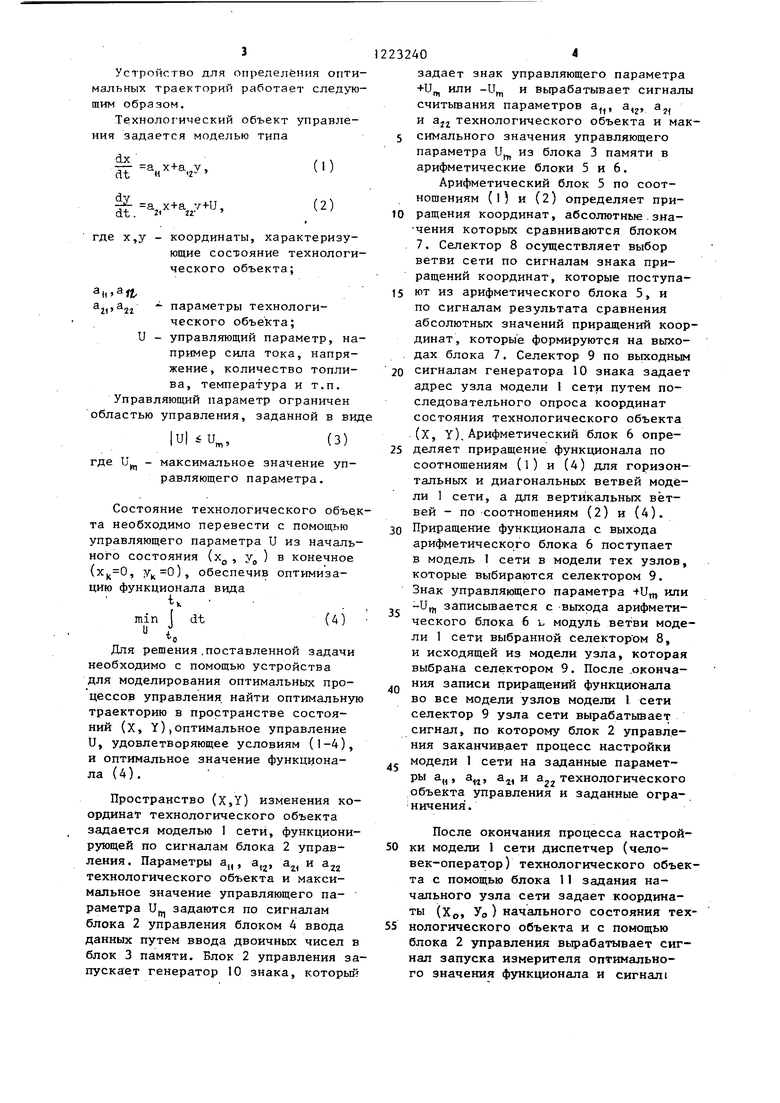

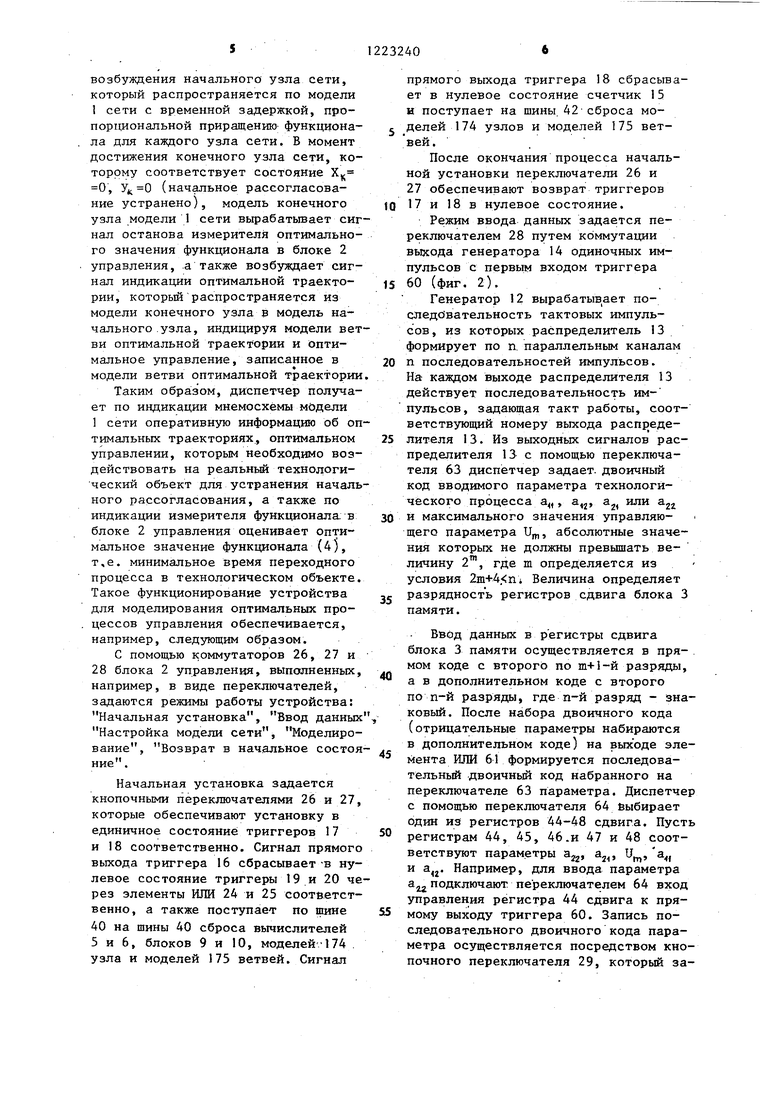

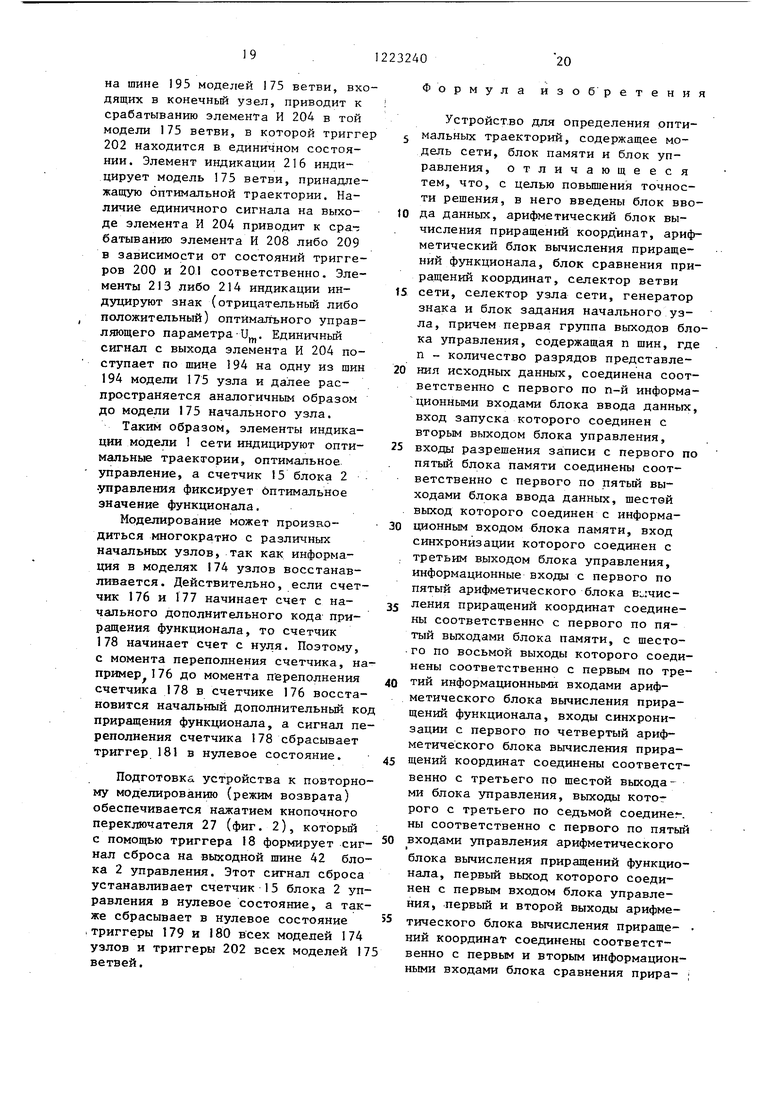

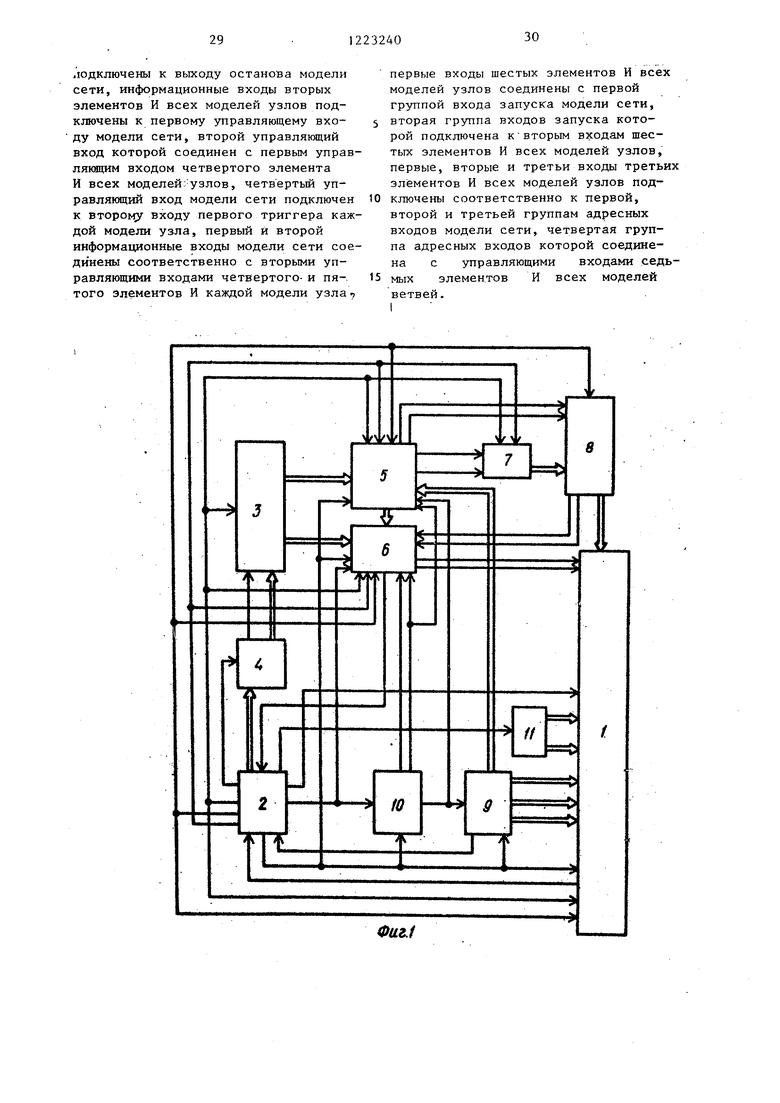

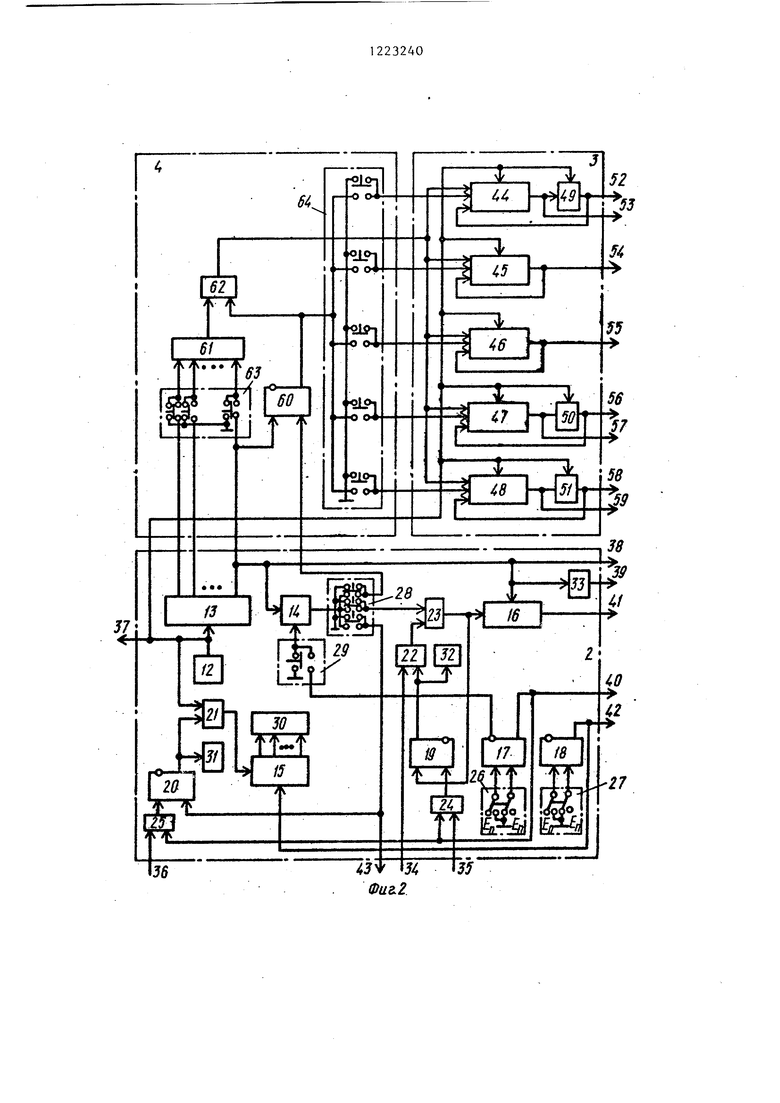

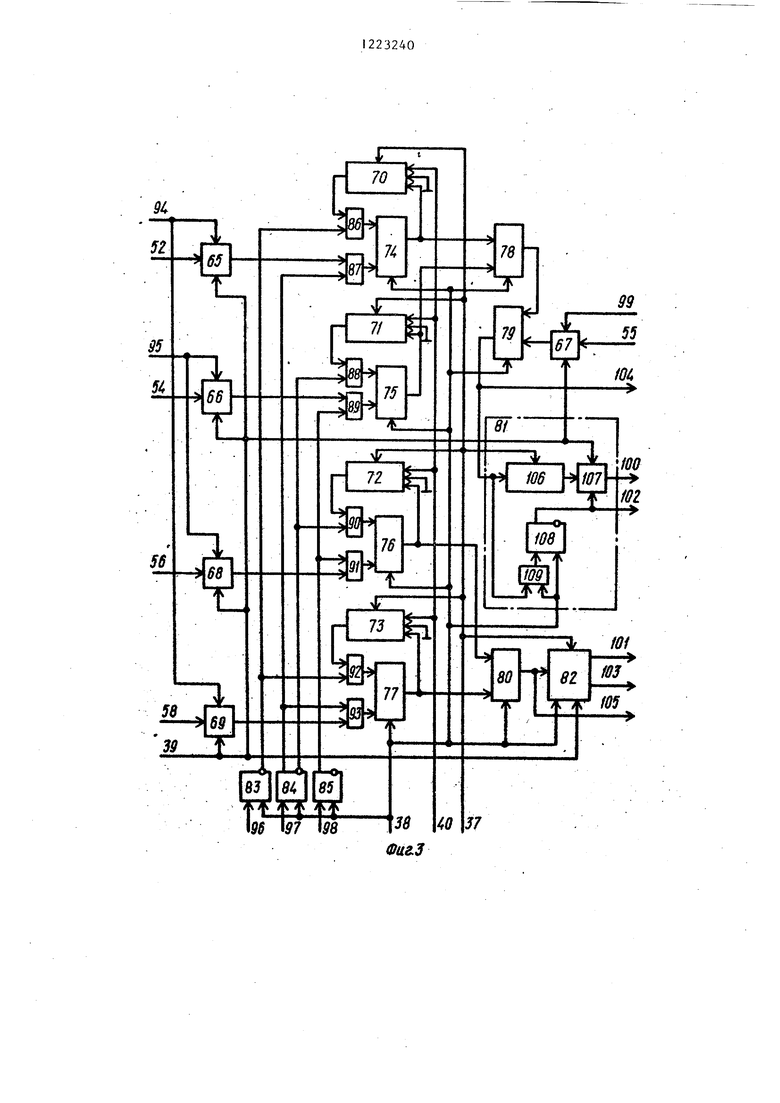

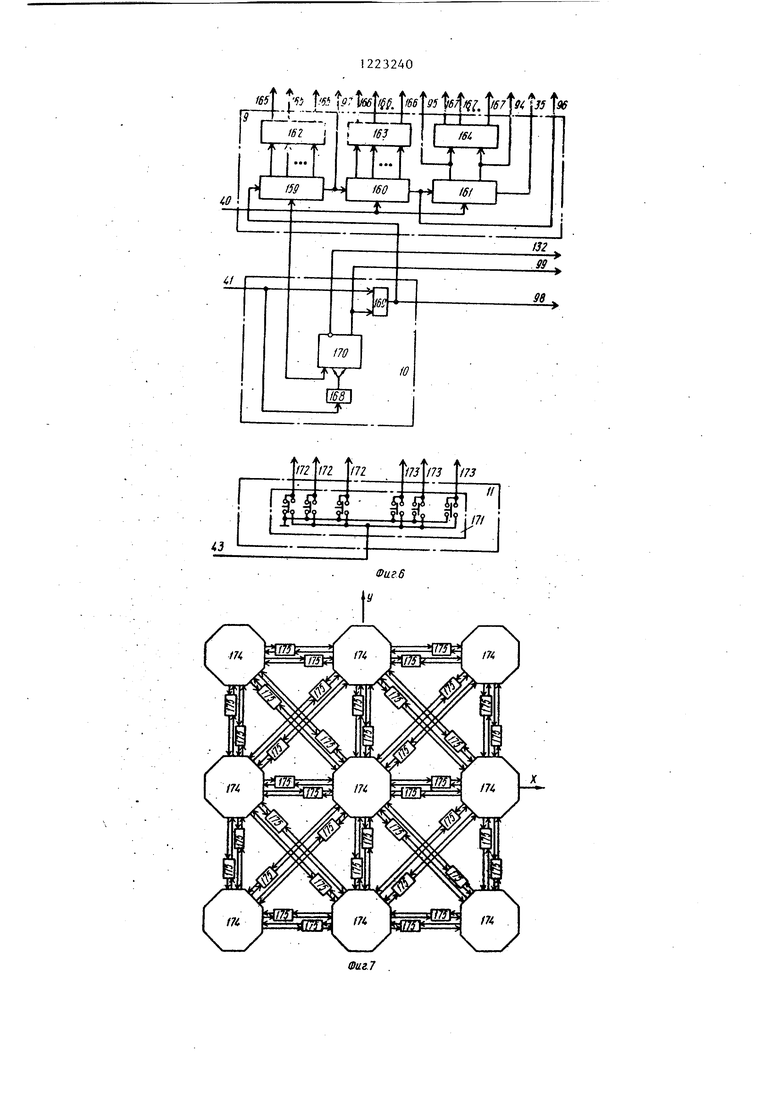

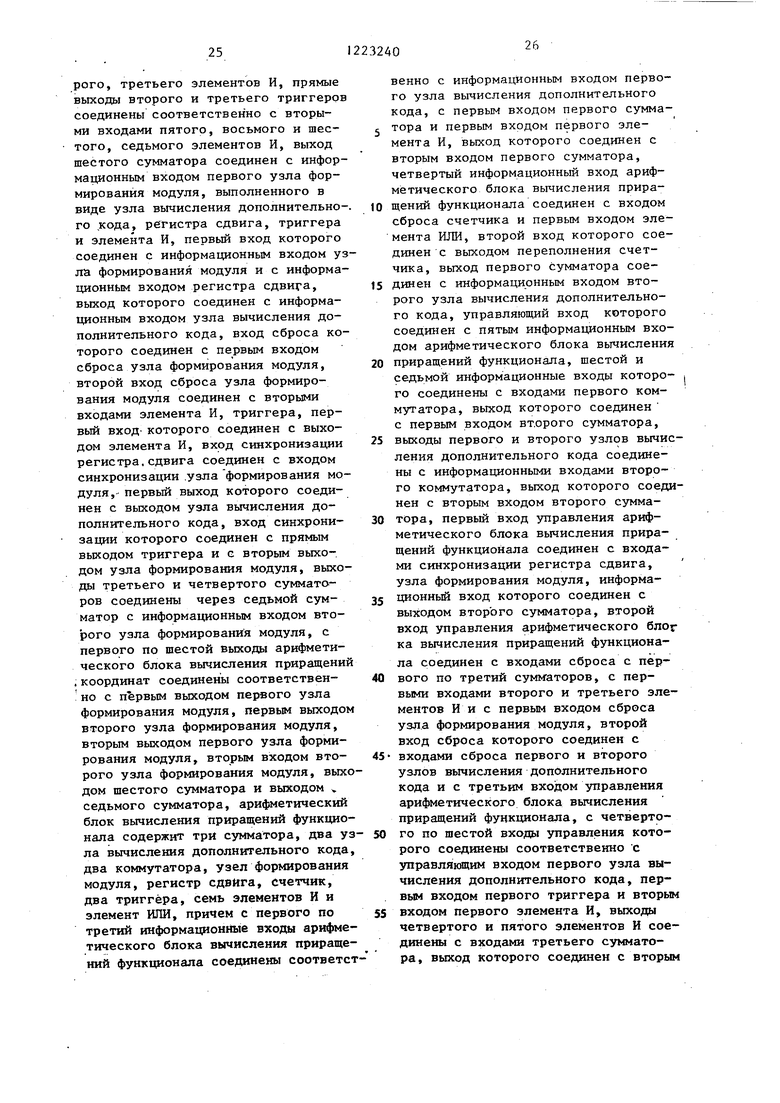

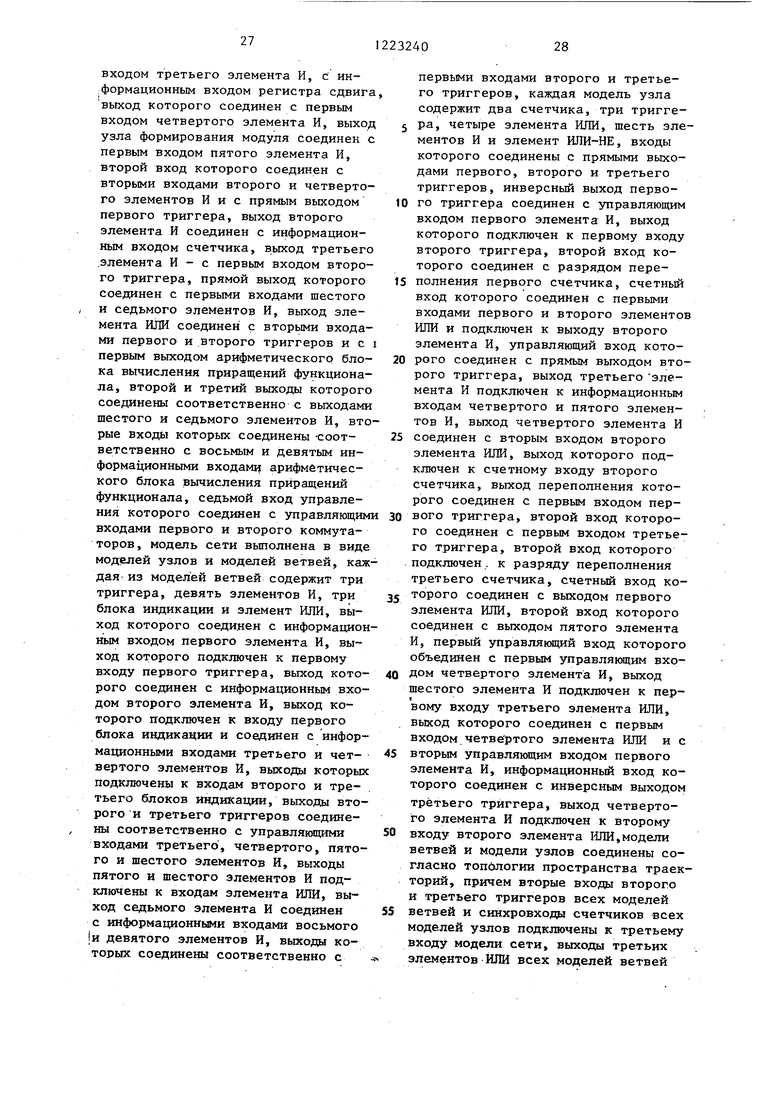

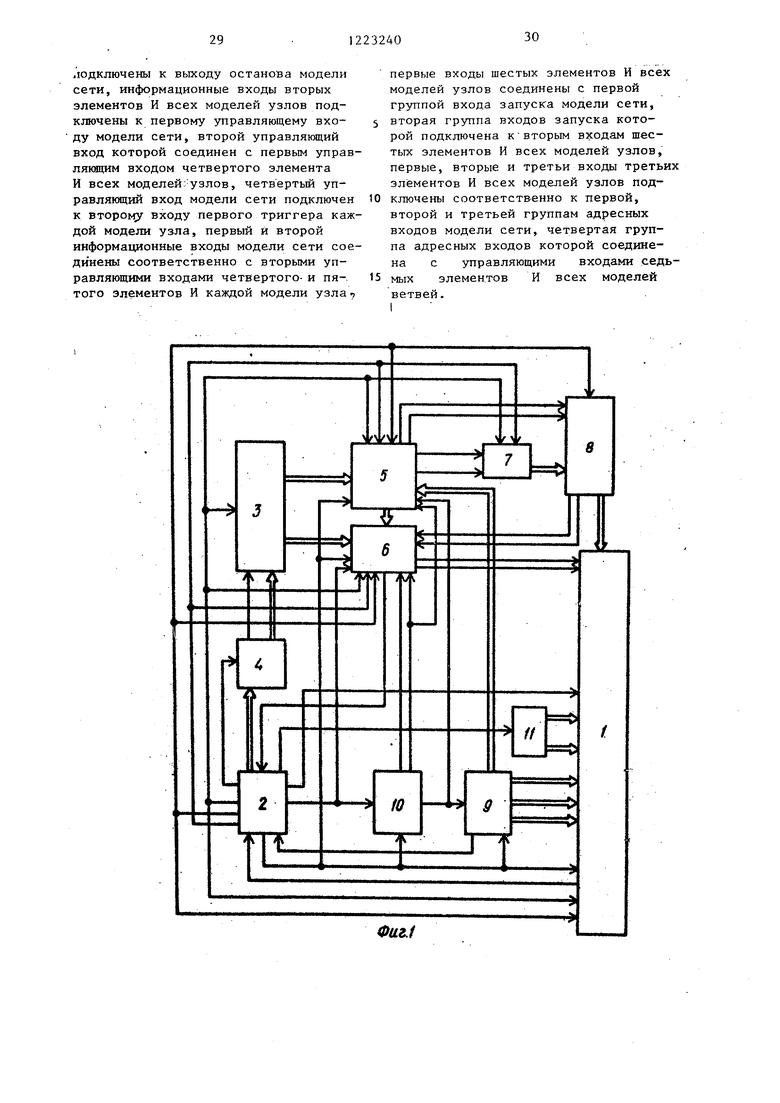

На фиг. I изображена структурная схема предлагаемого устройства для моделирования оптимальных процессов управления , на фиг. 2 - структурные схемы блока памяти, блока управления и блока ввода данньпс} на фиг. 3 - структурная схема, арифметического блока вычисления приращений координат; на фиг. 4 - структурная схема арифметического блока вычисления приращения функционала; на фиг.5 структурные схемы блока сравнения приращений координат и селектора ветви сети; на фиг. 6 - структур- ные схемы селектора узла сети, генератора знака и блока задания начального узла на фиг. 7 - структура модели сети; на фиг. 8 - структурная . схема модели узла сети; на фиг. 9 - структурная схема модели ветви сети.

Устройство для моделирования оптимальных процессов управления (фиг. ) содержит модель 1 сети, блок 2 управления, блок 3 памяти, блок 4 ввода данных, арифметический блок 5 вычисления приращений координат, арифметический блок 6 вычислений приращений функционала, блок 7 сравнения приращений координат, селектор 8 ветви сети, селектор 9 узла сети, генератор 10 знака и блок 11 задания начального узла сети.

Блок 2 управления (фиг. 2) содержит генератор 12 импульсов, ра;спре- делитель 13 импульсов, генератор 14 одиночных импульсов, счетчик 15, регистр 16 сдвига, триггеры 17-20, элементы И 21 и 22, элементы ИЛИ 23- 25, коммутаторы 26-29; группу элементов 30 индикации, элементы 31 и 32 индикации, элемент 33 задержки. Устройство включает шины 34-43. Блок 2 памяти (фиг. 2)содержит регистры 44-48 сдвига и элементы 49-51 задержки. Устройство включает также шины 52-59.

23240 2

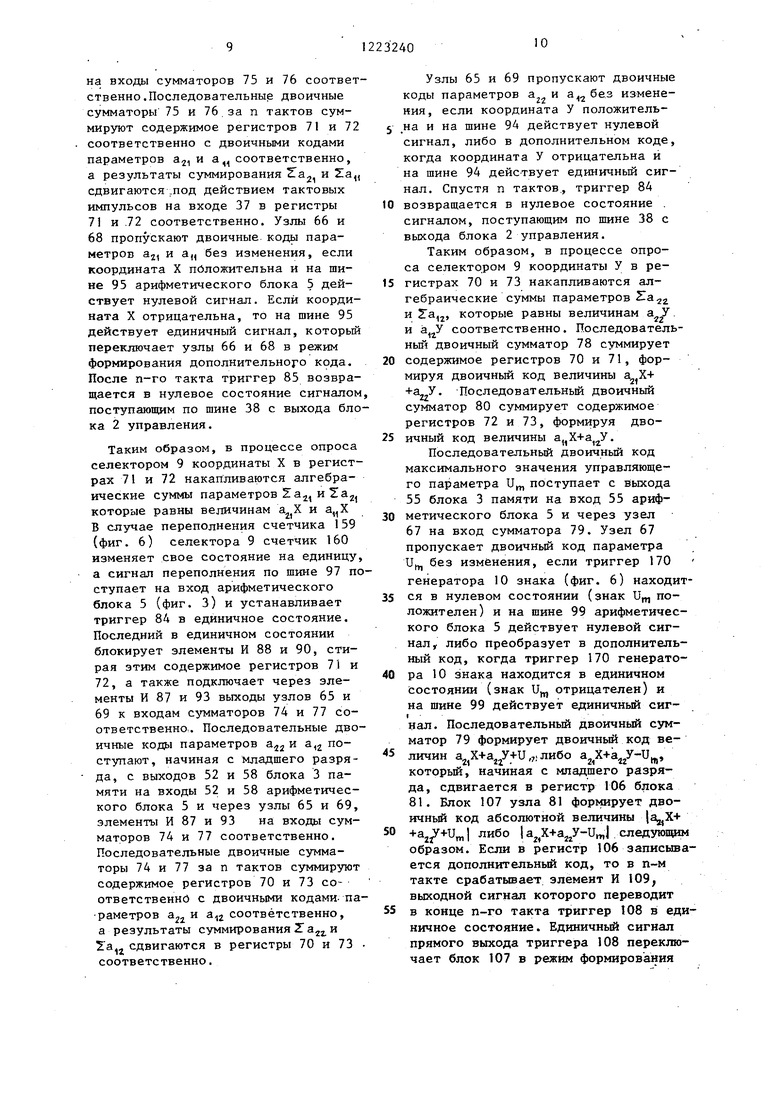

Блок 4 ввода данных (фиг.- 2)содержит триггер 60, элемент ИЛИ 61, элемент И 62, коммутаторы 63 и 64, Арифметический блок 5 вычисле- 5 .ния приращений координат (фиг. З) содержит узлы 65-69 вычисления дополнительного кода, регистры 70-73 сдвига,- сумматоры 74-80, узлы 81 и 82 формирования модуля-, .DF-триггеры 0 83-85, элементы И 86-93. Устройство включает шины 94-105.

Узел 81 формирования модуля содержит регистр 106 сдвига, узел 107 вычисления дополнительного кода, 15 триггер 108, элемент И 109.

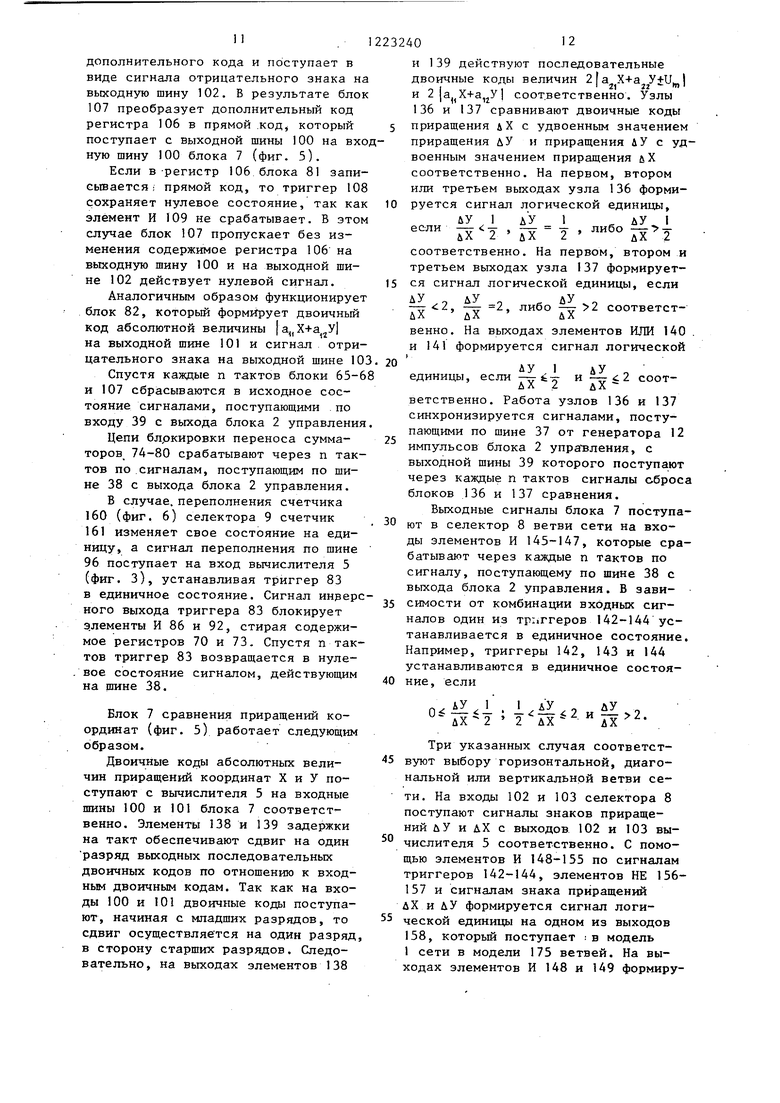

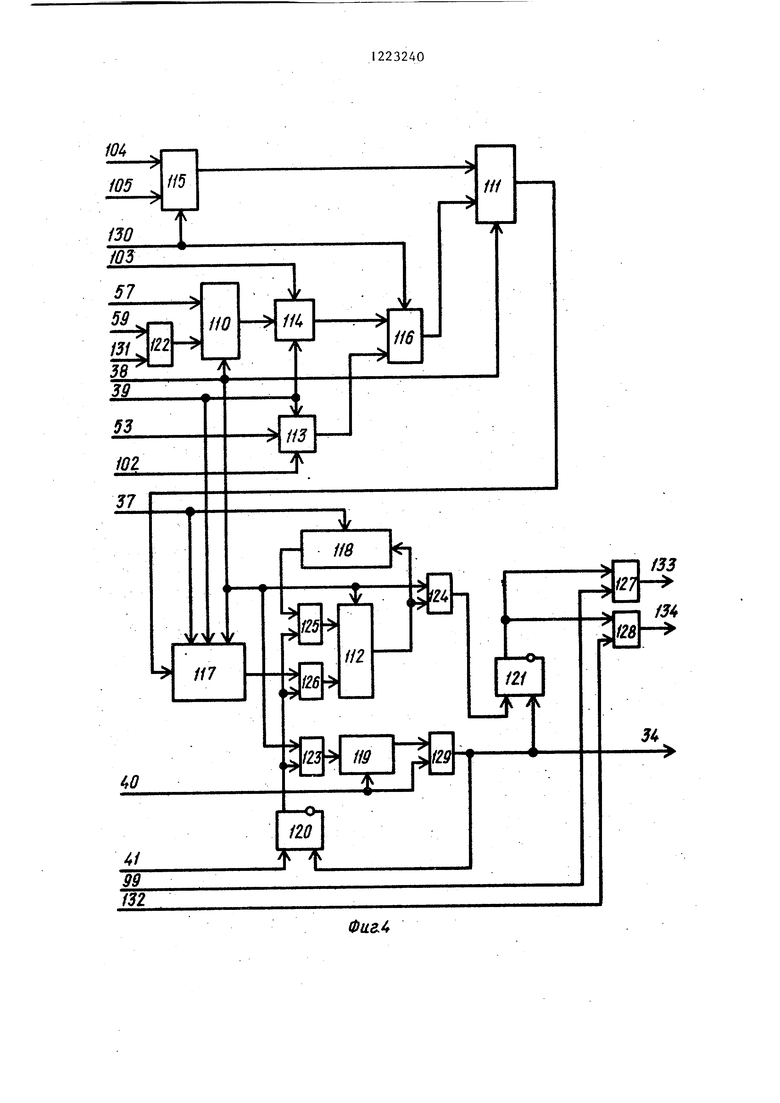

Арифметический блок 6 вычисления приращений функционала (фиг. 4) содержит сумматоры 110-112, блоки 113 и 114 дополнительного кода, ком- 20 мутаторы 115 и 116, узел 117 формирования модуля, регистр 118 сдвига, счетчик 119, DF-триггеры 120 и 121, элементы И 122-128, элемент ИЛИ 129. Устройство содержит шины 130-135. 25 Блок 7 сравнения приращений координат (фиг. 5) содержит уз лы 136 и 137 сравнения, элементы 138 и 139 задержки на такт и элементы ИЛИ 140

и 141.

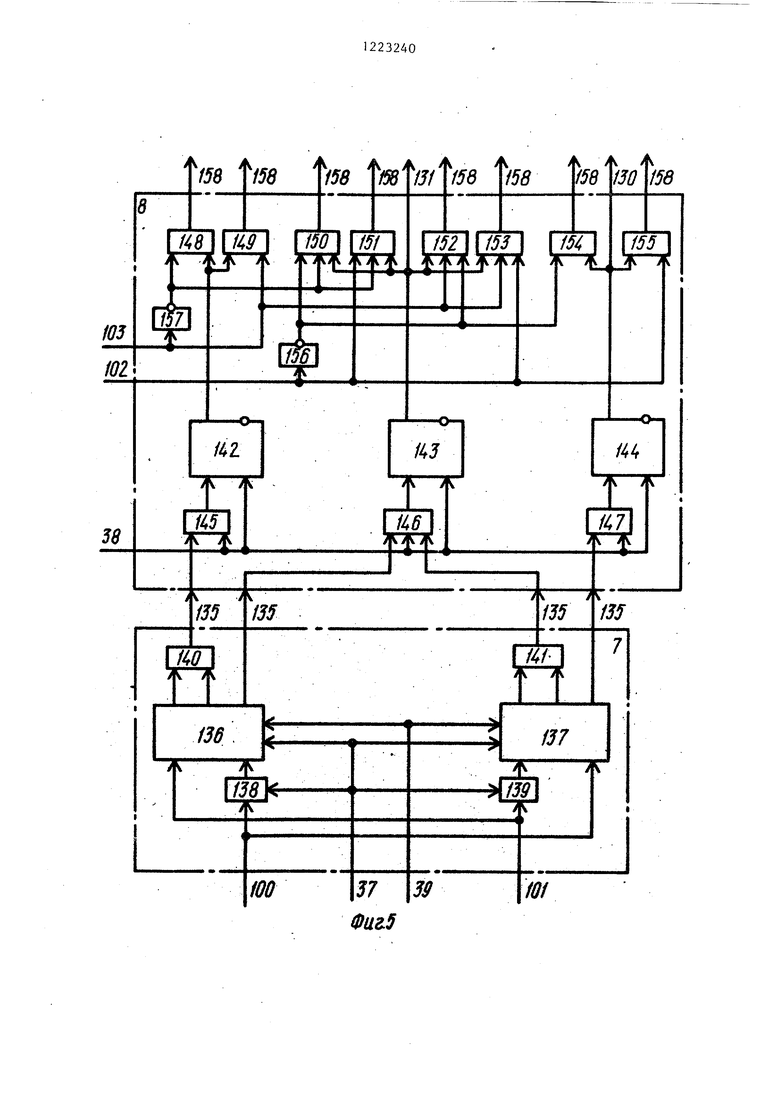

Селектор 8 ветви сети (фиг. 5) содержит DF-триггеры 142-144, элементы И 145-155, элементы НЕ 156 и 157. Устройство включает шину 158.

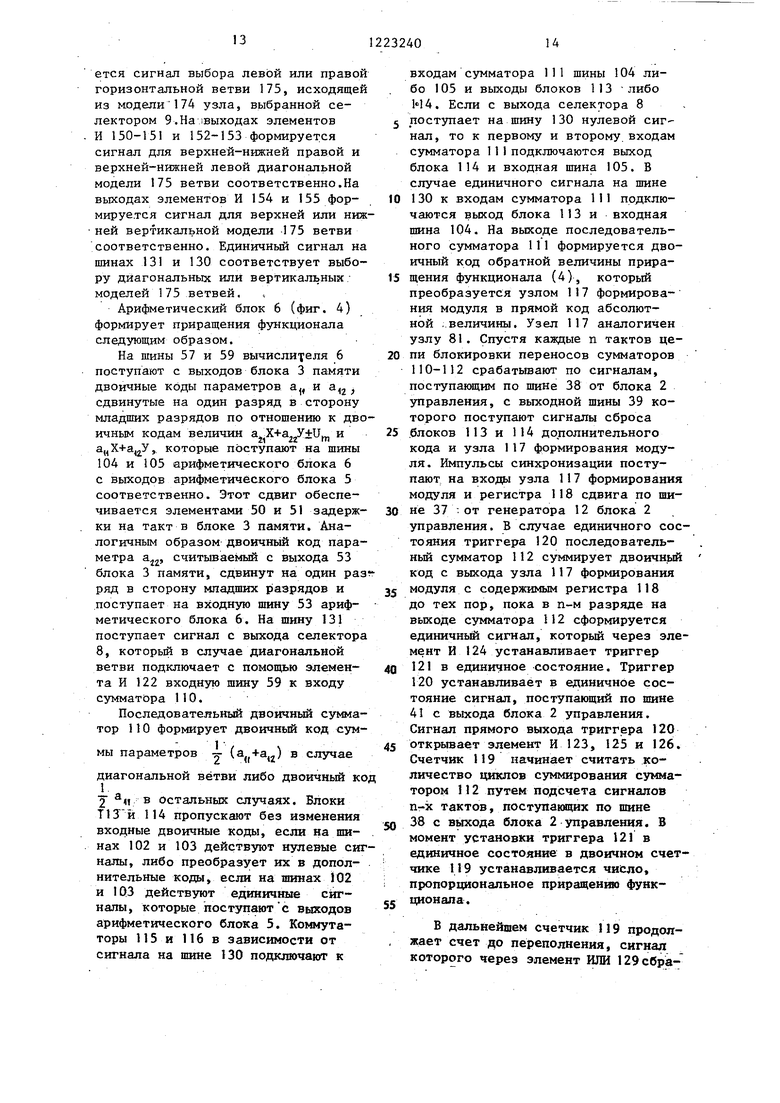

Селектор .9 узла сети (фиг. 6)

содержит счетчики 159-161 и дешифраторы 162-164. Устройство включает шины 165-167.

Генератор 10 знака (фиг. 6)с6держит элемент 168 задержки на такт, элемент И 169, RST-триггер 170.

Блок 11 задания начального узла сети (фиг. 6)содержит группу клавищ- ньк переключателей 171. Уctpoйcтвo включает шины 172 и 173.

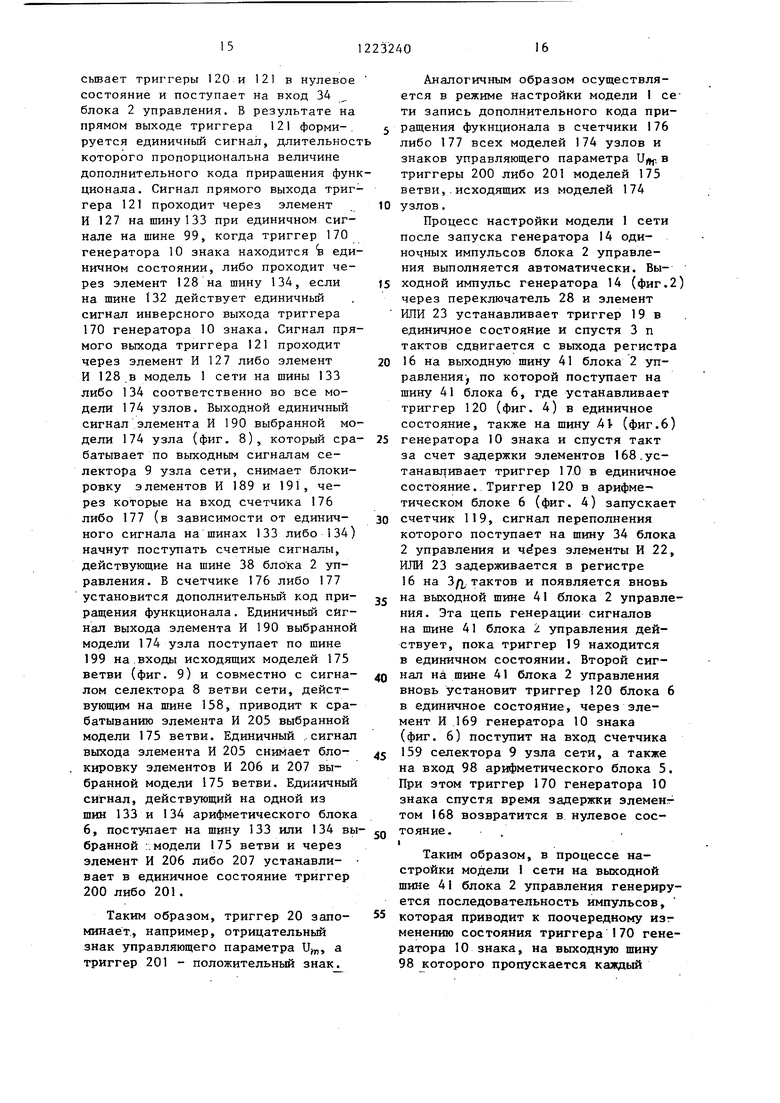

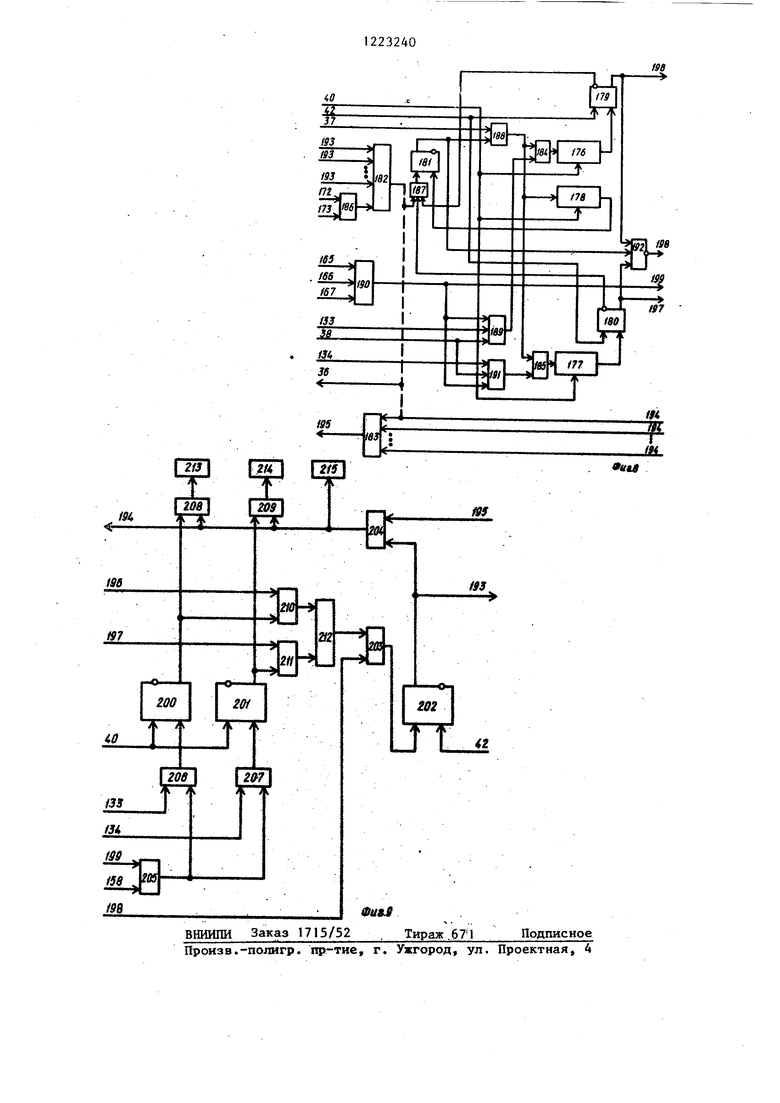

Модель 1 сети (фиг. 7) содержит модели 174 узлов и модели 175 ветвей. Модель 174 узла (фиг. 8) со- держит счетчики 176-178, RS-тригге- ры 179-181, элементы ИЖ 182-185, элементы И 186-191, элемент ИЛИ- НЕ 192.

Устройство включает шины 193-199.

Модель 175 ветви (фиг. 9) содержит RS-триггеры 200-202, элементы И 203-211, элемент ИЛИ 212, элементы 213-215 индикации.

Устройство для определения оптимальных траекторий работает следую- шим образом.

Технологический объект управления задается моделью типа

dx ,гУ

dt.

де х,у

aj,x+a,y+U,

(1) (2)

координаты, характеризующие состояние технологического объекта;

3 (,, а f J,

параметры технологического объекта; и - управляющий параметр, например сила тока, напряжение, количество топлива, температура и т.п. Управляющий параметр ограничен областью управления, заданной в виде

|и| i и.

т

(3)

где

максимальное значение управляющего параметра.

Состояние технологического объекта необходимо перевести с помощью управляющего параметра U из начального состояния (Xjj , УО ) в конечное {х,0, ), обеспечив оптимизацию функционала вида

min ( dt(4)

io

Для решения.поставленной задачи необходимо с помощью устройства для моделирования оптимальных процессов управления, найти оптимальную траекторию в пространстве состояний (Х, Y),оптимальное управление и, удовлетворяющее условиям (1-4), и оптимальное значение функционала (4).

Пространство (X,Y) изменения координат технологического объекта задается моделью 1 сети, функционирующей по сигналам блока 2 управления . Параметры а„, а,, а и а технологического объекта и максимальное значение управляющего па- раметра U задаются по сигналам блока 2 управления блоком 4 ввода данных путем ввода двоичных чисел в блок 3 памяти. Блок 2 управления запускает генератор 10 знака, который

задает знак +U или -LL

управляющего параметра и вырабатывает сигналы

считьгоания параметров а,р а,, а

я и технологического объекта и максимального значения управляющего параметра U из блока 3 памяти в арифметические блоки 5 и 6.

Арифметический блок 5 по соотношениям (l) и (2) определяет приращения координат, абсолютные.зна- чения которых сравниваются блоком 7. Селектор 8 осуществляет выбор ветви сети по сигналам знака приращений координат, которые поступают из арифметического блока 5, и по сигналам результата сравнения абсолютных значений приращений координат, которые формируются на выхо- дах блока 7. Селектор 9 по выходным

сигналам генератора 10 знака задает адрес узла модели I сети путем последовательного опроса координат состояния технологического объекта (Х, Y). Арифметический блок 6 определяет приращение функционала по соотношениям (l) и (4) для горизонтальных и диагональных ветвей модели 1 сети, а для вертикальных ветвей - по соотношениям (2) и (4).

Приращение функционала с выхода арифметического блока 6 поступает в модель I сети в модели тех узлов, которые выбираются селектором 9. Знак управляющего параметра -HJ или

-U(j, записьгоается с выхода арифметического блока 6 L модуль ветви модели 1 сети выбранной селектор ом 8, и исходящей из модели узла, которая выбрана селектором 9. После .окончания записи приращений функционала во все модели узлов модели 1 сети селектор 9 узла сети вырабатывает сигнал, по которому блок 2 управления заканчив.ает процесс настройки модели 1 сети на заданные параметры а„ , а„, а, и а технологического объекта управления и заданные огра- ничения .

После окончания процесса настройки модели 1 сети диспетчер (человек-оператор) технологического объекта с помощью блока 11 задания начального узла сети задает координаты (Хо, УО ) начального состояния технологического объекта и с помощью блока 2 управления вырабатывает сигнал запуска измерителя оптимального значения функционала и сигнал

возбуждения начального узла сети, который распространяется по модели 1 сети с временной задержкой, пропорциональной приращению функциона- ла для каждого узла сети. В момент достижения конечного узла сети, которому соответствует состояние Х 0, Yj; 0 (начальное рассогласование устранено), модель конечного узла модели 1 сети вьфабатьшает сигнал останова измерителя оптимального значения функционала в блоке 2 управления, .а также возбуждает сигнал индикации оптимальной траекто- рии, который распространяется из модели конечного узла в модель начального .узла, индицируя модели ветви оптимальной траектории и Оптимальное управление, записанное в модели ветви оптимальной траектории

Таким образом, диспетчер получает по индикации мнемосхемы модели 1 сети оперативную информацию об оптимальных траекториях, оптимальном управлении, которым необходимо воздействовать на реальный технологический объект для устранения начального рассогласования, а также по индикации измерителя функционала, в блоке 2 управления оценивает оптимальное значение функционала (4, т,е. минимальное время переходного процесса в технологическом объекте. Такое функционирование устройства для моделирования оптимальных процессов управления обеспечивается, например, следующим образом.

С помощью коммутаторов 26, 27 и 28 блока 2 управления, выполненных, например, в виде переключателей, задаются режимы работы устройства: Начальная установка, Ввод данных Настройка модели сети, Моделирование, Возврат в начальное состояние.

Начальная установка задается кнопочными переключателями 26 и 27, которые обеспечивают установку в единичное состояние триггеров 17 и 18 соответственно. Сигнал прямого выхода триггера 16 сбрасывает -в нулевое состояние триггеры 19 и 20 через элементы ИЛИ 24 и 25 соответственно, а также поступает по шине 40 на шины 40 сброса вычислителей 5 и 6, блоков 9 и 10, моделей 174 узла и моделей 175 ветвей. Сигнал

с JQ 5 20

25 зо

0 5

5

Q

5

прямого выхода триггера 18 сбрасывает в нулевое состояние счетчик 15 и поступает на шины. 42 сброса моделей 174 узлов и моделей 175 ветвей.

После окончания процесса начальной установки переключатели 26 и 27 обеспечивают возврат триггеров 17 и 18 в нулевое состояние.

Режим ввода данных задается переключателем 28 путем коммутации выхода генератора 14 одиночных импульсов с первым входом триггера 60 (фиг. 2).,

Генератор 12 вырабатывает последовательность тактовых импульсов, из которых распределитель 13 формирует по п. параллельным каналам п последовательностей импульсов. На каждом выходе распределителя 13 действует последовательность им- пульсов, задающая такт работы, соответствующий номеру выхода распреце- лителя 13. Из выходных сигналов распределителя 13 с помощью переключателя 63 диспетчер задает, двоичньш код вводимого параметра технологического процесса а, , a,j, а, или а,, и максимального значения управляющего параметра U, абсолютные значения которых не должны превышать величину 2™, где m определяется из условия Величина определяет разрядность регистров сдвига блока 3 памяти.

- Ввод данных в регистры сдвига блока 3 памяти осуществляется в пря- . мом коде с второго по m+1-й разряды, а в дополнительном коде с второго по п-й разряды, где п-й разряд - знаковый. После набора двоичного кода (отрицательные параметры набираются в дополнительном коде) на выходе элемента ИЛИ 61 формируется последова- тельньй двоичньй код набранного на переключателе 63 параметра. Диспетчер с помощью переключателя 64 Выбирает один из регистров 44-48 сдвига. Пусть регистрам 44, 45, 46.и 47 и 48 соответствуют параметры а, а, U, а, и а. Например, для ввода параметра подключают переключателем 64 вход управления регистра 44 сдвига к прямому выходу триггера 60. Запись последовательного двоичного кода параметра осуществляется посредством кнопочного переключателя 29, который запускает генератор 14 одиночного импульса. Один импульс из последовательности, действующей на последнем вьпсоде. распределителя 13, проходит. через генератор 14, переключатель 28 на первый вход триггера 60, устанавливая его в конце такта в единичное состояние. Триггер 60 находится в единичном состоянии п тактов с 1-го по h-и, в конце которого он сбросится по второму входу в нулевое состояние сигналами последнего выхода распределителя 13. Сигнал прямого выхода триггера 60 от- крьшает элемент И 62, через который с выхода элемента ИЛИ 61 последовательный двоичный код параметра а поступает, начиная с младшего разряда, на вход ввода данных регистра 44 и записывается в него под действием тактовых импульсов генератора 12. Регистры 44, 47 и 48 сдвига содержат п-1 разряд и дополняются соответственно элементами 49-51 задержки на такт до п разрядов. Регистры 45 и 46 содержат п разрядов. Аналогичным образом запи- сьгоаются остальные параметры в регистры 45-48 блока 3 памяти.

Режим настройки модели 1 сети задается переключателем 28, который подключает выход генератора 14 одиночных импульсов к первому входу .элемента ИЛИ 23. Настройка модели 1 сети Осуществляется последовательным опросом моделей 174 узлов и исходящих моделей 175 ветвей (фиг. 7), начиная с конечного узла, расположенного постоянно в начале координат Х,(0, Запуск процесса настройки модели 1 сети обеспечивается запуском генератора I4 одиночных импульсов с помощью кнопочного переключателя 29 блока 2 управления. Одиночный импульс с выхода генератора 14 через переключатель 28 и элемент ИЛИ 23 устанавливает триггер 19 в единичное состояние и записывается в регистр 16 сдвига под действием импульса последнего выхода распределителя 13. Регистр 16 на три разряда выполняет функцию дискретной задержки на 3 п тактов, за время которой вычислителем 5 и блоками 6-8 формируются сигналы выбора исходящей модели 175 ветви.

Сигналы выбора соответствующей модели 174 узла определяются состояниями счетчиков 159-161 (фиг. 6) 5 селектора 9 узла сети. Состояние счетчиков 159 и 160 определяют координаты X и У соответственно, а состояние двухразрядного счетчика 161 задает номер квадранта, в ко0 тором находится модель 174 узла. Сигналы с выходов дешифраторов 162- 164 селектора 9, поступая на соответствующие шины 165-167 моделей 174 узлов (фиг. 8), приводят к сра5 батыванию элемента И 190 выбранной модели 174 узла. На выходных пшнах 95 и 94 (фиг. 6) селектора 9 узла сети действуют единичные сигналы, когда опрашиваемые координаты X и У

0 соответственно отрицательны. В этом случае с выходных шин 94 и 95 селектора 9 на входные шины 94 и 95 соответственно арифметического блока 5 (фиг. 3) поступают единичные сиг налы.

Выбор исходящих моделей 175 ветвей соответствующей выбранной селектором 9 модели 174 узла, осуществляется арифметическим блоком 5, блоком

0 7 и селектором 8 следующим образом.

Арифметический блок 5 определяет приращения координат, соответствующие согласно соотношениям (1) и (2) текущим значениям опрашиваемыос ко5 ординат X и У, а также двум значениям управляющего параметра +U и -U. Его работу (фиг. 3)рассмотрим с момента формирования импульсного сигнала на выходе 98 (фиг. 6) генерато-

0 ра 10 знака, который поступает по шине 98 и устанавливает триггер 85 в единичное состояние. Одновременно выходной сигнал, действующий на шине 98 генератора 10 знака, изменяет

на единицу состояние счетчика 159 селектора 9 узла сети. Триггер 85 в единичном состоянии открывает сигналом прямого выхода элементы И 89 и 91, которые подключают выходы уз0 лов 66 и 68 вычисления дополнительного кода к входам сумматоров 75 и 76 соответственно. Последовательные двоичные коды параметров а и а поступают, начиная с младшего

5 разряда, с выходов 54 и 56 блока 3 памяти на входы 54 и 56 арифметического блока 5 соответственно и через узлы 66 и 68, элементы И 89 и 91

на входы сумматоров 75 и 76 соответственно. Последовательные двоичные сумматоры 75 и 76 за п тактов суммируют содержимое регистров 71 и 72 соответственно с двоичными кодами параметров а i соответственно, а результаты суммирования а, и 51а,, сдвигаются под действием тактовых импульсов на входе 37 в регистры 71 и .72 соответственно. Узлы 66 и 68 пропускают двоичные коды параметров а, и а,, без изменения, если координата X положительна и на шине 95 арифметического блока 5 действует нулевой сигнал. Если координата X отрицательна, то на шине 95 действует единичный сигнал, которьш переключает узлы 66 и 68 в режим формирования дополнительного кода. После п-го такта триггер 85 возвращается в нулевое состояние сигналом поступающим по шине 38 с выхода блока 2 управления.

Таким образом, в процессе опроса селектором 9 координаты X в регистрах 71 и 72 накапливаются алгебраические суммы параметров Za, и Zaj которые равны величинам и а,Х В случае переполнения счетчика 159 (фиг. 6) селектора 9 счетчик 160 изменяет свое состояние на единицу, а сигнал переполнения по шине 97 поступает на вход арифметического блока 5 (фиг. 3) и устанавливает триггер 84 в единичное состояние. Последний в единичном состоянии блокирует элементы И 88 и 90, стирая этим содержимое регистров 71 и 72, а также подключает через элементы И 87 и 93 выходы узлов 65 и 69 к входам сумматоров 74 и 77 соответственно,. Последовательные двоичные коды параметров а и а,2 поступают, начиная с младшего разряда, с выходов 52 и 58 блока 3 памяти на входы 52 и 58 арифметического блока 5 и через узлы 65 и 69, элементы И 87 и 93 на входы сумматоров 74 и 77 соответственно. Последовательные двоичные сумматоры 74 и 77 за п тактов суммируют содержимое регистров 70 и 73 соответственно с двоичными кодами, па- раметров а, и а,2 соответственно, а результаты суммированияZа и 2. a,j, сдвигаются в регистры 70 и 73 . соответственно.

Узлы 65 и 69 пропускают двоичные коды параметров а а без изменения, если координата У положитель- .на и на шине 94 действует нулевой сигнал, либо в дополнительном коде, когда координата У отрицательна и на шине 94 действует единичный сигнал. Спустя п тактов., триггер 84 возвращается в нулевое состояние . сигналом, поступающим по шине 38 с выхода блока 2 управления.

Таким образом, в процессе опроса селектором 9 координаты У в ре- гистрах 70 и 73 накапливаются алгебраические суммы параметров Га и S a,, которые равны величинам а У. и соответственно. Последователь- ньш двоичный сумматор 78 суммирует содержимое регистров 70 и 71, формируя двоичньй код величины а Х+ . Последовательный двоичный сумматор 80 суммирует содержимое регистров 72 и 73, формируя дво- ичный код величины .

Последовательньй двоичный код максимального значения управляющего параметра поступает с выхода 55 блока 3 памяти на вход 55 ариф- метического блока 5 и через узел 67 на вход сумматора 79. Узел 67 пропускает двоичный код параметра Uf без изменения, если триггер 170

генератора 10 знака (фиг. 6) находит- ся в нулевом состоянии (знак и,„ положителен) и на шине 99 арифметического блока 5 действует нулевой сигнал, либо преобразует в дополнительный код, когда триггер 170 генерато- ра 10 знака находится в единичном состоянии (знак U отрицателен) и

на шине 99 действует единичньй сиг- I нал. Последовательный двоичный сумматор 79 формирует двоичный код величин a X+ajj y+U ,7; либо , который, начиная с младшего разряда, сдвигается в регистр 106 блока 81. Блок 107 узла 81 формирует двоичный код абсолютной величины

либо I a,X+a,y-Uj следующим образом. Если в регистр 106 записывается дополнительный код, то в п-м такте срабатывает элемент И 109, выходной сигнал которого переводит

в конце п-го такта триггер 108 в единичное состояние. Единичный сигнал прямого выхода триггера 108 переключает блок 107 в режим формирования

дополнительного кода и поступает в виде сигнала отрицательного знака на выходную шину 102. В результате блок 107 преобразует дополнительный код регистра 106 в прямой .код который поступает с выходной шины 100 на вхоную шину 100 блока 7 (фиг. 5).

Если в-регистр 106 блока 81 запи- сьгоается: прямой код, то триггер 108 сохраняет нулевое состояние, так как элемент И 109 не срабатывает. В этом случае блок 107 пропускает без изменения содержимое регистра 106 на выходную шину 100 и на выходной шине 102 действует нулевой сигнал.

Аналогичным образом функционирует блок 82, который формирует двоичный код абсолютной величины (а„Х+а У| на выходной шине 101 и сигнал отрицательного знака на выходной шине 103

Спустя каждые п тактов блоки 65-6 и 107 сбрасываются в исходное состояние сигналами, поступающими по входу 39 с выхода блока 2 управления

Цепи блокировки переноса сумма- торов 74-80 срабатывают через п тактов по сигналам, поступающим по шине 38 с выхода блока 2 управления.

В случае, переполнения счетчика

160(фиг. 6) селектора 9 счетчик

161изменяет свое состояние на единицу, а сигнал переполнения по шине 96 поступает на вход вычислителя 5 (фиг. 3), устанавливая триггер 83

в единичное состояние. Сигнал инверсного выхода триггера 83 блокирует э.лементы И 86 и 92, стирая содержимое регистров 70 и 73. Спустя п тактов триггер 83 возвращается в нулевое состояние сигналом, действующим на шине 38.

Блок 7 сравнения приращений координат (фиг. 5) работает следующим образом.

Двоичные коды абсолютных величин приращений координат X и У поступают с вычислителя 5 на входные шины 100 и 101 блока 7 соответственно. Элементы 138 и 139 задержки на такт обеспечивают сдвиг на один разряд выходных последовательных двоичных кодов по отношению к входным двоичным кодам. Так как на входы 100 и 101 двоичные коды поступают, начиная с младших разрядов, то сдвиг осуществляется на один разряд, в сторону старших разрядов. Следовательно, на выходах элементов 138

5

и 139 действуют последовательные двоичные коды величин 2|а Х+а У+U) и 2|а Х+а,У соответственно. Узлы 136 и 137 сравнивают двоичные коды приращения лХ с удвоенным значением приращения ДУ и приращения ДУ с удвоенным значением приращения йХ соответственно. На первом, втором или третьем выходах узла 136 формируется сигнал логической едини1№1,

йУ 1 ЛУ 1 ™ 2 соответственно. На первом, втором и третьем выходах узла 137 формируется сигнал логической единицы, если

, - 2, либо - 2 соответст- дХ дХ йХ

венно. На выходах элементов ИЛИ 140 и 141 формируется сигнал логической

« АУ I

либо Л 4

ДУ I единицы, если -у у

ДУ о и -- 2 соотДХ

ветственно. Работа узлов 136 и 137 синхронизируется сигналами, поступающими по шиие 37 от генератора 12 импульсов блока 2 упра вления, с выходной шины 39 которого поступают через каждые п тактов сигналы сброса блоков 136 и 137 сравнения.

Выходные сигналы блока 7 поступают в селектор 8 ветви сети на входы элементов И 145-147, которые срабатывают через каждые п тактов по сигналу, поступающему по шине 38 с выхода блока 2 управления. В зави- симости от комбинации входных сигналов один из триггеров 142-144 устанавливается в единичное состояние. Например, триггеры 142, 143 и 144 устанавливаются в единичное состояние, если

„. . АУ I . 1 АУ , дУ - 2 il(. .

Три указанных случая соответст- вуют выбору горизонтальной, диагональной или вертикальной ветви сети. На входы 102 и 103 селектора 8 поступают сигналы знаков приращений л У и дХ с выходов 102 и 103 вычислителя 5 соответственно. С помощью элементов И 148-155 по сигналам триггеров 142-144, элементов НЕ 156- 157 и сигналам знака приращений ДХ и ДУ формируется сигнал логической единицы на одном из выходов 158, который поступает ; в модель 1 сети в модели 175 ветвей. На выходах элементов И 148 и 149 формируется сигнал выбора левой или правой горизонтальной ветви 175, исходящей из модели 174 узла, выбранной селектором 9.На выходах элементов И 150-151 и 152-153 формируется сигнал для верхней-нижней правой и верхней-нижней левой диагональной модели 175 ветви соответственно.На выходах элементов И 154 и 155 фор- мируе.тся сигнал для верхней или нижней вертикальной модели 175 ветви соответственно. Единичный сигнал на шинах 131 и 130 соответствует выбору диагональных или вертикальных моделей 175 ветвей.

Арифметический блок 6 (фиг. 4) формирует приращения функционала следующим образом.

На шины 57 и 59 вычислителя 6 поступают с выходов блока 3 памяти двоичные коды параметров а, и а, , сдвинутые на один разряд в сторону младших разрядов по отношению к двоичным кодам величин а и а„Х+а У, которые поступают на шины 104 и 105 арифметического блока 6 с выходов арифметического блока 5 соответственно. Этот сдвиг обеспечивается элементами 50 и 51 задерж- ки на такт в блоке 3 памяти. Аналогичным образом двоичный код параметра считываемый с выхода 53 блока 3 памяти, сдвинут на один раз ряд в сторону младших разрядов и поступает на входнзто шину 53 арифметического блока 6. На шину 131 поступает сигнал с выхода селектора 8, который в случае диагональной ветви подключает с помощью элемен- та И 122 входную шину 59 к входу сумматора 110.

Последовательный двоичньй сумматор 110 формирует двоичный код суммы

параметров у ( ® случае

диагональной ветви либо двоичный код

2 м в остальных случаях. Блоки 114 пропускают без изменения входные двоичные коды, если на шинах 102 и 103 действуют нулевые сигналы, либо преобразует их в допол- нительные , если на шинах 102 и 103 действуют единичные сигналы, которые поступают с выкодов арифметического блока 5. Коммутаторы 115 и 116 в зависимости от сигнала на шине 130 подключают к

5 10 15

20 25 30 j 0

5

0

входам сумматора 111 шины 104 либо 105 и выходы блоков 113 либо W4. Если с выхода селектора 8 поступает на шину 130 нулевой сигнал, то к первому и второму, входам сумматора 11 1 подключаются выход блока 114 и входная шина 105. В случае единичного сигнала на шине 130 к входам сумматора 111 подключаются выход блока 113 и входная шина 104. На выходе последовательного сумматора 111 формируется двоичный код обратной величины приращения функционала (4), который преобразуется узлом 117 формирования модуля в прямой код абсолютной .величины. Узел 117 аналогичен узлу 81. Спустя калодые п тактов цепи блокировки переносов сумматоров 110-112 срабатывают по сигналам, поступакяцим по шине 38 от блока 2 зшравления, с выходной шины 39 которого поступают сигналы сброса .блоков 113 и 114 дополнительного кода и узла 117 формирования модуля. Импульсы синхронизации поступают на входы узла 117 формирования модуля и регистра 118 сдвига по шине 37 от генератора 12 блока 2 управления. В случае единичного состояния триггера 120 последовательный сумматор 112 суммирует двоичный код с выхода узла 117 формирования модуля с содержимым регистра 118 до тех пор, пока в п-м разряде на выходе сумматора 112 сформируется единичньй сигнал, которьй через элемент И 124 устанавливает триггер 12 в единичное состояние. Триггер 120 устанавливает в единичное состояние сигнал, поступающий по шине 41 с выхода блока 2 управления. Сигнал прямого выхода триггера 120 открывает элемент И 123, 125 и 126. Счетчик I19 начинает считать количество циклов суммирования сумматором 112 путем подсчета сигналов п-х тактов, поступакщих по шине 38 с выхода блока 2 управления. В момент установки триггера 121 в единичное состояние в двоичном счетчике 119 устанавливается число, пропорциональное приращеишо функционала.

В дальИейшем счетчик 119 продолжает счет до переполнения, сигнал которого через элемент ИЛИ 129сбрасывает триггеры 120 и 121 в нулевое состояние и поступает на вход 34 блока 2 управления. В результате на прямом выходе триггера 121 форми-. руется единичный сигналт, длительност которого пропорциональна величине дополнительного кода приращения функционала . Сигнал прямого выхода триггера 121 проходит через элемент И 127 на шину 133 при единичном сигнале на шине 99, когда триггер 170 генератора 10 знака находится в единичном состоянии, либо проходит через элемент 128 на шину 134, если на шине 132 действует единичный сигнал инверсного выхода триггера 170 генератора 10 знака. Сигнал прямого выхода триггера 121 проходит через Элемент И 127 либо элемент И 128 в модель 1 сети на шины 133 либо 134 соответственно во все модели 174 узлов. Выходной единичный сигнал элемента И 190 выбранной модели 174 узла (фиг. 8), который ера- батывает по выходным сигналам селектора 9 узла сети, снимает блокировку элементов И 189 и 191, через которые на вход счетчика 176 либо 177 (в зависимости от единич- ного сигнала на шинах 133 либо 134) начнут поступать счетные сигналы, действующие на шине 38 блока 2 управления. В счетчике 176 либо 177 установится дополнительный код при- ращения функционала. Единичный сигнал выхода элемента И 190 выбранной модели 174 узла поступает по шине

199на.входы исходящих моделей 175 ветви (фиг. 9) и совместно с сигна- лом селектора 8 ветви сети, действующим на шине 158, приводит к срабатыванию элемента И 205 выбранной модели 175 ветви. Единичный ..сигнал выхода элемента И 205 снимает бло- кировку элементов И 206 и 207 выбранной модели 175 ветви. Единичный сигнал, действующий на одной из

шин 133 и 134 арифметического блока 6, посту-пает на шину 133 или 134 вы бранной :.модели 175 ветви и через элемент И 206 либо 207 устанавли- - вает в единичное состояние триггер

200либо 201.

Таким образом, триггер 20 запоминает., например, отрицательный знак управляющего параметра , а триггер 201 - положительный знак.

j 10 js 20 25 зо

0 j

Q

5

Аналогичным образом осуществляется в режиме настройки модели I сети запись дополнительного кода приращения фукнционала в счетчики 176 либо 177 всех моделей 174 узлов и знаков управляющего параметра U,, в триггеры 200 либо 201 моделей 175 ветви,.исходящих из моделей 174 узлов.

Процесс настройки модели 1 сети после запуска генератора 14 одиночных импульсов блока 2 управления выполняется автоматически. Выходной импульс генератора 14 (фиг.2) через переключатель 28 и элемент ИЛИ 23 устанавливает триггер 19 в единичное состояние и спустя 3 п тактов сдвигается с выхода регистра 16 на выходную щину 41 блока 2 управления, по которой поступает на шину 41 блока 6, где устанавливает триггер 120 (фиг. 4) в единичное состояние, также н.а шину .41- (фиг.6) генератора 10 знака и спустя такт за счет задержки элементов 168.устанавливает триггер 17.0 в единичное состояние. Триггер 120 в арифме тическом блоке 6 (фиг. 4) запускает счетчик 119, сигнал переполнения которого поступает на шину 34 блока 2 управления и через элементы И 22, ИЛИ 23 задерживается в регистре 16 на Зц. тактов и появляется вновь на выходной шине 41 блока 2 управления. Эта цепь генерации сигналов на шине 41 блока 2 управления действует, пока триггер 19 находится в единичном состоянии. Второй сигнал на шине 41 блока 2 управления вновь установит триггер 120 блока 6 в единичное состояние, через элемент И 169 генератора 10 знака (фиг. 6) поступит на вход счетчика 159 селектора 9 узла сети, а также на вход 98 арифметического блока 5. При этом триггер 170 генератора 10 знака спустя время задержки элемент- том 168 возвратится в нулевое состояние.

Таким образом, в процессе настройки модели 1 сети на выходной шине 41 блока 2 управления генерируется последовательность импульсов, которая приводит к поочередному изг менению состояния триггера 170 генератора 10 знака, на выходную шину 98 которого пропускается каждый

второй импульс входной последовательности, действующей на шине 41. Выходная последовательность импульсов на шине 98 генератора 10 знака последовательно изменяет состояние счетчиков 159-161, которые с помощью дешифраторов 162-164 соответственно осуществляют выбор модели 174 узла модели 1 сети. После окончания- опроса всех моделей 174 узла во всех четьфех квадрантах пространства (Х, у) на выходе перепол-г- нения счетчика 161 селектора 9 формируется импульсный сигнал, который поступает на шину 35 блока 2 управления и через элемент ИЛИ 24 сбрасывает триггер 19 в нулевое состояние, который сигналом прямого выхода блокирует элемент И.22.

Таким образом, процесс настройки модели 1 сети заканчивается и устройство готово для моделирования оптимальных процессов управления.

В режиме моделирования переключатель 28 блока 2 управления подключает выход генератора 14 одиночных импульсов к первому входу триггера 20 и к выходной шине 43, которая соединена с шиной 43 блока задания начального узла П. Диспетчер с помощью блока 11 задает координаты Х У(, начального узла сети, например, подключая переключателем 171 входную шину 43 к одной из шин группы выходов 172 и группы выходов I73. Запуск устройства осуществляется кнопочным переключателем 29 блока 2 управления путем запуска генератора 14 одиночных импульсов. Выходной импульс генератора 14 устанавливает триггер 20 в единичное состояние и поступает через блок 11 задания начального узла сети на входы 172 и 173 модели 174 узла, выбранного в качестве начального. Тригер 20 в единичном состоянии подключает через элемент И 21 выход генератора I2 тактовых импульсов к входу десятичного счетчика 15, который измеряет время моделирования, пропорциональное оптимальному значению функционала. Элемент И 186 модели 174 узла, выбранной в качестве начального узла сети, под действием импульсов на шинах 172 и 173 вырабатывает импульсный сигнал, который через элемент ИЛИ 182, И 187 устанавливает триггер 181 в единичное состояние. Элемент И 188 открывает- с сигналом прямого выхода триггера .181, что обеспечивает поступление тактовых импульсов генератора 12 блока 2 управления, действующих на шине 37, на входы счетчиков 176-178. Пусть, например, в счетчике 176

содержится начальный дополнительный код приращения функционала, тогда после переполнения счетчика 176 триггер 179 установится в единичное состояние и на выходе 196 сформируется единичный сигнал, который поступает на шину 196 всех исходящих моделей 175 ветви, а также на вход элемента Ш1И-НЕ 192, на выходе которого формируется сигнал блокировки, поступающий на шины 198 всех моделей 175 ветви, входящих в данную модель 174 узла. Единичный сигнал, действующий на шине 196 модели ветви, в случае единичного состояния триггера 200 пройдет через элементы И 210, ИЛИ 212, И 203 на вход триггера 202, устанавливая его в единичное состояние. Единичный сигнал прямого выхода триггера 202 поступает по шине 193 на один из входов 193 следуняцей модели 174 узла и че- . рез элемент ИЛИ 182 устанавливает триггер 181 в единичное состояние.

Таким образом, сигнал возбуждения начального узла распространяется по моделям 174 узла и моделям 175 ветви до тех пор, пока на один из входов 193 модели 174 конечиого узла не поступит единичный сигиал. Модель конечного узла отличается от моделей 174 остальных узлов наличием связи выхода элемента ИЛИ 182 с входом 194 элемента ИЛИ 183 (связь изображена пунктиром). В этом случае на выходной шине 195 сформируется сигиал логической единицы, который поступает, на шину всех входящих в конечный узел моделей 175. Сигнал с выхода элемента ИЛИ 182

конечного узла поступает также на шину 36 блока 2 управления (фиг. 2) и через элемент ИЛИ 25 сбрасывает триггер 20 в нулевое состояние. Элемент И 21 закрывается., а в счет-.

чике 15 фиксируется оптимальное зна- чение функционала, которое индицируется группой элементов 30 индикации. Появление единичного сигнала

на шине 195 моделей 175 ветви, входящих в конечньй узел, приводит к срабатыванию элемента И 204 в той модели 175 ветви, в которой тригге 202 находится в единичном состоянии. Элемент индикации 216 индицирует модель 175 ветви, принадлежащую Оптимальной траектории. Наличие единичного сигнала на выхо- де элемента И 204 приводит к ера-; батыванию элемента И 208 либо 209 в зависимости от состояний триггеров 200 и 201 соответственно. Элементы 213 либо 214 индикации ин- дуцируют знак (отрицательньш либо положительный) оптимального управляющего параметра-и. Единичный сигнал с выхода элемента И 204 поступает по шице 194 на одну из шин 194 модели 175 узла и далее распространяется аналогичным образом до модели 175 начального узла.

Таким образом, элементы индикации модели 1 сети индицируют опти- мальные траектории, оптимальное. управление, а счетчик 15 блока 2 -управления фиксирует оптимальное значение функционала.

Моделирование может произно- диться многократно с различных начальных узлов, так как информация в моделях 174 узлов восстанавливается . Действительно, если счетчик 176 и 177 начинает счет с на

чального дополнительного кода приращения функционала, то счетчик 178 начинает счет с нуля. Поэтому, с момента переполнения счетчика, например I76 до момента переполнения счетчика 178 в счетчике 176 восстановится начальный дополнительный код приращения функционала, а сигнал переполнения счетчика 178 сбрасывает триггер 181 в нулевое состояние.

Подготовка устройства к повторному моделированию (режим возврата) обеспечивается нажатием кнопочного переключателя 27 (фиг. 2), который с помощью триггера 18 формирует сиг- нал сброса на выходной щине 42 блока 2 управления. Этот сигнал сброса устанавливает счетчик 15 блока 2 управления в нулевое состояние, а также сбрасывает в нулевое состояние .триггеры 179 и 180 всех моделей 174 узлов и триггеры 202 всех моделей 17 ветвей.

0 s 0

5

О

5

Q

5

Формула изобретения

Устройство для определения оптимальных траекторий, содержащее модель сети, блок памяти и блок управления, отличающееся тем, что, с целью повьппения точности решения, в него введены блок ввода данных, арифметический блок вычисления приращений координат, арифметический блок вычисления приращений функционала, блок сравнения приращений координат, селектор ветви сети, селектор узла сети, генератор знака и блок задания начального узла, причем первая группа выходов блока управления, содержащая п шин, где п - количество разрядов представления исходных данных, соединена соответственно с первого по п-й информационными входами блока ввода данных, вход запуска которого соединен с вторым выходом блока управления, входы разрешения записи с первого по пятый блока памяти соединены соответственно с первого по пятый выходами блока ввода данных, шестой выход которого соединен с информа- 1ЩОННЫМ входом блока памяти, вход синхронизации которого соединен с третьим выходом блока управления, информационные входы с первого по пятый арифметического блока В1.:чис- ления приращений координат соединены соответственно с первого по пятый выходами блока памяти, с шестого по восьмой выходы которого соединены соответственно с первым по третий информационными входами арифметического блока вычисления приращений функционала, входы синхронизации с первого по четвертый арифметического блока вычисления приращений координат соединены соответственно с третьего по шестой выходами блока управления, выходы котог рого с третьего по седьмой соединен, ны соответственно с первого по пятый входами з равления арифметического

блока вычисления приращений функционала, первый выход которого соединен с первым входом блока управления, первый и второй выходы арифметического блока вычисления прираще- НИИ координат соединены соответственно с первым и вторым информационными входами блока сравнения прира- ;

щений координат, входы синхронизации которого соединены соответственно с третьим и пятым выходами блока управления, выходы блока сравнения приращений координат с первого по четвертый соединены соответственно с первым по четвертьй входами селектора ветви сети, пятый и шестой входы которого соединены соответственно с Третьим и четвертым выходами арифметического блока вычисления приращений координат, а седь- . мой вход - с четвертым выходом блока управления, с первого по четвертьй выходы селектора узла сети соединены соответственно с шестого по девятый информационными входами арифметического блока вычисления приращений координат, десятый и оди надцатый информационные входы которого соединены соответственно с первым и вторым выходами генератора знака, с третьего по шестой выходы арифметического блока вычисления приращений координат соединены соответственно с четвертым по седьмой информационными входами арифметического блока вычисления приращений функционала, восьмой и девятый информационные входы которого соединены соответственно с вторым и третьим выходами генератора знака, пятый выход селектора узла сети соединен с вторым входом блока управления, шестой и седьмой выходы которого соединены с первым и вторым входами генератора знака, шее- той выход блока управления соеди- нен с входом сброса селектора узла сети, вход синхронизации которого соединен с первым выходом генератора знака, первый и второй выходы селектора ветви сети соединены соответственно с шестым и седьмым входами управления арифметического блока вычисления приращений функционала, второй и третий выходы которого соединены соответственно с первым и вторым входами ввода данных модели сети, третий, четвертый, шестой и восьмой выходы блока управления соединены соответственно с первым, вторым, третьим и четвертым входами управления модели сети, выход останова которой соединен с третьим входом блока управления, шестая группа выходов с первого по К-й

где К - количество первых адресов, седьмая группа выходов с первого по . Р-й, где Р - количество вторых ад- 5 ресов, и восьмая группа выходов с первого по четвертый третьих адресов селектора узла сети соединены соответственно с первой, второй и третьей группами адресных входов

10 модели сети, четвертая группа с первого по восьмой адресных входов которой соединены соответственно с третьим по десятый выходами селектора ветви.сети, девятый выход блока

15 управления соединен с входом блока задания начального узла, первая группа с первого по М-й и вторая группа с первого по N-й выходов, где MX N - количество начальных узлов се20

25

30

ти, которого соединены соответственно с первой и второй группами входов запуска модели сети, причем блок управления содержит генератор импульсов, распределитель импульсов, генератор одиночных импульсов, счетчик, регистр сдвига, четыре триггера, два элемента И, три элемента ИЛИ, четыре коммутатора, группу элементов индикации, два элемента индикации и элемент задержки, причем выход генератора импульсов соединен с входом распределителя импульсов, выходы п разрядов которого являются первой группой выходов блока управления, выход п-го разряда распределителя импульсов соединен с входом синхронизации регистра сдвига, с входом элемента задержки и через генератор одиночных импульсов - с

входом первого коммутатора, первый вьгход которого является вторым выходом блока управления, выход генератора импульсов соединен с третьим выходом блока, управления и.с первым

входом первого элемента И, выход которого соединен с информационным входом счетчика, выходь разрядов которого соединены с входами группы . элементов индикации, четвертый, пятый, шестой, седьмой и восьмой выходы блока управления соединены со ответственно с выходом п-го разряда распределителя импульсов, выходом элемента задержки, прямым выходом первого триггера, выходом регистра сдвига и прямым выходом второго триггера, вход управления генератора одиночных импульсов соединен

ерез второй коммутатор с инверсным выходом первого триггера, прямой выход которого соединен с первьми входами первого и второго элементов ИЛИ, второй выход первого коммутатора соединен с первым входом третьего элемента ИЛИ, выход которого соединен с информационным вхоом регистра сдвига и с первым входом третьего триггера, третий выход первого коммутатора соединен с девятым выходом блока управления и с первым входом четвертого триггера, прямой выход которого соединен с вторым входом первого элемента И и с входом первого элемента индикации, прямой выход третьего триггера соединен с входом второго элемента индикации и с первым вхоом второго элемента И, выход и второй вход которого соединены соотетственно с входом третьего элеента ИЛИ и с первым входом блока правления, вторые входы третьего четвертого триггеров соединены соответственно с выходами первого и второго элементов ИЛИ, вторые входы которых являются соответств.ен- но вторым и третьим входами блока управления, входы первого и второго триггеров соединены соответственно через третий и четвертый коммутаторы с нулевой шиной устройства, а выход второго триггера - с входом сброса счетчика, арифметический блок вычисления приращений координат содержит пять узлов вычисления дополнительного кода, четыре регистра сдвига, семь сумматоров, два узла формирования модуля, три триггера и восемь элементов И, причем информационные входы с пер- . вого по пятый узлов вычисления дот полнительного кода соединены ответственно с первым по пятый информационными входами арифметического блока вычисления приращений координат, щестой информационный вход которого соединен с входами синхронизации первого и пятого узлов вычисления дополнительного кода, входы синхронизации второго и четвертого узлов вычисления дополнительного кода соединены с седьмым информационным входом арифметического блока вычисления приращений координат, информационные входы с

восьмого по десятый которого соединены соответственно с первыми входами с первого по третий триггеров, 5 информационные входы с первого по четвертый регистров сдвига соединены соответственно с выходами с первого по четвертый сумматоров, первые входы KOTOpblx соединены соот0 ветственно с выходами с первого по четвертый элементов И, выходы первого и второго сумматоров соединены через пятый сумматор с первым входом шестого сумматора, второй

5 вход которого соединен с выходом

третьего узла вычисления дополнительного кода, управляющий вход которого является одиннадцатым информационным входом арифметического блока

0 вычисления приращений координат,

первый вход управления которого соединен с входами синхронизации с первого по четвертый регистров сдвига и входами синхронизации первого и

5 второго узлов формирования модуля, входы сброса с первого по пятый узлов вычисления дополнительного кода и первые входы сброса первого и -второго узлов формирования модуля сое0 динены с третьим входом управления арифметического блока вычисления приращений координат, второй вход управления которого соединен с входами сбросов с первого по седьмой

5 сумматоров, с вторыми входами сбросов первого и втогого узлов форми- .

рования модуля и с вторыми входами с первого по третий триггеров, выходы первого, второго, четвертого и

0 пятого узлов вычисления дополнительного кода соединены соответственно с первыми входами с пятого по восьмой элементов И, выходы которых соединены соответственно с вторыми

5 входами с первого по четвертый сумматоров, первые входы с первого по четвертый элементов И соединены соответственно с выходами с первого по четвертый регистров сдвига, вхо0 ды синхронизации и ввода данных которых соединены соответственно с четвертым входом управления арифметического блока вь1числения приращений координат НС шиной нулевого

5 потенциала устройства, инверсные выходы первого и второго триггеров соединены соответственно с вторыми . |Входами первого, четвертого и второго, третьего элементов И, прямые выходы второго и третьего триггеров соединены соответственно с вторыми входами пятого, восьмого и шестого, седьмого элементов И, выход шестого сумматора соединен с информационным входом первого узла формирования модуля, выполненного в виде узла вычисления дополнительного кода, регистра сдвига, триггера и элемента И, первый вход которого соединен с информационным входом узла формирования модуля и с информационным входом регистра сдвига, выход которого соединен с информационным входом узла вычисления дополнительного кода, вход сброса которого соединен с первым входом сброса узла формирования модуля, второй вход сброса узла формирования модуля соединен с вторыми входами элемента И, триггера, первый вход которого соединен с выходом элемента И, вход синхронизации регистра.сдвига соединен с входом синхронизации .узла формирования модуля,- первый выход которого соединен с выходом узла вычисления дополнительного кода, вход синхронизации которого соединен с прямым выходом триггера и с вторым выходом узла формирования модуля, выходы третьего и четвертого сумматоров соединены через седьмой сумматор с информационным входом второго узла формирования модуля, с первого по шестой выходы арифметического блока вычисления приращений .координат соединены соответствен- :но с первым выходом первого узла формирования модуля, первым выходом второго узла формирования модуля, вторым выходом первого узла формирования модуля, вторым входом второго узла формирования модуля, выходом шестого сумматора и выходом v седьмого сумматора, арифметический блок вычисления приращений функционала содержит три сумматора, два узла вычисления дополнительного кода, два коммутатора, узел формирования модуля, регистр сдвига, счетчик, два триггера, семь элементов И и элемент ИЛИ, причем с первого по третий информационные входы арифметического блока вычисления прираще- иий функционала соединены соответственно с информационным входом первого узла вычисления дополнительного кода, с первым входом первого сумма- тора и первым входом первого элемента И, выход которого соединен с вторым входом первого сумматора, четвертый информационный вход арифметического блока вычисления приращений функционала соединен с входом сброса счетчика и первым входом элемента ИЛИ, второй вход которого соединен с выходом переполнения счетчика, выход первого сумматора соединен с информационным входом второго узла вычисления дополнительного кода, управляющий вход которого соединен с пятым информационным входом арифметического блока вычисления

приращений функционала, шестой и

седьмой информационные входы которого соединены с входами первого коммутатора, выход которого соединен с первым входом второго сумматора,

выходы первого и второго узлов вычисления дополнительного кода соединены с информационными входами второго коммутатора, выход которого соединен с вторым входом второго сумматора, первый вход управления арифметического блока вычисления приращений функционала соединен с входами синхронизации регистра сдвига, узла формирования модуля, информационный вход которого соединен с выходом второго сумматора, второй вход управления а.рифметического блог ка вычисления приращений функционала соединен с входами сброса с первого по третий сумм аторов, с первыми входами второго и третьего элементов И и с первым входом сброса узла формирования модуля, второй вход сброса которого соединен с

входами сброса первого и второго узлов вычисления дополнительного кода и с третьим входом управления арифметического блока вычисления приращений функционала, с четвертого по шестой входы управления которого соединены соответственно с управлякяцим входом первого узла вычисления дополнительного кода, первым входом первого триггера и вторым

входом первого элемента И, выходы четвертого и пятого элементов И соединены с входами третьего сумматора, выход которого соединен с вторым

входом третьего элемента И, с ин- ;формационным входом регистра сдвига выход которого соединен с первым входом четвертого элемента И, выход узла формирования модуля соединен с перньш входом пятого элемента И, второй вход которого соединен с вторыми входами второго и четвертого элементов И и с прямым выходом первого триггера, выход второго элемента И соединен с информационным входом счетчика, выход третьего .элемента И - с первым входом второго триггера, прямой выход которого соединен с первыми входами шестого и седьмого элементов И, выход элемента ИЛИ соединен с вторыми входами первого и .второго триггеров и с первым выходом арифметического бло- ка вычисления приращений функционала, второй и третий выходы которого соединены соответственно с выходами шестого и седьмого элементов И, вторые входы которых соединены -соот- ветственно с восьмым и девятым информационными входам арифметического блока вычисления приращений функционала, седьмой вход управления которого соединен с управляющим входами первого и второго коммутаторов , модель сети выполнена в виде моделей узлов и моделей ветвей, каждая из моделей ветвей содержит три триггера, девять элементов И, три блока индикации и элемент РШИ, выход которого соединен с информационным входом первого элемента И, выход которого подключен к первому входу первого триггера, выход кото- рого соединен с информационным входом второго элемента И, выход которого подключен к входу первого блока индикации и соединен с информационными входами третьего и чет- вертого элементов И, выходы которых подключены к входам второго и третьего блоков индикации, выходы второго и третьего триггеров соединены соответственно с управлянвдими входами третьего, четвертого, пятого и шестого элементов И, выходы пятого и шестого элементов И подключены к входам элемента ИЛИ, выход седьмого элемента И соединен с информахщонными входами восьмого |и девятого элементов И, выходы которых соединены соответственно с

первыми входами второго и третьего триггеров, каждая модель узла содержит два счетчика, три триггера, четыре элемента ИЛИ, шесть элементов И и элемент ИЛИ-НЕ, входы которого соединены с прямыми выходами первого, второго и третьего триггеров, инверсный выход первого триггера соединен с управляющим входом первого элемента И, выход которого подключен к первому входу второго триггера, второй вход которого соединен с разрядом переполнения первого счетчика, счетньш вход которого соединен с первыми входами первого и второго элементов ИЛИ и подключен к выходу второго элемента И, управляющий вход которого соединен с прямым выходом второго триггера, выход третьего элемента И подключен к информационным входам четвертого и пятого элементов И, выход четвертого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, выход переполнения которого соединен с первым входом первого триггера, второй вход которого соединен с первым входом третьего триггера, второй вход которого подключен, к разряду переполнения третьего счетчика, счетный вход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, первый управляняций вход которого объединен с первым управлякмцим входом четвертого элемента И, выход шестого элемента И подключен к первому входу третьего элемента ИЛИ, выход которого соединен с первым входом четве ртого элемента ИЛИ и с вторым управляющим входом первого элемента И, информационный вход которого соединен с инверсным выходом третьего триггера, выход четвертого элемента И подключен к второму входу второго элемента ШШ,модели ветвей и модели узлов соединены согласно топйлогии пространства траекторий, причем вторые входы второго и третьего триггеров всех моделей ветвей и синхровкоды счетчиков всех моделей узлов подключены к третьему входу модели сети, выходы третьих элементов ИЛИ всех моделей ветвей

лодключены к выходу останова модели сети, информационные входы вторых элементов И всех моделей узлов подключены к первому управляющему входу модели сети, второй управлякщий вход которой соединен с первым управ- лякацим входом четвертого элемента И всех моделей; узлов, четвертый управляющий вход модели сети подключен к второму входу первого триггера каждой модели узла, первый и второй информационные входы модели сети соединены соответственно с вторыми управляющими входами четвертого- и пя-. того элементов И каждой модели узла 7

первые входы шестых элементов И всех моделей узлов соединены с первой группой входа запуска модели сети, вторая группа входов запуска которой подключена к вторым входам шестых элементов И всех моделей узлов, первые, вторые и третьи входы третьих элементов И всех моделей узлов подключены соответств-енно к первой, второй и третьей группам адресных входов модели сети, четвертая группа адресных входов которой соединена с управляющими входами седьмых элементов И всех моделей

ветвей.

I

1 iFl

сю

i i

2

Р4

00fe

t ТТ

т 97

99

Фи.г.4

Фиг.5

/tf4..VM

73

616 (

r , yfy j

A A

iJ5 Sff

73 I/7J

616 (

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения игровых задач на вычислительных сетях | 1982 |

|

SU1104522A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для моделирования графа | 1985 |

|

SU1278877A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для вывода графической информации | 1978 |

|

SU752403A1 |

| Устройство для вычисления местоположения транспортного средства | 1988 |

|

SU1589292A1 |

| Устройство для отображения векторов на экране элт | 1977 |

|

SU739585A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах для оптимизации и в системах оптимального управления технологическими объектами в различных отраслях про- мьшшенности. Цель изобретения - повьшение точности решения. Указанная цель достигается введением в устройство блока ввода данных, арифметического блока вычисления приращений координат, арифметического блока вычисления приращений функционала, блока сравнения приращений координат, селектора ветви сети, селектора узла сети, генератора знака и блока задания начального узла. Состояние технологического объекта необходимо перевести с помощью управ- лякнцего. параметра U из начального состояния(Х, Уд )в конечное (Xj,0, Уу 0), обеспечив оптимизацию функционала вида мин J dt. Для решения U Т0 поставленной задачи необходимо с помощью устройства найти оптимальную траекторию в пространстве состояний (Х, у), оптимальное.управление и и оптимальное значение функционала. 9 ил. i (Л ю со to 4

т

№7

гк

/t3

ZuB -ч

| Авторское свидетельство СССР № 758179, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения оптимальных траекторий | 1978 |

|

SU748429A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-07—Публикация

1983-04-28—Подача