Фиг.1

112

Изобретение относится к электротехнике и может быть использовано в стабилизированных конверторах, вторичных источниках питания, ключевых усилителях сигналов низкой частоты и т.п.

Целью изобретения является улучшение динамических характеристик при повьшении надежности устройства.

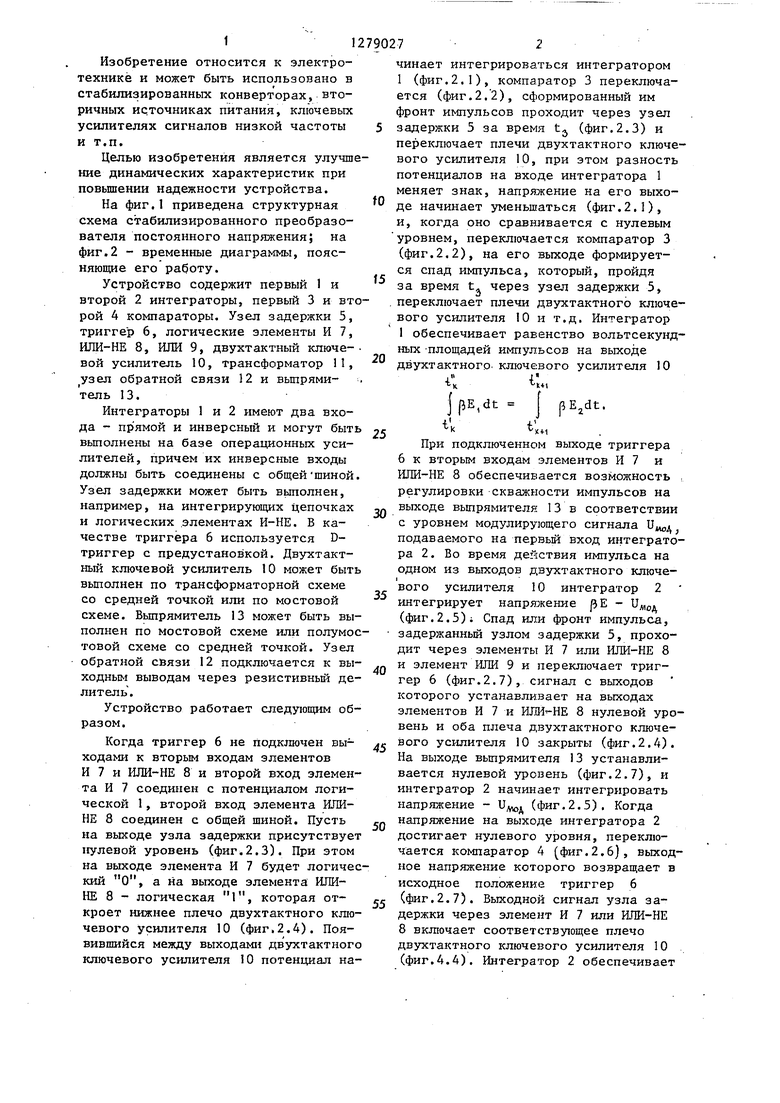

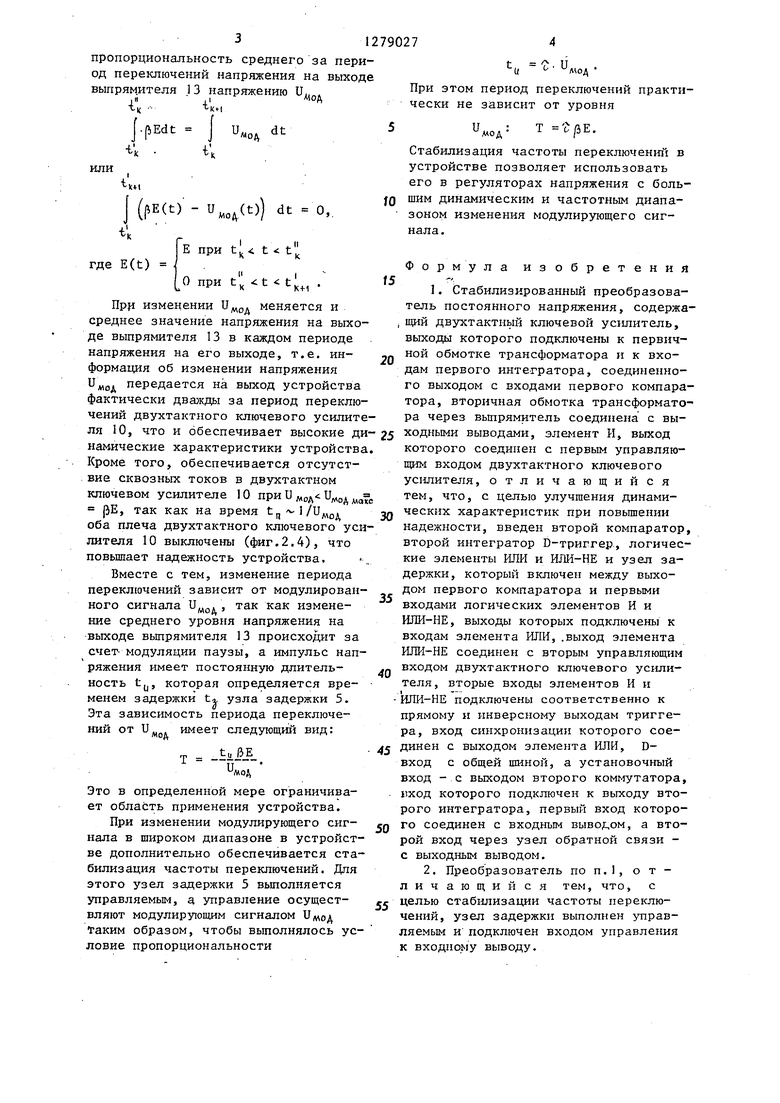

На фиг.1 приведена структурная схема стабилизированного преобразователя постоянного напряжения; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит первый 1 и второй 2 интеграторы, первый 3 и второй 4 компараторы. Узел задержки 5, триггер 6, логические элементы И 7, ИЛИ-НЕ 8, ИЛИ 9, двухтактный ключевой усилитель 10, трансформатор И, узел обратной связи 12 и вьшрями- тель 13.

Интеграторы 1 и 2 имеют два входа - пр ямой и инверсный и могут быть вьшолнены на базе операци:онных усилителей, причем их инверсные входы должны быть соединены с общей шиной. Узел задержки может быть выполнен, например, на интегрирующих цепочках и логических .элементах И-НЕ. В качестве триггера 6 используется D- триггер с предустановкой. Двухтактный ключевой усилитель 10 может быть вьтолнен по трансформаторной схеме со средней точкой или по мостовой схеме. Выпрямитель 13 может быть выполнен по мостовой схеме или полумостовой схеме со средней точкой. Узел обратной связи 12 подключается к выходным выводам через резистивный делитель .

Устройство работает следующим образом.

Когда триггер 6 не подключен выходами к вторым входам элементов И 7 и ИЛИ-НЕ 8 и второй вход элемента И 7 соединен с потенциалом логической 1, второй вход элемента ИЛИ- НЕ 8 соединен с общей шиной. Пусть на выходе узла задержки присутствует нулевой уровень (фиг.2.3). При этом на выходе элемента И 7 будет логический О, а на выходе элемента ИЛИ- НЕ 8 - логическая 1, которая откроет нижнее плечо двухтактного ключевого усилителя 10 (фиг,2.4). Появившийся между выходами двухтактного ключевого усилителя 10 потенциал на

5

0

5

чинает интегрироваться интегратором 1 (фиг.2.1), компаратор 3 переключается (фиг.2.2), сформированный им фронт импульсов проходит через узел задержки 5 за время t (фиг.2.3) и переключает плечи двухтактного ключевого усилителя 10, при этом разность потенциалов на входе интегратора 1 меняет знак, напряжение на его выходе начинает уменьшаться (фиг.2.1), и, когда оно сравнивается с нулевым уровнем, переключается компаратор 3 (фиг.2.2), на его выходе формируется спад импульса, который, пройдя за время t через узел задержки 5, переключает плечи двухтактного ключевого усилителя 10 и т.д. Интегратор 1 обеспечивает равенство вольтсекунд- ных -площадей импульсов на вьпсоде двухтактного, ключевого усилителя 10

(V

IF

dt

il

ш

1 Р

tn

.

0

5

0

5

0

5

При подключенном выходе триггера 6 к вторьп входам элементов И 7 и ИЛИ-НЕ 8 обеспечивается возможность , регулировки скважности импульсов на выходе вьтрямителя 13 в соответствии с уровнем модулирующего сигнала Uj подаваемого на первьй вход интегратора 2. Во время действия импульса на одном из выходов двухтактного ключевого усилителя 10 интегратор 2 интегрирует напряжение рЕ - U. (фиг.2.5); Спад или фронт импульса, задержанный узлом задержки 5, проходит через элементы И 7 или ИЛИ-НЕ 8 и элемент ИЛИ 9 и переключает триггер 6 (фиг.2.7), сигнал с выходов которого устанавлиззает на выходах элементов И 7 и ИЛИ -НЕ 8 нулевой уровень и оба плеча двухтактного ключевого усилителя 10 закрыты (фиг.2.4). На выходе вьшрямитсзля 13 устанавливается нулевой уровень (фиг.2.7), и интегратор 2 начинает интегрировать напряжение - и,д (фиг.2.5), Когда напряжение на выходе интегратора 2 достигает нулевого уровня, переключается компаратор 4 (фиг.2.6), выходное напряжение которого возвращает в исходное положение триггер 6 (фиг.2.7). Выходной сигнал узла з а- держки через элемент И 7 или ИЛИ-НЕ 8 включает соответствующее плечо двухтактного ключевого усилителя 10 (фиг.4.4). Интегратор 2 обеспечивает

31279027

пропорциональность среднего за перипереключении напряжения на выходе рямителя 13 напряжению U,

4

4 t|{

J.fiEdt

-ЧоА

и

i .

i

«Oft

dt

или

X

J frE(t) - U,(t)) dt 0,.

i . где E(t)

E при t t t;;.

0 при t . t t

K-H

ПРИ изменении меняется и среднее значение напряжения на выходе выпрямителя 13 в каждом периоде напряжения на его выходе, т.е. информация об изменении напряжения Mof, передается на выход устройства фактически за период переключений двухтактного ключевого усилителя 10, что и обеспечивает высокие ди- 25 ходными выводами, элемент И, выход намические характеристики устройства. Кроме того, обеспечивается отсутствие сквозных токов в двухтактном ключевом усилителе 10 приП . рЕ, так как на время ,;, 30 оба плеча двухтактного ключевого усилителя 10 выключены (фиг.2.4), что повьшает надежность устройства.

Вместе с тем, изменение периода переключений зависит от модулирован35

которого соединен с первым управляю щим входом двухтактного ключевого усилителя, отличающийся тем, что, с целью улучшения динамических характеристик при повьшении надежности, введен второй компарато второй интегратор D-триггер, логиче кие элементы ИЛИ и ИЛИ-НЕ и узел за держки, который включен между выходом первого компаратора и первыми входами логических элементов И и ИЛИ-НЕ, выходы которых подключены к входам элемента ИЛИ, .выход элемента ИЛР1-НЕ соединен с вторым управляющи входом двухтактного ключевого усили теля, вторые входы элементов И и - ИЛИ-НЕ подключены соответственно к прямому и инверсному выходам триггера, вход синхронизации которого сое ле динен с выходом элемента ИЛИ, D- вход с общей шиной, а установочный вход - с выходом второго коммутатор которого подключен к выходу вто рого интегратора, первый вход которо го соединен с входным выво,ом, а вто рой вход через узел обратной связи - с выходным выводом.

ного сигнала U

моА

так как изменение среднего уровня напряжения на выходе вьшрямитеЛя 13 происходит за счет модуляции паузы, а импульс напряжения имеет постоянную длительность tjj, которая определяется временем задержки t узла задержки 5. Эта зависимость периода переключений от и

«оА

имеет следующий вид:

Т

.

Это в определенной мере ограничивает область применения устройства.

При изменении модулирующего сигнала в широком диапазоне в устройстве дополнительно обеспечивается стабилизация частоты переключений. Для этого узел задержки 5 выполняется управляемым, а управление осуществляют модулиругощим сигналом Таким образом, чтобы выполнялось условие пропорциональности

t,.

и.

O

5

0

ц

При этом период переключений практически не зависит от уровня

UMOA т /jE.

Стабилизация частоты переключений в устройстве позволяет использовать его в регуляторах напряжения с большим динамическим и частотным диапазоном изменения модулирующего сигнала.

Формула изобретения

1. Стабилизированный преобразователь постоянного напряжения, содержащий двухтактный ключевой усгшитель, выходы которого подключены к первичной обмотке трансформатора и к входам первого интегратора, соединенного выходом с входами первого компаратора, вторичная обмотка трансформатора через вьтрямитель соединена с выходными выводами, элемент И, выход

которого соединен с первым управляющим входом двухтактного ключевого усилителя, отличающийся тем, что, с целью улучшения динамических характеристик при повьшении надежности, введен второй компаратор, второй интегратор D-триггер, логические элементы ИЛИ и ИЛИ-НЕ и узел задержки, который включен между выходом первого компаратора и первыми входами логических элементов И и ИЛИ-НЕ, выходы которых подключены к входам элемента ИЛИ, .выход элемента ИЛР1-НЕ соединен с вторым управляющим входом двухтактного ключевого усилителя, вторые входы элементов И и ИЛИ-НЕ подключены соответственно к прямому и инверсному выходам триггера, вход синхронизации которого сое- динен с выходом элемента ИЛИ, D- вход с общей шиной, а установочный вход - с выходом второго коммутатора, которого подключен к выходу второго интегратора, первый вход которого соединен с входным выво,ом, а второй вход через узел обратной связи - с выходным выводом.

2. Преобразователь по п.1, о т - л и ч а ю щ и и с я тем, что, с целью стабилизации частоты переклю

чений, узел задержки выполнен управляемым И подключен входом управления к входному выводу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный преобразователь постоянного напряжения | 1984 |

|

SU1241372A1 |

| Широтно-импульсный модулятор | 1983 |

|

SU1226640A1 |

| Широтно-импульсный модулятор | 1984 |

|

SU1203694A1 |

| Усилитель мощности класса "Д | 1981 |

|

SU1030952A1 |

| Управляемый преобразователь напряжения | 1983 |

|

SU1130851A1 |

| Широтно-импульсный модулятор | 1985 |

|

SU1256188A1 |

| Широтно-импульсный модулятор | 1984 |

|

SU1256187A1 |

| Широтно-импульсный модулятор | 1981 |

|

SU1022306A1 |

| Регулятор напряжения | 1985 |

|

SU1288847A1 |

| Усилитель класса "Д | 1983 |

|

SU1170582A1 |

Изобретение относится к электротехнике, в частности к вторичным источникам электропитания. Цель изобретения - улучшение динамических характеристик при повьшении надежности, а также стабилизация частоты переключений. Подключение выхода триггера 6 к вторым входам элементов И 7 и ИЛИ-НЕ 8 обеспечивает регулировку скважности импульсов на выходе вьтрямителя 13 в соответствии с уровнем модулирующего сигнала, подаваемого на интегратор 2. Информация об изменении модулирующего сигнала передается на выход устройства дважды за период переключения двухтактного ключевого усилителя 10. Это улучшает динамические характеристики. Надежность повышается тем, что в усилителе 10 .отсутствуют сквозные токи, так как на время, обратно пропорциональное модулирующему сигналу, оба плеча усилителя 10 выключены. Стабилизация частоты переключений осуществляется узлом 5 задержки, управляемым модулирующим сигналом. 1 з.п. ф-лы, 2 ил. с $ (П С CD О ю

| Стабилизированный конвертор | 1977 |

|

SU655044A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-10—Подача