fPus.f

Изобретение относится к электротехнике и может быть использовано для вторичных источников питания, коллекторных модуляторов передатчиков, усилителей низких частот и т.п.

Цель изобретения - расширение области применения регулятора напряжения.

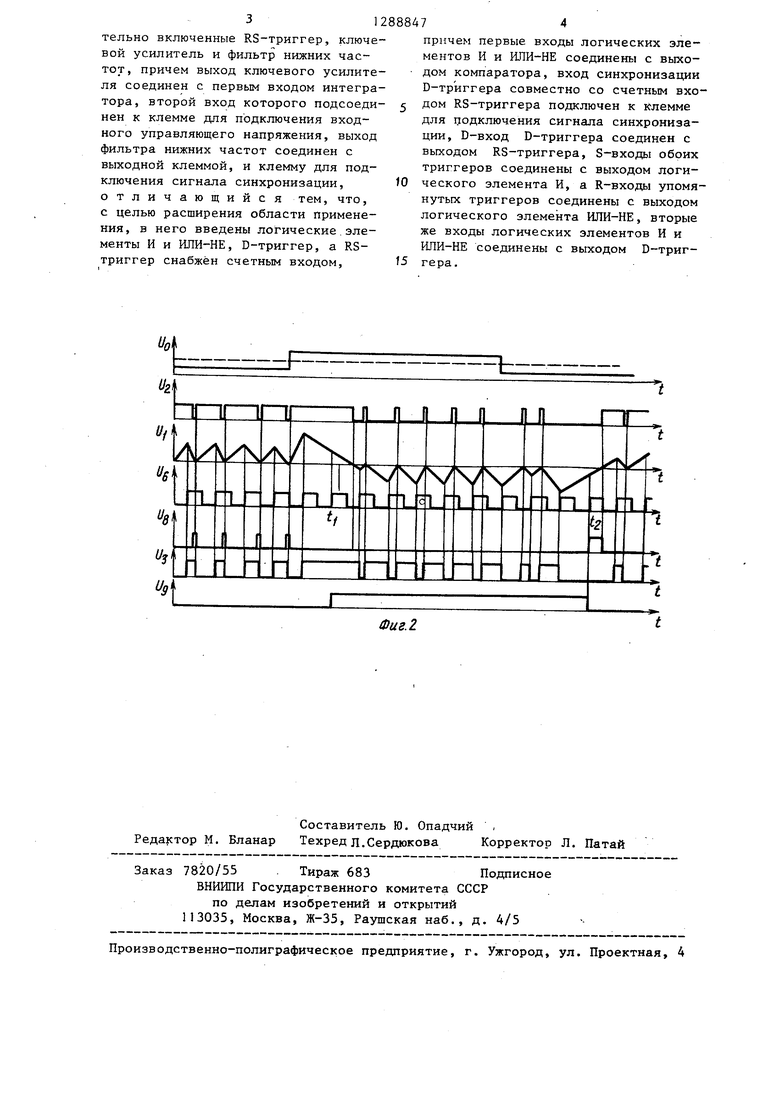

На фиг. 1 приведена структурная схема регулятора напряжения; на фиг. 2 - временные диаграммы, поясняющие работу регулятора напряжения.

Регулятор содержит последовательно соединенные интегратор 1 и компаратор 2, а также последовательно включенные RS-триггер 3, ключевой усилитель 4 и фильтр 5 нижних частот, клемму 6 для подключения сигнала синхронизации, логические эле- менты И 7 и ИЛИ-НЕ 8, выходы которых соединены соответственно с S- и R-входами RS-триггера 3 и D-триг- гера 9, выход которого соединен с входами логических элементов И 7 И ИЛИ-НЕ 8, другие входы которых соединены с выходом компаратора 2, причем счетный вход RS-триггера З и вход синхронизации D-триггера 9 соединены с клеммой 6 для подключения сигнала синхронизации, а выход ключевого усилителя 4 соединен с первым входом интегратора -1, второй вход которого подсоединен к клемме 10 для подключения входного управляющего напряжения.

Предлагаемое устройство работает следующим образом.

В рабочем режиме устройство обес- печивает повторение на выходе в выбранном масштабе напряжения, приложенного к клемме 10 для подключения входного управляющего напряжения. При этом, -если входное управляющее напряжение меньше половинного уровня напряжения питания (фиг. 2, ,), в устройстве осуществляется синхронизация момента включения ключевого усилителя 4. В противном случае, t , в устройстве автоматически устанавливается синхронизация момента окончания импульса ключевого усилителя 4. Ввиду этого обеспечивается устойчивая работа регулятора напря- жения при любых уровнях входных сигналов в режиме внешней синхронизации

При входном сигнале и меньше половинного уровня напряжения питания

5

5

0 5

0 5 0 5

на выходе D-триггера 9 формируется нулевой потенциал U ., позволяющий сигналу и 2 выхода компаратора 2 поступать на вход триггера 3 Си), в результате чего RS-триггер 3 устанавливается в нулевое состояние (U.j) по поступлению каждого импульса U-. В единичное состояние RS-триггер

О

3 переводится сигналом U синхронио

зации, поступающим на его счетный вход.

При увеличении сигнала на клемме 10 вьщ1е половинного уровня напряжения питания напряжение U, на выходе интегратора 1 за время паузы нарастает до большей величины и во время следующего, импульса оно спадает до нулевого уровня за время, превьш1аю- щее период Т сигнала U, синхронизао ,

ции. в результате этого, в момент времени t , прихода следующего синхроимпульса Ug напряжение U на выходе триггера 3 сохраняется равным логической 1 (сигнал на выходе элемента ИЛИ-НЕ отсутствует), что вызывает переключение D-триггера 9 по синхроимпульсу в момент времени t . Ввиду этого напряжение П становится равным логической I и сигнал с выхода компаратора 2, не изменяя полярности, поступает на вход триггера 9, обеспечивая его включение, выключение триггера- происходит по сигналу Ug синхронизации. Таким образом, при больших входных сигналах обеспечивается синхронизация окончания импульса и 2 на входе (выходе) ключевого усилителя 4.

При уменьшении входного сигнала до уровня, меньшего половины напряжения питания, аналогичным образом происходит обратное переключение D-триггера 9 в момент времени t и требуемое изменение режима синхронизации.

Таким образом, в предлагаемом устройстве обеспечивается необходимый режим синхронизации для любых уровней входных сигналов, что позволяет существенно расширить область применения регуляторов напряжения с внешней синхронизацией.

Формула изобретения

Регулятор напряжения, содержащий последовательно соединенные интегратор и компаратор, а также последова31

тельно включенные RS-триггер, ключевой усилитель и фильтр нижних частот, причем выход ключевого усилите ля соединен с первьи входом интегра тора, второй вход которого подсоеди нен к клемме для подключения входного управляющего напряжения, выход фильтра нижних частот соединен с выходной клеммой, и клемму для подключения сигнала синхронизации, отличающийся тем, что, с целью расширения области применения, в него введены логические.элементы И и ИЛИ-НЕ, D-триггер, а RS- триггер снабжён счетным входом.

888474

причем первые входы логических элементов И и ИЛИ-НЕ соединены с выходом компаратора, вход синхронизации D-триггера совместно со счетным вхос дом RS-триггера подключен к Клемме для подключения сигнала синхронизации, D-вход D-триггера соединен с выходом RS-триггера, 8-входы обоих триггеров соединены с выходом логи- fO ческого элемента И, а R-входы упомянутых триггеров соединены с выходом логического элемента ИЛИ-НЕ, вторые же входы логических элементов И и ИЛИ-НЕ соединены с выходом D-триг- f5 гера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный преобразователь постоянного напряжения | 1985 |

|

SU1279027A1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1982 |

|

SU1035593A2 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-дискретный интегратор | 1979 |

|

SU809250A2 |

| Устройство для интегрирования | 1983 |

|

SU1108470A1 |

| Устройство для управления транзисторным полумостовым инвертором | 1989 |

|

SU1676033A1 |

| Регулятор напряжения | 1983 |

|

SU1156033A1 |

| Устройство для стабилизированного питания приемников энергии | 1987 |

|

SU1545290A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

Изобретение относится к вторичным источникам питания радиоаппаратуры. Целью изобретения является расширение области применения импульсного стабилизатора напряжения. При входном сигнале, меньшем половинного уровня напряжения питания, на входе D-триггера 9 формируется нулевой потенциал. Это позволяет сигналу с выхода компаратора 2 поступать на вход триггера 3, который устанавливается в нулевое состояние. В единичное состояние триггер 9 переводится сигналом синхронизации, поступающим на его счетный вход. Логическая 1 с выхода триггера 3 вызывает переключение триггера 9, на выходе которого появляется логическая 1. Сигнал с выхода компаратора 2 поступает на S-вход триггера 9, обеспечивая его включение, выключение же триггера 3 происходит по сигналу синхронизации. При уменьшении входного сигнала происходит обратное переключение триггера 9. 2 ил. (Л

j-Ug

t

JIJLJLJIJ

ww

и

Составитель Ю. Опадчий Редактор М. Бланар Техред л.Сердюкова Корректор Л. Патай

Заказ 7820/55 . Тираж 683Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Стабилизированный преобразователь напряжения | 1982 |

|

SU1050061A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Карпов Р.Г., Карпов Н.Р | |||

| Преобразование и математическая обработка шнротно-импульсных сигналов | |||

| - М | |||

| , 1977, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-02-07—Публикация

1985-05-13—Подача