1128

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля цифровых блоков.

Цель изобретения - повышение достоверности контроля.за счет исключения помех по цепям питания контролируемого и эталонного цифровых блоков и совмещения задания детерминированных и случайных входных воздействий на контролируемьш цифровой блок.

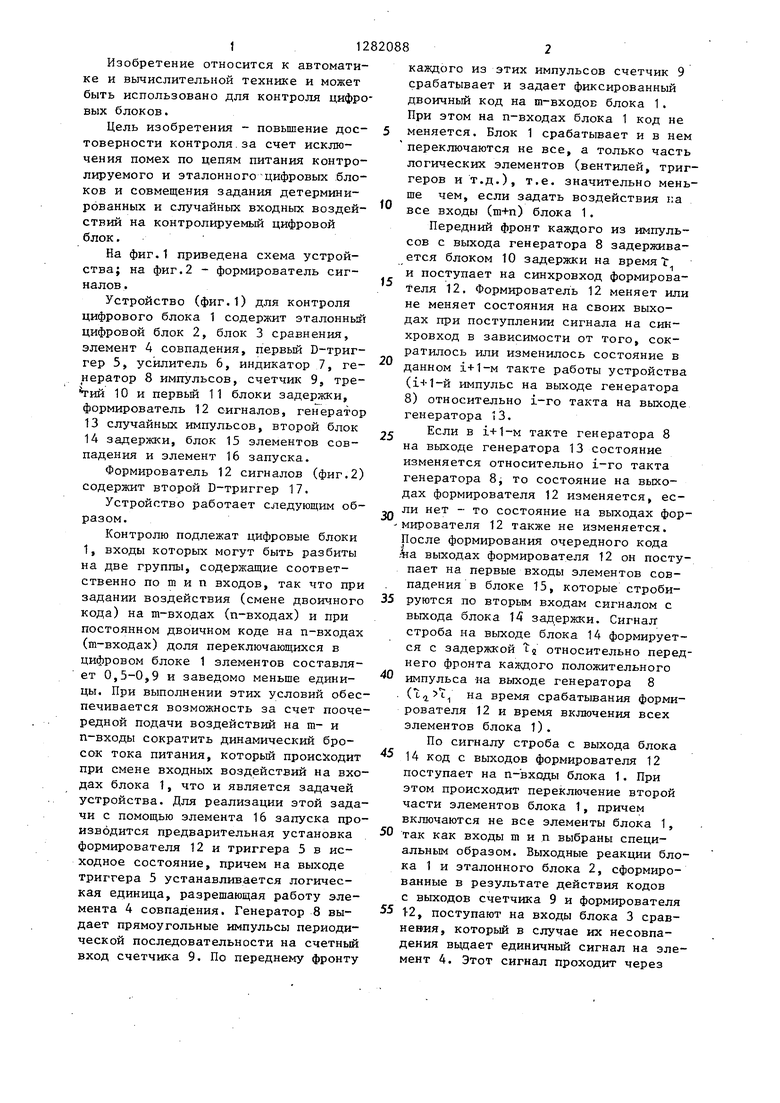

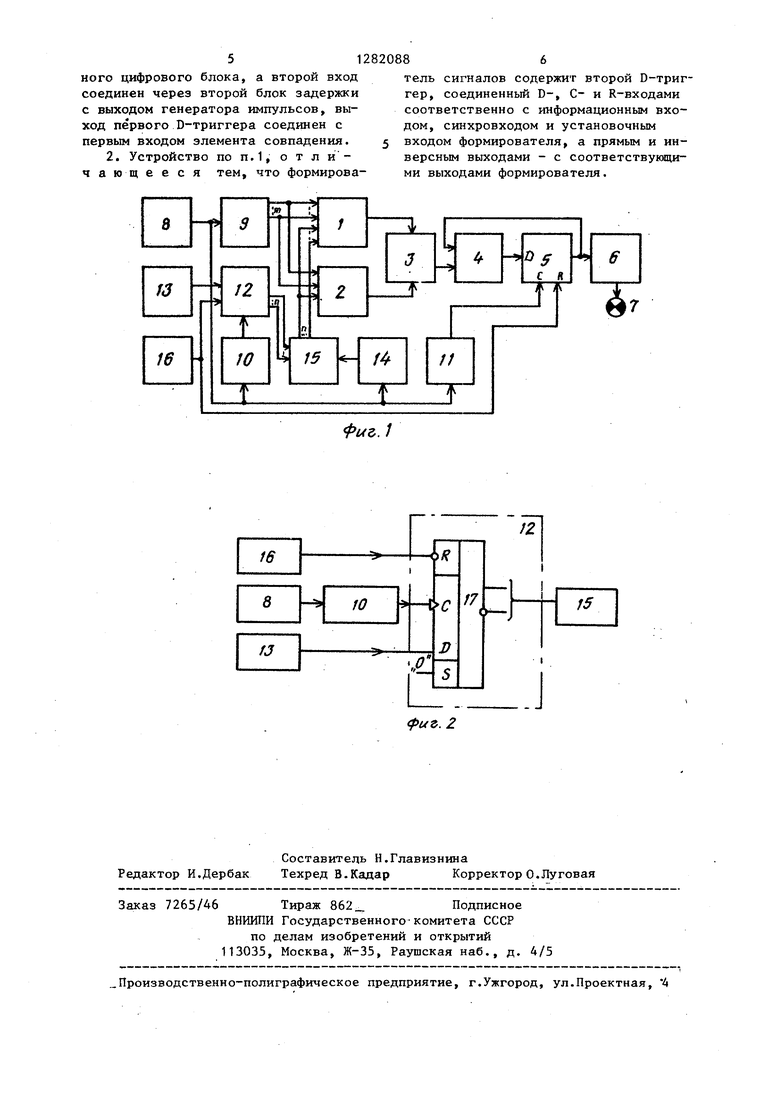

На фиг.1 приведена схема устройства; на фиг.2 - формирователь сигналов .

Устройство (фиг.1) для контроля цифрового блока 1 содержит эталонный цифровой блок 2, блок 3 сравнения, элемент 4 совпадения, первьй D-триг- гер 5, усилитель 6, индикатор 7, генератор 8 импульсов, счетчик 9, третий 10 и первьй 11 блоки задержки, формирователь 12 сигналов, генератор

13случайных импульсов, второй блок

14задержки, блок 15 элементов совпадения и элемент 16 запуска.

Формирователь 12 сигналов (фиг.2) содержит второй D-триггер 17.

Устройство работает следующим образом.

Контролю подлежат цифровые блоки 1, входы которых могут быть разбиты на две группы, содержащие соответственно по m и п входов, так что при задании воздействия (смене двоичного кода) на т-входах (п-входах) и при постоянном двоичном коде на п-входах (т-входах) доля переключающихся в цифровом блоке 1 элементов составляет 0,5-0,9 и заведомо меньше единицы. При выполнении этих условий обеспечивается возможность за счет поочередной подачи воздействий на т- и п-входы сократить динамический бросок тока питания, который проис5содит при смене входных воздействий на входах блока 1, что и является задачей устройства. Для реализации этой задачи с помощью элемента 16 запуска производится предварительная установка формирователя 12 и триггера 5 в исходное состояние, причем на выходе триггера 5 устанавливается логическая единица, разрешающая работу элемента 4 совпадения. Генератор 8 выдает прямоугольные импульсы периодической последовательности на счетный вход счетчика 9. По переднему фронту

5

0

5

каждого из этих импульсов счетчик 9 срабатывает и задает фиксированный двоичный код на т-входов блока 1. При этом на п-входах блока 1 код не меняется. Блок 1 срабатывает и в нем переключаются не все, а только часть логических элементов (вентилей, триггеров и т.д.), т.е. значительно меньше чем, если задать воздействия па все входы (ш+п) блока 1.

Передний фронт каждого из импульсов с выхода генератора 8 задерживается блоком 10 задержки на время Тг и поступает на синхровход формирователя 12. Формирователь 12 меняет или не меняет состояния на своих выходах при поступлении сигнала на синхровход в зависимости от того, сократилось или изменилось состояние в данном i+1-м такте работы устройства (iH-1-й импульс на выходе генератора 8) относительно i-ro такта на выходе генератора 13.

Если в i+1-м такте генератора 8 на выходе генератора 13 состояние изменяется относительно i-ro такта генератора 8, то состояние на выходах формирователя 12 изменяется, если нет - то состояние на выходах формирователя 12 также не изменяется. После формирования очередного кода даа выходах формирователя 12 он поступает на первые входы элементов совпадения в блоке 15, которые строби- руются по вторым входам сигналом с выхода блока 14 задержки. Сигнал строба на выходе блока 14 формируется с задержкой tj относительно переднего фронта каждого положительного импульса -на выходе генератора 8 . ( на время срабатывания формирователя 12 и время включения всех элементов блока 1).

По сигналу строба с выхода блока 14 код с выходов формирователя 12 поступает на п-входы блока 1. При этом происходит переключение второй части элементов блока 1, причем включаются не все элементы блока 1, так как входы шип выбраны специальным образом. Выходные реакции блока 1 и эталонного блока 2, сформированные в результате действия кодов с выходов счетчика 9 и формирователя 55 1-2, поступают на входы блока 3 сравнения, который в случае их несовпадения выдает единичный сигнал на элемент 4. Этот сигнал проходит через

0

35

40

45

50

31282088

элемент 4 (так как триггер 5 находится в единичном состоянии) и поступает на D-вход триггера 5. Через время 1 относительно переднего фронта каждого положительного импульса генера-

Dмура

5 бл ге со ум

тора 8 (т i ,2

t ) на С-вход триггера 5 с выхода блока 11 задержки поступает другой синхросигнал, что приводит в случае отказа блока 1 (единица на D-входе триггера) к переключению триггера 5 в состояние с нулем на выходе и запиранию элемента 4. При этом через усилитель 6 включается индикатор 7, индицирующий факт негодности блока 1. Задержку синхросигнала блоком 11 вводят для того, чтобы запись результата контроля в триггере 5 производилась после окончания переходных процессов в блоках 1 и 2 и элементах устройства.

Генератор 13 формирует непериодическую последовательность импульсов, распределенных во времени случайным образом. Вследствие этого изменение или сохранение кода на выходах формирователя 12 также случайно, а при нескольких полных циклах работы счетчика 9 появление одинаковых сочетаний кодов с текстовых наборов на (m+n)-входов блоков 1 и 2 в первом, втором, третьем и т.д. циклах работы счетчика 9 маловероятно. Это обеспечивает сочетание проверки блока 1 на детерминированных кодах счетчика 9 со случайными кодами на выходах формирователя 12.

За счет того, что входные воздействия на блоки 1 и.2 задаются по очереди по группам из т- и п входов, а не сразу на (ir.+n)-входов, обеспечивается уменьшение количества одновременно сработавших элементов блоков 1 и 2, уменьшение броска тока по цепям их питания, соответствующее

уменьшение амплитуды помех и сокраще-45 блок задержки, формирователь сигнание числа и уменьшение вероятности ложных срабатываний блоков 1 и 2.

Формирователь 12 сигналов (фиг.2) может быть выполнен, например, на D-триггере 17 (в случае п 2). При

этом сигнал с выхода блока 10 задержки поступает на С-вход D-триггера 17 и записывает в него случайный уровень, имеющийся на D-входе. Причем, если уровень на D-входе триггера 17 не изменяется в такте его опроса относительно i-ro такта, то и уровни на его выходах не меняются, в противном случае - меняются.

При необходимости (п 2) выход Dтриггера 17 подключается к счетному входу сметчика, выходы которого работают на выходы формирователя 12.

5 Таким образом, за счет введения блока 10 задержки, формирователя 12, генератора 13 и блока 15 элементов совпадения устройство обеспечивает уменьшение броска тока в цепях пиO тания блоков 1 и 2 в момент подачи входного токового воздействия, а также совмещение задания детерминированных и случайных кодов на входы блоков 1 и 2, что повышает достоверность

5 контроля.

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее генератор импульсов, соединенньй вьгходом через первьш блок задержки с С-входом первого D-триггера, а непосредственно - со счетным входом счетчика, выходы которого являются первыми выходами устройства и соединены с первыми входами эталонного цифрового блока, выходы которого соединены с первыми входами блока сравнения, вторые входы которого являются первыми входами устройства, а выход соединен с первым входом элемента совпадения, соединенного выходом с D-входом первого D-триггера, выход которою сое5 динен через усилитель с входом индикатора, а также второй блок задержки и элемент запуска, отличаю- щ е е с я тем, что, с целью повышения достоверности контроля за счет

0 исключения помех по цепям питания

контролируемого и эталонного цифровых блоков и совмещения задания детерминированных и случайных входных воздействий, в устройство введены третий

0

5

0

лов, генератор случайных имцульсов и блок элементов совпадения, причем выход генератора импульсов соединен через третий блок задержки с синхровхо- дом формирователя сигналов, устаноЭочньш вход которого соединен с выходом элемента запуска и с R-входом первого D-триггера, информационный вход - с выходом генератора случайных импульсов, а выходы - с первыми входами блока элементов совпадения, выходы которого являются вторыми выходами устройства и соединены с соответствующими вторыми входами эталонного цифрового блока, а второй вход соединен через второй блок задержки с выходом генератора импульсов, выход первого D-триггера соединен с первым входом элемента совпадения. 2. Устройство по П.1, о т л и - чающееся тем, что формироваФи. 1

тель сигналов содержит второй D-триг- гер, соединенный D-, С- и R-входами соответственно с информационным входом, синхровходом и установочным входом формирователя, а прямым и инверсным выходами - с соответствукщи- ми выходами формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения операторов | 1985 |

|

SU1320831A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2475831C1 |

| Тренажер оператора автоматизированной системы управления | 1983 |

|

SU1092554A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| Устройство для автоматического измерения динамических характеристик быстродействующих аналого-цифровых преобразователей | 1980 |

|

SU892705A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2477887C1 |

| СПОСОБ И УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1994 |

|

RU2098862C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля цифровых блоков. Цель изобретения - повышение достоверности контроля за счет исключения помех по цепям питания контролируемого и эталонного цифровых блоков и совмещения задания детерминированных и случайных входных воздействий на контролируемый цифровой блок. Устройство содержит эталонный цифровой блок, блок сравнения, элемент совпадения, D-триг- гер, усилитель, индикатор, генератор импульсов, счетчик, три блока задержки, формирователь сигналов, генератор случайных импульсов, блок элементов совпадения и элемент запуска. За счет введения третьего блока задержки, формирователя сигналов, генератора случайных импульсов и блока элементов совпадения устройство обеспечивает уменьшение броска тока в цепях питания контролируемого и эталонного блоков в момент подачи входного тестового воздействия, а также совмещение задания детерминированных и случайных входных кодов. 1 з.п. ф-лы, 2 нл. с (Л to 00 to о 00 00

/2

Редактор И.Дербак

Составитель Н.Главизнина

Техред В.Кадар Корректор О.Луговая

Заказ 7265/46 Тираж 862 Подписное ВНИИПИ Государственного-комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

„Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

. 2

| Устройство для обнаружения неисправностей в логических схемах | 1971 |

|

SU441532A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения и диагностики неисправностей логических блоков | 1976 |

|

SU615492A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-01-07—Публикация

1984-12-06—Подача