ми информационным и: входами блока регистрации.

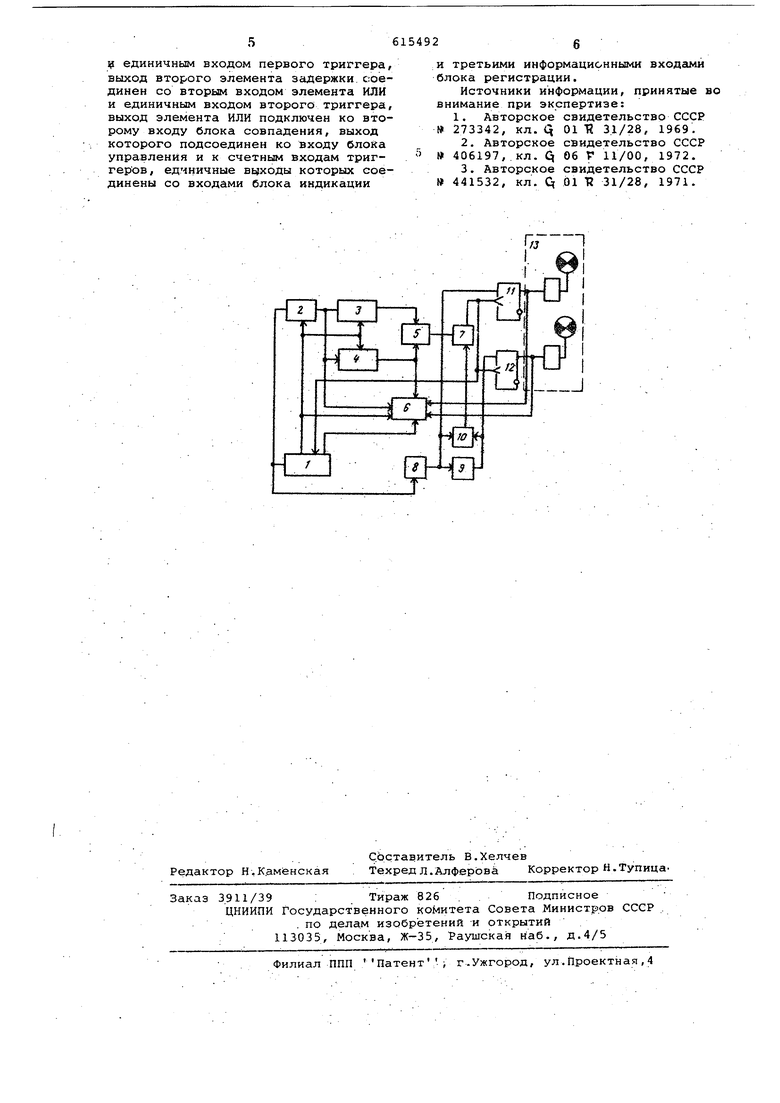

На чертеже показана блок-схема устройства для одного выхода контро(Лируемого блока.

Устройство содержит блок управления- 1, счетчик 2, эталонный блок 3, контролируемый логический блок 4, блок сравнения 5, блок регистрации блок совпадения 7, первый 8 и второй 9 элементы задержки, элемент ИЛИ 10, первый 11 и второй 12 триггеры- и блок индикации 13.

Устройство работает следующим образом.

Синхронный блок управления 1 выдает сигнал установки нуля на счетчик 2, эталонный блок 3, блок 4 и блок регистрации 6. Следующий тактовый сигнал установки контрольных наборов с блока 1 переводит счетчик в положение, определяккцее контрольный набор на информационных входах эталонного блока 3 и контролируемого блока 4. Этот же сигнал поступает . На первый элемент задержки 8. Выход каждого разряда счетчика 2 соединен с одноименными входами эталонного и контролируемого блоков и блока регистрации 6. Выходы контролируемого и эталонного блоков подключены к соответствующим входам блока сравнения 5, кроме того выходы контролируемого блока подключены ко входам блока регистрации 6. Сигналы неисправности, которые появляются на выходах блока сравнения 5, в зависимости от момента опроса, могут свидетельствовать о неисправности как по быстродействию, так и по функционированию, д

. Сигнал опроса с первого элемента задержки 8, настроенного на проверку контролируемого блока по быстродействию, поступает на вход триггера 11 неисправности по быстродействию и через элемент ИЛИ 10 на первые входы элементов 7, Если на выходе блока 4 присутствует сигнал неисправности, то на соответствующем выходе блока сравнения 5 появится сигнал рассогласования, который приведет триггер 11 в состояние , и в блоке индикации 13, состоящем из усилителей мощности и ламп индикации, загорится соответствующая лампа. Сигналопроса свыхода задержки 8 поступает на вход второго элемента задержки 9, настроенный на проверку контролируемого, блока по функционированию. Второй сигнал опро поступает на вход триггера 12 неисправности по функционированию и чере элемент ИЛИ 10 на вход блока совпадения 7. Если на каком-то из выходов блока 4 имеется неисправность по их функционированию, то импульс с выхода 7 переведет триггер 12 в состояние . ив блоке 13 загорится соответствующая лампа.

Таким образом, если сработал только триггер 11, то имеется неисправность по быстродействию по данному выходу, если сработал триггер 12, то имеется неисправность по функционированию, если сработали оба триггера, то имеется неисправность и по быстродействию и по функционированию, если триггеры не сработали, то объект контроля по реакции на данный тест исправен.

Сигналы о неисправности поступают на входы блока управления 1, свидетельствуя о необходимости регистрации данного цикла проверки, а сигналы конкретной неисправности с единичных выходов триггеров поступают в блок регистрации, который по тактовым сигналам с блока 1 осуществляет регистрацию контрольного теста, состояний выходов контролируемого блока и выходов, на которых обнаружены неисправности по быстродействию и по функционированию.

Устройство позволяет совместить контроль логических блоков по быстродействию и на функционирование, что позволяет более полно диагностировать неисправности.

Формула изобретения

. Устройство для контроля и диагностики неисправностей логических блоков, со/1ержащее блок индикации, счетчик , выходы которого соединены с первыми информационными входами блока регистрации, эталонным блоком и контро.пируемым логическим блоком, выходы которого соединены со вторыми информационными входами блока регистрации и с первыми входами блока сравнения, вторые входы которого подключены к выходам эталонного блока, а выходы - к первому входу блока совпадения, блок управления, выход установки нуля которого соеди.нен с входами сброса счетчика, блока регистрации, эталонного и контролируемого логического блоков, выход установки тактового набора - со счетным входом счетчика, а выход тактовых сигналов записи блока управления подключен к управляющему входу блока регистрации, отличающее с я тем, что, с целью повышения достоверности контроля и диагностирования, в устройство введены элементы задержки, элемент ИЛИ и триггеры, выход установки тактового набора блока управления через первый элемент задержки соединён со входом второго.элемента задержки, первым входом элемента ИЛИ. единичным входом первого триггера, выход второго элемента задержки.соединен со вторым входом элемента ИЛИ и единичным входом второго триггера, выход элемента ИЛИ подключен ко второму входу блока совпадения, выход которого подсоединен ко входу блока управления и к счетным входам триггеров, единичные выходы которых соединены со входами блока индикации 615492 и бл вн третьими информационными входами ока регистрации. Источники информации, принятые во имание при экспертизе: 1. Авторское свидетельство СССР 273342, кл. q 01 Т 3.1/28, 1969. 2,Авторское свидетельство СССР 406197, кл. Q 06 Г 11/00, 1972. 3.Авторское свидетельство СССР 441532, кл. Q 01 К 31/28, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических блоков | 1986 |

|

SU1312534A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для диагностирования логических схем | 1988 |

|

SU1684757A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля времени установления цифроаналогового преобразователя | 1990 |

|

SU1786660A1 |

| Устройство для контроля логических схем | 1976 |

|

SU728134A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1483456A1 |

Гп

Авторы

Даты

1978-07-15—Публикация

1976-08-23—Подача