со

00

со со

О) 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Генератор тестов | 1986 |

|

SU1424020A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре контроля цифровых объектов. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор 1, счетчики 2 и 14, генератор 4 псевдослучайной последовательности (ПСП), формирователь 5 сигнатур, компаратор 7, логические элементы И-НЕ 9, И 10, 11, 12 и 13,ИЛИ 16, блок 15 памяти, регистры 17 и 19, коммутатор 18, вход 26 задания режима. В первом режиме генератор 4 передает через коммутатор 18 и регист- 19 ЦСЦ тестовых воздействий с заданным законом распределения на исправный контролируемый блок 6, реакции которого обрабатываются формирователем 5. Количество воздействий задается счетчиком 2. Во втором режиме генератор 4, регистр 17 и счетчик 14 передают содержимое ячеек блока 15 через коммутатор 18 и регистр 19 на входы блока 6 взамен тестовых воздействий. Передаваемая последовательность искажена так, что обеспечивает установку исправного блока 6 в состояние, соответствующее заданному списку его неисправностей. На выходе компаратора 7 можно наблюдать значения сигнатур и результаты их сравнения. Работа данного устройства как в режиме прямой генерации тестов, так и в режиме искаженной генерации, т. е. искусственного искажения входных сигналов, позволяет повысить достоверность контроля цифровых объектов. 4 ил. сл

Фиг.

Готов

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре контроля дискретных объектов.

Цель изобретения - повышение достоверности контроля.

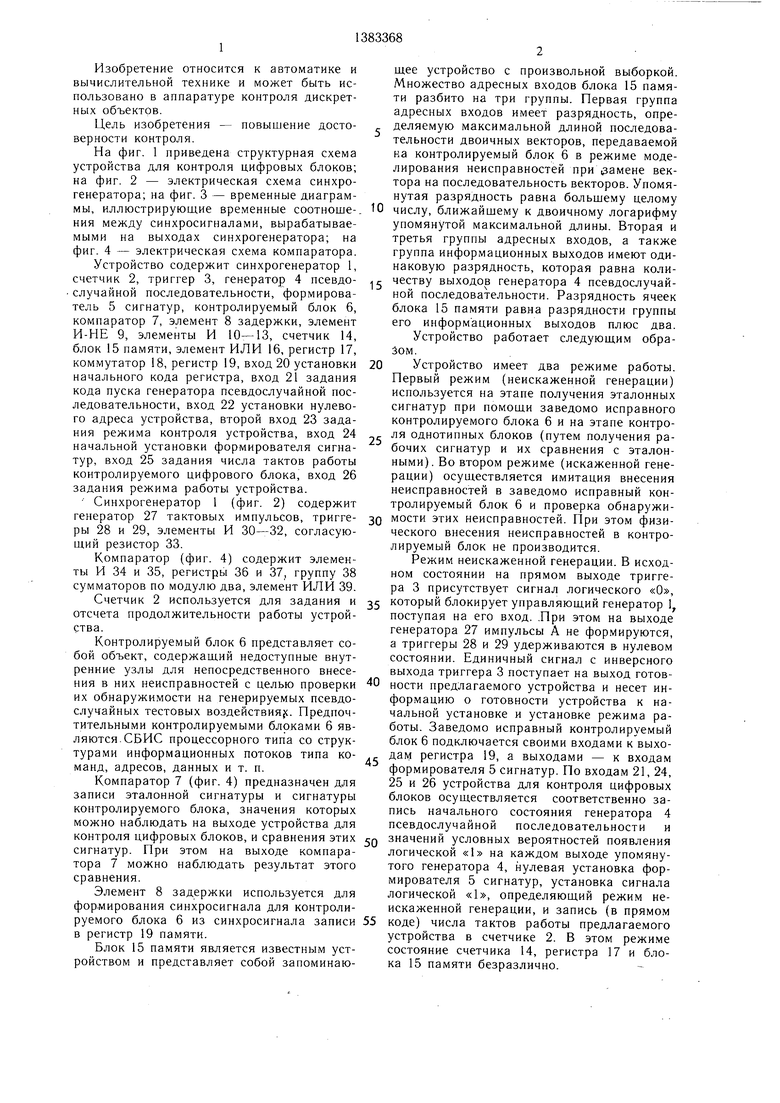

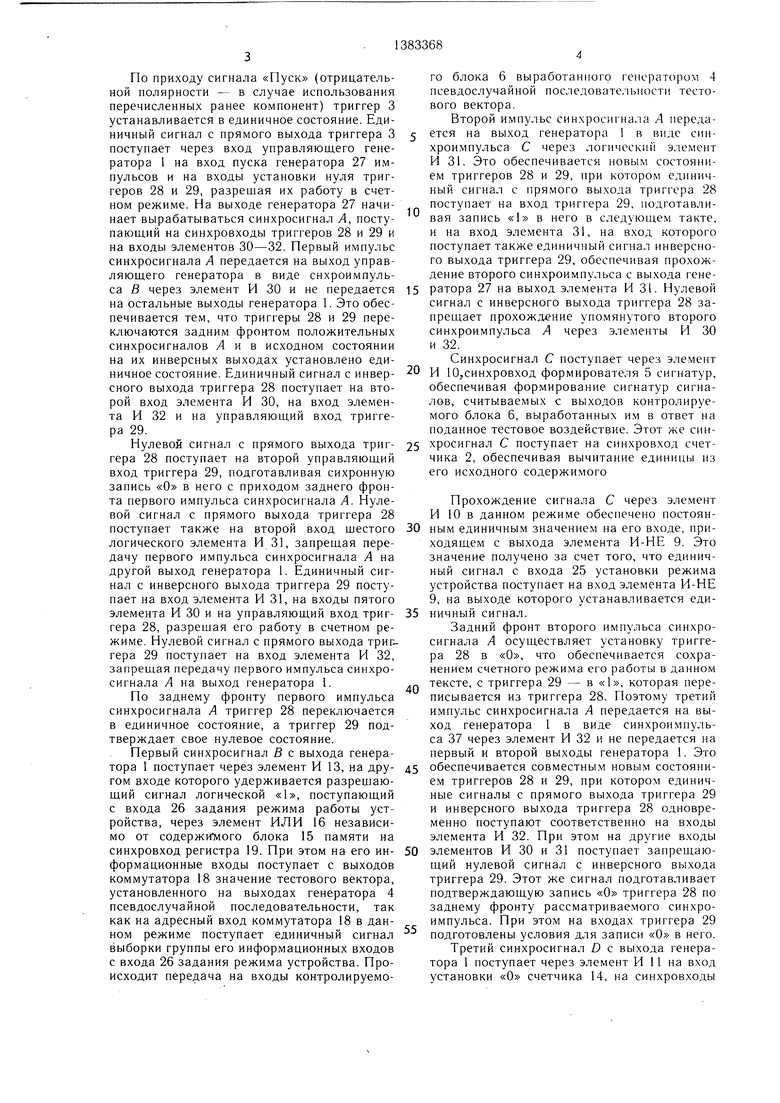

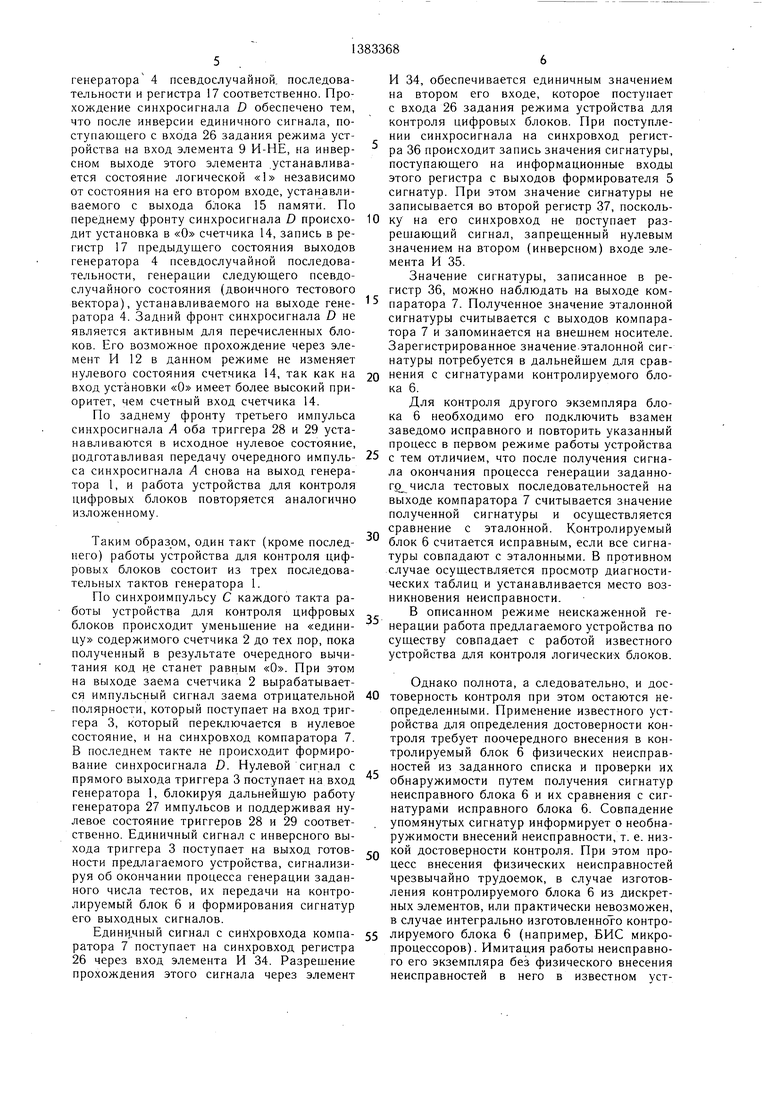

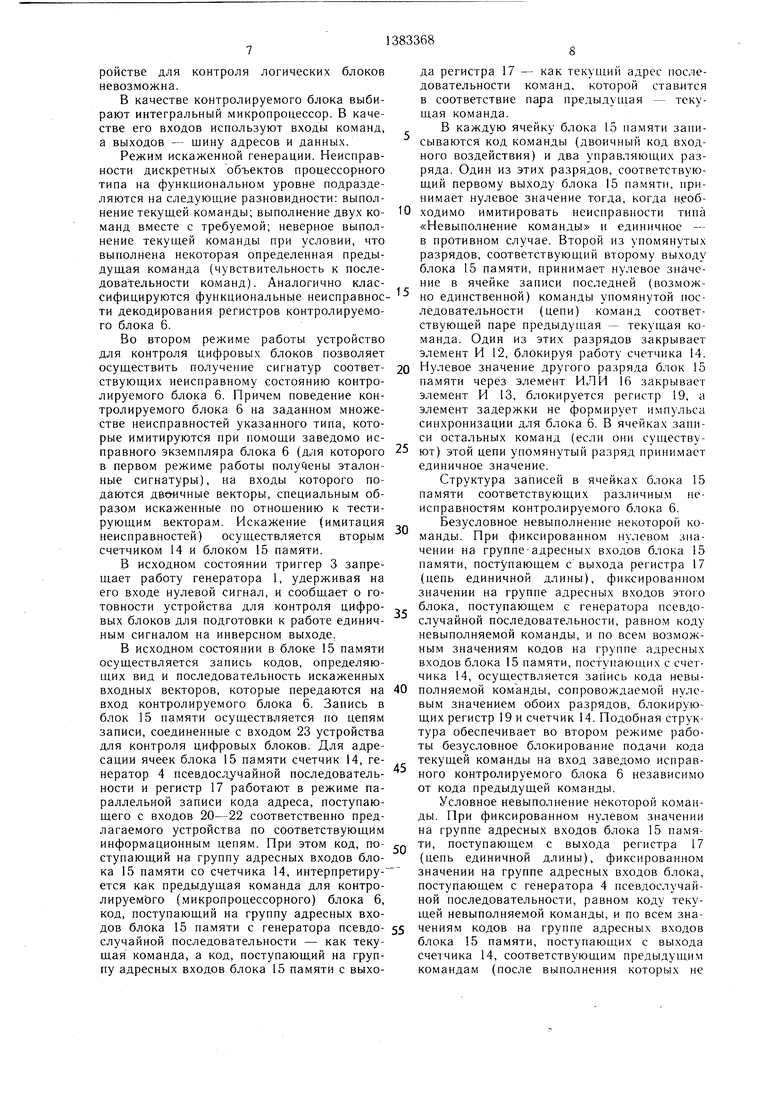

На фиг. 1 приведена структурная схема устройства для контроля цифровых блоков; на фиг. 2 - электрическая схема синхро- генератора; на фиг. 3 - временные диаграммы, иллюстрирующие временные соотноше-. ния между синхросигналами, вырабатываемыми на выходах синхрогенератора; на фиг. 4 - электрическая схема компаратора. Устройство содержит синхрогенератор 1, счетчик 2, триггер 3, генератор 4 псевдо- случайной последовательности, формирователь 5 сигнатур, контролируемый блок 6, компаратор 7, элемент 8 задержки, элемент И-НЕ 9, элементы И 10-13, счетчик 14, блок 15 памяти, элемент ИЛИ 16, регистр 17, коммутатор 18, регистр 19, вход 20 установки начального кода регистра, вход 21 задания кода пуска генератора псевдослучайной последовательности, вход 22 установки нулевого адреса устройства, второй вход 23 задания режима контроля устройства, вход 24 начальной установки формирователя сигнатур, вход 25 задания числа тактов работы контролируемого цифрового блока, вход 26 задания режима работы устройства.

Синхрогенератор 1 (фиг. 2) содержит генератор 27 тактовых импульсов, триггеры 28 и 29, элементы И 30-32, согласующий резистор 33.

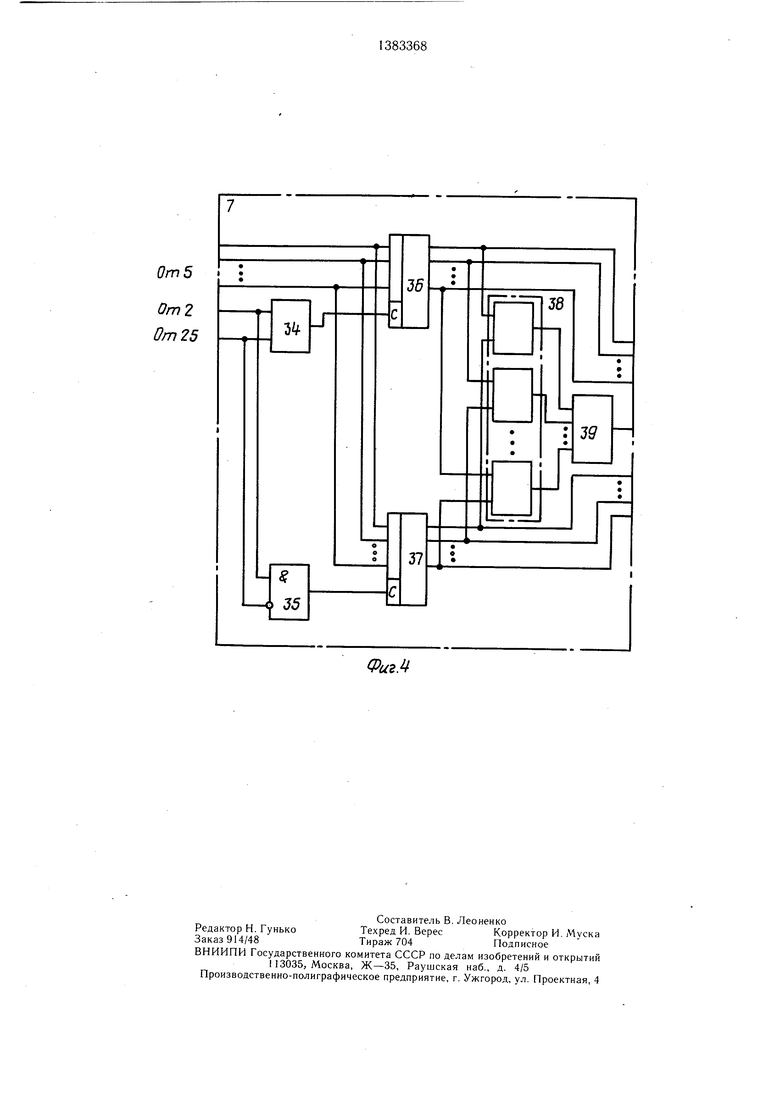

Компаратор (фиг. 4) содержит элементы И 34 и 35, регистры 36 и 37, группу 38 сумматоров по модулю два, элемент ИЛИ 39. Счетчик 2 используется для задания и отсчета продолжительности работы устройства.

Контролируемый блок 6 представляет собой объект, содержащий недоступные внутренние узлы для непосредственного внесения в них неисправностей с целью проверки их обнаружимости на генерируемых псевдослучайных тестовых воздействия с. Предпочтительными контролируемыми блоками 6 являются.СБИС процессорного типа со структурами информационных потоков типа команд, адресов, данных и т. п.

Компаратор 7 (фиг. 4) предназначен для записи эталонной сигнатуры и сигнатуры контролируемого блока, значения которых можно наблюдать на выходе устройства для контроля цифровых блоков, и сравнения этих сигнатур. При этом на выходе компаратора 7 можно наблюдать результат этого сравнения.

Элемент 8 задержки используется для формирования синхросигнала для контролируемого блока 6 из синхросигнала записи в регистр 19 памяти.

Блок 15 памяти является известным устройством и представляет собой запоминающее устройство с произвольной выборкой. Множество адресных входов блока 15 памяти разбито на три группы. Первая группа адресных входов имеет разрядность, определяемую максимальной длиной последовательности двоичных векторов, передаваемой на контролируемый блок 6 в режиме моделирования неисправностей приЛзамене вектора на последовательность векторов. Упомянутая разрядность равна больщему целому

0 числу, ближайщему к двоичному логарифму упомянутой максимальной длины. Вторая и третья группы адресных входов, а также группа информационных выходов имеют одинаковую разрядность, которая равна колиг честву выходов генератора 4 псевдослучайной последовательности. Разрядность ячеек блока 15 памяти равна разрядности группы его информационных выходов плюс два. Устройство работает следующим образом.

0 Устройство имеет два режиме работы. Первый режим (неискаженной генерации) используется на этапе получения эталонных сигнатур при помощи заведомо исправного контролируемого блока 6 и на этапе контро ля однотипных блоков (путем получения рабочих сигнатур и их сравнения с эталонными). Во втором режиме (искаженной генерации) осуществляется имитация внесения неисправностей в заведомо исправный контролируемый блок 6 и проверка обнаружи0 мости этих неисправностей. При этом физического внесения неисправностей в контролируемый блок не производится.

Режим неискаженной генерации. В исходном состоянии на прямом выходе триггера 3 присутствует сигнал логического «О,

5 который блокирует управляющий генератор 1, поступая на его вход. .При этом на выходе генератора 27 импульсы А не формируются, а триггеры 28 и 29 удерживаются в нулевом состоянии. Единичный сигнал с инверсного выхода триггера 3 поступает на выход готов0

ности предлагаемого устройства и несет информацию о готовности устройства к начальной установке и установке режима работы. Заведомо исправный контролируемый блок 6 подключается своими входами к выхо- с дам регистра 19, а выходами - к входам формирователя 5 сигнатур. По входам 21, 24, 25 и 26 устройства для контроля цифровых блоков осуществляется соответственно запись начального состояния генератора 4 псевдослучайной последовательности и

0 значений условных вероятностей появления логической «1 на каждом выходе упомянутого генератора 4, нулевая установка формирователя 5 сигнатур, установка сигнала логической «1, определяющий режим неискаженной генерации, и запись (в прямом

5 коде) числа тактов работы предлагаемого устройства в счетчике 2. В этом режиме состояние счетчика 14, регистра 17 и блока 15 памяти безразлично.

По приходу сигнала «Пуск (отрицательной полярности - в случае использования перечисленных ранее компонент) триггер 3 устанавливается в единичное состояние. Единичный сигнал с прямого выхода триггера 3 поступает через вход управляющего генератора 1 на вход пуска генератора 27 импульсов и на входы установки нуля триггеров 28 и 29, разрешая их работу в счетном режиме. На выходе генератора 27 начинает вырабатываться синхросигнал А, поступающий на синхровходы триггеров 28 и 29 и на входы элементов 30-32. Первый импульс синхросигнала А передается на выход управляющего генератора в виде снхроимпуль- са В через элемент И 30 и не передается на остальные выходы генератора 1. Это обеспечивается тем, что триггеры 28 и 29 переключаются задним фронтом положительных синхросигналов Лив исходном состоянии на их инверсных выходах установлено единичное состояние. Единичный сигнал с инверсного выхода триггера 28 поступает на второй вход элемента И 30, на вход элемента И 32 и на управляющий вход триггера 29.

Нулевой сигнал с прямого выхода триггера 28 поступает на второй управляющий вход триггера 29, подготавливая сихронную запись «О в него с приходом заднего фронта первого импульса синхросигнала А. Нулевой сигнал с прямого выхода триггера 28 поступает также на второй вход щестого логического элемента И 31, запрещая передачу первого импульса синхросигнала А на другой выход генератора 1. Единичный сигнал с инверсного выхода триггера 29 поступает на вход элемента И 31, на входы пятого элемента И 30 и на управляющий вход триггера 28, разрещая его работу в счетном режиме. Нулевой сигнал с прямого выхода триггера 29 поступает на вход элемента И 32, запрещая передачу первого импульса синхросигнала А на выход генератора 1.

По заднему фронту первого импульса синхросигнала А триггер 28 переключается в единичное состояние, а триггер 29 подтверждает свое нулевое состояние.

Первый синхросигнал В с выхода генератора 1 поступает через элемент И 13, на другом входе которого удерживается разрещаю- щий сигнал логической «1, поступающий с входа 26 задания режима работы устройства, через элемент ИЛИ 16 независимо от содержитиого блока 15 памяти на синхровход регистра 19. При этом на его информационные входы поступает с выходов коммутатора 18 значение тестового вектора, установленного на выходах генератора 4 псевдослучайной последовательности, так как на адресный вход коммутатора 18 в данном режиме поступает единичный сигнал выборки группы его информационных входов с входа 26 задания режима устройства. Происходит передача на входы контролируемого блока 6 выработанного генератором 4 псевдослучайной последовательности тестового вектора.

Второй импульс синхросигнала А переда- ется на выход генератора 1 в виде синхроимпульса С через логический элемент И 31. Это обеспечивается новым состоянием триггеров 28 и 29, при котором единичный сигнал с прямого выхода триггера 28 поступает на вход триггера 29, подготавли

вая запись «1 в него в следующем такте.

и на вход элемента 31, на вход которого поступает также единичный сигнал инверсного выхода триггера 29, обеспечивая прохождение второго синхроимпульса с выхода гене5 ратора 27 на выход элемента И 31. Нулевой сигнал с инверсного выхода триггера 28 запрещает прохождение упомянутого второго синхроимпульса А через элементы И 30 и 32.

Синхросигнал С поступает через элемент

0 И 10,синхровход формирователя 5 сигнатур, обеспечивая формирование сигнатур сигналов, считываемых с выходов контролируемого блока 6, выработанных им в ответ на поданное тестовое воздействие. Этот же син5 хросигнал С поступает на синхровход счетчика 2, обеспечивая вычитание единицы из его исходного содержимого

Прохождение сигнала С через элемент И 10 в данном режиме обеспечено постоян0 ным единичным значением на его входе, приходящем с выхода элемента И-НЕ 9. Это значение получено за счет того, что единичный сигнал с входа 25 установки режима устройства поступает на вход элемента И-НЕ 9, на выходе которого устанавливается еди5 ничный сигнал.

Задний фронт второго импульса синхросигнала А осуществляет установку триггера 28 в «О, что обеспечивается сохранением счетного режима его работы в данном

„ тексте, с триггера 29 - в «1, которая переписывается из триггера 28. Поэтому третий импульс синхросигнала А передается на выход генератора 1 в виде синхроимпульса 37 через элемент И 32 и не передается на первый и второй выходы генератора 1. Это

5 обеспечивается совместным новы.м состоянием триггеров 28 и 29, при котором единичные сигналы с прямого выхода триггера 29 и инверсного выхода триггера 28 одновременно поступают соответственно на входы элемента И 32. При этом на другие входы

0 элементов И 30 и 31 поступает запрещающий нулевой сигнал с инверсного выхода триггера 29. Этот же сигнал подготавливает подтверждающую запись «О триггера 28 по заднему фронту рассматриваемого синхроимпульса. При этом на входах триггера 29 подготовлены условия для записи «О в него. Третий синхросигнал D с выхода генератора 1 поступает через элемент И 11 на вход установки «О счетчика 14, на синхровходы

генератора 4 псевдослучайной, последовательности и регистра 17 соответственно. Прохождение синхросигнала D обеспечено тем, что после инверсии единичного сигнала, поступающего с входа 26 задания режима устройства на вход элемента 9 И-НЕ, на инверсном выходе этого элемента .устанавливается состояние логической «1 независимо от состояния на его втором входе, устан вли- ваемого с выхода блока 15 памяти. По переднему фронту синхросигнала D происходит установка в «О счетчика 14, запись в регистр 17 предыдущего состояния выходов генератора 4 псевдослучайной последовательности, генерации следующего псевдослучайного состояния (двоичного тестового вектора), устанавливаемого на выходе генератора 4. Задний фронт синхросигнала D не является активным для перечисленных блоков. Его возможное прохождение через элемент И 12 в данном режиме не изменяет нулевого состояния счетчика 14, так как на вход установки «О имеет более высокий приоритет, чем счетный вход счетчика 14.

По заднему фронту третьего импульса синхросигнала А оба триггера 28 и 29 устанавливаются в исходное нулевое состояние, подготавливая передачу очередного импульса синхросигнала А снова на выход генератора 1, и работа устройства для контроля цифровых блоков повторяется аналогично изложенному.

Таким образом, один такт (кроме последнего) работы устройства для контроля цифровых блоков состоит из трех последовательных тактов генератора 1.

По синхроимпульсу С каждого такта работы устройства для контроля цифровых блоков происходит уменьшение на «единицу содержимого счетчика 2 до тех пор, пока полученный в результате очередного вычитания код н,е станет равным «О. При этом на выходе заема счетчика 2 вырабатывается импульсный сигнал заема отрицательной полярности, который поступает на вход триггера 3, который переключается в нулевое состояние, и на синхровход компаратора 7. В последнем такте не происходит формирование синхросигнала D. Нулевой сигнал с прямого выхода триггера 3 поступает на вход генератора 1, блокируя дальнейшую работу генератора 27 импульсов и поддерживая нулевое состояние триггеров 28 и 29 соответственно. Единичный сигнал с инверсного выхода триггера 3 поступает на выход готовности предлагаемого устройства, сигнализируя об окончании процесса генерации заданного числа тестов, их передачи на контролируемый блок 6 и формирования сигнатур его выходных сигналов.

Единичный сигнал с син хровхода компаратора 7 поступает на синхровход регистра 26 через вход элемента И 34. Разращение прохождения этого сигнала через элемент

0

И 34, обеспечивается единичным значением на втором его входе, которое поступает с входа 26 задания режима устройства для контроля цифровых блоков. При поступлении синхросигнала на синхровход регистра 36 происходит запись значения сигнатуры, поступающего на информационные входы этого регистра с выходов формирователя 5 сигнатур. При этом значение сигнатуры не записывается во второй регистр 37, поскольку на его синхровход не поступает разрешающий сигнал, запрещенный нулевым значением на втором (инверсном) входе элемента И 35.

Значение сигнатуры, записанное в регистр 36, можно наблюдать на выходе ком- паратора 7. Полученное значение эталонной сигнатуры считывается с выходов компаратора 7 и запоминается на внешнем носителе. Зарегистрированное значение эталонной сигнатуры потребуется в дальнейщем для сравнения с сигнатурами контролируемого блока 6.

Для контроля другого экземпляра блока 6 необходимо его подключить взамен заведомо исправного и повторить указанный процесс в первом режиме работы устройства с тем отличием, что после получения сигнала окончания процесса генерации заданного числа тестовых последовательностей на выходе компаратора 7 считывается значение полученной сигнатуры и осуществляется сравнение с эталонной. Контролируемый блок 6 считается исправным, если все сигнатуры совпадают с эталонными. В противном случае осуществляется просмотр диагностических таблиц и устанавливается место возникновения неисправности.

В описанном режиме неискаженной генерации работа предлагаемого устройства по существу совпадает с работой известного устройства для контроля логических блоков.

0

5

0

5

0

5

Однако полнота, а следовательно, и достоверность контроля при этом остаются неопределенными. Применение известного устройства для определения достоверности контроля требует поочередного внесения в контролируемый блок 6 физических неисправностей из заданного списка и проверки их обнаружимости путем получения сигнатур неисправного блока 6 и их сравнения с сигнатурами исправного блока 6. Совпадение упомянутых сигнатур информирует о необна- ружимости внесений неисправности, т. е. низкой достоверности контроля. При этом процесс внесения физических неисправностей чрезвычайно трудоемок, в случае изготовления контролируемого блока 6 из дискретных элементов, или практически невозможен, в случае интегрально изготовленноТо контро- 5 лируемого блока 6 (например, БИС микропроцессоров). Имитац.ия работы неисправного его экземпляра без физического внесения неисправностей в него в известном уст0

ройстве для контроля логических блоков невозможна.

В качестве контролируемого блока выбирают интегральный микропроцессор. В качестве его входов используют входы команд, а выходов - шину адресов и данных.

Режим искаженной генерации. Неисправности дискретных объектов процессорного типа на функциональном уровне подразделяются на следующие разновидности: выполнение текущей команды; выполнение двух команд вместе с требуемой; неверное выполнение текущей команды при условии, что выполнена некоторая определенная предыдущая команда (чувствительность к последовательности команд). Аналогично классифицируются функциональные неисправности декодирования регистров контролируемого блока 6.

Во втором режиме работы устройство для контроля цифровых блоков позволяет осуществить получение сигнатур соответствующих неисправному состоянию контролируемого блока 6. Причем поведение контролируемого блока 6 на заданном множестве неисправностей указанного типа, которые имитируются при помощи заведомо исправного экземпляра блока 6 (для которого в первом режиме работы получены эталонные сигнатуры), на входы которого подаются двсжчные векторы, специальным образом искаженные по отношению к тестирующим векторам. Искажение (имитация неисправностей) осуществляется вторым счетчиком 14 и блоком 15 памяти.

В исходном состоянии триггер 3 запрещает работу генератора 1, удерживая на его входе нулевой сигнал, и сообщает о готовности устройства для контроля цифровых блоков для подготовки к работе единичным сигналом на инверсном выходе.

В исходном состоянии в блоке 15 памяти осуществляется запись кодов, определяющих вид и последовательность искаженных входных векторов, которые передаются на вход контролируемого блока 6. Запись в блок 15 памяти осуществляется по цепям записи, соединенные с входом 23 устройства для контроля цифровых блоков. Для адресации ячеек блока 15 памяти счетчик 14, генератор 4 псевдослучайной последовательности и регистр 17 работают в режиме параллельной записи кода адреса, поступающего с входов 20-22 соответственно предлагаемого устройства по соответствующим информационным цепям. При этом код, поступающий на группу адресных входов блока 15 памяти со счетчика 14, интерпретиру- ется как предыдущая команда для контролируемого (микропроцессорного) блока 6, код, поступающий на группу адресных входов блока 15 памяти с генератора псевдослучайной последовательности - как текущая команда, а код, поступающий на группу адресных входов блока 15 памяти с выхо5

5

да регистра 17 - как текущий адрес последовательности команд, которой ставится в соответствие пара предыдущая - текущая команда.

В каждую ячейку блока 15 памяти записываются код команды (двоичный код входного воздействия) и два управляющих разряда. Один из этих разрядов, соответствующий первому выходу блока 15 памяти, принимает нулевое значение тогда, когда нроб- 10 ходимо имитировать неисправности типа «Невыполнение команды и единичное - в противном случае. Второй из упомянутых разрядов, соответствующий второму выходу блока 15 памяти, принимает нулевое значение в ячейке записи последней (возможно единственной) команды упомянутой последовательности (цепи) команд соответствующей паре предыдущая - текущая команда. Один из этих разрядов закрывает элемент И 12, блокируя работу счетчика 14. 0 Нулевое значение другого разряда блок 15 памяти через элемент ИЛИ 16 закрывает элемент И 13, блокируется регистр 19, а элемент задержки не формирует импульса синхронизации для блока 6. В ячейках записи остальных команд (если они существуют) этой цепи упомянутый разряд принимает единичное значение.

Структура записей в ячейках блока 15 памяти соответствующих различным неисправностям контролируемого блока 6.

Безусловное невыполнение некоторой команды. При фиксированном нулевом значении на группе-адресных входов блока 15 памяти, поступающем с выхода регистра 17 (цепь единичной длины), фиксированном значении на группе адресных входов это1 о блока, поступающем с генератора псевдослучайной последовательности, равном коду невыполняемой команды, и по всем возможным значениям кодов на группе адресных входов блока 15 памяти, поступающих с счетчика 14, осуществляется зап ись кода невыполняемой команды, сопровождаемой нулевым значением обоих разрядов, блокирующих регистр 19 и счетчик 14. Подобная структура обеспечивает во втором режиме работы безусловное блокирование пОлЧачи кода текущей команды на вход заведомо исправного контролируемого блока 6 независимо от кода предыдущей команды.

Условное невыполнение некоторой команды. При фиксированном нулевом значении на группе адресных входов блока 15 памяти, поступающем с выхода регистра 17 (цепь единичной длины), фиксированном значении на группе адресных входов блока, поступающем с генератора 4 псевдослучайной последовательности, равном коду текущей невыполняемой команды, и по всем зна- 5 чениям кодов на группе адресных входов блока 15 памяти, поступающих с выхода счетчика 14, соответствующим предыдущим командам (после выполнения которых не

0

5

0

5

0

должна выполняться текущая команда), записывается код текущей невыполняемой команды, сопровождаемый нулевым значением обоих разрядов, блокирующих регистр 19 и счетчик 14 цепи. По оставшимся зна|Чениям кодов на группе адресных входов блока 15 памяти, поступающих со счетчика 15, записывается код текущей команды, сопровождаемый единичным значением разряда блокировки регистра 19. Подобная структура обеспечивает блокирова- ние подачи кода текущей команды на вход заведомо исправного контролируемого блока 6 только при условии, что ей предшествует одна из команд, вызывающая невыполнение (эффект взаимного влияния). В противном случае текущая команда выполняется.

Безусловное выполнение некоторой команды взамен требуемой текущей. При фиксированном нулевом значении на группе адресных входов блока 15 памяти, поступающем с выхода регистра 17 (цепь единич- ной длины), фиксированном значении на группе адресных входов этого блока, поступающем с выхода генератора 4 псевдослучайной последовательности, равном коду текущей команды, и по всем возможным значением кодов на групне адресных входов блока 15 памяти, поступающих со счетчика 14, записывается код команды, подлежащей выполнению взамен текущей, сопровождаемой единичным значением разряда, поступающего на элемент ИЛИ 16, и нулевым значением разряда, поступающего на элемент И 12. Подобная структура обеспечивает безусловную замену кода текущей команды на другую команду (эффект пере- путывания команд). Для контролируемых блоков 6 непроцессорного типа упомянутая структура имитирует одиночные и краткие константные неисправности на их входах. Условное выполнение некоторой команды взамен требуемой текущей. При фиксированном нулевом значении на группе адресных входов блок а 15 памяти, поступающем с выхода регистра 17 (цепь единичной длины), фиксированном значении на группе адресных входов этого блока, поступающем с генератора 4 псевдослучайной последовательности, равной коду текущей команды, и по всем значениям кодов на группе адресных входов блока 15 памяти, поступающих со счетчика 14, соответствующих предыдущим командам, после выполнения которых происходит выполнение другой команды взамен текущей, записывается код команды, подлежащей выполнению взамен текущей, сопровождаемой единичным значением индикатора выполнения и нулевым значением индикатора цепи. По оставшимся значениям кодов на группе адресных входов блока 15 памяти, поступающих со счетчика 14, запи- сывается код текущей команды, сопровождаемый единичным значением разряда, поступающего на вход элемента ИЛИ 16, и ну

5

0

0 0 5

0

5

5

0

левым значением разряда, поступающим на вход элемента И 12. Подобная структура обеспечивает замену кода текущей команды на другую команду только при условии, что ей предществует одна из команд, вызывающая эффект замены команды (взаимное выполнение команд). В противном случае выполняется текущая команда.

Безу.словное выполнение нескольких команд вместе с текущей либо вместо текущей. При фиксированном значении на группе адресных входов блока 15 памяти, поступающем с выхода генератора 4 псевдослучайной последовательности, равном коду текущей команды, и по всем возможным значениям кодов предыдущей команды на группе адресных входов, поступающих со счетчика 14, записывается последовательность кодов команд (цепь), начиная с нулевого значения на группе адресных входов блока 15 памяти, поступающих с регистра 17, и далее последовательным приращением по единице после каждой записи. Длина цепи не должна превыщать максимального числа, представимого при помощи группы адресных входов блока 15 памяти, поступающего с выхода регистра 17. Коды сопровождаются единичным значением разряда, поступающего на вход элемента ИЛИ 16, за исключением последнего кода цепи, единичным значением разряда, поступающего на элемент И 12. Последний код цепи сопровождается нулевым значением разряда, поступающего на элемент И 12. Упомянутая цепь команд может содержать либо не содержать код текущей команды. Подобная структура обеспечивает независимую от значения кода предыдущей команды замену кода текущей команды на последовательность команд, способную перевести исправный контролируемый блок 6 в такое логическое состояние, которое соответствует сложной функциональной неисправности (т. е. совпадает с состоянием неисправного контролируемого блока 6 при подаче на его вход текущей команды).

Условное выполнение нескольких команд вместо текущей либо вместе с текущей. При фиксированном значении на группе адресных входов блока 15 памяти, поступающем с выхода генератора 4 псевдослучайной последовательности, равном коду текущей команды, и по всем значениям кодов на группе адресных входов блока 15 памяти, поступающих с выхода счетчика 14, соответствующих предыдущим командам, после выполнения которых происходит выполнение нескольких команд вместо либо вместе с текущей, записывается цепь команд, начиная с нулевого значения на группе адресных входов блока 15 памяти, поступающего с выхода регистра 17, и далее последовательным приращением по единице после каждой записи. Разным предыдущим командам могут соответствовать разные цепи. Цепь может содержать код текущей команды. Коды цепи сопровождаются единичным значением разряда, поступающего на вход элемента ИЛИ 16 и, за исключением последнего, единичным значением разряда, поступаю- щего на вход элемента И 12. Последний код цепи метится нулевым значением разряда, поступающего на вход элемента И 12. По оставшимся значениям кодов на группе адресных входов блока 15 памяти, поступаю- щих с выходов счетчика 14, записывается код текущей команды, сопровождаемый единичным значением разряда, поступающего на вход элемента ИЛИ 16, и нулевым знаВ описываемом втором режиме работы предлагаемого устройства тестовые векторы, вырабатываемые генератором 4 псевдослучайной последовательности, на входы контролируемого блока 6 непосредственно не поступают, а используются как составная

чением разряда, поступающего на вход

элемента И 12. Подобная структура обеспе- 5 часть адреса ячеек блока 15 памяти, содерчивает замену кода текущей команды на пос-жимое которых передается через коммуледовательность команд только при условии,татор 18 и второй регистр 19 на входы кончто ей предшествует одна из команд, вызы-тролируемого блока 6.

вающая эффект замены команды цепьюСовместное состояние выходов счетчи(сложное взаимное влияние команд). В про-20 Регистра 17 и генератора 4 псевдотивном случае выполняется текущая ко-случайной последовательности полностью

манда.определяет адрес считываемой ячейки блоНормальное выполнение текущей коман-ка 15 памяти, на выходах которого, в завиды. При фиксированном нулевом значениисимости от типа имитируемой неисправности,

на группе адресных входов блока 15 памяти,появляются коды команд, заменяющие тепоступающем с выхода регистра 17, фиксиро-25 кущую, сопровождаемые соответствующими

разрядами блокировки. Возможны следующие ситуации, соответствующие описанным структурам.

ванном значении на группе адресных входов этого блока, поступающем с выхода генератора 4 псевдослучайной последовательности, равном коду текущей команды, и по всем возможным значениям кодов на

разрядами блокировки. Возможны следующие ситуации, соответствующие описанным структурам.

Безусловное либо условное невыполнение текущей команды. Код памяти, считыгруппе адресных входов блока 15 памяти, ваемый с группы информационных выходов

блока 15 памяти, поступает на информационные входы регистра 19 через вторую группу информационных входов коммутатора 18, на адресный вход которого посту„.„„.„......,.. ,..„., ..v,.j.„ ..„ нает нулевой сигцал выборки первой группы

вход элемента И 12. Подобная структура информационных входов с входа 26 задания используется для оставшихся команд, ими- режима предлагаемого устройства. При этом

поступающих с выходов счетчика 14, записывается код текущей команды, сопровождаемый единичным значением разряда, поступающего на вход элемента ИЛИ 16, и нулевым значением разряда, поступающего на

тировать неисправное поведение на которых не требуется. Она обеспечивает безусловное (независимое от предыдущей команды) выполнение текуьцей команды.

Заведомо исправный контролируемый блок 6 остается подключенным к устройству для отладки тестов. После подготовки блока 15 памяти и установки его в режим чтения на входе 25 задания режима предлагаенулевои сигнал первого разряда поступает с первого выхода блока 15 памяти через вход элемента ИЛИ 16 на вход элемен- 40 та И 13. На входе элемента ИЛИ 16 при этом установлен нулевой сигнал, поступающий с входа 26 задания режима устройства для контроля цифровых блоков. Нулевой сигнал с второго разряда поступает с второго выхода блока 15 памяти на вход элемента И 12

мого устройства устанавливается нулевой и на вход элемента И-НЕ 9,на входе которого

сигнал, задающий режим искаженной генерации.

По входу 20 устройства осуществляется запись того же- самого начального состояустанавливается единичное состояние.

В этих условиях первый синхросигнал В, поступая с первого выхода генератора 1 на ния генератора 4 псевдослучайной последо- вход элемента И 13, не передается на его вы- вательности, что и в первом режиме с теми ход и во второй регистр 19 не осуществля- же значениями вероятностей появления логической «1 на каждом выходе генератора 4. Одновременно по входам 20, 24, 22 и 26 осуществляется запись кода некоторой команды

в регистр 17, нулевая установка формиро- 55 ния текущей команды. Второй синхросиг- вателя 5 сигнатур, второго счетчика 14 и за-нал С поступает через вход элемента И 10,

пись того же числа тактов работы устройства в первый счетчик 2, что и в первом реется запись текущей команды, которая не поступает на вход контролируемого блока 6. Последний сохраняет свое состояние неизменным, осуществляя имитацию невыполнена синхровходы формирователей 5 сигнатур, обеспечивая формирование сигнатур выходжиме. Код в регистре 17 имеет смысл команды, предшествующей первой команде.

По приходу сигнала «Пуск триггер 3 переключается в единичное состояние. В каждом такте работы устройства для отладки тестов на первом, втором и третьем выходах генератора 1 последовательно вырабатываются синхросигналы А, В и С соответственно. Работа генератора 1 во втором режиме аналогична работе в первом режиме.

В описываемом втором режиме работы предлагаемого устройства тестовые векторы, вырабатываемые генератором 4 псевдослучайной последовательности, на входы контролируемого блока 6 непосредственно не поступают, а используются как составная

часть адреса ячеек блока 15 памяти, содеркущую, сопровождаемые соответствующими

разрядами блокировки. Возможны следующие ситуации, соответствующие описанным структурам.

Безусловное либо условное невыполнение текущей команды. Код памяти, считываемый с группы информационных выходов

нулевои сигнал первого разряда поступает с первого выхода блока 15 памяти через вход элемента ИЛИ 16 на вход элемен- та И 13. На входе элемента ИЛИ 16 при этом установлен нулевой сигнал, поступающий с входа 26 задания режима устройства для контроля цифровых блоков. Нулевой сигнал с второго разряда поступает с второго выхода блока 15 памяти на вход элемента И 12

и на вход элемента И-НЕ 9,на входе которого

устанавливается единичное состояние.

В этих условиях первый синхросигнал В, поступая с первого выхода генератора 1 на вход элемента И 13, не передается на его вы- ход и во второй регистр 19 не осуществля-

ния текущей команды. Второй синхросиг- нал С поступает через вход элемента И 10,

ется запись текущей команды, которая не поступает на вход контролируемого блока 6. Последний сохраняет свое состояние неизменным, осуществляя имитацию невыполнена синхровходы формирователей 5 сигнатур, обеспечивая формирование сигнатур выход

ных сигналов, поступающих с выходов контролируемого блока 6. На входе элемента 10 присутствует разрешающий сигнал логической «1. Синхросигнал С поступает на вычитающий синхровход счетчика 2, уменьщая его соде ржимое на «1. Третий синхросиг- нал поступает через вход элемента И 11 на вход установки «О счетчика 14 и на синхровходы генератора 4 псевдослучайной последовательности и регистра 17, и не поступает на синхровход счетчика 14. Перед- НИИ фронт упомянутого синхросигнала D подтверждает нулевое состояние счетчика 14, записывает код предыдущей команды с выходов генератора 4 псевдослучайной последовательности в регистр 17 и формирует код следующей команды на выходе генератора 4, которая становится текущей, что обеспечивает считывание из блока 15 памяти очередной ячейки, адрес которой определяется совместным состоянием всех трех групп адресных входов этого блока 15.

Безусловное либо условное выполнение некоторой команды взамен текущей. Код команды, заменяющий текущую, установленную на выходе генератора 4 псевдослучайной последовательности, поступает с группы выходов блока 15 памяти через коммутатор 18 на информационные входы регистра 19. При этом единичный сигнал первого разряда, поступая с первого выхода блока 15 памяти через элемент ИЛИ 16 на вход элемента И 13, разрешает прохождение первого синхросигнала В с первого выхода генератора 1 на синхровход регистра 19, обеспечивая запись .в него и передачу на входы контролируемого блока 6 заменяющей команды. Контролируемый блок 6 выполняет команду, отличную от текущей, переходя в состояние, соответствующее неисправному контролируемому блоку 6. Второй синхросигнал С поступает через вход элемента И 10 на синхровходы формирователей 5 сигнатур, обеспечивая формирование сигнатур выходных сигналов контролируемого блока 6. Это обеспечивается сочетанием нулевых сигна- налов, поступающих с входа 26 задания режима устройства для контроля цифровых блоков и второго разряда блока 15 памяти. При этом осуществляется вычитание единицы из содержимого счётчика 2. Третий синхросигнал D подтверждает нулевое состояние счетчика 14, переписывает код предыдущей команды в регистр 17 и формирует код следующей команды на выходе генератора 4 псевдослучайной последовательности, которая становится текущей. Новое состояние на выходах генератора 4, регистра 17 и счетчика 14 .обеспечивает считывание очередной ячейки из блока 15 памяти и соответствующей текущей команде, поступа- ющей при условии, что на предыдущем такте выполняется предыдущая команда, хранимая в регистре 17. Аналогично выпол

5

5

0 0

5

0

5

0

5

0

няются незаменяемые (нормально выполняемые) текущие команды.

Безусловное либо условное выполнение нескольких команд вместо текущей либо вместе с текущей. Код первой команды, принадлежащий последовательности (цепи) команд, заменяющей текущую команду, поступает с группы выходов блока 15 памяти на информационные входы регистра 19 через коммутатор 18. При этом единичный сигнал первого разряда, поступая с первого выхода блока 15 памяти через логический элемент ИЛИ 16 на первый вход четвертого логического элемента И 13, разрещается прохождение первого синхросигнала В с первого выхода генератора 1 на синхровход регистра 19, обеспечивая запись в него и передачу на входы контролируемого блока 6 замещающей команды. Единичный сигнал второго разряда блокировки, проходя через логический элемент И-НЕ 9, инвертируется и посту- пает в виде запрещающего нулевого сигнала на входы элемента 10 и 11 соответственно. Упомянутый единичный сигнал второго разряда блокировки поступает в виде разрешающего сигнала на вход элемента И 12. Поэтому второй синхросигнал С с второго выхода генератора 1 не поступает через элемент И синхровход формирователей 5 сигнатур и вычитающий вход счетчика 2. Третий сигнал D с третьего выхода генератора 1 не поступает через элемент И 11 на вход установки «О счетчика 14 и на синхровходы генератора 4 псевдослучайной последовательности и регистра 17, сохраняя неизменной пару предыдущая-текущая ко.манда.

Третий синхросигнал С поступает через элемент И 12 на синхровход счетчика 14, увеличивая его содержимое на единицу и вызывая адресацию следующей ячейки блока 15 памяти, принадлежащей этой же цепи. Если второй разряд блокировки этой ячейки единичен, то снова происходит только подача новой команды цепи на входы контролируемого блока 6 без формирования сигнатуры и подсчета числа тестов, а также осу- ш,ествляется приращение содержимого счетчика 14 и. чтение новой команды цепи. Процесс продолжается до тех пор, пока из блока 15 памяти в результате очередного приращения содержимого счетчика 14 не считан код команды, сопровождае.мый нулевым значением второго заряда блокировки (конец цепи). В этом случае первый синхросигнал В также передает команду на вход контролируемого блока 6, но теперь второй синхросигнал С уже поступает через элемент И 10 на синхровходы формирователей 5 сигнатур, обеспечивая формирование сигнатур заключительной реакции контролируемого блока 6 на поданную цепь команд, а также обеспечивая подсчет счетчиком 2 всей цепи как одной команды.

Третий синхросигнал D не поступает через заблокированный элемент И 12 на синхровход счетчика 14, а поступает через эле- - мент И 11 на вход установки «О упомянутого счетчика 14 и на синхровходы генератора 4 псевдослучайной последовательности и регистра 17 соответственно. При этом происходит установка «О счетчика 14, запись кода предыдущей команды с выходов генератора 4 псевдослучайной последовательности в регистр 17 и формирование кода новой текущей команды на выходе этого генератора 4, считывание новой ячейки из блока 15 памяти.

10 щим выходам контролируемого блока, отличающееся тем, что, с целью повыа ения достоверности контроля, в него введены второй, третий и четвертый элементы И, элемент И-НЕ, элемент ИЛИ, компаратор, элемент задержки, два регистра, блок памяТаким образом, процесс повторяется до тех пор, пока очередной синхросигнал С в результате формирования сигнатуры послед-... него теста либо заменяющей его цепи не ти, коммутатор, вход задания режима рабо- приведет к обнулению содержимого счетчи- ты устройства соединен с синхровходами

ка 2, на выходе заема которого появляется импульс установки «О триггера 3 и записи значения сигнатуры контролируемого блока 6 в регистр 37 компаратора 7, разрещаю- 20 мый единичным сигналом, поступающим на вход элемента И 35. Управляющий генератор 1 прекращает вырабатывать синхросигналы, а на выходе готовности предлагаемого устройства появляется единичный

компаратора и коммутатора, с первыми входами элемента ИЛИ и элемента И-НЕ, выход которого соединен с первыми входами первого и второго элементов И, выход которого соединен с синхровходом формирователя сигнатур, и с синхровходом первого счетчика, информационный вход которого соединен с входом задания начальных условий устройства, а выход заема первого

сигнал готовности, сообщающий об оконча- счетчика соединен с входом блокировки комнии процесса подачи воздействий. Элементы суммирования по модулю два группы 38 компаратора 7 осуществляют сравнение значений сформированных сигнатур с эталонными (полученными в первом режиме работы). Результат сравнения этих значений через элемент ИЛИ 33, поступает на выход устройства для контроля цифровых блоков. Если упомянутые одноименные сигнатуры не совпадают (на втором выходе компаратора 7

30

паратора и с входом сброса триггера, прямой выход триггера соединен с входам пуска генератора синхросигналов, первый выход которого соединен с входом третьего элемента И, второй выход генератора синхроимпульсов соединен с вторым входом первого и первым входом четвертого элементов И, третий выход генератора синхроимпульсов соединен с вторым входом второго элемента И и с входом останова генераустановлен единичный сигнал), то псевдо- -, тора псевдослучайной последовательности, случайный тест и формирователи сигнатурвыход первого элемента И соединен с синхрообеспечивают обнаружение проимитирован- ных неисправностей (достоверность теста удовлетворительна). В противном случае проимитированные неисправности не обнару40

жимы тестом (достоверность теста неудовлетворительная). Необходимо подобрать новые вероятностные значения сигналов генератора 4 псевдослучайной последовательности и повторить сначала процесс получевходом первого регистра, с входом сброса второго счетчика, группа выходов генератора псевдослучайной последовательности соединена с первой группой информационных входов коммутатора, с,первой группой адресных входов блока памяти и с группой информационных входов первого регистра, группа выходов которого соединена с второй группой адресных входов блока памяти, вход

ния эталонных сигнатур в первом режимезапись-чтение которого соединен с входом

т-. о ooT Q. т-, .,,. л#с,,л 4j 1япяниа i nHTnnnfl ;ртппйртия RTAработы, а затем процесс проверки обна- ружимости заданного списка неисправностей во втором режиме работы. Отладка псевдослучайных тестов продолжается до тех пор, пока н е достигнута требуемая достоверность контроля.

Таким образом, использование предлагаемого устройства позволяет осуществлять отладку псевдослучайных тестов, используя заведомо исправные контролируемые блоки 6 в интегральном исполнении (т. е. в том случае, когда внесение физических неисправностей практически невозможно), и тем самым повысить достоверность контроля.

50

55

задания режима контроля устройства, второй вход элемента И-НЕ соединен с выходом признака блокировки работы устройства блока памяти и с вторым входом четвертого элемента И, выход которого соединен с входом блокировки второго счетчика, информационный вход которого соединен с входом задания числа тактов работы контролируемого цифрового блока устройства, группа разрядных выходов второго счетчика соединена с третьей группой адресных входов блока памяти, группа выходов поля тестов которого подключена к второй группе информационных входов коммутатора, выход признака конца контроля блока памяти

Формула изобретения Устройство для контроля цифровых блоков, содержащее генератор синхросигналов, два счетчика, триггер, первый элемент И, генератор псевдослучайной последовательности, формирователь сигнатур, причем единичный вход триггера является входом пуска устройства, информационный вход формирователя сигнатур является входом устройства для подключения к соответствующим выходам контролируемого блока, отличающееся тем, что, с целью повыа ения достоверности контроля, в него введены второй, третий и четвертый элементы И, элемент И-НЕ, элемент ИЛИ, компаратор, элемент задержки, два регистра, блок памя... ти, коммутатор, вход задания режима рабо- ты устройства соединен с синхровходами

компаратора и коммутатора, с первыми входами элемента ИЛИ и элемента И-НЕ, выход которого соединен с первыми входами первого и второго элементов И, выход которого соединен с синхровходом формирователя сигнатур, и с синхровходом первого счетчика, информационный вход которого соединен с входом задания начальных условий устройства, а выход заема первого

счетчика соединен с входом блокировки ком0

паратора и с входом сброса триггера, прямой выход триггера соединен с входам пуска генератора синхросигналов, первый выход которого соединен с входом третьего элемента И, второй выход генератора синхроимпульсов соединен с вторым входом первого и первым входом четвертого элементов И, третий выход генератора синхроимпульсов соединен с вторым входом второго элемента И и с входом останова генератора псевдослучайной последовательности, выход первого элемента И соединен с синхровходом первого регистра, с входом сброса второго счетчика, группа выходов генератора псевдослучайной последовательности соединена с первой группой информационных входов коммутатора, с,первой группой адресных входов блока памяти и с группой информационных входов первого регистра, группа выходов которого соединена с второй группой адресных входов блока памяти, вход

1япяниа i nHTnnnfl ;ртппйртия RTA

задания режима контроля устройства, второй вход элемента И-НЕ соединен с выходом признака блокировки работы устройства блока памяти и с вторым входом четвертого элемента И, выход которого соединен с входом блокировки второго счетчика, информационный вход которого соединен с входом задания числа тактов работы контролируемого цифрового блока устройства, группа разрядных выходов второго счетчика соединена с третьей группой адресных входов блока памяти, группа выходов поля тестов которого подключена к второй группе информационных входов коммутатора, выход признака конца контроля блока памяти

соединен с вторым входом элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход которого соединен с входом элемента задержки и с синхро- входом второго регистра, выходы которого являются выходами устройства для подключения к входам контролируемого цифрового

ОтЪ

блока, группа выходов формирователя сигнатур соединена с группой информационных входов компаратора, выходы которого являются выходом ошибки устройства, выход элемента задержки является выходом устройства для подключения к синхровходу контролируемого цифрового блока.

На 115

На 11,12

Фи.

От 5

О т 2 О т 25

Фиг.Ч

| Устройство для отладки тестов | 1979 |

|

SU860076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU951312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-09-26—Подача