Изобретение относится к вычислительной технике и может быть использовано в ее ставе системы радиотелеуправления - телесигнализации, использующей режим ct нхронной связи с перерывами, для организации обмена информацией управляющей вычислительной системы с каналом сайзи.

Целью изобретения является расширение области ,приеменения устройства путем обеспечения достоверного ввода последо- в тельной информации при сопряжении ЦВМ с радиоканалом.

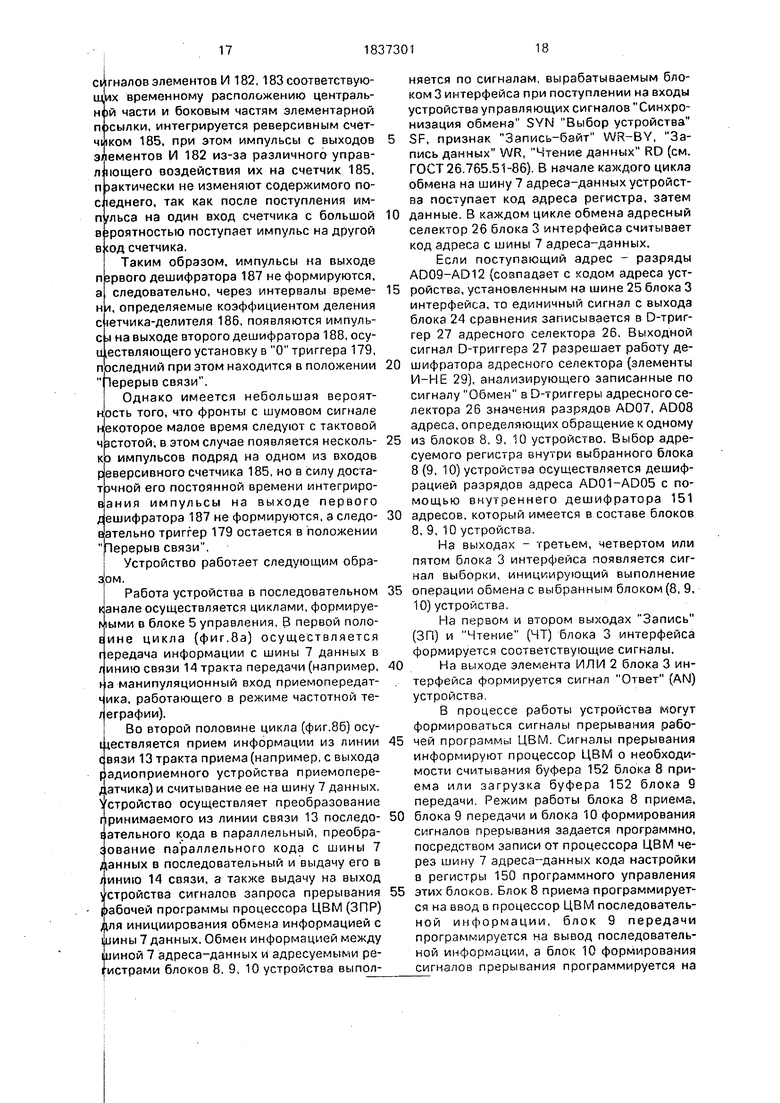

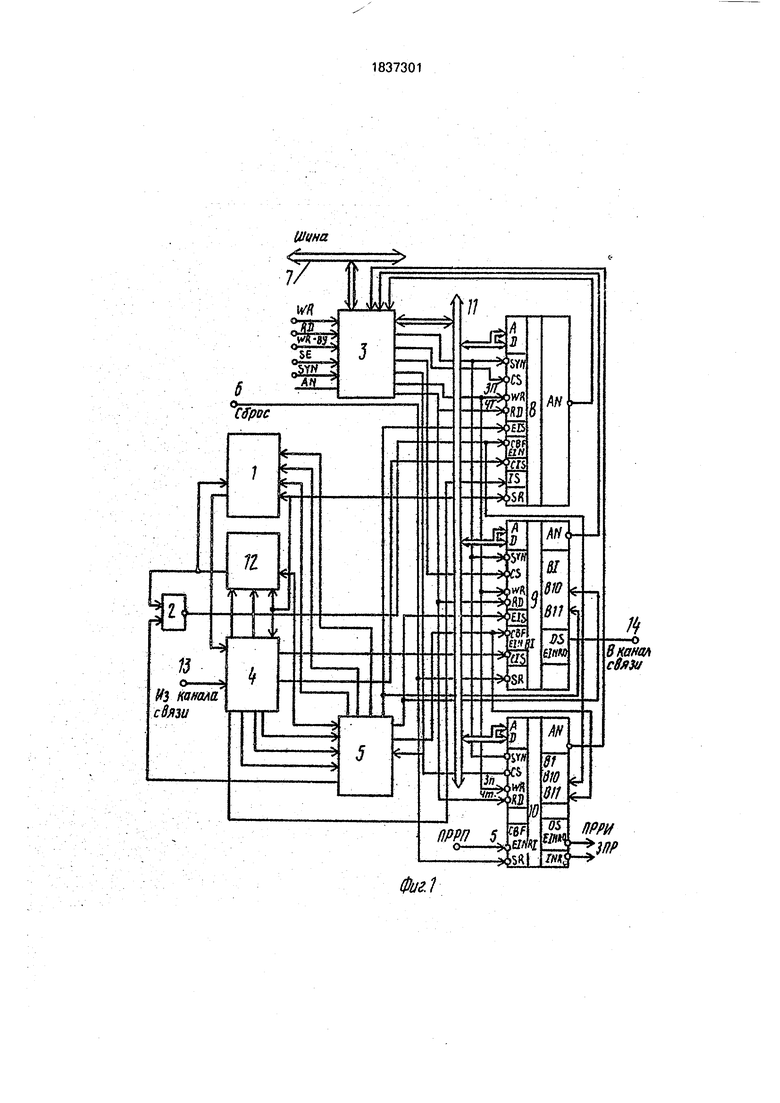

Сущность изобретения поясняется длльнейшим описанием и чертежом фиг.1, нз котором представлена структурная схе- маустройства сопряжения цифровой вычисл

отельной машины с каналом связи.

На фиг.1 обозначены:

1 - формирователь, 2 - элемент И-НЕ, 3 - блок интерфейса, 4 - блок тактовой синхронизации, 5 - блок управления, 6 - вход СБРОС устройства, 7 - шина адреса-дан- ных, 8 - блок приема (ПРМ), 9 - блок передачи (ПРД), 10 - блок формирования сигналов прерывания, 11 - внутренняя шина адреса-данных устройства, 11 - дискриминатор сигнал - шум, 13 - линия связи тракта приема. 14 - линия связи тракта передачи.

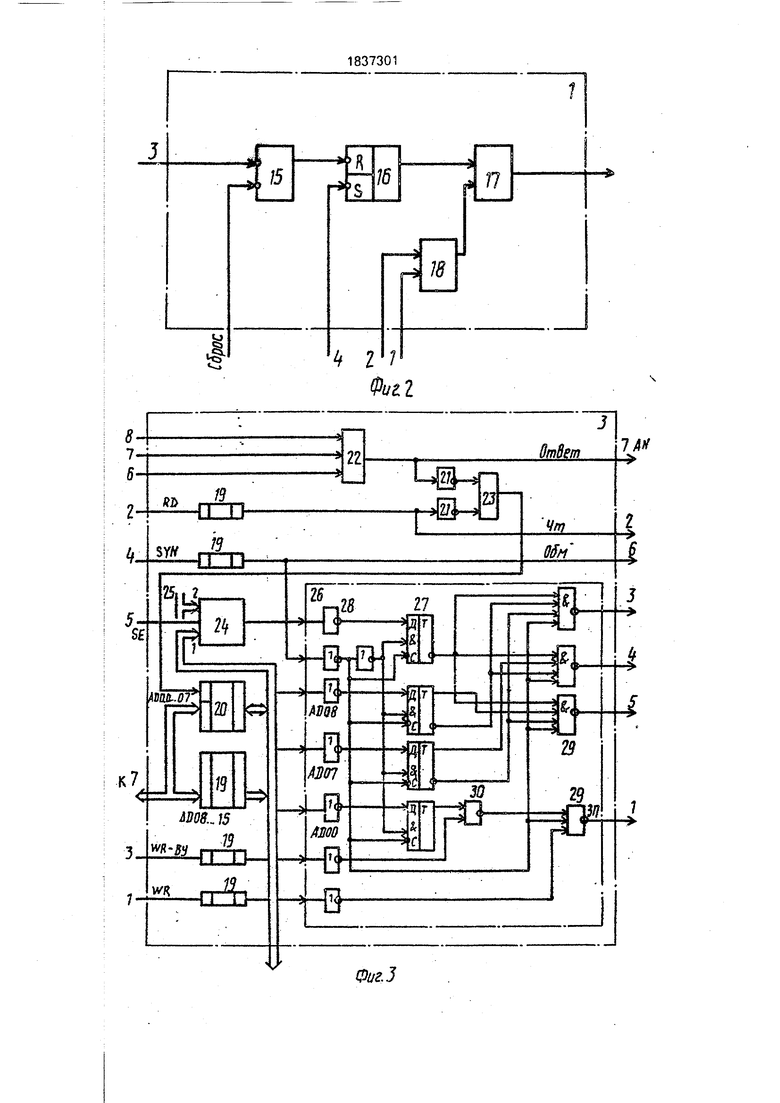

Структурная схема формирователя 1 приведена на фиг.2, где обозначены:

15 - элемент ИЛИ, 16 - триггер, 17 - второй элемент ИЛИ, 18 - элемент И.

Структурная схема блока 3 интерфейса представлена на фиг.З, где обозначены:

00

СА)

4

00 О

19 - магистральные однонаправленные буферы. 20 - магистральные двунаправленные буферы, 21 -элементы НЕ, 22-элемент ИЛИ, 23 - элемент И, 24 - блок сравнения, 25 - шина адреса устройства, 26 - адресный селектор, 27 - D-триггер, 28 - элемент НЕ, 29, 30 - элементы И-НЕ.

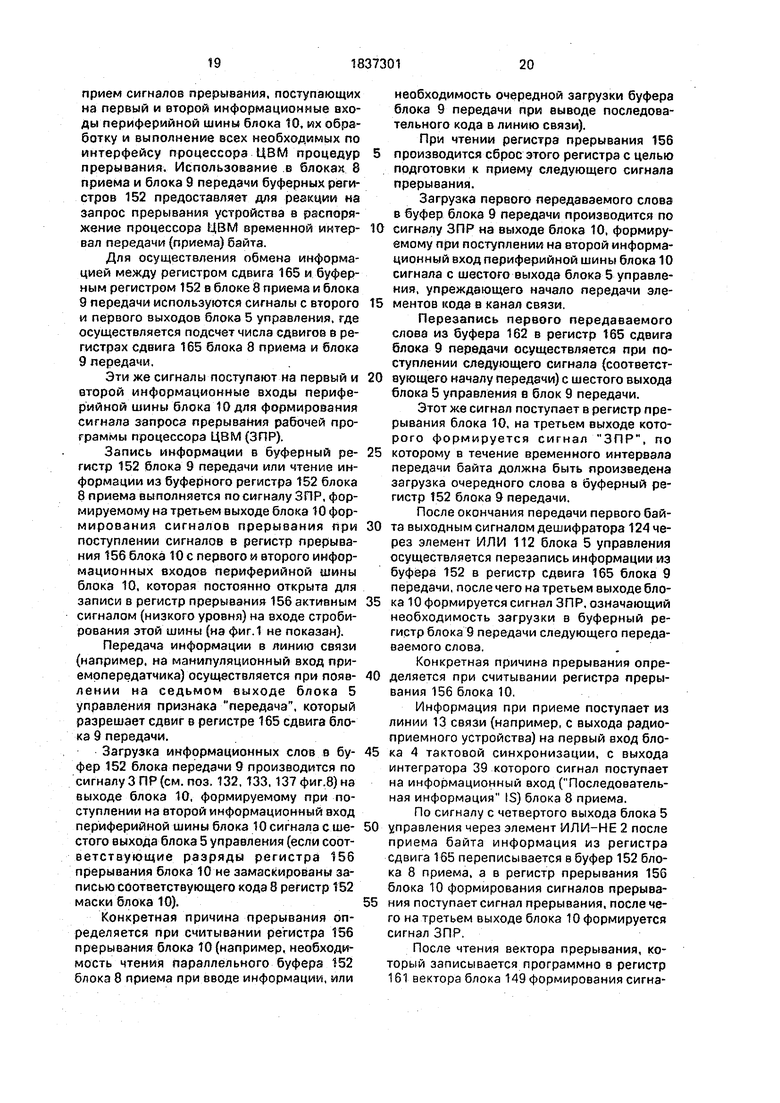

Структурная схема блока 4 тактовой синхронизации приведена на фиг.4, где обозначены;

31 - синхронизатор, 32 - формирователь эталонных тактовых импульсов (ЭТИ), 33 - управляемый делитель частоты, 34 - формирователь сигналов фазовых зон, 35 - умножитель сигналов, 36 - усредняющий блок (реверсивный счетчик), 37 - пороговый блок, 38 - формирователь сигналов, соответствующих фронтам посылок, 39 - интегратор, 40 - формирователь импульсов деления тактового интервала регулируемых тактовых импульсов (РТИ) на 15 равных частей, 41 - генератор импульсов (ГИ), 42 - распределитель импульсов (РИ), 43i...43e - элементы НЕ, 44 - счетчик - делитель частоты, 45 - элемент И (дешифратор), 46 - эле- мент ИЛИ/НЕ, 47 - элемент И, 48 - вычитающий счетчик - делитель, 49 - шина ввода числа, 50 - стробируемый дешифратор нулевого кода, 51 - D-триггер, 52 - элемент ИЛИ, 53, 54 - первый и второй триггеры, 55 - элемент И-НЕ, 56 - элемент НЕ, 57 - вычитающий счетчик - делитель, 58 - стробируемый дешифратор нулевого кода, 59 - D-триггер, 60 - элемент ИЛИ, 61 - элемент НЕ, 62 - элемент И-НЕ, 63 - элемент И, 64 - счетчик, 65 - стробируемый дешифратор, 66, 67 - триггеры, 68, 69 - элементы И-НЕ, 70 - шина ввода числа, 71 стробируемый дешифратор, 72,73 -элементы И-НЕ, 74 - элемент ИЛИ-НЕ, 75 - D- триггер. 76 - элемент ИЛИ, 77 - сумматор по модулю два, 78 - D-триггер, 79 - триггер со счетным входом, 80 - D-триггер, 81 - элемент И, 82 - счетчик, 83 - D-триггер, 841,2.3 - элементы И-НЕ, 84/} - элемент И.

Временная диаграмма, иллюстрирующая работу устройства, представлена на фиг.5. где обозначены:

85 - сигнал на выходе генератора импульсов (ГИ) синхронизатора 31 (F 2,5 МГц, Т 0,4 мкс).

86-93 - сигналы на первом-восьмом выходах распределителя импульсов (РИ) синхронизатора31 Ф1, Ф2...Ф8(Т 1,6мкс, т 0,4 мкс),

94 - эталонные тактовые импульсы (ЭТИ) на седьмом входе (Импульсы сдвига блока 9 передачи F 300 Гц, г т(ФЗУФ4).

95- сигнал РТИ8Ф4 на синхровходе D-триггера интегратора 39,

96- сигнал РТИ8Ф5 на седьмом входе (Импульсы сдвига (CIS)) блока 8 приема.

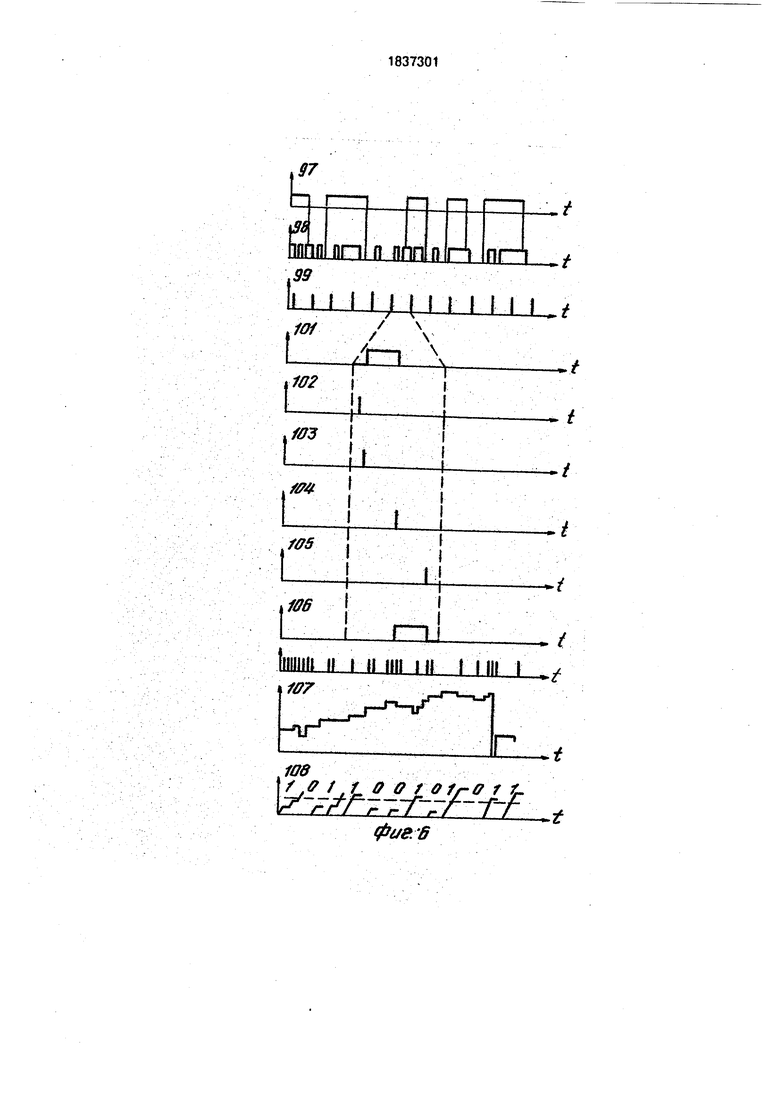

Временная диаграмма, иллюстрирующая работу блока 4 тактовой синхронизации, приведена на фиг.6, где обозначены:

97- кодовая посылка,

98- смесь кодовой посылки и помехи (сигнала с линии связи 13 тракта приема, принятый входным D-триггером 80 формирователя 38 сигналов, соответствующих фронтам посылок),

99- сигнал на выходе дешифратора 58 управляемого делителя 33 частоты блока 4 тактовой синхронизации (регулируемые тактовые импульсы (РТИ), F 300 Гц),

100- сигнал на выходе триггера 66 формирователя 34 сигналов фазовых зон,

101-104 - сигналы на первом-четвер- том выходах дешифратора 65 формирователя 34 сигналов фазовых зон,

105- сигнал на выходе триггера 67 формирователя 34 сигналов фазовых зон.

106- сигнал на выходе сумматора 77 по модулю два формирователя 38,

107- сигнал - на выходе усредняющего блока 36.

108- сигнал на выходе счетчика 82 интегратора 39.

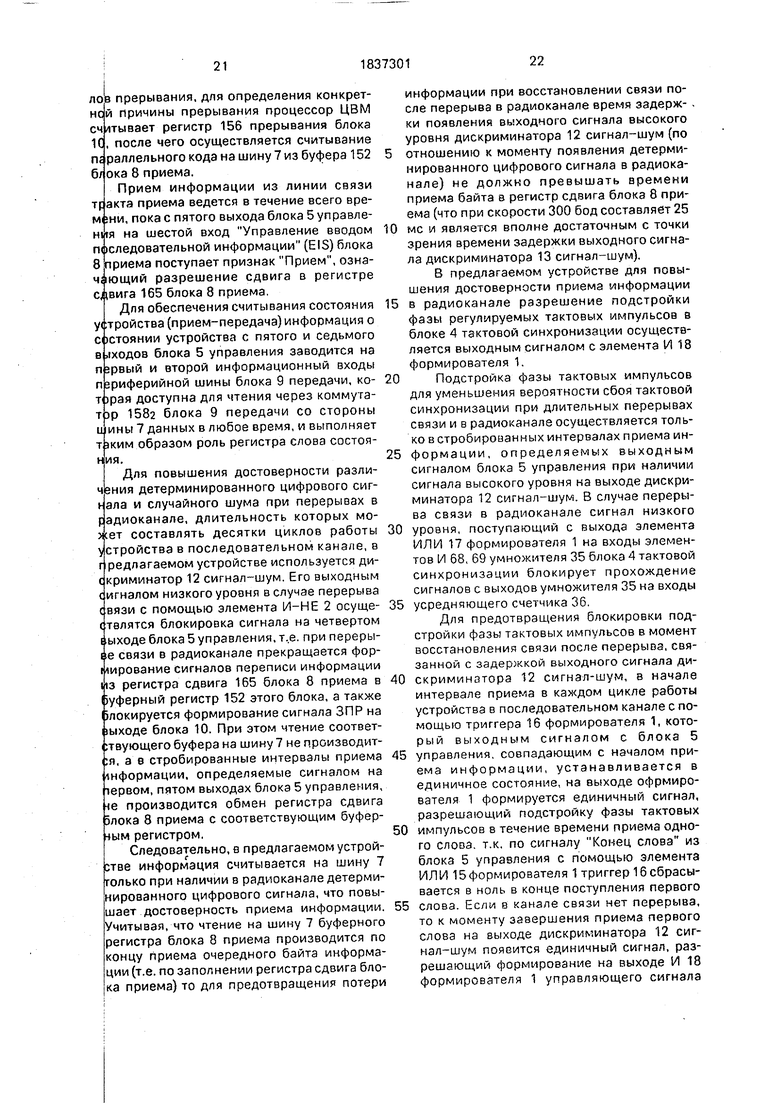

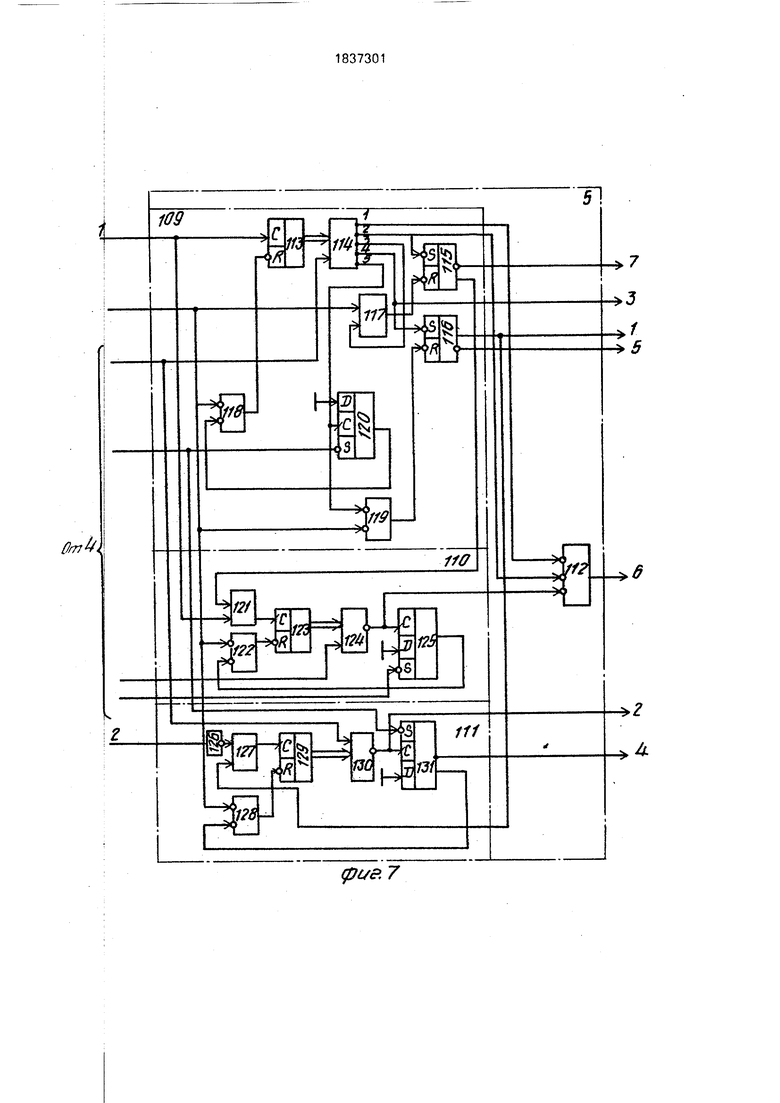

Структурная схема блока 5 управления представлена на фиг.7, где обозначены:

109- формирователь циклограммы работы устройства в последовательном канале,

110, 111 - формирователи сигналов Способ синхронизации обмена между регистрами для блока 9 передачи и блока 8 приема соответственно, 112-элемент ИЛИ, 113 - счетчик, 114 - стробируемый дешифратор. 115, 116 - триггеры. 117-119 - элементы ИЛИ, 120- D-триггер, 121 -элемент И, 122 - элемент ИЛИ, 123 - счетчик, 124 - стробируемый дешифратор, 125 - D-триггер. 126 - элемент НЕ, 127 - элемент И, 128 -элемент ИЛИ, 129-счетчик, 130-стробируемый дешифратор, 131 -D-триггер.

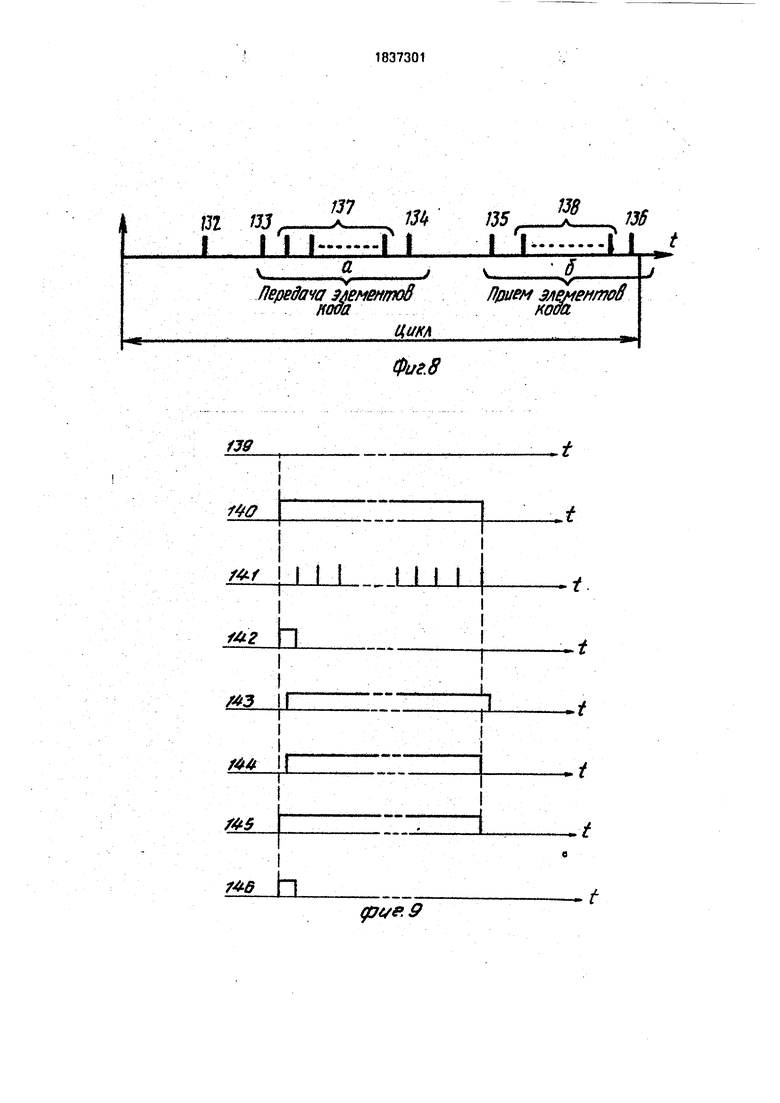

Временная диаграмма, иллюстрирующая цикл работы устройства в последовательном канале, приведена на фиг.8, где обозначены:

132-136-сигналы на первом-пятом выходах дешифратора 114 формирователя 109 циклограммы соответственно,

137, 138 - сигналы на выходах строби- руемых дешифраторов, 124, 130 формирователей 110, 111, соответствующие завершению передачи (приема) слова последовательной информации.

Зременная диаграмма, иллюстрирующая работу формирователя 1, приведена на фиг 9. где обозначены:

139-сигнал Начало приема на выходе бло са 5 управления, 140 - стробированный интфвал приема информации (сигнал на

пер;

зом выходе блока управления),

141- импульсы Завершение приема слова на втором выходе блока 5 управления,

142- сигнал на выходе триггера 16,

14

- сигнал на выходе дискриминатора 12

сигнал - шум при наличии детерминирован- ного цифрового сигнала в канале связи,

14/

-сигнал на выходе элемента И 18, 145 симал на выходе элемента ИЛИ 17, 146 - сигнал на выходе ИЛИ 17 при перерыве свгзи.

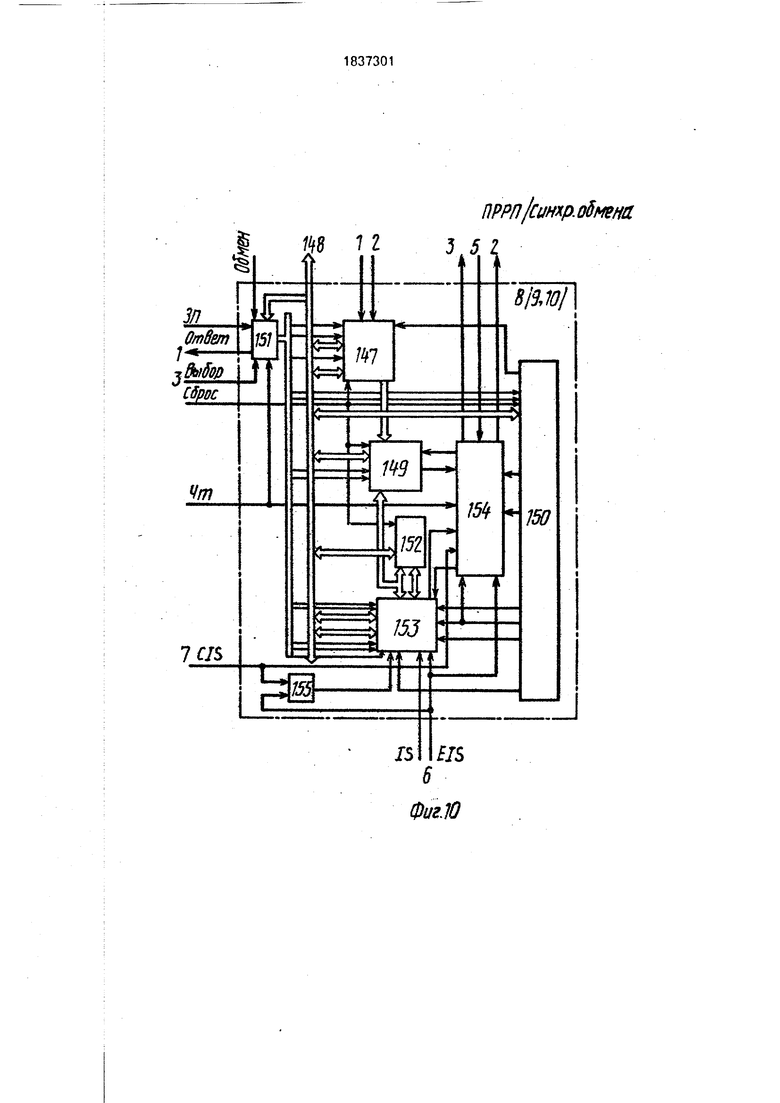

Блоки 8, 9, 10 конструктивно могут быть выполнены на основе параллельно-лосле- допательного адаптера типа М1809ВВ1 (3), структурная схема которого приведена на фи -.10, где обозначены:

147 - блок формирования сигналов обмена информацией, 148 - шина данных, 14 ) - блок формирования сигналов перерыва шя, 150-регистр программногоуправле- ния, 151 - дешифратор, 152 - буферный

гистр, 153 - блок преобразования кодов, 4 - блок управления, 155 - элемент И.

Р& 15

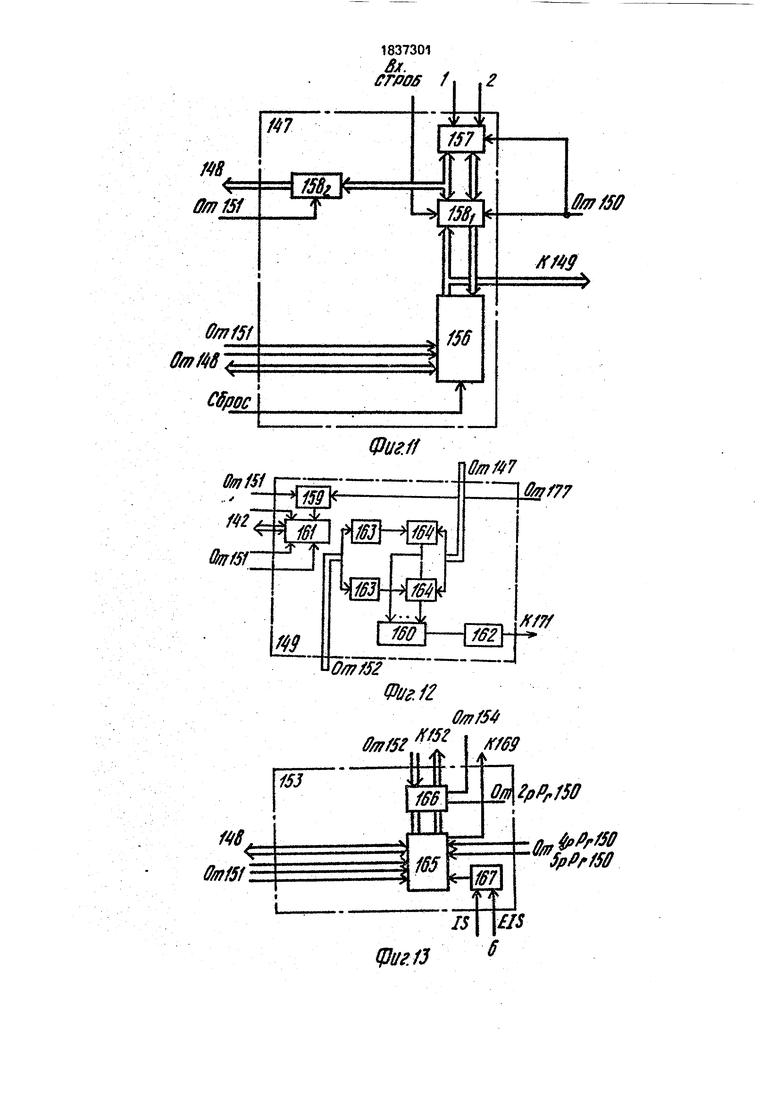

t Упрощенная структурная схема блока формирования сигналов обмена инфор- 1ией представлена на фиг.11, где обозна- чеЬы:

156 - регистр, 157 - многоразрядный магистральный буфер, 1581, 158а - комму- тйгор.

Структурная схема блока 149 формиро- Всния сигналов прерывания представлена HI фиг.12, где обозначены:

159,160-элементы ИЛ И, 161 -регистр, К 2 -формирователь, 163-инверторы, 164 - Э ементы И.

Структурная схема блока 153 преобразования кодов представлена на фиг.13, где обозначены:

165 - регистр сдвига, 166 - коммутатор, 1i57 - элемент И.;

t Структурная схема блока 154 управле- я представлена на фиг. 14, где обозначе- :

168, 169 - элементы ИЛИ, 170 - инвертор, 171-173-триггеры, 174-177,-элеменTJI/I.

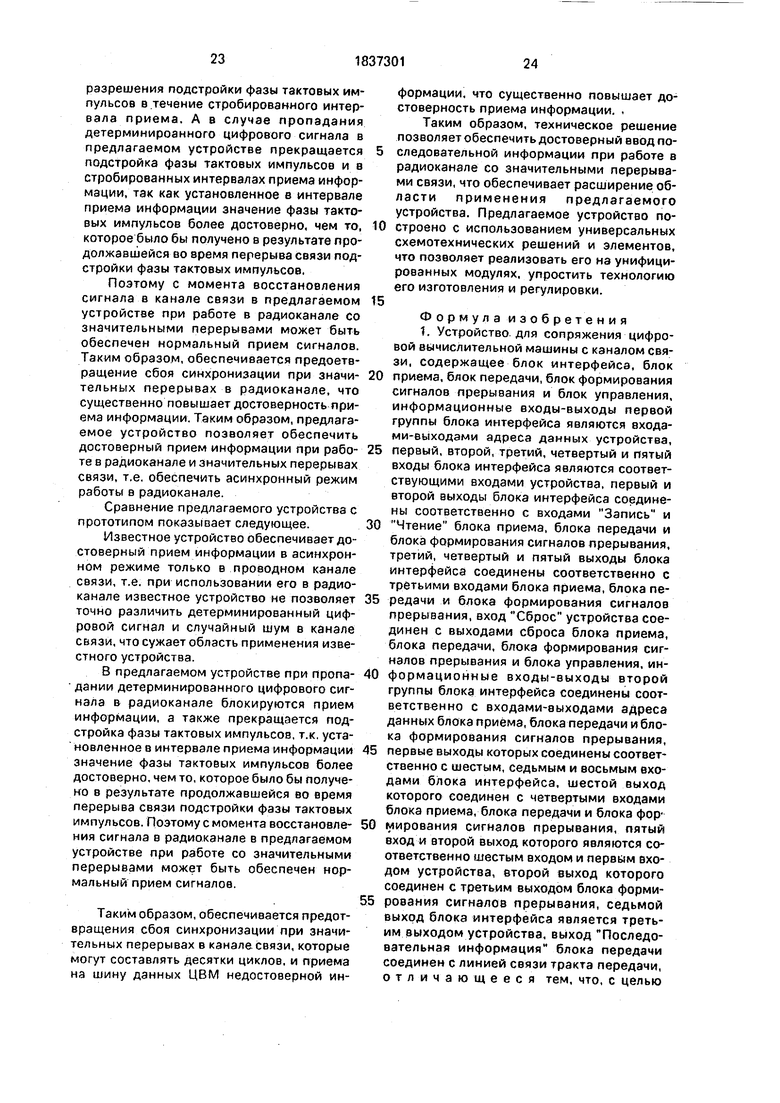

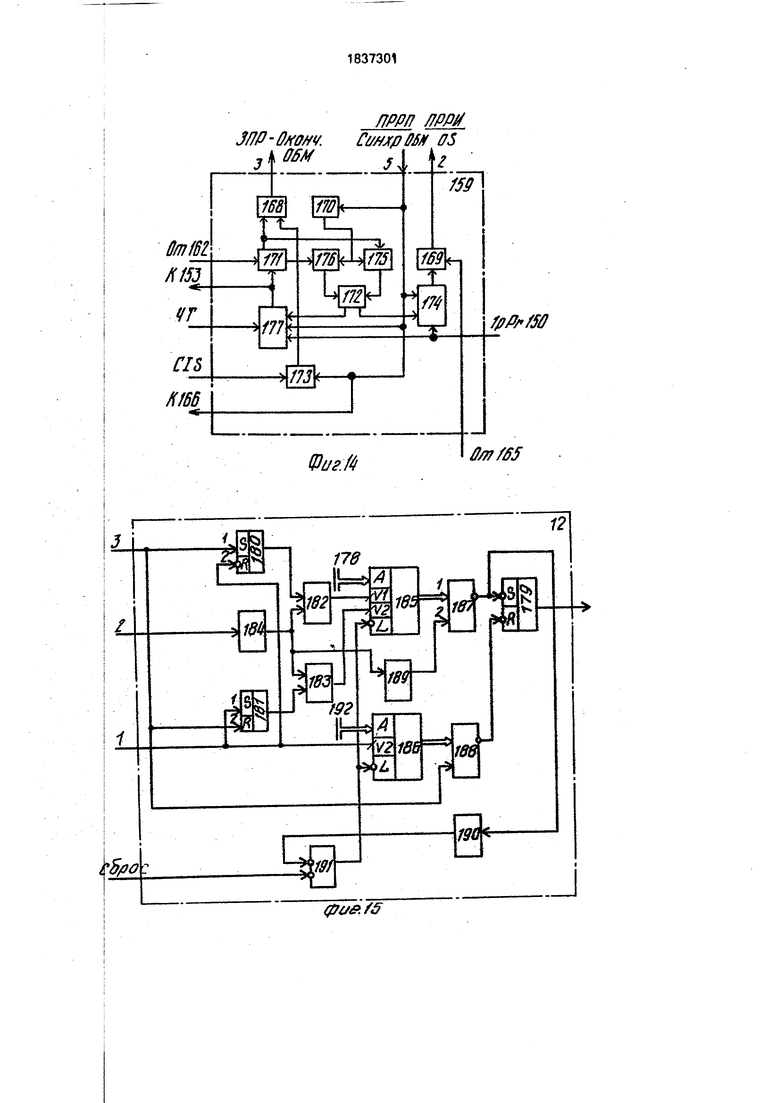

Структурная схема дискриминатора 12 Приведена на фиг.15, где обозначены:

178 - первая шина ввода числа, 179 - эиггер 180 - формирователь импульсов, эответствующих центру посылки, 181 - Ьормирователь импульсов, соответствующих началу и концу посылки, 182, 183 - первый и второй элементы И, 184 - блок задержки, 185 - интегратор (реверсивный счетчик), 186 - счетчик - делитель (вычитающий счетчик). 187, 188 - первый и второй дешифраторы, 189, 190 - первый и второй элементы задержки, 191 -элемент ИЛИ, 192 - вторая шина ввода числа.

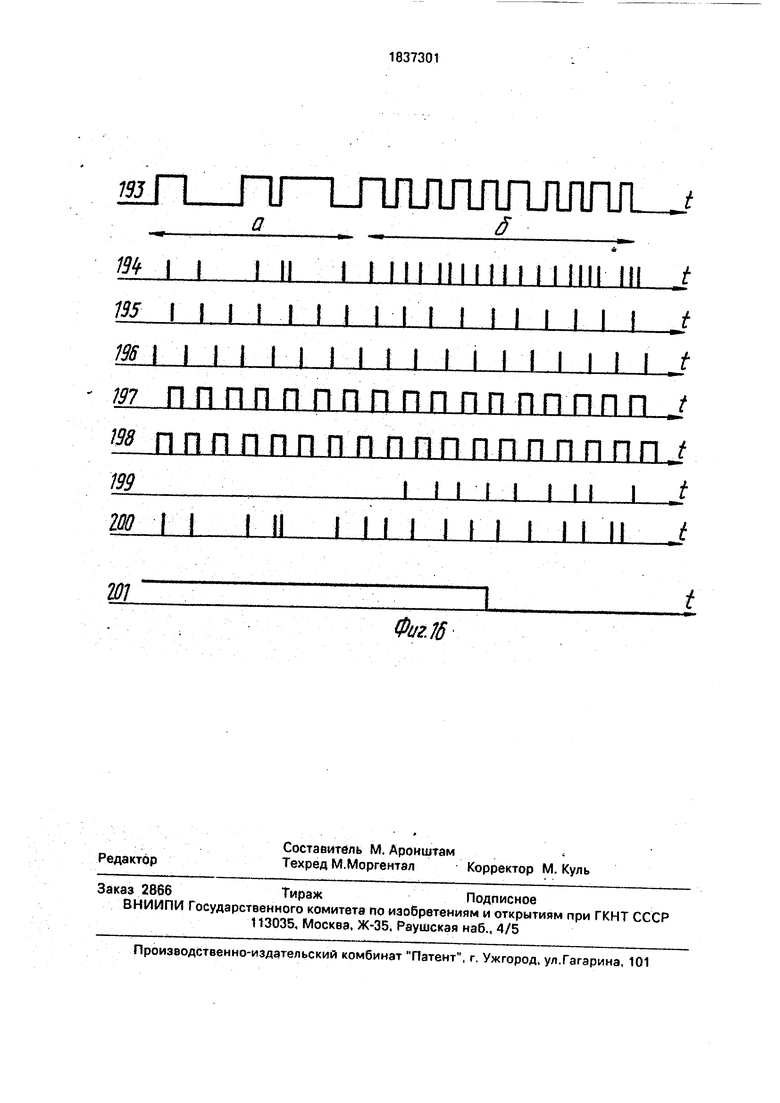

Временная диаграмма, иллюстрирую0 щая работу дискриминатора 12 сигнал - шум, приведена на фиг. 16 , где обозначены:

193 - детерминированный цифровой сигнал (а) и шум (б) в линии связи (на выходе

5 триггера 80 формирователя 38 блока 4 тактовой синхронизации), 194 - сигнал на выходе блока 184 задержки дискриминатора 12 сигнал - шум, 195 - тактовые импульсы, сдвинутые на половину тактового периода,

0 на шестом выходе блока 4 тактовой синхронизации, 196-тактовыеимпульсы,а втором выходе блока 4 тактовой синхронизации, 197 - сигнал на выходе формирователя 180 импульсов, соответствующих центру посыл5 ки, дискриминатора 12 сигнал-шум,

198 - сигнал на выходе формирователя 181 импульсов, соответствующих началу и концу посылки, дискриминатора 12 сигнал- шум,.,0199 - сигнал на выходе первого элемента И 182 дискриминатора 12 сигнал-шум.

200- сигнал на выходе второго элемента И 183 дискриминатора 12 сигнал-шум,

201- сигнал на выходе дискриминатора 5 12 сигнал-шум.

Адрес устройства на магистрали определяется установкой кода на шине 25.

Если в разрядах АД09-АД12 на шине 7 текущее значение кода совпадает с кодом,

0 установленным на шине 25 адреса устройства, то единичный сигнал с выхода блока 24 сравнения, стробируемого сигналом Выбор внешнего устройства на пятом входе блока 3 интерфейса, запоминается по фрон5 ту сигнала Синхронизация обмена на четвертом входе блока 3 интерфейса в D-триггере адресного селектора 26, выходным сигналом которого разрешается работа его внутреннего дешифратора, анализирую-1

0 щего значение разрядов АД07, АД08, определяющих адрес одного из блоков 8, 9, 10 устройства (сигналы на выходах 3,4,5 блока 3 интерфейса).

Для переключения двунаправленных

5 магистральных буферов 20 при чтении информации используется выходной сигнал элемента И 23.

Блок 4 тактовой синхронизации обеспечивает осуществление временной синхронизации, формирование эталонных

тактовых импульсов (ЭТИ), используемых в канале передачи информации и для формирования в блоке 5 управления циклограммы работы устройства, а также осуществляет подстройку фазы регулируемых тактовых импульсов (РТИ) в канале приема по кодовым информационным посылкам, поступающим на информационный вход блока 4 тактовой синхронизации из линии связи 13 тракта приема.

Синхронизатор 31 содержит генератор 41 импульсов (ГИ), многофазный распределитель 42 импульсов (РМ). блок элементов НЕ 43i-43e, счетчик-делитель частоты 44, дешифратор (элемент И) 45, элемент ИЛИ- НЕ 46 и элемент И 47.

Распределитель импульсов 42 предназначен для преобразования последовательности импульсов, поступающей на тактовый вход распределителя (F 2,5 МГц, скважность - 2), в распределенные по отдельным шинам тактовые импульсы (такты). Распределитель импульсов построен на 8- разрядном сдвигателе на D-триггерах, замыкаемом в кольцо. На выходах сдвигате- яя образуются 8 перекрывающихся тактовых последовательностей (Ф1,Ф2-Ф8), у которых интервал перекрытия равен полупериоду входной частоты. Длительность тактового импульса равна периоду входной частоты (0,4 мкс).

Номера выходов распределителя 42 импульсов соответствуют номерам тактов его выходных сигналов.

Формирователь 32 эталонных тактовых импульсов (ЭТИ) содержит счетчик-делитель 48, работающий на вычитание, шину 49 ввода числа, выходной код которой соответствует коэффициенту деления (К 64) счетчика-делителя 48, етробируемый дешифратор 50 нулевого кода и формирователь отрицательного импульса предварительной установки счетчика-делителя 48 на основе D-триггера 51, D-вход которого соединен с шиной О питания, и элемента ИЛИ 52.

Управляемый делитель 33 частоты содержит шифратор, состоящий из триггеров 5.3,54, элемента И-НЕ 55 и элемента НЕ 56, счетчик-делитель 57, работающий на вычитание, етробируемый дешифратор нулевого кода 58, формирователь отрицательного импульса предварительной установки счетчика-делителя 57 на основе D-триггера 59, D-вход которого соединен с шиной О питания, и элемента ИЛИ 60, элементы НЕ 61, И 62, И-НЕ 63,

Формирователь 34 сигналов фазовых зон содержит счетчик 64, етробируемый дешифратор 65 и триггеры 66, 67.

Умножитель 35 сигналов содержит элементы И-НЕ 68, 69.

Усредняющий блок 36 содержит реверсивный счетчик и шину 70 его предваритель- 5 ной установки, на которой задается число, равное половине емкости счетчика, определяющее коэффициент усреднения импульсов рассогласования.

Пороговый блок 37 соержит стробируе0 мый дешифратор 71 нулевого кода, 2 элемента И-НЕ 72. 73 элемент ИЛИ-НЕ 74 и формирователь отрицательного импульса предварительной установки счетчика усредняющего блока 36 на основе D-триггера 75,

5 D-вход которого соединен с шиной О питания.

Формирователь 38 сигналов, соответствующих фронтам посылок, осуществляет фиксацию моментов перехода через нуль

0 сигналов, приходящих из канала связи. Конструктивно формирователь 38 выполнен в виде цепи, состоящей из последовательно соединенных сумматора 77 по модулю два, D-триггера 78, выполняющего роль эле5 мента задержки и триггера 79 с счетным входом, выход которого соединен с одним из входов сумматора 77 по модулю, два второй вход которого соединен с выходом входного D-триггера 80. Выход сумматора 77 по

0 модулю два является выходом формирователя 38.

Интегратор 39 осуществляет интегрированный поэлементный (побитный) прием информационных посылок. Интегратор 39

5 содержит последовательно соединенные элементы И 81, счетчик 82 и О-триггер 83.

Формирователь 40 импульсов деления тактового интервала РТИ на 15 равных частей содержит дешифраторы - элементы И0 НЕ и элемент Л.

На первый вход элемента И 844 поступают импульсы дискретизации фазы (ИДЖФ) с выхода элемента И 47 синхронизатора 31 (64 импульса ИДФ составляют

5 номинальную длительность тактового интервала РТИ).

Сигнал с выхода элемента И-НЕ 84i обеспечивает прохождение каждого четвертого импульса ИДФ на выход элемента И

0 844, т.к. входы этого элемента И-НЕ 84i соединены с выходами младших разрядов счетчика 57.

Выходной сигнал элемента И-НЕ 84z запрещает прохождение каждого 64-го им5 пульса ИДФ на выход элемента И 844.

Таким образом, тактовый интервал РТИ делится на 15 частей с помощью импульсов, формируемых на выходе элемента И 844.

Блок 4 тактовой синхронизации работа- ет следующим образом. Частота импульсов

дискретизации фазы (ИДФ) с выхода элемента И 45 синхронизатора 31 делится (коэффициент деления Ко 64) с помощью вычитающего счетчика 48 формирователя ЭТИ 32, на выходе дешифратора 50 нулевого кода которого, стробируемого импульсами с выхода элемента И 47 синхронизатора 31 формируются эталонные тактовые им- путьсы.

Импульсы ИДФ также делятся с помощью вычитающего счетчика 57 управляе- мс го делителя частоты 33, на выходе дешифратора 58 нулевого кода которого. ст эобируемого импульсами с выхода эле- ме нта И 47 синхронизатора 31, формируют- регулируемые тактовые импульсы (РТИ). етчик считает импульсы от Ко (или другого ганавливаемого на него коэффициента К) Д 0.

Из информационных посылок, поступа- ю(цих из канала связи, на выходе сумматора по модулю два формирователя 38 форми- ются короткие импульсы, длительность торых (0.4 мкс) определяется величиной зности фаз сигналов на синхровходах одного D-триггера 80 (Ф1) и D-триггера 78 (сфз), совпадающие по фронту с моментом рехода через нуль информационных полок.

Для осуществления привязки эсинхрон- го сигнала, поступающего с выхода ра- д оприемного устройства линия связи, к еменной диаграмме работы блока 4 так- тфвой синхронизации, на входе формировали 38 используется D-триггер 80, с мощью которого осуществляется опрос одного информационного .сигнала сигна- м с первого выхода распределителя 42 пульсов синхронизатора 31 (Т 1,6 мкс), ч стота которого значительно превышает орость работы в последовательном канале (F 300 Гц) и, следовательно, при этом практически отсутствуют искажения входного сигнала, связанные с его временной дискретизацией.

При изменении значения сигнала, по- сгупающего из канала связи, с выхода входного D-триггера 80 на вход сумматора 77 по модулю два формирователя 38. на выходе мматора 77 возникает единичный сигнал, торый поступает через D-триггер 78 на етный вход триггера 79 и положительным ронтом перебрасывает его в противопо- ожное состояние. I Изменившийся на выходе триггера 79 сигнал, заведенный на вход сумматора 77 по модулю два, восстанавливает на выходе (умматора 77 по модулю два сигнал О.

Умножитель сигналов 35 контролирует попадание сигналов, соответствующих

фронтам посылок, в одну из трех зон такта (равного интервалу соседними тактовыми импульсами) зоны отставания, зоны опережения и зоны синхронного приема

(см. поз. 100, 105 фиг. 6),

Интегратор 39 осуществляет интегрированный поэлементный прием информационных посылок. На входы элемента И 81 интегратора 39 поступают импульсы с фор0 мирователя 40 импульсов деления тактового интервала РТИ на 15 частей и с выхода входного D-триггера 80. Выходной сигнал элемента И 81 интегратора 39 подсчитывается счетчиком 82, сигнал с выхода старшего

5 разряда которого в конце каждого такта считывается D-триггером 83 интегратора 39. Если с выхода элемента И 81 снимается за такт 8 или больше импульсов, то с выхода D-триггера 83 интегратора 39 снимается

0 единичный уровень сигнала, в противном случае - нулевой сигнал.

Коррекция фазы тактовых импульсов производится, если фронты принимаемых сигналов попадают в зону опережения или

5 отставания.

Для обеспечения достаточной помехоустойчивости синхронизации фазовое рассогласование интегрируется реверсивным счетчиком усредняющего блока 36.

0 Коррекция фазы производится, если пороговым блоком 37 зафиксировано определенное число импульсов рассогласования.

Сигналы триггеров 66, 67 формировате5 ля 34 сигналов фазовых зон управляют элементами 1/1-НЕ 68, 69 умножителя 35, разрешая прохождение импульсов с выхода формирователя 38 на усредняющий блок 36.

0В зависимости от фазового положения

фронтов входного сигнала реверсивный счетчик 36 работает на сложение или на вычитание. Предварительно в реверсивный счетчик 36 записывается число, равное по5 ложению его емкости. На выходе дешифратора 71 нулевого кода порогового блока 37 сигнал появляется при нулевом состоянии реверсивного счетчика усредняющего блока 36, т.е. когда разность числа отстающих и

0 опережающих импульсов равна числу, введенному в реверсивный счетчик 36 при его предварительной установке. Если содержимое реверсивного счетчика усредняющего блока 36 не превышает заданных порогов,

5 на счетчик-делитель 57 управляемого делителя 33 устанавливается номинальный коэффициент деления (Ко 64) и длина очередного такта является номинальной. В случае, если границы кодовых посылок опережают тактовые импульсы и сигнал положительной разности фаз накапливается в реверсивном счетчике 36 до величины, превышающей установленный порог, на счетчик-делитель 57 управляемого делителя 33 с выхода шифратора (позиции 53, 54, 55, 56) блока 33 устанавливается уменьшенный коэффициент деления 63, и очередной такт укорачивается на один интервал импульсов ИДФ, поступающих на счетный вход счетчика-делителя 57 управляемого делителя 33 частоты. Одновременно сигнал с выхода D-триггера 75 порогового блока 37 через элемент ИЛИ 76 осуществляет предварительную запись в реверсивный счетчик 36 после чего накопление сигнала возможной разности фаз в реверсивном счетчике 36 начинается сначала,

Аналогичным образом, блок 4 тактовой синхронизации работает при отставании границ кодовых посылок от тактовых импульсов, В этом случае при превышении содержимым реверсивного счетчика 36 порога на счетчик-делитель 57 управляемого делителя 33 устанавливается увеличенный коэффициент деления (К 65), и очередной такт удлиняется на один интервал импульсов ИДФ на счетном входе счетчика-делителя 57 управляемого делителя частоты 33.

Так происходит приближение тактовых импульсов к границам кодовых посылок.

Блох 5 управления формирует циклограмму работы устройства в последовательном канале, а также обеспечивает счет числа сдвигов в регистрах сдвига блока 8 приема и блока 9 передачи, и обеспечивает формирование сигналов, соответствующих завершению приема (передачи) слов последовательного кода.

Формирователь 109 блока 5 управления Обеспечивает циклический счет эталонных тактовых импульсов, формируя при этом циклограмму работы устройства в последовательном канале.

Формирователи 110 и 111 обеспечивают счет числа сдвигов соответственно в регистрах сдвига блока 9 передачи и блока 8 приема и вырабатывают на выходах своих дешифраторов 2124 и 130 сигналы, соответствующие завершению передачи (приема) слова последовательного кода.

С помощью элемента ИЛИ 112 формируется сигнал Строб синхронизации обмена между регистрами для блока 9 передачи.

С помощью D-триггеров 125 и 131 D- входы которых соединены с шиной О пита- ния, осуществляется формирование отрицательных импульсов для сброса соответствующих счетчиков.

Блок 8 приема обеспечивает прием последовательного кода, поступающего из линии связи 13 (например, с выхода радиоприемного устройства радиоканала) и хранение принятого символа в буферном регистре в течение временного интервала приема следующего символа из линии связи.

Блок 9 передачи обеспечивает вывод по

0 линии связи 14 в виде последовательного крда информации, поступающей с шины 7 устройства.

Блок 10 формирования сигналов прерывания обеспечивает формирование, хране5 ние и выдачу в процессор ЦВМ сигналов прерывания рабочей программы ЦВМ, возникающих в процессе обмена с периферийным устройством (приемопередатчик) линии связи.

0 Адаптер типа М1809ВВ1 имеет 8-разрядную структуру с расчетом на подключение к правому (младшему) байту разрядной сетки процессора ЦВМ. Адаптер воспринимает и дешифрирует разряды адреса 05-01.

5 Адаптер М1809ВВ1 является многофункциональным устройством, в котором перестройка функций выполняется программно подачей соответствующих адресов на дешифратор 151 и записью соответствующих

0 управляющих кодов в регистр 150 программного управления.

В предлагаемом устройстве используются следующие функции, которые может выполнять адаптер:

5 1. Вывод параллельным потенциальным или импульсным кодом на первую и вторую периферийную шину данных с шины 148 через регистр 156 блока 147 соответственно.

0 2. Ввод данных параллельным кодом с периферийной шины через коммутатор 1582 многоразрядных шин блока 147 на шину данных Т48.

3.Ввод данных с периферийной шины и 5 регистр 156 блока 147 по внешним импульсам сопровождения.

4.Прием сигналов прерывания с периферийной шины в регистр 156, обработку их в блоке 149 по коду маски в регистре 152 и

0 вывод сигнала Запрос прерывания.

5.Считывание на шину 148 из регистра 161 вектора прерывания (записанного в него при первоначальном включении) по сигналу Предоставление прерывания

5 приемнику на пятом входе адаптера при наличии сигнала Запрос прерывания на третьем выходе адаптера.

6.Вывод на второй выход адаптера последовательным кодом по импульсам сдвига на седьмом входе адаптера содержимого

регистра 165, которое предварительно было в него записано с шины 11 или регистра 152.

7. Преобразование входного последовательного кода поступающего по шине Последовательная информация в параллельный код по импульсам сдвига на седьмом входе адаптера с помощью регистра 1 )5 с последующим считыванием из него цину 11 или в буферный регистр 152. .

Существует взаимооднозначное соот- вэтствие между значением каждого разряда регистра и выполняемой функцией адаптера ввода-вывода (номера разрядов регистра 150 соответствуют номерам его выводов.

Обмен информацией между шиной 11 дреса-данных и регистрами 150, 152, 156, 61,165 выполняется по сигналам с выходов ешифратора 151, который в каждом цикле бмена по переднему фронту сигнала 06- ен считывает.код адреса с шины 11 (в ачале каждого цикла обмена на шину 11 вступает код адреса, а затем данные) и по игнала Запись (ЗП) или Считывание -IT) формирует на одном из своих выходов дресное обращение к какому-либо блоку даптера для разрешения обмена, а на вы- одную шину Ответ выдает сигнал Ответ для завершения цикла обмена по интерфей- у процессора ЦВМ.

Адаптер может быть настроен программе на прием сигналов прерывания, посту- ающих с первой периферийной шины, их бработку и выполнение всех необходимых о интерфейсу процессора ЦВМ процедур рерывания.

Этот режим работы задается сигналом первого выхода (разряда) регистра 150, вступающего на входы элементов I/I 174, 77 блока 154, следующим порядком:

при 1р Рг150 1 и 6р Рг150 1 в регистр 156 блока 147 с периферийной шины записываются сигналы прерывания, регистр 152 используется как регистр маски, по третьему выходу выдается сигнал Запрос прерывания, по пятому входу поступает сигнал Представление прерывания приемнику, на второй выход выдается сигнал Предоставление прерывания источнику.

; Блок 149 формирует на своем выходе сигнал, когда в какой-либо разряд регистра 156 блока 147 поступил сигнал прерывания, |а соответствующий ему разряд регистра 152 |находится в сброшенном состоянии (не за- | маскирован).

I Запись 1 в какой-либо разряд регист- 1 ра 152 блокирует (маскирует) прохождение сигнала прерывания из соответствующего

разряда регистра 156 блока 147 на выход блока 149, т.е. в блоке 149 выполняется сборка с помощью элемента ИЛИ 160 поразрядных совпадений на элементах И 164 прямых кодов регистра 156 блока 147 и инверсных кодов с помощью инверторов 163, регистра 152.

Формирователь 162 по переднему фронту сигнала, поступающего с выхода

0 элемента ИЛИ 160, выдает на своем выходе импульсный сигнал, который переводит триггер 171 блока 154 в состояние 1, при котором сигнал с его первого выхода через элемент И 175, который по своему второму

5 входу имеет разрешение при отсутствии сигнала на пятом входе адаптера переводит триггер 172 в состояние 1, при котором он выдает разрешение на элемент И 177 и блокирует элемент И 174.

0 Одновременно сигнал с выхода триггера 171 через элемент ИЛИ 168 формирует на третьем выходе адаптера сигнал Запрос прерывания.

В ответ на сигнал Запрос прерывания

5 процессор выставляет на пятом входе адаптера сигнал Предоставление прерывания приемнику и сигнал Считывание на втором входе адаптера, которые через элемент И 177, подготовленный по двум другим сво:

0 им входам сигналами на пятом входе адаптера и первом выходе регистра 150, осуществляет сброс триггера 171 и через элемент ИЛИ 159 блока 149 считывание вектора прерывания из регистра 161 на шину

5 11 (вектор прерывания записывается предварительно в регистр 161 с шины 7 программно).

При сбросе триггера 171 снимается сигнал Запрос прерывания с третьего выхода

0- адаптера.

По окончании сигнала Предоставление прерывания приемнику на пятом входе адаптера сигнал с выхода инвертора 170 разрешает через элементы И 175, 176 пере5 пись состояния триггера .171 (к этому моменту он уже сброшен) и триггера 172.

В сброшенном состоянии триггер 172 блокирует элемен И 177 и выдает разрешение на элемент И 174.

0В соответствии с процедурой ввода сигнала прерывания по интерфейсу, когда в системе используются несколько устройств ввода-вызода, работающих в режиме ввода сигналов прерывания и на вход данного ус5 тройства (на пятый вход адаптера (пришел сигнал Предоставление прерывания приемнику (и ответ на сигнал Запрос прерывания от другого устройства) на третьем выходе адаптера отсутствует сигнал Запрос прерывания (триггер 171 находится в

сброшенном состоянии, то сигнал с пятого входа адаптера через элемент И 174, подготовленный по двум другим входам сигналами: от триггера 172 и от первого разряда регистра 150 и через элемент ИЛИ 169, фор- мирует на втором выходе адаптера сигнал Предоставление прерывания источнику (поступающий на пятый вход другого устройства ввода-вывода, работающего в системе прерывания с меньшим приорите- том).

Адаптер может быть программно настроен на выполнение процедуры ввода вывода последовательной информации, когда регистр 165 блока 153 используется для вво- да через шину (Последовательная информация) или вывода через шину (Последовательная информация) последовательных кодов с промежуточной буферизацией данных через регистр 152.

Разрешение ввода последовательной информации задается сигналом Управление вводом последовательной информации.

Настройка адаптера на выполнение же- лаемой процедуры осуществляется через регистр 150 программного управления.

При 4рРг150 1 регистр 165 работает в режиме сдвигового регистра для ввода-вывода последовательной информации по сиг- налам сдвига, поступающим на седьмой вход адаптера, которые поступают на управляющий вход регистра 165.

На выход блока 154 и далее на коммутатор 166 проходит сигнал Синхронизация обмена между регистрами 152, 165 с пятого входа адаптера.

Ввод или вывод последовательеных кодов определяется сигналом с выхода 2-го разряда регистра 150 программного управ- ления, поступающего на коммутатор 166 многоразрядных шин блока 153.

При 2р Рг150 1 по сигналу с выхода блока 154 происходит перезапись содержимого регистра 152 через коммутатор много- разрядных шин 166 блока 153 и регистр 165 и выдача из него последовательного кода по сигналам сдвига на седьмом входе адаптера на второй выход адаптера (Последовательная информация).

При 2р Рг150 0 происходит прием входной информации, поступающей с шины Последовательная информация последовательным кодом через элемент И 167 блока 153, подготовленный по второму входу сигналом Управление вводом последовательной информации на шестом входе адаптера, на вход регистра 165 и по сигналу с выхода блока 154 (завершение приема байта) перепись ее из регистра 165 через

коммутатор 166 многоразрядных шин в буферный регистр 152.

Дискриминатор 12 сигнал-шум формирует на выходе сигнал низкого уровня при пропадании детерминированного цифрового сигнала в канале связи.

На второй вход дискриминатора 12 сигнал-шум поступают импульсы с выхода сумматора 77 по модулю 2 формирователя 38 блока 4 тактовой синхронизации, соответствующие фронтам посылок в канале связи.

. На первый и третий входы дискриминатора 12 сигнал-шум поступают с выходов блока 4 тактовой синхронизации соответственно тактовые импульсы, имеющие одинаковую частоту и сдвинутые между собой на половину тактового периода.

Различение поступления из канала связи детерминированного сигнала или случайного шума основано на различии закона распределения фронтов сигнала или фронтов случайного шума.

Если фронты сигнала даже при больших временных искажениях распределены с небольшой дисперсией относительно границ идеальной посылки, то в центральной части посылки таких фронтов становится незначительное количество (дробление посылок и импульсные помехи).

При воздействии на вход устройства случайного шума фронты от этого шума распределяются равномерно в интервале всей длительности посылки, поэтому при подсчете выходных сигналов формирователя 38 блока 4 тактовой синхронизации в центре и по краям посылок количество фронтов примерно одинаково, если интервал опробования в центре и сумма интервалов опробования по краям посылки равны.

При перерыве цифрового сигнала на вход блока 4 тактовой синхронизации поступает шум, уровень которого соизмерим с уровнем цифрового сигнала, что объясняется наличием автоматической регулировки усиления в приемном устройстве радиоканала.

На выходе формирователя 38 блока 4 тактовой синхронизации возникают импульсы и в момент прохождения шумового напряжения через нуль, которые через блок 184 задержки поступают на входы элементов И 182, 183. Поскольку импульсы от случайного шума распределены равномерно в интервале всей длительности посылки, а длительности центральных импульсов равны сумме длительностей импульсов начала и конца посылки, то появление импульсов с выходов обоих элементов И 182, 183 равновероятно. Фазовое смешение выходных

сигналов элементов И 182,183 соответствующих временному расположению центральной части и боковым частям элементарной посылки, интегрируется реверсивным счетчиком 185. при этом импульсы с выходов элементов И 182 из-за различного управляющего воздействия их на счетчик 185. п эактически не изменяют содержимого последнего, так как после поступления импульса на один вход счетчика с большой вероятностью поступает импульс на другой вход счетчика.

Таким образом, импульсы на выходе пэрвого дешифратора 187 не формируются, а следовательно, через интервалы времени, определяемые коэффициентом деления счетчика-делителя 186, появляются импульса на выходе второго дешифратора 188, осуществляющего установку в О триггера 179, последний при этом находится в положении Перерыв связи.

Однако имеется небольшая вероят- н ость того, что фронты с шумовом сигнале некоторое малое время следуют с тактовой частотой, в этом случае появляется несколько импульсов подряд на одном из входов реверсивного счетчика 185, но в силу достаточной его постоянной времени интегрирования импульсы на выходе первого дешифратора 187 не формируются, а следо- тельно триггер 179 остается в положении ерерыв связи.

Устройство работает следующим образцом.

Работа устройства в последовательном канале осуществляется циклами, формируемыми в блоке 5 управления, В первой поло- еине цикла (фиг.За) осуществляется гередача информации с шины 7 данных в линию связи 14 тракта передачи (например, на манипуляционный вход приемопередатчика, работающего в режиме частотной те- геграфии).

Во второй половине цикла (фиг.8б) осуществляется прием информации из линии с вязи 13 тракта приема (например, с выхода радиоприемного устройства приемопередатчика) и считывание ее на шину 7 данных. Устройство осуществляет преобразование принимаемого из линии связи 13 последовательного кода в параллельный, преобразование параллельного кода с шины 7 данных в последовательный и выдачу его в линию 14 связи, а также выдачу на выход устройства сигналов запроса прерывания рабочей программы процессора ЦВМ (ЗПР) для инициирования обмена информацией с шины 7 данных. Обмен информацией между шиной 7 адреса-данных и адресуемыми регистрами блоков 8, 9, 10 устройства выполняется по сигналам, вырабатываемым блоком 3 интерфейса при поступлении на входы устройства управляющих сигналов Синхронизация обмена SYN Выбор устройства

SF, признак Запись-байт WR-BY, Запись данных WR, Чтение данных RD (см. ГОСТ 26.765.51-86). В начале каждого цикла обмена на шину 7 адреса-данных устройства поступает код адреса регистра, затем

0 данные. В каждом цикле обмена адресный селектор 26 блока 3 интерфейса считывает код адреса с шины 7 адреса-данных.

Если поступающий адрес - разряды AD09-AD12 (совпадает с кодом адреса уст5 ройства, установленным на шине 25 блока 3 интерфейса, то единичный сигнал с выхода блока 24 сравнений записывается в D-триг- гер 27 адресного селектора 26. Выходной сигнал D-триггерз 27 разрешает работу де0 шифратора адресного селектора (элементы И-НЕ 29), анализирующего записанные по сигналу Обмен в D-триггеры адресного селектора 26 значения разрядов AD07, AD08 адреса, определяющих обращение к одному

5 из блоков 8, 9, 10 устройство. Выбор адресуемого регистра внутри выбранного блока 8 (9, 10) устройства осуществляется дешифрацией разрядов адреса AD01-AD05 с помощью внутреннего дешифратора 151

0 адресов, который имеется в составе блоков 8, 9, 10 устройства.

На выходах - третьем, четвертом или пятом блока 3 интерфейса появляется сигнал выборки, инициирующий выполнение

5 операции обмена с выбранным блоком (8, 9, 10)устройства.

На первом и втором выходах Запись (ЗП) и Чтение (ЧТ) блока 3 интерфейса формируется соответствующие сигналы.

0На выходе элемента ИЛИ 2 блока 3 интерфейса формируется сигнал Ответ (AN) устройства.

В процессе работы устройства могут формироваться сигналы прерывания рабо5 чей программы ЦВМ. Сигналы прерывания информируют процессор ЦВМ о необходимости считывания буфера 152 блока 8 приема или загрузка буфера 152 блока 9 передачи. Режим работы блока 8 приема,

0 блока 9 передачи и блока 10 формирования сигналов прерывания задается программно, посредством записи от процессора ЦВМ через шину 7 адреса-данных кода настройки в регистры 150 программного управления

5 этих блоков. Блок 8 приема программируется на ввод в процессор ЦВМ последовательной информации, блок 9 передачи программируется на вывод последовательной информации, а блок 10 формирования сигналов прерывания программируется на

прием сигналов прерывания, поступающих на первый и второй информационные входы периферийной шины блока 10, их обработку и выполнение всех необходимых по интерфейсу процессора ЦВМ процедур прерывания. Использование в блоках 8 приема и блока 9 передачи буферных регистров 152 предоставляет для реакции на запрос прерывания устройства в распоряжение процессора ЦВМ временной интервал передачи (приема) байта.

Для осуществления обмена информацией между регистром сдвига 165 и буферным регистром 152 в блоке 8 приема и блока 9 передачи используются сигналы с второго и первого выходов блока 5 управления, где осуществляется подсчет числа сдвигов в регистрах сдвига 165 блока 8 приема и блока 9 передачи.

Эти же сигналы поступают на первый и второй информационные входы периферийной шины блока 10 для формирования сигнала запроса прерывания рабочей программы процессора ЦВМ (ЗПР).

Запись информации в буферный регистр 152 блока 9 передачи или чтение информации из буферного регистра 152 блока 8 приема выполняется по сигналу ЗПР, формируемому на третьем выходе блока 10 формирования сигналов прерывания при поступлении сигналов в регистр прерывания 156 блока 10 с первого и второго информационных входов периферийной шины блока 10, которая постоянно открыта для записи в регистр прерывания 156 активным сигналом (низкого уровня) на входе строби- рования этой шины (на фиг.1 не показан).

Передача информации в линию связи (например, на манипуляционный вход приемопередатчика) осуществляется при появлении на седьмом выходе блока 5 управления признака передача, который разрешает сдвиг в регистре 165 сдвига блока 9 передачи.

Загрузка информационных слов в буфер 152 блока передачи 9 производится по сигналу 3 ПР (см. поз. 132, 133, 137 фиг.8) на выходе блока 10, формируемому при поступлении на второй информационный вход периферийной шины блока 10 сигнала с шестого выхода блока 5 управления (если соответствующие разряды регистра 156 прерывания блока 10 не замаскированы записью соответствующего кода 8 регистр 152 маски блока 10).

Конкретная причина прерывания определяется при считывании регистра 156 прерывания блока ТО (например, необходимость чтения параллельного буфера 152 блока 8 приема при вводе информации, или

необходимость очередной загрузки буфера блока 9 передачи при выводе последовательного кода в линию связи).

При чтении регистра прерывания 156 5 производится сброс этого регистра с целью подготовки к приему следующего сигнала прерывания.

Загрузка первого передаваемого слова в буфер блока 9 передачи производится по

0 сигналу ЗПР на выходе блока 10, формируемому при поступлении на второй информационный вход периферийной шины блока 10 сигнала с шестого выхода блока 5 управления, упреждающего начало передачи эле5 ментов кода в канал связи.

Перезапись первого передаваемого слова из буфера 162 в регистр 165 сдвига блока 9 передачи осуществляется при поступлении следующего сигнала (соответст0 вующего началу передачи) с шестого выхода блока 5 управления в блок 9 передачи.

Этот же сигнал поступает в регистр прерывания блока 10, на третьем выходе которого формируется сигнал ЗПР, по

5 которому в течение временного интервала передачи байта должна быть произведена загрузка очередного слова в буферный регистр f 52 блока 9 передачи.

После окончания передачи первого бай0 та выходным сигналом дешифратора 124 через элемент ИЛИ 112 блока 5 управления осуществляется перезапись информации из буфера 152 в регистр сдвига 165 блока 9 передачи, после чего на третьем выходе бло5 ка 10 формируется сигнал ЗПР, означающий необходимость загрузки в буферный регистр блока 9 передачи следующего передаваемого слова.

Конкретная причина прерывания опре0 деляется при считывании регистра прерывания 156 блока 10.

Информация при приеме поступает из линии 13 связи (например, с выхода радиоприемного устройства) на первый вход бло5 ка 4 тактовой синхронизации, с выхода интегратора 39 которого сигнал поступает на информационный вход (Последовательная информация IS) блока 8 приема.

По сигналу с четвертого выхода блока 5

0 управления через элемент ИЛИ-НЕ 2 после приема байта информация из регистра сдвига 165 переписывается в буфер 152 блока 8 приема, а в регистр прерывания 156 блока 10 формирования сигналов прерыва5 ния поступает сигнал прерывания, после чего на третьем выходе блока 10 формируется сигнал ЗПР.

После чтения вектора прерывания, который записывается программно в регистр 161 вектора блока 149 формирования сигнало в прерывания, для определения конкретной причины прерывания процессор ЦВМ

/ггывает регистр 156 прерывания блока 1Q, после чего осуществляется считывание

раллельного кода на шину 7 из буфера 152 б/|ока 8 приема.

Прием информации из линии связи тракта приема ведется в течение всего врени, пока с пятого выхода блока 5 управлем

HI

последовательной информации (EIS) блока

8 приема поступает признак Прием, означ{ ющий разрешение сдвига в регистре

сдвига 165 блока 8 приема,

Для обеспечения считывания состояния

тройства (прием-передача) информация о состоянии устройства с пятого и седьмого в иходов блока 5 управления заводится на

эрвый и второй информационный входы

я на шестой вход Управление вводом

п

зриферийной шины блока 9 передачи, ко- 20

зрая доступна для чтения через коммута- трр 1582 блока 9 передачи со стороны ц ины 7 данных в любое время, и выполняет

жим образом роль регистра слова состоян

ля.

Для повышения достоверности разли- ния детерминированного цифрового сиг- Нала и случайного шума при перерывах в радиоканале, длительность которых мо- |сет составлять десятки циклов работы стройства в последовательном канале, в редлагаемом устройстве используется ди- криминатор 12 сигнал-шум. Его выходным игналом низкого уровня в случае перерыва вязи с помощью элемента И-НЕ 2 осуще- телятся блокировка сигнала на четвертом ыходе блока 5 управления, т.е. при переры- е связи в радиоканале прекращается формирование сигналов переписи информации is регистра сдвига 165 блока 8 приема в уферный регистр 152 этого блока, а также (локируется формирование сигнала ЗПР на ыходе блока 10. При этом чтение соответ- твующего буфера на шину 7 не производит- п, а в стробированные интервалы приема нформации, определяемые сигналом на ервом, пятом выходах блока 5 управления, е производится обмен регистра сдвига лока 8 приема с соответствующим буфер- ым регистром.

Следовательно, в предлагаемом устрой- тве информация считывается на шину 7 олько при наличии в радиоканале детерминированного цифрового сигнала, что повышает достоверность приема информации. Учитывая, что чтение на шину 7 буферного регистра блока 8 приема производится по концу приема очередного байта информации (т.е. по заполнении регистра сдвига блока приема) то для предотвращения потери

5

0

0

5

5

0 5 0 5 0

5

информации при восстановлении связи после перерыва в радиоканале время задержки появления выходного сигнала высокого уровня дискриминатора 12 сигнал-шум (по отношению к моменту появления детерминированного цифрового сигнала в радиоканале) не должно превышать времени приема байта в регистр сдвига блока 8 приема (что при скорости 300 бод составляет 25 мс и является вполне достаточным с точки зрения времени задержки выходного сигнала дискриминатора 13 сигнал-шум).

В предлагаемом устройстве для повышения достоверности приема информации в радиоканале разрешение подстройки фазы регулируемых тактовых импульсов в блоке 4 тактовой синхронизации осуществляется выходным сигналом с элемента И 18 формирователя 1.

Подстройка фазы тактовых импульсов для уменьшения вероятности сбоя тактовой синхронизации при длительных перерывах связи и в радиоканале осуществляется только в стробированных интервалах приема информации, определяемых выходным сигналом блока 5 управления при наличии сигнала высокого уровня на выходе дискриминатора 12 сигнал-шум. В случае перерыва связи в радиоканале сигнал низкого уровня, поступающий с выхода элемента ИЛИ 17 формирователя 1 на входы элементов И 68, 69 умножителя 35 блока 4 тактовой синхронизации блокирует прохождение сигналов с выходов умножителя 35 на входы усредняющего счетчика 36.

Для предотвращения блокировки подстройки фазы тактовых импульсов в момент восстановления связи после перерыва, связанной с задержкой выходного сигнала дискриминатора 12 сигнал-шум, в начале интервале приема в каждом цикле работы устройства в последовательном канале с помощью триггера 16 формирователя 1, который выходным сигналом с блока 5 управления, совпадающим с началом приема информации, устанавливается в единичное состояние, на выходе офрмиро- вателя 1 формируется единичный сигнал, разрешающий подстройку фазы тактовых импульсов в течение времени приема одного слова, т.к. по сигналу Конец слова из блока 5 управления с помощью элемента И Л И 15 формирователя 1 триггер 1 б сбрасывается в ноль в конце поступления первого слова. Если в канале связи нет перерыва, то к моменту завершения приема первого слова на выходе дискриминатора 12 сигнал-шум появится единичный сигнал, разрешающий формирование на выходе И 18 формирователя 1 управляющего сигнала

разрешения подстройки фазы тактовых импульсов в.течение стробированного интервала приема. А в случае пропадания детерминироанного цифрового сигнала в предлагаемом устройстве прекращается подстройка фазы тактовых импульсов и в стробироеанных интервалах приема информации, так как установленное в интервале приема информации значение фазы тактовых импульсов более достоверно, чем то, которое было бы получено в результате продолжавшейся во время перерыва связи подстройки фазы тактовых импульсов.

Поэтому с момента восстановления сигнала в канале связи в предлагаемом устройстве при работе в радиоканале со значительными перерывами может быть обеспечен нормальный прием сигналов. Таким образом, обеспечивается предоетв- ращение сбоя синхронизации при значительных перерывах в радиоканале, что существенно повышает достоверность приема информации. Таким образом, предлагаемое устройство позволяет обеспечить достоверный прием информации при работе в радиоканале и значительных перерывах связи, т.е. обеспечить асинхронный режим работы в радиоканале.

Сравнение предлагаемого устройства с прототипом показывает следующее.

Известное устройство обеспечивает достоверный прием информации в асинхронном режиме только в проводном канале связи, т.е. при использовании его в радиоканале известное устройство не позволяет точно различить детерминированный цифровой сигнал и случайный шум в канале связи, что сужает область применения известного устройства.

В предлагаемом устройстве при пропадании детерминированного цифрового сигнала в радиоканале блокируются прием информации, а также прекращается подстройка фазы тактовых импульсов, т.к. установленное в интервале приема информации значение фазы тактовых импульсов более достоверно, чем то, которое было бы получено в результате продолжавшейся во время перерыва связи подстройки фазы тактовых импульсов. Поэтому с момента восстановления сигнала в радиоканале в предлагаемом устройстве при работе со значительными перерывами может быть обеспечен нормальный прием сигналов.

Таким образом, обеспечивается предотвращения сбоя синхронизации при значительных перерывах в канале связи, которые могут составлять десятки циклов, и приема на шину данных ЦВМ недостоверной информации, что существенно повышает достоверность приема информации. .

Таким образом, техническое решение позволяет обеспечить достоверный ввод по- 5 следовательной информации при работе в радиоканале со значительными перерывами связи, что обеспечивает расширение области применения предлагаемого устройства. Предлагаемое устройство по0 строено с использованием универсальных схемотехнических решений и элементов, что позволяет реализовать его на унифицированных модулях, упростить технологию его изготовления и регулировки.

5

Формула изобретения 1. Устройство для сопряжения цифровой вычислительной машины с каналом связи, содержащее блок интерфейса, блок

0 приема, блок передачи, блок формирования сигналов прерывания и блок управления, информационные входы-выходы первой группы блока интерфейса являются входами-выходами адреса данных устройства,

5 первый, второй, третий, четвертый и пятый входы блока интерфейса являются соответствующими входами устройства, первый и второй выходы блока интерфейса соединены соответственно с входами Запись и

0 Чтение блока приема, блока передачи и блока формирования сигналов прерывания, третий, четвертый и пятый выходы блока интерфейса соединены соответственно с третьими входами блока приема, блока пе5 редачи и блока формирования сигналов прерывания, вход Сброс устройства соединен с выходами сброса блока приема, блока передачи, блока формирования сигналов прерывания и блока управления, ин0 формационные входы-выходы второй группы блока интерфейса соединены соответственно с входами-выходами адреса данных блока приёма, блока передачи и блока формирования сигналов прерывания,

5 первые выходы которых соединены соответственно с шестым, седьмым и восьмым входами блока интерфейса, шестой выход которого соединен с четвертыми входами блока приема, блока передачи и блока фор0 мирования сигналов прерывания, пятый вход и второй выход которого являются соответственно шестым входом и первым входом устройства, второй выход которого соединен с третьим выходом блока форми5 рования сигналов прерывания, седьмой выход блока интерфейса является третьим выходом устройства, выход Последовательная информация блока передачи соединен с линией связи тракта передачи, отличающееся тем, что, с целью

расширения области применения устройства путем обеспечения достоверного ввода последовательной информации в радиоканале, в него введены блок тактовой синхронизации, формирователь, дискриминатор сигнал-шум и элемент И-НЕ, первый вход котор ого соединен с выходом дискриминатора 1 :игнал-шум и с первым входом форми- poeai еля, второй, третий и четвертый входы которого соединены соответственно с пер- вым, вторым и третьим выходами блока упрапления, четвертый выход которого со- единзн с вторым входом элемента И-НЕ, выход которого соединен с первым информационным входом периферийной шины блок; формирования сигналов прерывания и с пятым входом блока приема, шестой вход которого соединен с пятым выходом блокл управления, шестой выход которого соединен с вторым информационным вхо- дом г ериферийной шины блока формирования сигналов прерывания и с пятым входом блок, i передачи, шестой выход которого соединен с седьмым выходом блока управления, первый вход которого соединен с первым выходом блока тактовой синхро- низа им, второй выход которого соединен с вторым входом блока управления, с первым входом дискриминатора сигнал-шум и седьмым входом блока приема, третий вы- ход (тока тактовой синхронизации соединен с седьмым входом блока передачи, перв й вход блока тактовой синхронизации

соединен с линией связи связи тракта приема, выход формирователя соединен с вторым входом блока тактовой синхронизации, вход Последовательная информация блока приема соединен с четвертым выходом блока тактовой синхронизации, пятый и шестой выходы которого соединены соответст- венно с вторым и третьим входами дискриминатора сигнал-шум, вход сброса которого соединен с входами сброса формирователя, блока тактовой синхронизации и входом Сброс устройства, выходы группы выходов блока тактовой синхронизации соединены соответственно с входами группы входов блока управления, пятый и седьмой выходы блока управления соединены соответственно с первым и вторым информационными входами периферийной шины блока передачи.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что формирователь содержит последовательно соединенные первый элемент ИЛИ, триггери второй элемент ИЛИ, второй вход которого соединен с выходом элемента И. входы которого являются первым и вторым входами формирователя, третьим и четвертым входами которого являются соответственно первый вход элемента ИЛИ и вход установки единицы триггера, второй вход первого элемента ИЛИ является входом сброса формирователя, выходом которого является второй выход второго элемента ИЛИ.

Вканал с8яы

WP

Фиг

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

87-t

6

Kb

19

-OZDжчЈ1

25, L2

т

E

ik

26

МиЬЖ

10

АШ

к 7

/9

АЯ07

ЛШ.Л5

пЛм

v/ft

-cd

A300

21

OmQem

7 A

Вн

4m

№n

I

i

I

C5.J

ППППППППППППП

фвг.5

е

I I I I I I 11 I л /

/ / v ,

him it i и mi in tun I

fff7

.ля l J+LtJLJJ r ff / rrl г r-7 f / I A

ft jnnln

ПГП . f

/ / v ,

Г

tJLJJ r ff r-7 f / I A

fit/e. 6

t

фиа7

pv&9

т 12

ПРР/1/Синхр. од меня 551

6 Фиг.Ю

т

ffmfSt

fSStW ZF

0mf5t

Omf48 A

Сброс

ffrnM

AW

%

т

(Pue.ff

Фиг. ft

0/7ff54

IS Ј1S

qtotti 6

ЛРРЛ ЯРМ JflP-OxMV. Ct/MpffM 05

3

178

№

t

/04-W

т

19

Врщ.

(pve.fS

fpfrfSff

12

т

йя

i/wr

WL

F

.J

jn jTrnjinjiJTnmifuiJL

a$

6

т г i i и i i in in им i inn in Tt т i i i iii I I ii i i i i i i i /ям i ii ii ii i i ii i l i i I i ,t

197 П П П П П П П П П П П П Л Л П П П ./

т ппппппггппппп.пппппп t

199I I I I I I I I I t

т i i i 11 in ii 11 i и 11 л

w Ii

.Фиг.16

Авторы

Даты

1993-08-30—Публикация

1991-01-14—Подача