Изобретение относится к автоматике и вычислительной технике.

Цель изобретения - повьшение достоверности, а также расширение функ- циойальных возможностей за счет воз- 5 можности суммирования входных переменных .

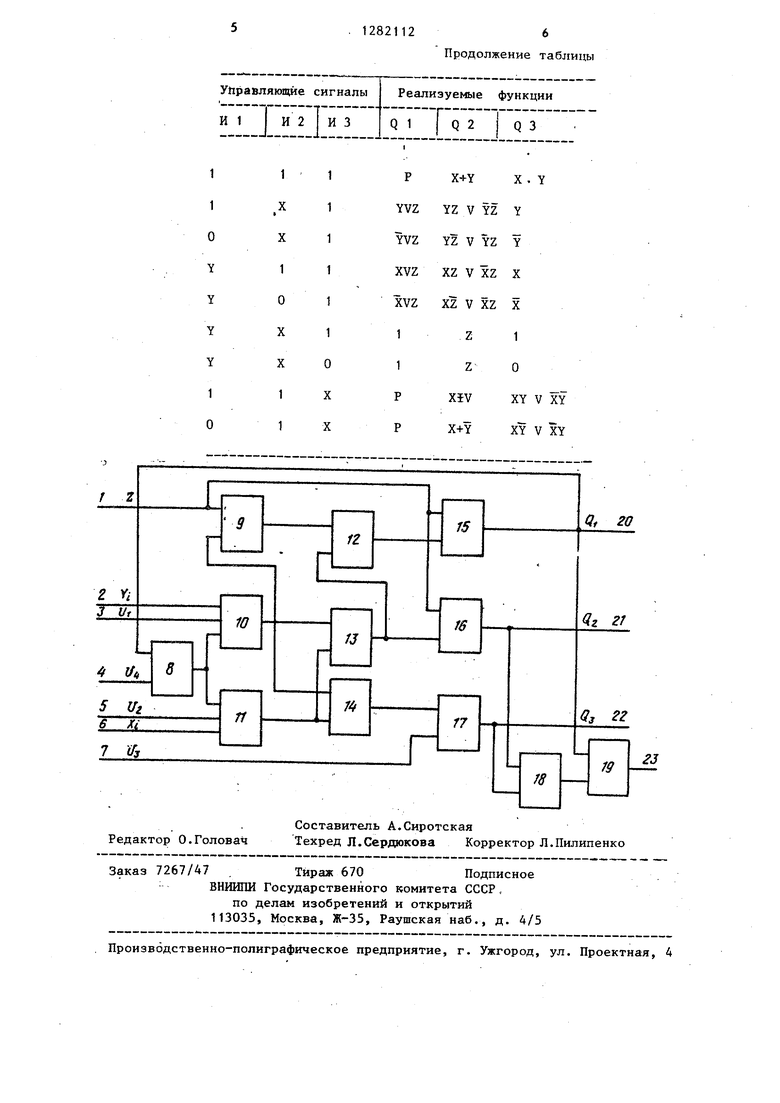

На чертеже представлена функциональная схема модуля.

Модуль содержит настроечный вход JO 1, информационный вход 2, настроечные входы 3-5, информационный вход 6, настроечный вход 7, элемент И-НЕ

8, элемент НЕРАВНОЗНАЧНОСТЬ 9, сумма- l iМоторы 10 и 11 по модулю два, элемент де 21 и выходе 20 - сигналы суммы и И 12, элемент РАВНОЗНАЧНОСТЬ 13,элеми сигналами И 1 и. И 2, которые могут принимать значения О или 1. Если на настроечные входы 3, 5 и 7 в качестве управляющих сигналов подать информационные сигналы иХ,то модуль дополнительно реализует на выходах 20, 21, 22 ряд логических . функций.

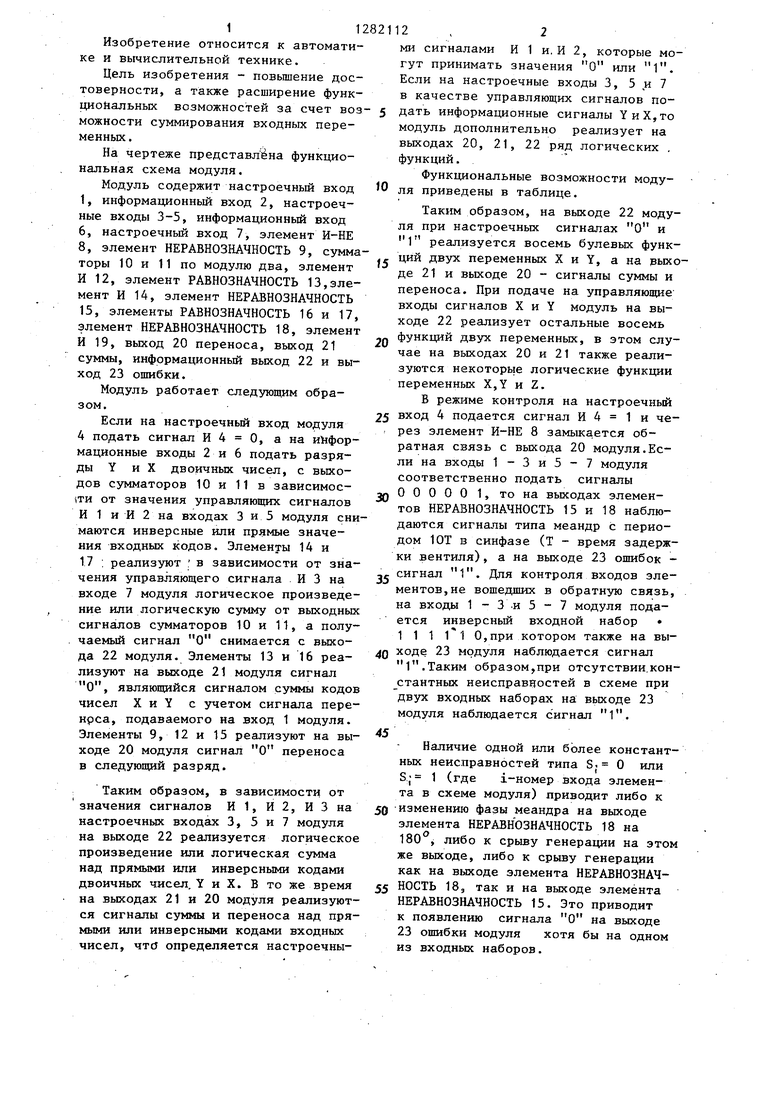

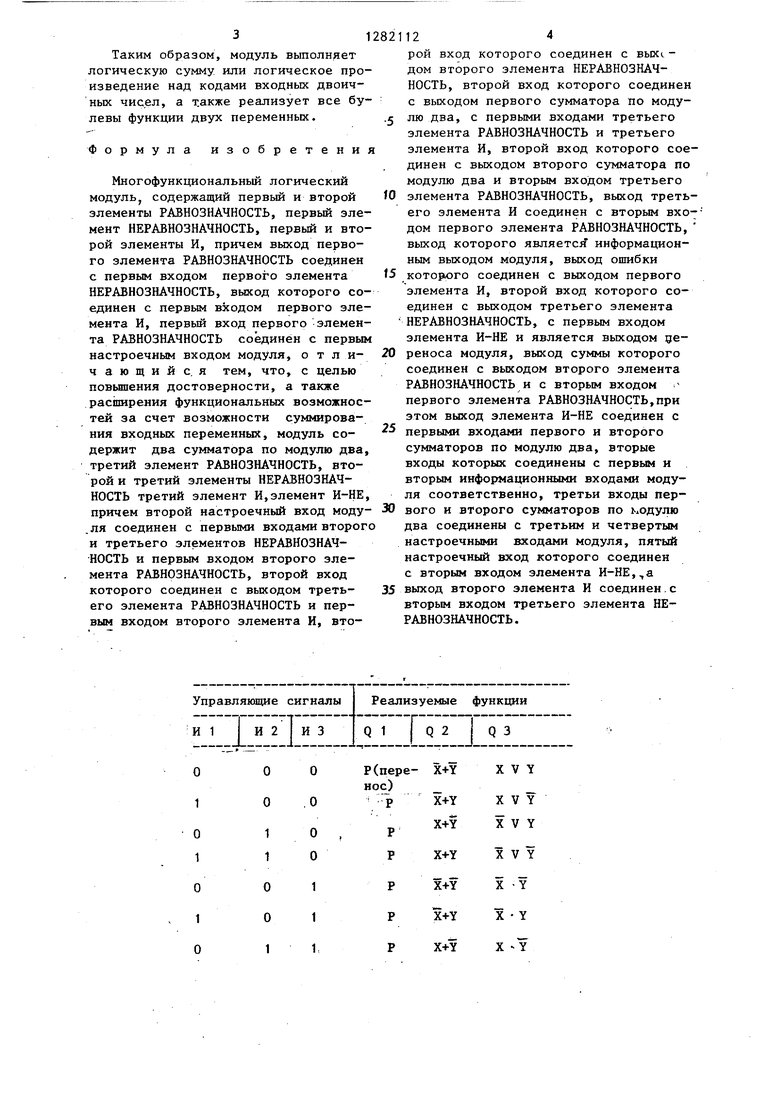

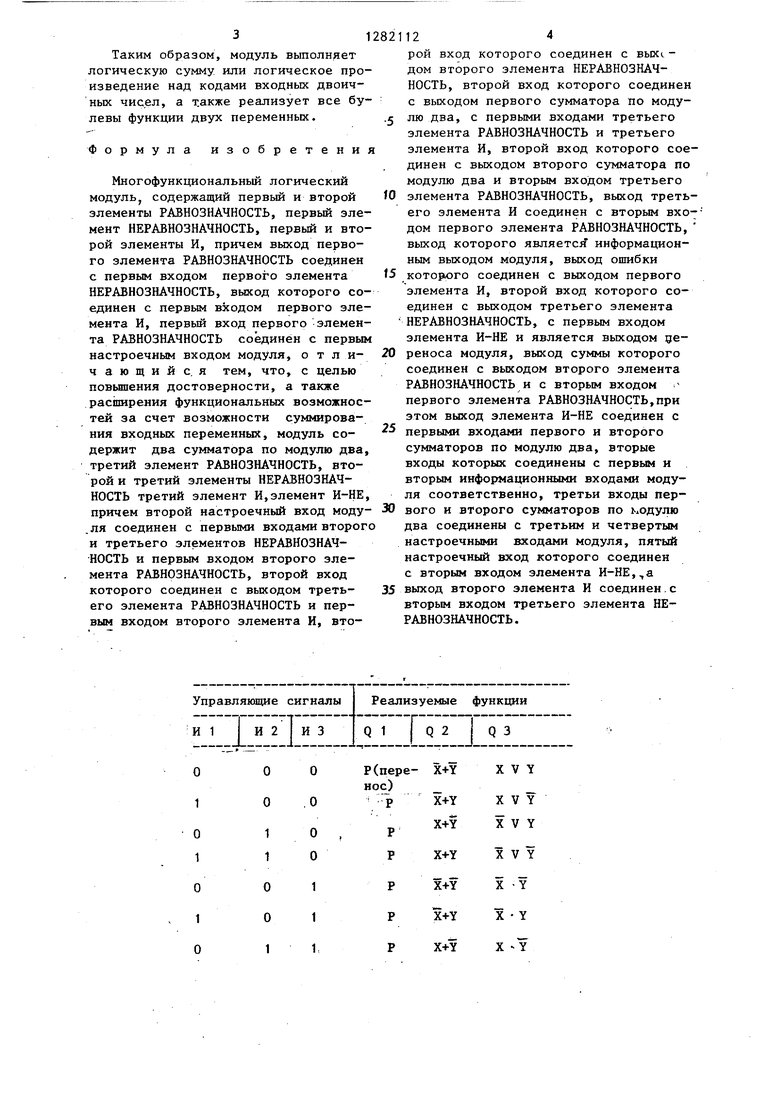

Функциональные возможности модуля приведены в таблице.

Таким образом, на выходе 22 модуля при настроечных сигналах О и 1 реализуется восемь булевых функмент И 14, элемент НЕРАВНОЗНАЧНОСТЬ 15, элементы РАВНОЗНАЧНОСТЬ 16 и 17, элемент НЕРАВНОЗНАЧНОСТЬ 18, элемент И 19, выход 20 переноса, выход 21 суммы, информационный выход 22 и выход 23 ошибки.

Модуль работает следующим образом.

Если на настроечный вход модуля 4 подать сигнал И 4 О, а на информационные входы 2 и 6 подать разряды Y и X двоичных чисел, с выходов сумматоров 10 и 11 в зависимос- (ти от значения управляющих сигналов И 1 и И 2 на входах 3 и 5 модуля снимаются инверсные или прямые значения входных кодов. Элементы 14 и 17 ; реализуют : в зависимости от значения управляющего сигнала И 3 на входе 7 модуля логическое произведение или логическую сумму от выходных сигнашов сумматоров 10 и 11, а получаемый сигнал о снимается с выхода 22 модуля. Элементы 13 и 16 реализуют на выходе 21 модуля сигнал О, являющийся сигналом суммы кодов чисел X и Y с учетом сигнала пере- нрса, подаваемого на вход 1 модуля. Элементы 9, 12 и 15 реализуют на выходе 20 модуля сигнал О переноса в следующий разряд.

Таким образом, в зависимости от значения сигналов И 1, И 2, ИЗ на настроечных входах 3, 5 и 7 модуля на выходе 22 реализуется логическое произведение или логическая сумма над прямыми или инверсными кодами двоичных чисел. Y и X. В то же время на выходах 21 и 20 модуля реализуются сигналы суммы и переноса над прямыми или инверсными кодами входных чисел, что определяется настроечныде /I и выходе Zu - сигналы суммы переноса. При подаче на управляющие входы сигналов X и Y модуль на выходе 22 реализует остальные восемь

2Q функций двух переменных, в этом случае на выходах 20 и 21 также реализуются некоторые логические функции переменных X,Y и Z.

В режиме контроля на настроечный

25 вход 4 подается сигнал И 4 1 и че- : рез элемент И-НЕ 8 замыка.ется обратная связь с выхода 20 модуля.Если на входы 1 - 3 и 5 - 7 модуля соответственно подать сигналы 00000 1, то на выходах элементов НЕРАВНОЗНАЧНОСТЬ 15 и 18 наблюдаются сигналы типа меандр с периодом ЮТ в синфазе (Т - время задержки вентиля), а на выходе 23 ошибок 30

35

сигнал 1. Для контроля входов элементов, не вошедших в обратную связь, на входы 1 - 3 .и 5 - 7 модуля подается инверсный входной набор 1 1 1 l l О,при котором также на вы- 40 ходе 23 модуля наблюдается сигнал 1.Таким образом,при отсутствии.константных неисправностей в схеме при двух входных наборах на выходе 23 модуля наблюдается сигнал 1.

45

Наличие одной или более константных неисправностей типа S. О или S| 1 (где i-номер входа элемента в схеме модуля) приводит либо к

50 изменению фазы меандра на выходе элемента НЕРАВНОЗНАЧНОСТЬ 18 на 180 , либо к срыву генерации на этом же выходе, либо к срыву генерации как на выходе элемента НЕРАВНОЗНАЧ55 НОСТЬ 18, так и на выходе элемента НЕРАВНОЗНАЧНОСТЬ 15. Это приводит к появлению сигнала О на выходе 23 ошибки модуля хотя бы на одном из входных наборов.

l iМоде 21 и выходе 20 - сигналы суммы и

ми сигналами И 1 и. И 2, которые могут принимать значения О или 1. Если на настроечные входы 3, 5 и 7 в качестве управляющих сигналов подать информационные сигналы иХ,то модуль дополнительно реализует на выходах 20, 21, 22 ряд логических . функций.

Функциональные возможности модуля приведены в таблице.

Таким образом, на выходе 22 модуля при настроечных сигналах О и 1 реализуется восемь булевых функ l iМоде 21 и выходе 20 - сигналы суммы и

де /I и выходе Zu - сигналы суммы переноса. При подаче на управляющие входы сигналов X и Y модуль на выходе 22 реализует остальные восемь

функций двух переменных, в этом случае на выходах 20 и 21 также реализуются некоторые логические функции переменных X,Y и Z.

В режиме контроля на настроечный

вход 4 подается сигнал И 4 1 и че- рез элемент И-НЕ 8 замыка.ется обратная связь с выхода 20 модуля.Если на входы 1 - 3 и 5 - 7 модуля соответственно подать сигналы 00000 1, то на выходах элементов НЕРАВНОЗНАЧНОСТЬ 15 и 18 наблюдаются сигналы типа меандр с периодом ЮТ в синфазе (Т - время задержки вентиля), а на выходе 23 ошибок

35

сигнал 1. Для контроля входов элементов, не вошедших в обратную связь, на входы 1 - 3 .и 5 - 7 модуля подается инверсный входной набор 1 1 1 l l О,при котором также на вы- 40 ходе 23 модуля наблюдается сигнал 1.Таким образом,при отсутствии.константных неисправностей в схеме при двух входных наборах на выходе 23 модуля наблюдается сигнал 1.

45

Наличие одной или более константных неисправностей типа S. О или S| 1 (где i-номер входа элемента в схеме модуля) приводит либо к

50 изменению фазы меандра на выходе элемента НЕРАВНОЗНАЧНОСТЬ 18 на 180 , либо к срыву генерации на это же выходе, либо к срыву генерации как на выходе элемента НЕРАВНОЗНАЧ55 НОСТЬ 18, так и на выходе элемента НЕРАВНОЗНАЧНОСТЬ 15. Это приводит к появлению сигнала О на выходе 23 ошибки модуля хотя бы на одном из входных наборов.

31282

Таким образом, модуль выполняет логическую сумму или логическое произведение над кодами входных двоичных чисел, а т.акже реализует все булевы функции двух переменных.

5

Формула изобретения

Многофункциональный логический модуль, содержащий первый и второй элементы РАВНОЗНАЧНОСТЬ, первый элемент НЕРАВНОЗНАЧНОСТЬ, первый и второй элементы И, причем выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом первого элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом первого элемента И, первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым настроечным входом модуля, о т л и- чающийс. я тем, что, с целью повьяпения достоверности, а также расширения функциональных возможностей за счет возможности суммирования входных переменных, модуль содержит два сумматора по модулю два, третий элемент РАВНОЗНАЧНОСТЬ, второй и третий элементы НЕРАВНОЗНАЧНОСТЬ третий элемент И,элемент И-НЕ, причем второй настроечный вход моду- .ля соединен с первыми входами второг и третьего элементов НЕРАВНОЗНАЧ- НОСТЬ и первым входом второго элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом треть- его элемента РАВНОЗНАЧНОСТЬ и первым входом второго элемента И, вто

Управляющие сигналы

и1 И2ИЗ Q1 Q2 |дз

О

о

1 1

о о 1

о о

о о

1 1 1,

5

5

О 0 5

0

5

1124

рой вход которого соединен с выхс- дом вгорого элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом первого сумматора по модулю два, с первыми входами третьего элемента РАВНОЗНАЧНОСТЬ и третьего элемента И, второй вход которого соединен с выходом второго сумматора по модулю два и вторым входом третьего элемента РАВНОЗНАЧНОСТЬ, выход третьего элемента И соединен с вторым входом первого элемента РАВНОЗНАЧНОСТЬ, выход которого являете информационным выходом модуля, выход ошибки которого соединен с выходом первого элемента И, второй вход которого соединен с выходом третьего элемента

НЕРАВНОЗНАЧНОСТЬ, с первым входом элемента И-НЕ и является выходом де- реноса модуля, выход суммы которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ и с вторым входом первого элемента РАВНОЗНАЧНОСТЬ,при этом выход элемента И-НЕ соединен с первыми входами первого и второго сумматоров по модулю два, вторые входы которых соединены с первым и вторым информационными входами модуля соответственно, третьи входы первого и второго сумматоров по кодулю два соединены с третьим и четвертым настроечными входами модуля, пятый настроечный вход которого соединен с вторым входом элемента И-НЕ,,а выход второго элемента И соединен.с вторым входом третьего элемента НЕРАВНОЗНАЧНОСТЬ.

Реализуемые функции

е

X+Y

X+Y X+Y

X+Y X+Y X+Y X+Y

X V Y

X V Y X V Y

X V Y X -Y X Y

X -Y

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1320808A1 |

| Многофункциональный логический элемент | 1985 |

|

SU1251066A1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Многофункциональный логический модуль | 1986 |

|

SU1310800A1 |

| Многофункциональный логический модуль | 1986 |

|

SU1348816A1 |

| Универсальный логический модуль | 1985 |

|

SU1260939A1 |

| Многофункциональный логический модуль | 1986 |

|

SU1368872A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1765821A1 |

| Тестопригодное логическое устройство | 1986 |

|

SU1451695A1 |

| Многофункциональный модуль | 1978 |

|

SU700864A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повышение достоверности, а также расширение функциональных возможностей за счет возможности суммирования входных переменных. Модуль содержит три элемента НЕРАВНОЗНАЧНОСТЬ, два сумматора по модулю два, три элемента И, элемент И-НЕ, три элемента РАВНОЗНАЧНОСТЬ. Модуль работает в зависимости от сигналов настройки как сумматор, формируя сигналы переноса, а также как универсальный логический модуль, реализующий все булевы функции двух переменных. 1 ил. « (Л с ND 00

| Логический модуль | 1978 |

|

SU798806A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1083180A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1985-07-01—Подача