(54) МНОГОФУНКЦИОНАЛЬНЫЙ МОДУЛЬ

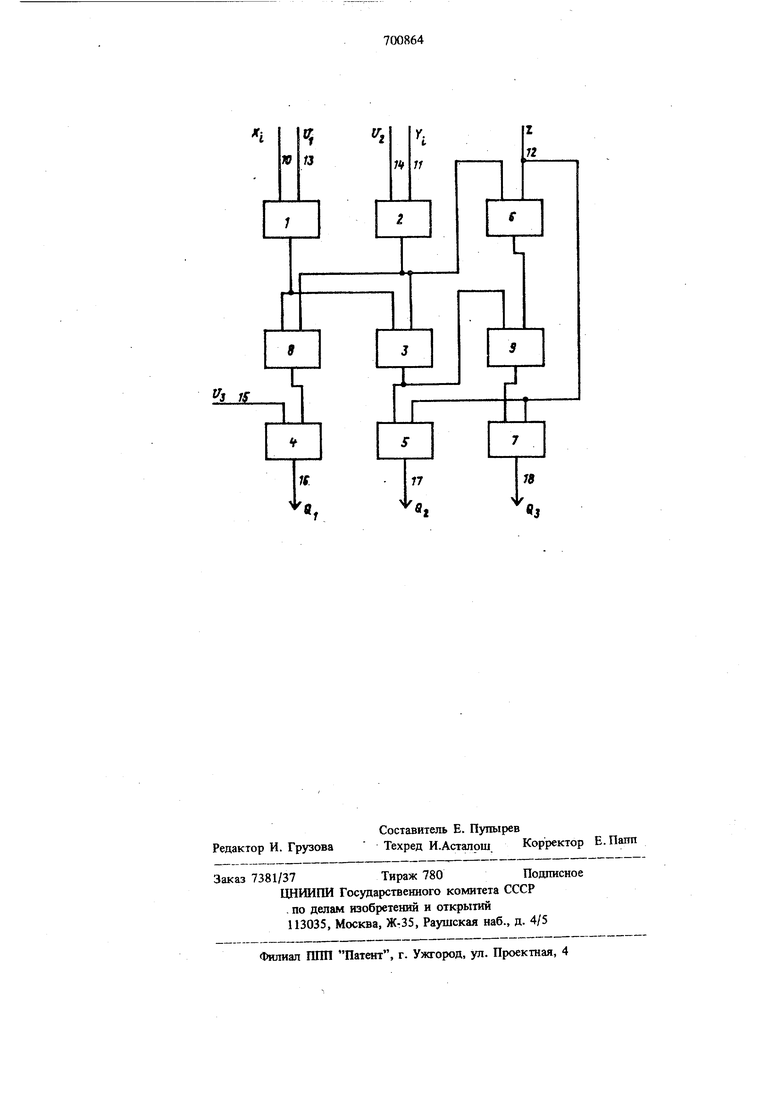

На информационные входы 10 и 11 модуля подаются разряды X и Y двоичных чисел, с выходов элементов 1 и 2, в зависимости от значения управляющих сигналов Ui и U на входах 13 и 14 модуля, снимаются прямые или инверсные значения входных кодов. Элементы 4 и 8 реализуют в зависимости от значения управляющего сигнала УЗ на входе 15 модуля логическое произведение или логическую сумму от выходных сигналов элементов 1 и 2, а получаемый сигнал О снимается с выхода 16 модуля. Элементы 3 и 5 реализуют на выходе 17 модуля сигнал О, являющийся сигналом суммы кодов чисел X и Y с учетом сигнала переноса, подаваемого на вход 12 модуля. Логические элементы 6,7 и 9 реализуют на выходе 18 модуля сигнал О переноса в следующий разряд.

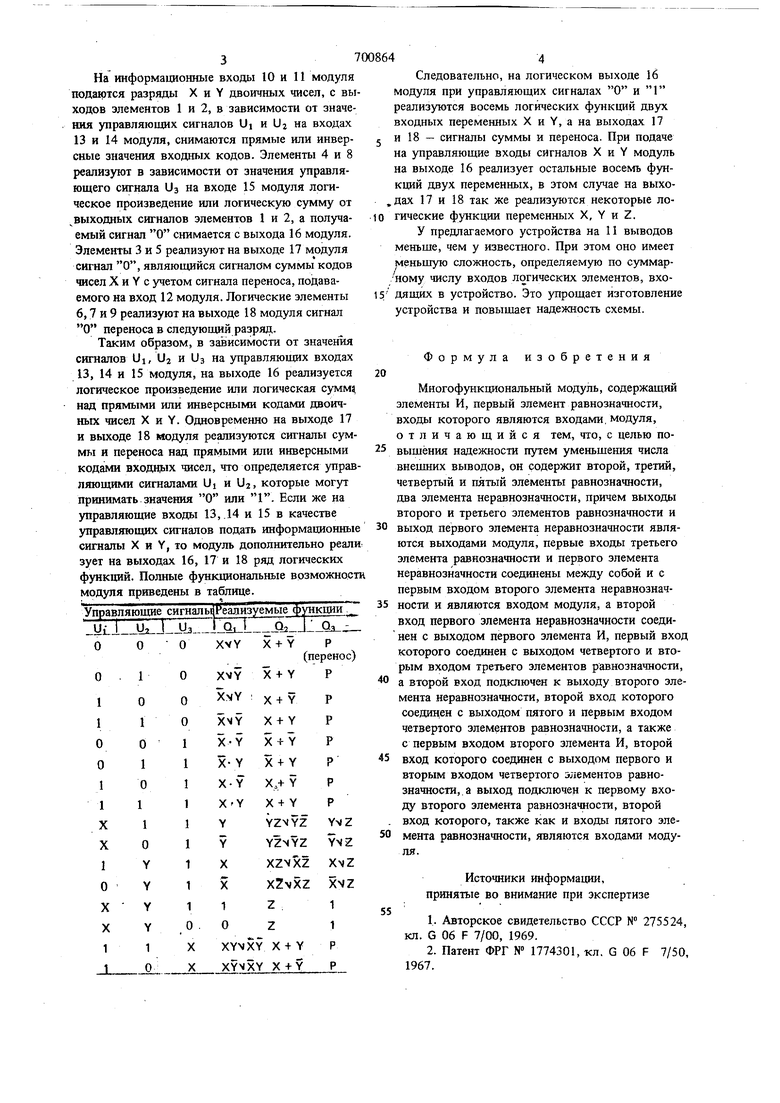

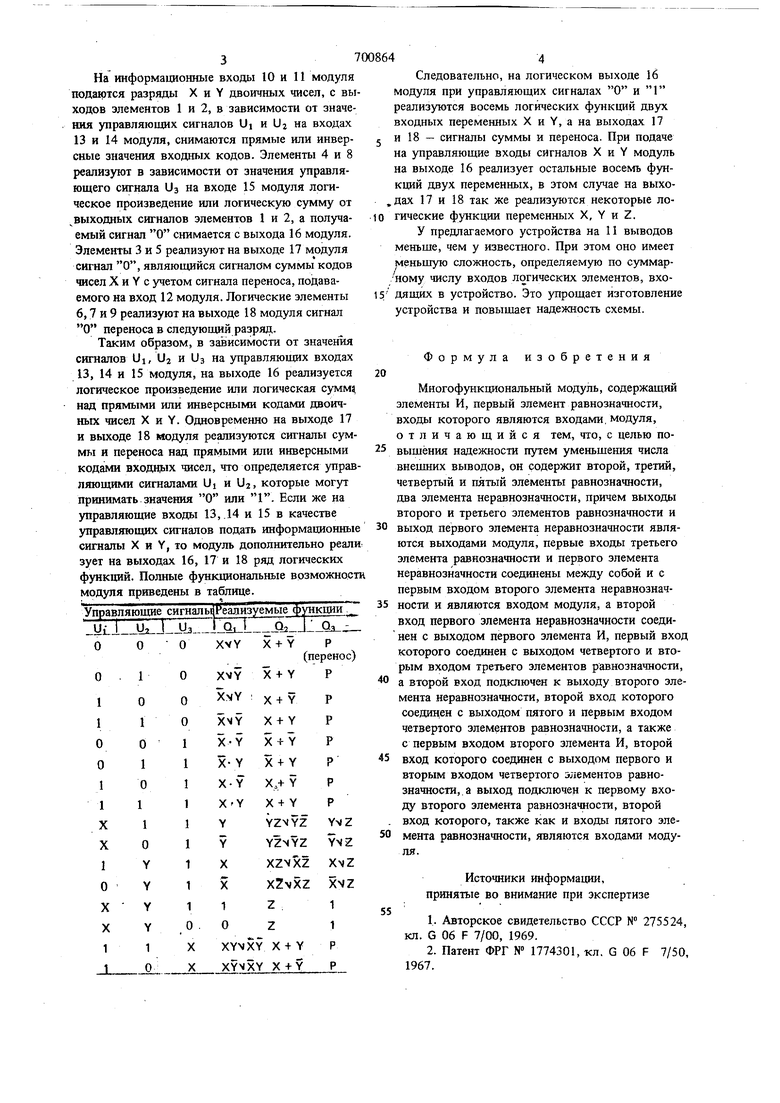

Таким образом, в зависимости от значения сигналов Ui, Ua и Us на управляющих входах 13, 14 и 15 модуля, на выходе 16 реализуется логическое произведение или логическая суммг над прямыми или инверсными кодами двоичных чисел X и Y. Одновременно на выходе 17 и выходе 18 модуля реализуются сигналы суммы и переноса над прямыми или инверсными кодами входных чисел, что определяется управляющими сигналами Ui и U2, которые могут принимать значения О или 1. Если же на управляющие входы 13, 14 и 15 в качестве управляющих сигналов подать информационные сигналы X и У, то модуль дополнительно реали зует на выходах 16, 17 и 18 ряд логических функций. Полные функциональные возможности модуля приведены в таблице.

Следовательно, на логическом выходе 16 модуля при управляющих сигналах О и 1 реализуются восемь логических функций двух входных переменных X и У, а на выходах 17

и 18 - сигналы суммы и переноса. При подаче

на управляющие входы сигналов X и У модуль

на выходе 16 реализует остальные восемь функвдй двух переменных, в этом случае на выходах 17 и 18 так же реализуются некоторые логические функции переменных X, У и Z.

У предлагаемого устройства на И выводов меньше, чем у известного. При этом оно имеет NieHbuiyio сложность, определяемую по суммарному числу входов логических элементов, входящих в устройство. Это зшрощает изготовление устройства и повышает надежность схемы.

Формула изобретения

Многофункциональный модуль, содержащий элементы И, первый элемент равнозначности, входы которого являются входами, модуля, отличающийся тем, что, с целью повышения надежности путем уменьшения числа внешних выводов, он содержит второй, третий, четвертый и пятый элементы равнозначности, два элемента неравнозначности, причем выходы второго и третьего элементов равнозначности и выход первого элемента неравнозначности являются выходами модуля, первые входы третьего элемента равнозначности и первого элемента неравнозначности соединены между собой и с первым входом второго элемента неравнозначности и являются входом модуля, а второй вход первого элемента неравнозначности соединен с выходом первого элемента И, первый вход которого соединен с выходом четвертого и вторым входом третьего элементов равнозначности, а второй вход подключен к выходу второго элемента неравнозначности, второй вход которого соединен с выходом пятого и первым входом четвертого элементов равнозначности, а также с первым входом второго элемента И, второй вход которого соединен с выходом первого и вторым входом четвертого элементов равнозначности,, а выход подключен к первому входу второго элемента равнозначноста, второй вход которого, также как и входы пятого элемента равнозначности, являются входами модуля.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 275524, кл. G 06 F 7/00, 1969.

2.Патент ФРГ № 1774301, кл. G 06 F 7/50, 1967.

«J

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1282112A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| Самосинхронный одноразрядный троичный сумматор с нулевым спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2810631C1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Арифметико-логический модуль | 1983 |

|

SU1160395A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Управляемый арифметический модуль | 1978 |

|

SU840881A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

Авторы

Даты

1979-11-30—Публикация

1978-06-26—Подача