Изобретение относится к области обучающих устройств и может быть использовано для получения практических навыков работы с цифровыми электрическими схемами, преобразователями аналоговых сигналов в цифровой код, исследования динамики работы цифровых устройств.

Наиболее близким техническим решением, выбранным в качестве прототипа, является стенд для изучения основ цифровой электроники (RU, 2214628, 7 G 09 В 23/18). Стенд содержит блок управления, наборное поле, блок триггеров, блок диодных разветвителей, блок логических элементов, дешифратор двоичного кода в позиционный, два коммутатора, блок индикации, знакосинтезирующий индикатор и задатчик кода вариантов заданий.

Недостатком данного прототипа является ограниченный набор изучаемых устройств, в котором отсутствует возможность сборки и исследования цифроаналоговых и аналогоцифровых преобразователей (ЦАП и АЦП). Кроме того, устройство имеет низкие дидактические возможности, так как не позволяет запомнить и передать в компьютер массив состояний контрольных точек изучаемых электронных схем для автоматического построения временных диаграмм их работы и облегчения выполнения расчетов.

Задача, решаемая изобретением, - расширение номенклатуры изучаемых электронных схем при повышении дидактических возможностей их изучения.

Указанная задача выполняется за счет того, что в стенд для изучения электронных средств автоматизации, содержащий два коммутатора, дешифратор двоичного кода в позиционный, комплект перемычек-соединителей и наборное поле, к гнездам которого подключены блок триггеров, блок логических элементов, набор диодов, блок индикации и блок управления, дополнительно введены третий, четвертый, пятый и шестой коммутаторы, блок ввода-вывода, счетчик, регистр, генератор, блок переключателей, аналоговый сумматор, блок компараторов, регулятор напряжения, набор резисторов, набор конденсаторов и вольтметр.

Предложенное техническое решение имеет следующие отличительные от прототипа признаки:

- более широкая номенклатура элементов для сборки сложных устройств дискретной автоматики;

- наличие элементов с различной степенью интеграции для упрощения сборки сложных схем;

- использование многоразрядных коммутаторов для выполнения групповых соединений;

- наличие блока ввода-вывода с внутренней памятью для записи данных и выдачи их в компьютер.

Функционально полный набор логических элементов позволяет собирать и исследовать синтезированные с помощью средств булевой алгебры комбинационные логические схемы: коммутаторы, шифраторы, дешифраторы, преобразователи кодов, триггеры и т.п.

Набор готовых триггеров позволяет построить на их основе и исследовать работу самых разнообразных счетчиков, регистров и других устройств дискретной автоматики.

Счетчик, регистр, дешифратор также являются "элементарными кирпичиками" более сложных устройств - они используются для построения различных аналого-цифровых преобразователей.

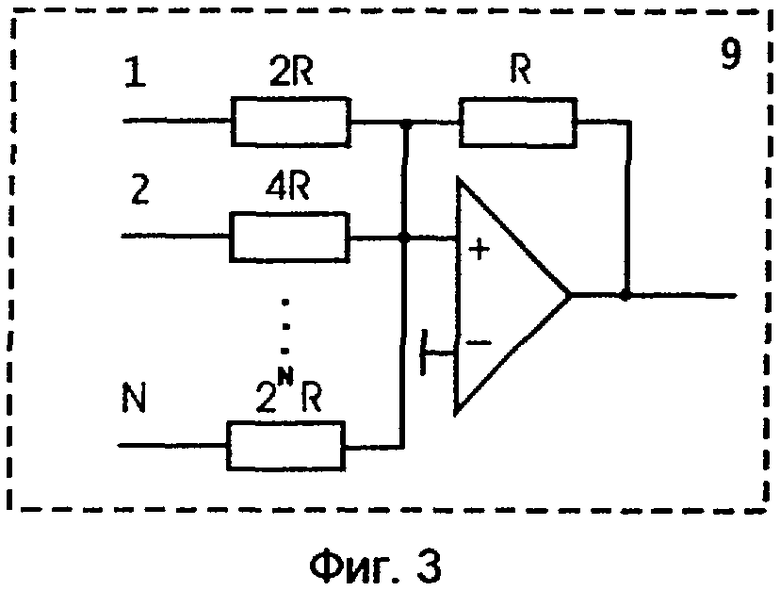

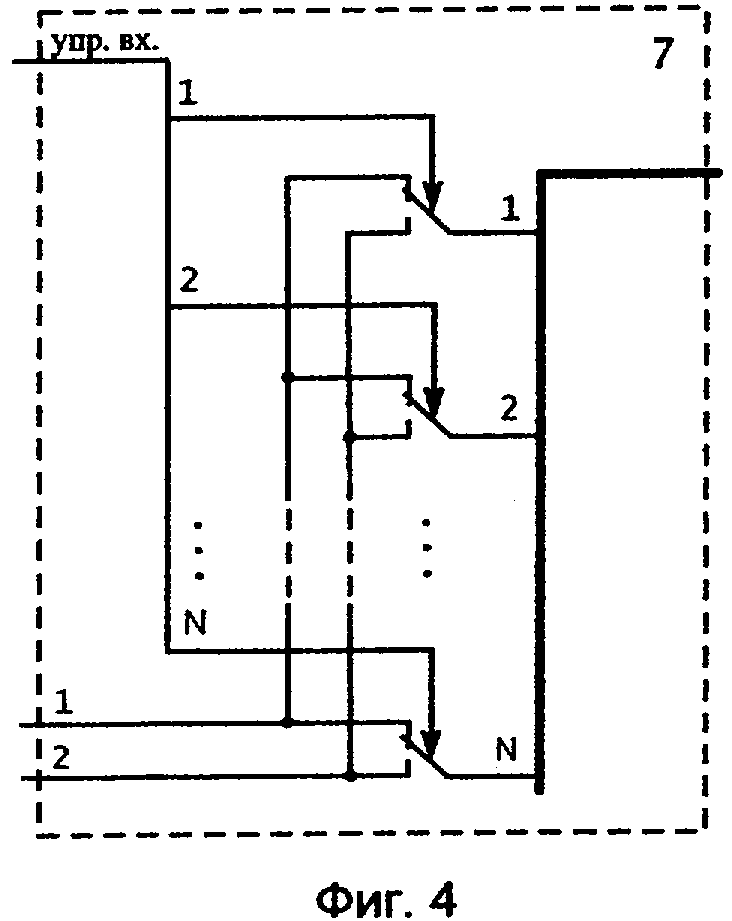

Для предварительной обработки аналоговых сигналов и построения простейших цифроаналоговых преобразователей стенд содержит блок переключателей, блок компараторов и аналоговый сумматор. Блок переключателей позволяет подавать на его выходы одно из двух входных напряжений в соответствии с цифровым кодом, поступающим на управляющие входы блока. Блок компараторов состоит из нескольких компараторов напряжения, первые входы которых объединены, а сигнал на выходе каждого компаратора имеет уровень логического "0", если потенциал на его втором входе меньше, потенциал на первом входе, и логической "1" в противном случае. Исполнение аналогового сумматора с номиналами резисторов, относящихся как 1:21:22:...2N необходимо для того, чтобы получить на его выходе напряжение пропорциональное входному коду, поступающему на управляющие входы блока переключателей.

Для проверки работоспособности собранных схем в шаговом режиме используется блок индикации.

Входные воздействия задаются кнопками и переключателями блока управления, к выходам которых для подавления "дребезга" контактов подключены RS-триггеры.

Чтобы исследовать работу схем в динамике, входные воздействия задаются с помощью генератора, а текущие состояния контрольных точек заносятся с выбранной тактовой частотой в память блока ввода-вывода, откуда они могут быть считаны в компьютер. При этом компьютер под управлением соответствующего программного обеспечения работает как логический анализатор - многоканальный индикатор временных диаграмм.

При изучении сложных логических схем, имеющих регулярную внутреннюю структуру, не требуется большого числа логических элементов для воссоздания всей структуры, так как стенд позволяет изучать и собирать ее из элементов с различной степенью интеграции.

Для выполнения групповых соединений используются многоразрядные управляемые коммутаторы, что упрощает и ускоряет процесс сборки, а также повышает надежность схем и наглядность их изучения.

Возможность автоматического построения временных диаграмм, выполнения компьютерных измерений и выдачи на принтер результатов работы повышают дидактические возможности устройства.

Приведенная совокупность признаков, характеризующих заявленный объект, обуславливает достижение технического результата, обеспечивающего решение задачи изобретения.

Анализ уровня техники показывает, что не известен стенд, которому присущи признаки, идентичные всем существенным признакам данного изобретения. Это говорит о новизне предложенного технического решения.

Предложенное техническое решение применимо, работоспособно, осуществимо и воспроизводимо, так как может быть изготовлено в условиях серийного и единичного производства с применением выпускаемых серийно комплектующих, и, следовательно, соответствует условию патентоспособности "промышленная применимость".

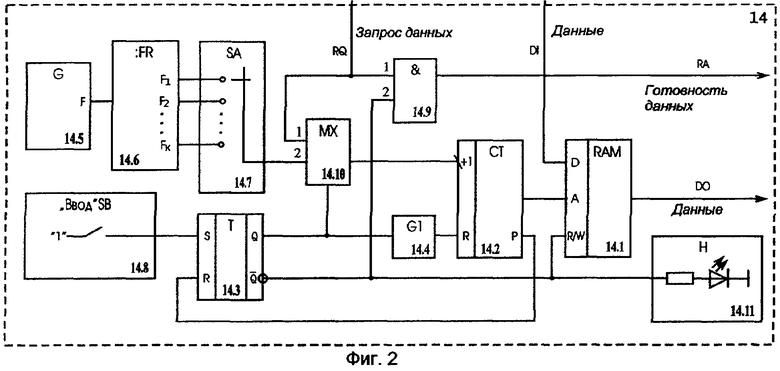

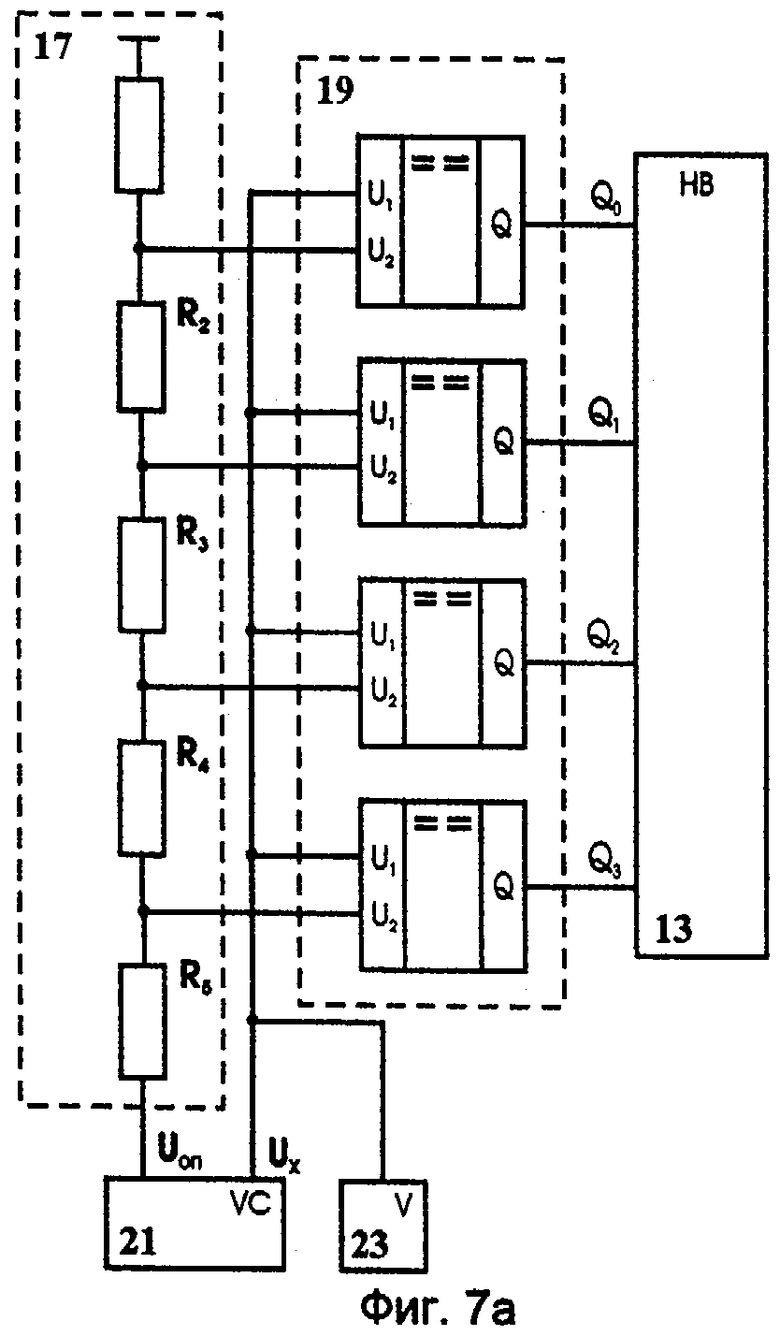

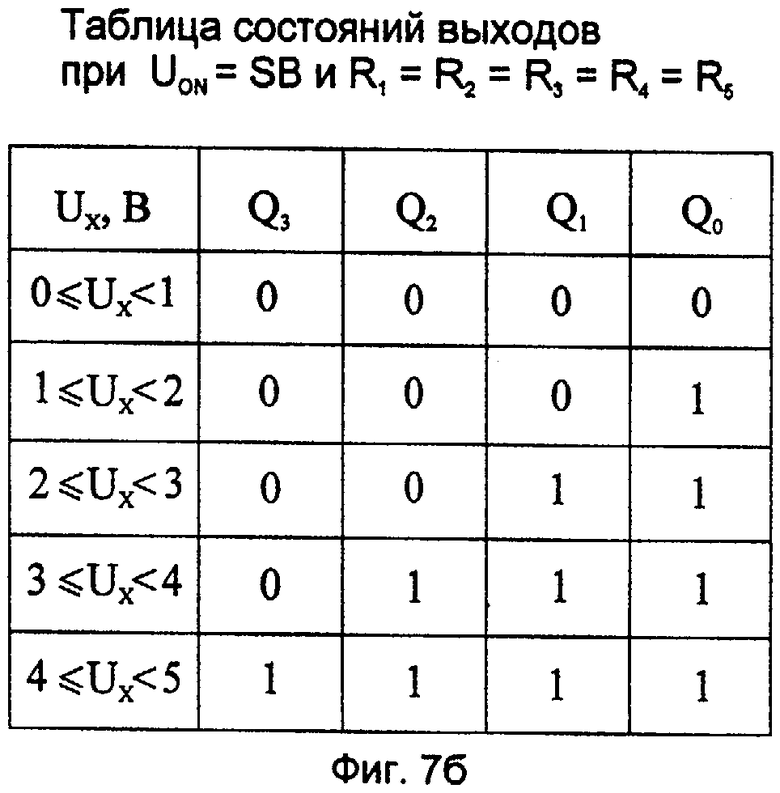

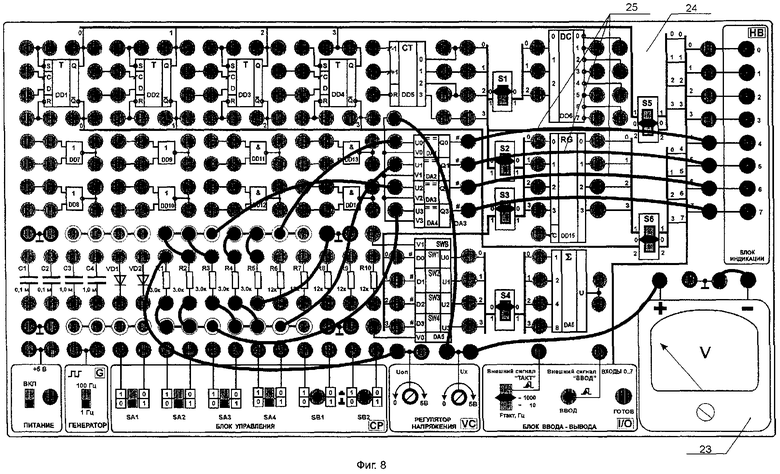

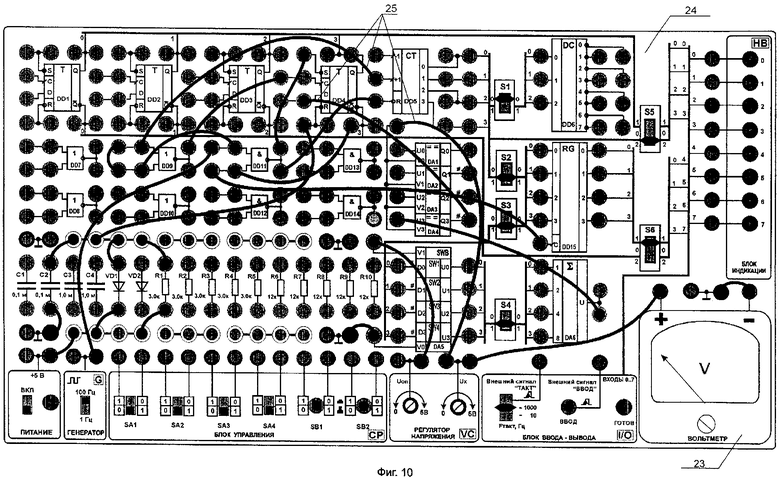

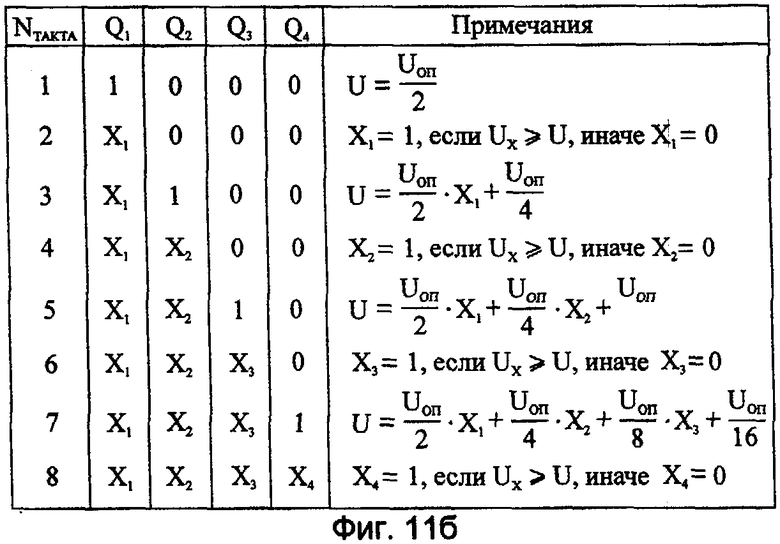

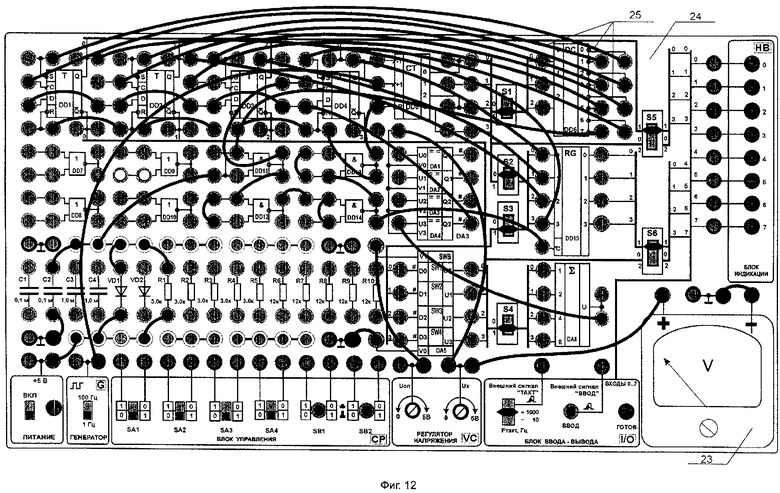

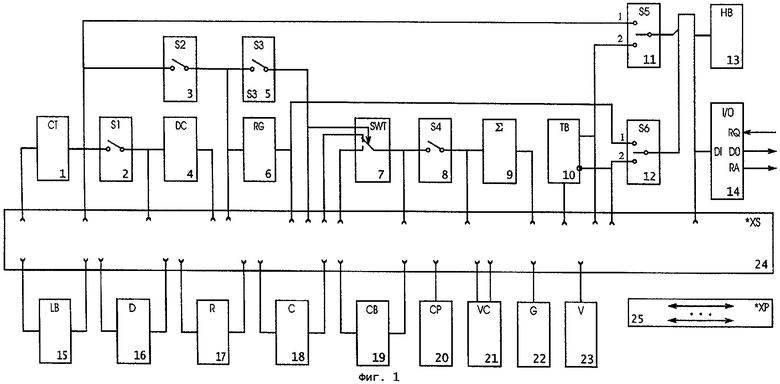

На фиг.1 изображена структура учебного стенда, на фиг.2 - схема блока ввода-вывода, на фиг.3 - вариант внутренней структуры аналогового сумматора, на фиг.4 - вариант схемы блока переключателей, на фиг.5 - вариант схемы блока управления, на фиг.6 - вариант внутренней структуры генератора, на фиг.7а - схема параллельного двухразрядного АЦП, 7б - пример составления таблицы результатов исследования параллельного двухразрядного АЦП, на фиг.8 - пример сборки на наборном поле параллельного двухразрядного АЦП, на фиг.9 - схема четырехразрядного АЦП последовательного приближения, на фиг.10 - пример сборки на наборном поле четырехразрядного АЦП последовательного приближения, фиг.11а - схема четырехразрядного АЦП поразрядного уравновешивания, фиг.11б - пример составления таблицы состояния четырехразрядного АЦП поразрядного уравновешивания, на фиг.12 - пример сборки на наборном поле четырехразрядного АЦП поразрядного уравновешивания.

Стенд для изучения электронных средств автоматизации (фиг.1) содержит счетчик 1, первый коммутатор 2 (S1), второй коммутатор 3 (S2), дешифратор 4 двоичного кода в позиционный, третий коммутатор 5 (S3), регистр 6, блок 7 переключателей, четвертый коммутатор 8 (S4), аналоговый сумматор 9, блок 10 триггеров, пятый коммутатор 11 (S5), шестой коммутатор 12 (S6), блок 13 индикации, блок 14 ввода-вывода, блок 15 логических элементов, набор 16 диодов, набор 17 резисторов, набор 18 конденсаторов, блок 19 компараторов, блок 20 управления, регулятор напряжения 21, генератор 22, вольтметр 23, наборное поле 24 с комплектом перемычек-соединителей 25. К наборному полю 24 подключены счетчик 1, шесть коммутаторов 2, 3, 5, 8, 11 и 12, дешифратор 4, регистр 6, блок переключателей 7, аналоговый сумматор 9, блок 10 триггеров, блок индикации 13, блок ввода-вывода 14, блок 15 логических элементов, набор 16 диодов, набор 17 резисторов, набор 18 конденсаторов, блок 19 аналоговых компараторов, блок управления 20, регулятор напряжения 21, генератор 22 и вольтметр 23. Выход счетчика 1 подключен к входам первого 2 и второго 3 коммутаторов и к первому входу пятого коммутатора 11. Выходы пятого 11 и шестого 12 коммутаторов образуют многоразрядную шину данных, подключенную к входу блока индикации 13 и входу данных блока ввода-вывода 14, вход запроса данных, выход данных и выход подтверждения готовности данных которого являются соответствующими выходами стенда и могут быть подключены к компьютеру (на фиг.1 не показан). Выход первого коммутатора 2 подключен к входу дешифратора 4 двоичного кода в позиционный, выход второго коммутатора 3 подключен к входу регистра 6 и к входу третьего коммутатора 5, выход которого подключен к управляющему входу блока переключателей 7, выход которого через четвертый коммутатор 8 подключен к аналоговому сумматору 9. Выход регистра 6 подключен к первому входу шестого коммутатора 12, второй вход которого подключен к первому выходу блока триггеров 10, второй выход которого подключен к второму входу пятого коммутатора 11. Блок ввода-вывода 14 (фиг.2) содержит модуль оперативной памяти 14.1, счетчик адреса 14.2, триггер 14.3, генератор одиночных импульсов 14.4, генератор импульсов записи 14.5, делитель частоты 14.6, переключатель 14.7, кнопку "ВВОД" 14.8, элемент "И" 14.9, мультиплексор 14.10 и индикатор 14.11. Вход копки "ВВОД" 14.8 подключен к логической "1", а выход - к установочному входу триггера 14.3, прямой выход которого соединен с управляющим входом мультиплексора 14.10 и входом запуска генератора одиночных импульсов 14.4, а инверсный выход - с индикатором 14.11, входом разрешения записи модуля оперативной памяти 14.1 и вторым входом элемента "И" 14.9, выход которого является выходом готовности (RA) данных блока 14. Генератор импульсов записи 14.5 подключен к делителю частоты 14.6, выходы которого подключены к соответствующим входам переключателя 14.7. Первый вход мультиплексора 14.10 является входом запроса данных (RQ) блока ввода-вывода 14 и соединен с первым входом элемента "И" 14.9. Второй вход мультиплексора 14.10 подключен к выходу переключателя 14.7, а выход - к инкрементному входу счетчика адреса 14.2, вход сброса которого соединен с выходом генератора одиночных импульсов 14.4. Вход сброса триггера 14.3 подключен к выходу переполнения счетчика адреса 14.2, другой выход которого соединен с адресным входом модуля оперативной памяти 14.1, вход данных которого является входом данных (DI) блока 14, а выход - выходом данных (DO) блока ввода-вывода 14.

Устройство работает следующим образом.

При изучении работы комбинационных логических схем обучаемый задает с помощью кнопок и переключателей блока управления 20 (фиг.1, 5) входные воздействия ("0", "1") на изучаемый логический элемент или схему, собранную из нескольких логических элементов блока 15, контрольные точки которой подключаются к блоку индикации 13 для визуального контроля их состояния.

Таким же образом изучается работа триггерных схем различной структуры, где схемы собираются при помощи элементов блока триггеров 10 и логических элементов блока 15.

При изучении работы счетчиков и регистров обучаемый по методическому заданию собирает на наборном поле 24 различные варианты счетчиков и регистров, входные состояния которых задаются с помощью блока управления 20, а состояния входов и выходов собранной схемы отображаются индикаторами блока индикации 13.

При изучении работы комбинированных устройств, например, цифроаналогового или аналого-цифрового преобразователей, используются аналоговый сумматор 9 (фиг.3), блок переключателей 7 (фиг.4), и блок компараторов 19. Для задания входных воздействий используются переменное и опорное напряжения, которые подключают в схему от соответствующих гнезд регулятора напряжения 21 с помощью перемычек-соединителей 25. Контроль уровня напряжения осуществляется вольтметром 23.

Наборы резисторов 17 и конденсаторов 18 используются для формирования интегрирующих и дифференцирующих цепочек, линий задержки, а также для построения резисторных делителей напряжения. Набор диодов 16 используется для построения формирователей, объединителей, разветвителей.

Чтобы исследовать работу схем в динамике, входные воздействия задаются с помощью генератора 22 (фиг.6), а текущие состояния контрольных точек заносятся в память блока ввода-вывода 14 с тактовой частотой, заданной положением переключателя 14.7. Они могут быть считаны в компьютер через стандартный интерфейс.

Блок ввода-вывода 14 (фиг.2) работает следующим образом. В исходном состоянии счетчик адреса 14.2 и триггер 14.3 сброшены. Сигнал низкого уровня с прямого выхода триггера 14.3 подключает первый вход мультиплексора 14.10, соединенный со входом запроса данных блока ввода-вывода 14, к инкрементному входу счетчика 14.2. А сигнал высокого уровня с инверсного выхода триггера 14.3 устанавливает модуль оперативной памяти 14.1 в режим чтения и разрешает формирование сигнала готовности данных. Индикатор 14.11 светится, сигнализируя о готовности блока ввода-вывода 14 к обмену данными с компьютером. При поступлении сигнала запроса данных, хранящихся в модуле оперативной памяти 14.1, на выходе элемента "И" 14.9 формируется сигнал готовности, по которому данные, хранящиеся в ячейке памяти с адресом "0", могут быть считаны с выхода модуля оперативной памяти 14.1. По снятию сигнала запроса данных состояние счетчика адреса 14.2 увеличивается, и на выход поступают данные, хранящиеся в следующей ячейке памяти. Далее процесс чтения содержимого памяти повторяется. Для записи данных в память используются синхроимпульсы, вырабатываемые генератором 14.5 импульсов записи, и поступающие на вход делителя частоты 14.6. Чтобы занести данные в память, следует выбрать нужную тактовую частоту переключателем 14.7 и нажать кнопку "ВВОД" 14.8. При этом триггер 14.3 взводится, сигнал с его прямого выхода поступает на вход генератора 14.4, который вырабатывает одиночный импульс сброса счетчика адреса 14.2, и на управляющий вход мультиплексора 14.10, который подключает к инкрементному входу счетчика адреса 14.2 выход переключателя 14.7. А сигнал низкого уровня с инверсного выхода триггера 14.3 запрещает формирование сигнала готовности данных и устанавливает модуль оперативной памяти 14.1 в режим записи. При этом индикатор 14.11 гаснет, а данные, поступающие на вход блока ввода-вывода 14, записываются с нужной тактовой частотой в ячейки модуля оперативной памяти 14.1 до переполнения счетчика адреса 14.2, сигнал переполнения которого сбрасывает триггер 14.3 и переводит блок ввода-вывода в исходное состояние.

Рассмотрим несколько примеров работы обучаемого со стендом.

1. Обучаемый по методическому заданию выполняет сборку параллельного двухразрядного АЦП, схема которого приведена на фиг.7а. Сборка выполняется при использовании резисторов набора резисторов 17 и аналоговых компараторов блока 19 путем соединения соответствующих гнезд наборного поля 24 с помощью перемычек 25, как показано на фиг.8. В этом случае коммутаторы 11 и 12 должны быть установлены в положение "0". Обучаемый устанавливает соответствие входного напряжения Ux, которое подается в схему от регулятора напряжения 21 и отображается на вольтметре 23, и выходного кода блока аналоговых компараторов 19, который отображается светодиодами блока индикации 13. Результаты заносятся в таблицу (фиг.7б). Пороги срабатывания компараторов блока 19 легко изменяются путем установки различных значений опорного напряжения Uоп на регуляторе напряжения 21. Для преобразования весового кода в двоичный, обучаемый может синтезировать с помощью средств булевой алгебры простейшую комбинационную схему неполного шифратора и легко собрать ее из имеющихся логических элементов.

2. Обучаемый по методическому заданию выполняет сборку четырехразрядного АЦП последовательного приближения, схема которого приведена на фиг.9, на наборном поле 24 (см. фиг.10). При этом используются элементы блока триггеров 10, блока логических элементов 15 и блока аналоговых компараторов 19, счетчик 1, блок переключателей 7, аналоговый сумматор 9, регистр 6. Для сборки формирователя сигнала "Начальный сброс", который необходим для установки схемы в исходное состояние после включения питания, используются элементы наборов диодов 16, резисторов 17 и конденсаторов 18. Соединение выходов счетчика 1 с входами регистра 6 производится установкой коммутатора 3 (S2) в положение "1"; с управляющими входами блока переключателей 7 - установкой коммутатора 5 (S3) в положение "1"; с разрядами 0...3 входа блока индикации 13 - установкой коммутатора 11 (S5) в положение "1". Выходы регистра 6 подключаются к разрядам 4...7 входа блока индикации 13 установкой коммутатора 12 (S6) в положение "1". После включения питания с генератора 22 на счетчик 1 поступают прямоугольные импульсы. Кодом на его выходе замыкаются соответствующие переключатели блока переключателей 7, подающие Uоп с регулятора напряжения 21 на соответствующие входы аналогового сумматора 9. На его выходе появляется напряжение, изменяющееся в соответствии с кодом счетчика 1. Когда напряжение на выходе аналогового сумматора 9 превысит входное напряжение Ux, на выходе компаратора блока 19 появится логическая "1", которая "защелкивается" в триггере блока 10 фронтом сигнала, поступающего с выхода элемента "НЕ" блока 15. По сигналу с его инверсного выхода код счетчика 1 запоминается в регистре 6 и отображается на индикаторе 13. Этим же сигналом, поступающим через элемент "И-НЕ" блока 15, выполняется сброс счетчика 1 и установка в "1" триггера блока 10. Обучаемый устанавливает соответствие входного напряжения Ux и выходного кода, который отображается светодиодами блока индикации 13. Для отладки схемы и ее проверки в шаговом режиме выход счетчика 1 через коммутатор 11 (S5) подключен к блоку индикации 13, а выход Ux регулятора напряжения 21 подключен к входу вольтметра 23. Для автоматического построения временных диаграмм и выполнения компьютерных измерений обучаемый должен записать текущие состояния контрольных точек в память блока ввода-вывода 14 (на фиг.8 не показан), для чего выбирает тактовую частоту переключателем Fтакт, нажимает кнопку "ВВОД" 14.8, при этом индикатор 14.11 "ГОТОВ" гаснет на время записи, и посылает от компьютера запрос RQ на выдачу данных, записанных в память блока ввода-вывода 14. При этом компьютер под управлением соответствующего программного обеспечения работает как логический анализатор - многоканальный индикатор временных диаграмм.

3. Обучаемый выполняет сборку четырехразрядного АЦП поразрядного уравновешивания, схема которого приведена на фиг.11a, таблица состояний - на фиг.11б, а результат сборки - на фиг.12. Групповые соединения, как и в предыдущих примерах, выполняются многоразрядными коммутаторами, что упрощает и значительно ускоряет процесс сборки схемы без потери наглядности. Остальные связи, имеющие, однако, принципиальное значение для понимания работы схемы, выполняются вручную с помощью перемычек-соединителей 25 - это способствует более глубокому усвоению материала. В схеме используются счетчик 1, дешифратор 4, блок триггеров 10, регистр 6, компаратор блока 19; блок переключателей 7, коммутатор 8 и аналоговый сумматор 9, образующие цифроаналоговый преобразователь (см. схему ЦАП на фиг.9); коммутаторы 2, 5, 11 и 12 и элементы блока логических элементов 15, наборов диодов 16 и конденсаторов 18, образующих "Узел перезапуска", и формирователь сигнала "Начальный сброс" (см. ФСНС на фиг.9). После включения питания счетчик 1 и триггеры блока 10 сбрасываются сигналом от "Узла перезапуска", а с генератора 22 (на фиг.11a не показан) на счетчик 1 начинают поступать прямоугольные импульсы. Дешифратор 4 преобразует двоичный код на выходе счетчика 1 в унитарный. Сигнал с выхода "0" дешифратора 4 устанавливает в "1" первый триггер блока 10. ЦАП (см. фиг.9) преобразует код на выходе блока триггеров 10 в соответствующее коду напряжение U. Компаратор блока 19 сравнивает это напряжение с входным напряжением Ux. Если Ux>U на выходе компаратора блока 19 устанавливается значение логической "1", которая сигналом с выхода "1" дешифратора 4 записывается в первый триггер блока 10. В противном случае туда заносится "0". Далее процесс повторяется для остальных триггеров блока 10. Сигнал с последнего выхода дешифратора 4 поступает на первый вход элемента "И-НЕ" "Узла перезапуска", сигнал с первого выхода которого фиксирует в регистре 6 кодовую комбинацию, полученную на выходе блока триггеров 10. А сигнал со второго выхода "Узла перезапуска" сбрасывает счетчик 1 и триггеры блока 10, подготавливая схему к следующему циклу аналого-цифрового преобразования. Результирующий код, соответствующий входному напряжению Ux, обучаемый может наблюдать на блоке индикации 13. Для отладки схемы и ее проверки в шаговом режиме выход блока триггеров 10 через коммутатор 11 (S5) подключен к блоку индикации 13, а выход Ux регулятора напряжения 21 (фиг.12) подключен к входу вольтметра 23 (на фиг.11а не показаны). Процесс аналого-цифрового преобразования методом поразрядного уравновешивания приведен в таблице на фиг.11б.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ СРЕДСТВ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 2002 |

|

RU2237927C2 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ОСНОВ РЕЛЕЙНОЙ АВТОМАТИКИ | 2001 |

|

RU2237926C2 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ОСНОВ ЭЛЕКТРОТЕХНИКИ | 2001 |

|

RU2236708C2 |

| Устройство для программного счета витков из гибкого материала | 1985 |

|

SU1298783A1 |

| Устройство для контроля знаний обучаемого | 1988 |

|

SU1569864A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для обучения операторов | 1989 |

|

SU1709372A1 |

| Тренажер сварщика | 1988 |

|

SU1550571A1 |

Изобретение относится к области обучающих устройств и может быть использовано для получения практических навыков работы с цифровыми электрическими схемами, цифроаналоговыми и аналого-цифровыми преобразователями, исследования динамики работы цифровых устройств, выполнения компьютерных измерений. Технический результат достигаемый изобретением - расширение номенклатуры изучаемых электронных схем при повышении дидактических возможностей их изучения. Стенд для изучения электронных средств автоматизации содержит счетчик (1), дешифратор двоичного кода в позиционный (4), регистр (6), блок переключателей (7), аналоговый сумматор (9), блок триггеров (10), шесть коммутаторов (2), (3), (5), (8), (11) и (12) блок индикации (13), блок ввода-вывода (14), блок логических элементов (15), набор диодов (16) набор резисторов (17), набор конденсаторов (18), блок компараторов (19), блок управления (20), регулятор напряжения (21), генератор (22), вольтметр (23) и наборное поле (24) с комплектом перемычек-соединителей (25). С помощью стенда возможно изучение как простейших логических элементов, так и сложных электронных схем в статическом и динамическом режимах работы. Возможность автоматического построения временных диаграмм, выполнения компьютерных измерений и выдачи на принтер результатов работы повышают дидактические возможности устройства. 4 з.п. ф-лы, 12 ил.

| RU 2214628 C2, 20.10.2003 | |||

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для правки пруткового материала | 1975 |

|

SU534273A2 |

Авторы

Даты

2006-07-10—Публикация

2005-01-11—Подача