Изобретение относится к ныч исли- тельнон технике и может бг.ггь использовано в системах обработки и передачи цифровой информации,

Цель изобретения - повьипение достоверности декодирования информации и быстродействия устройства.

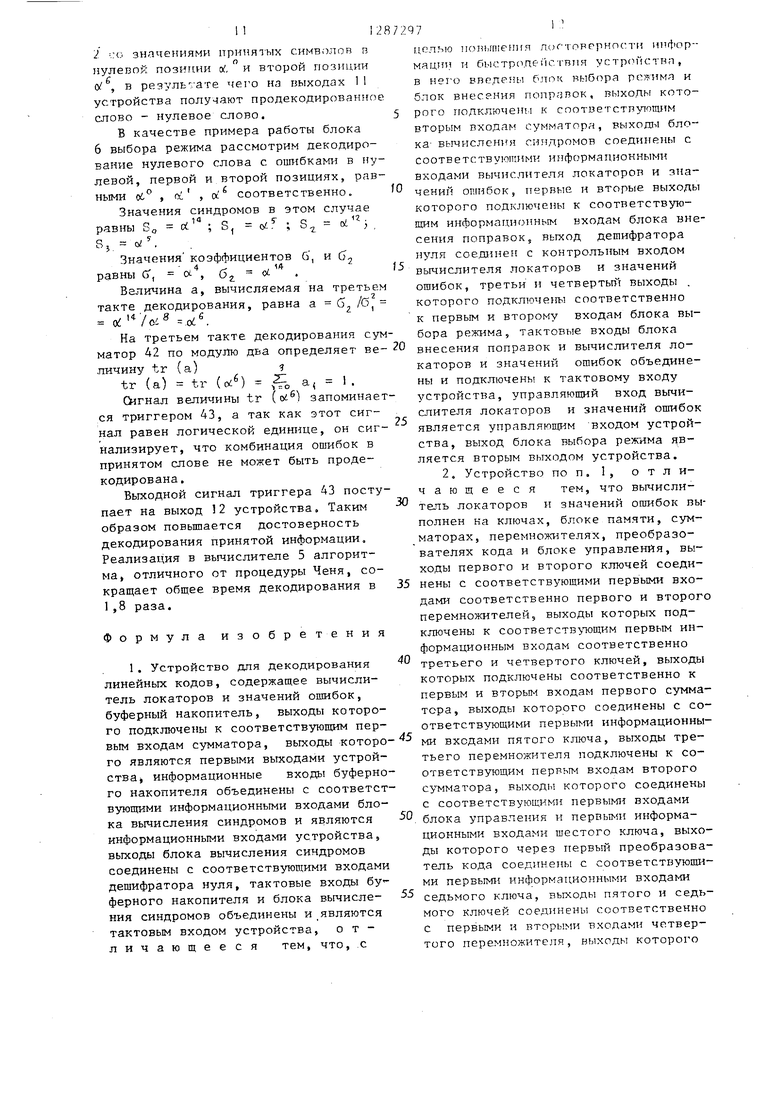

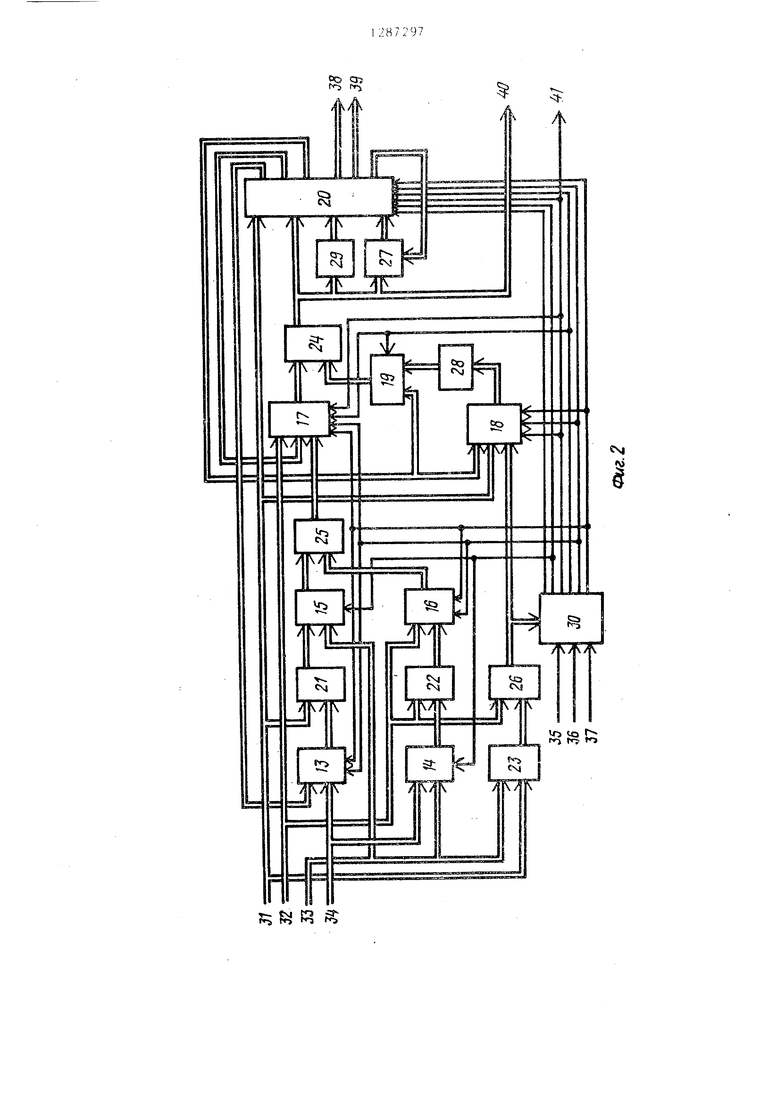

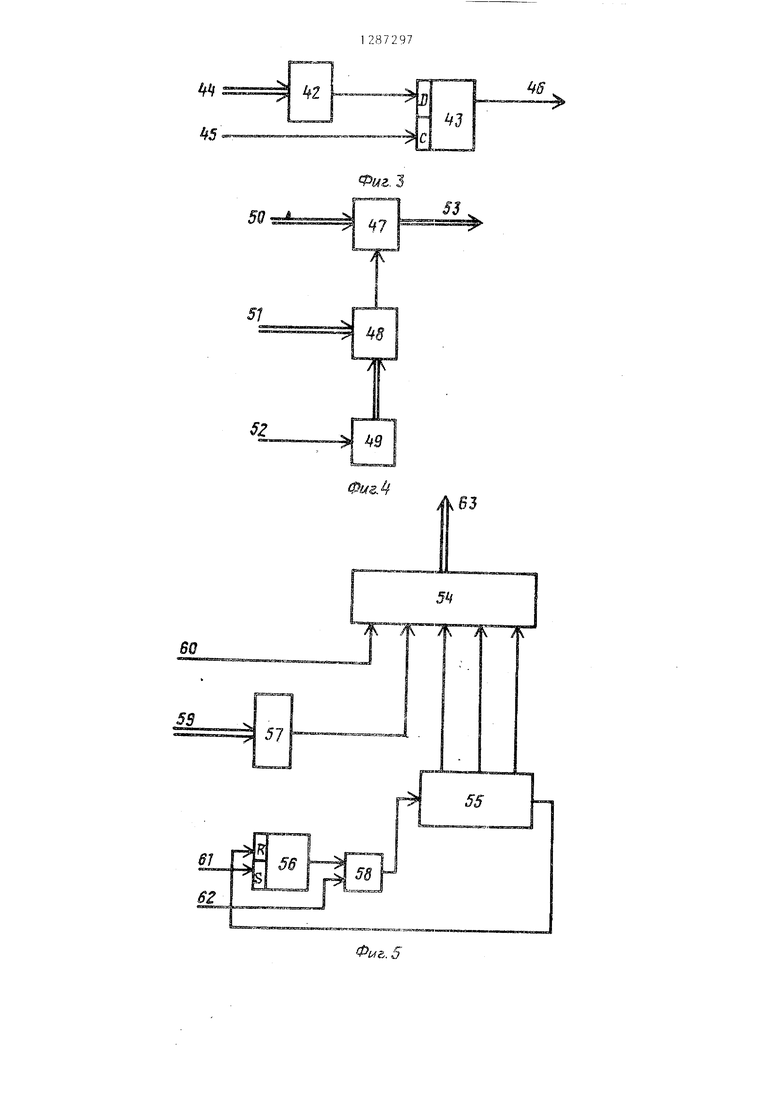

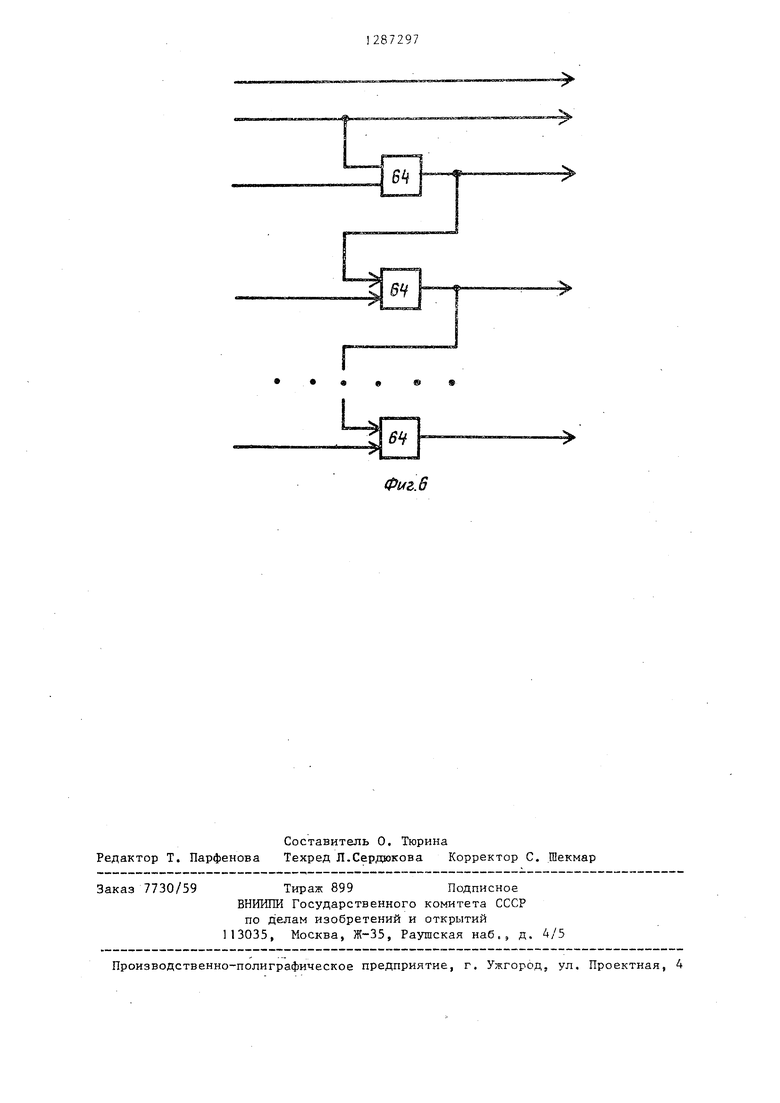

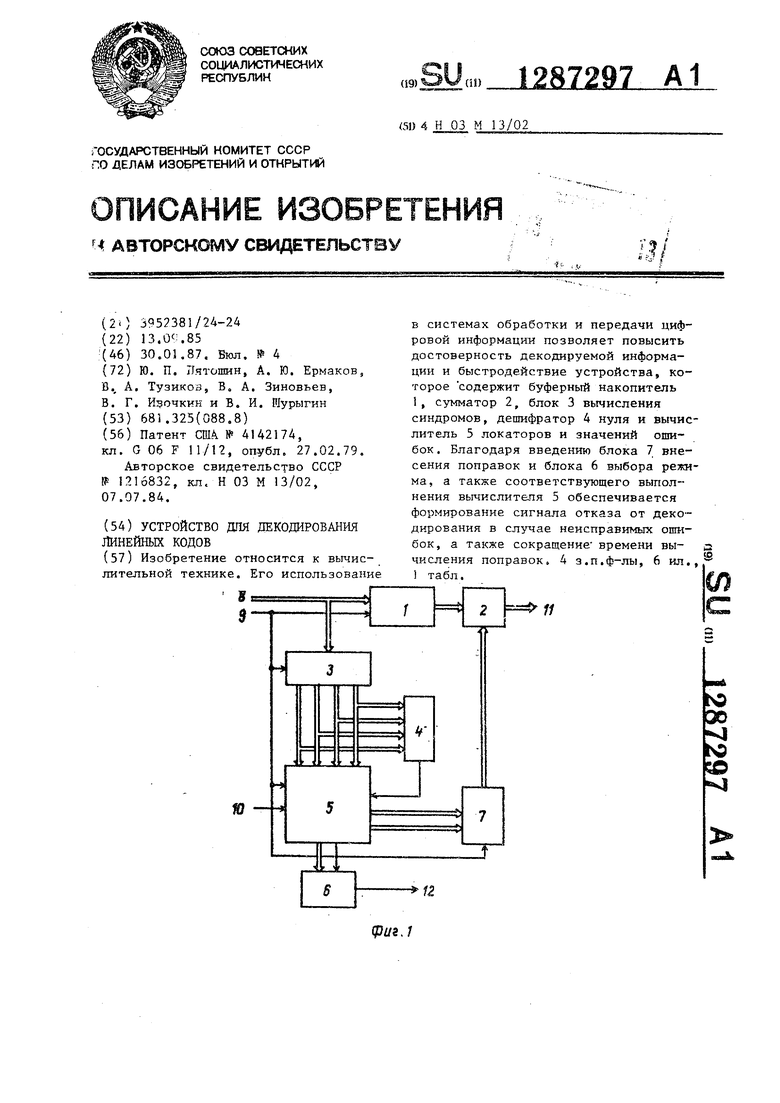

На фиг. изображена блок-схема устройства для декодирования линейных кодов; на фиг. 2 - функциональная схема вычислителя локаторов и значений ошибок; на фиг„ 3 - функциональная схема блока выбора режима| на фиг. 4 - функциональная схема блока

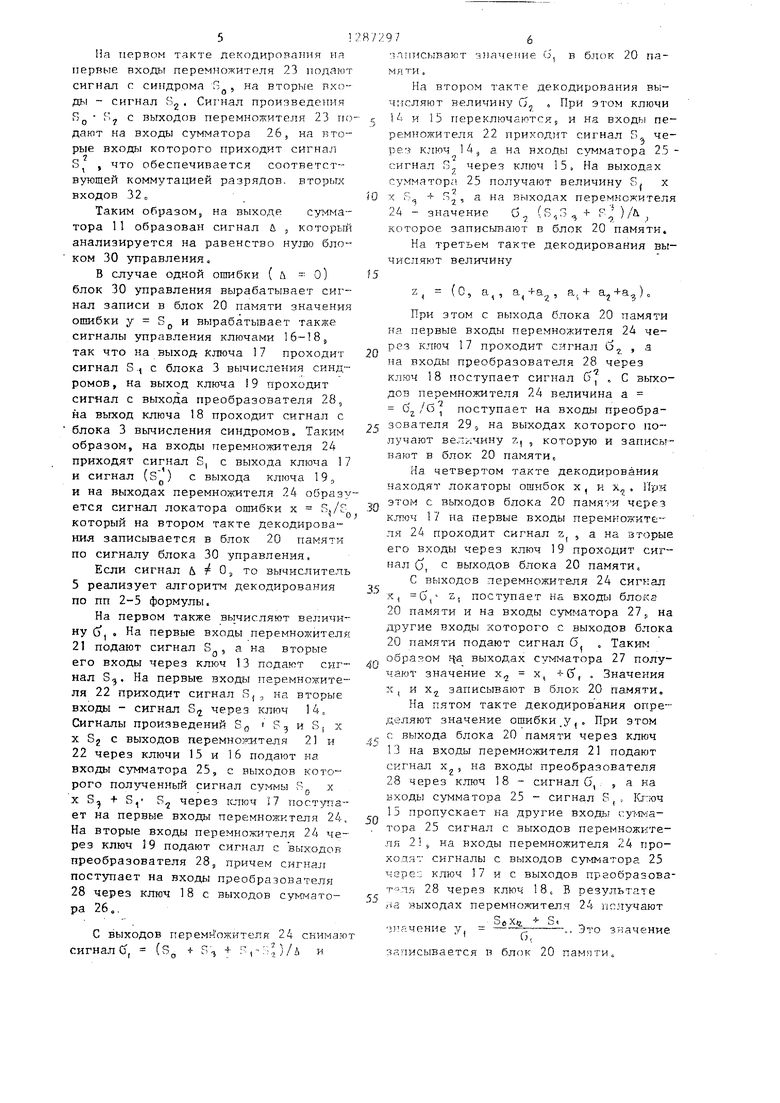

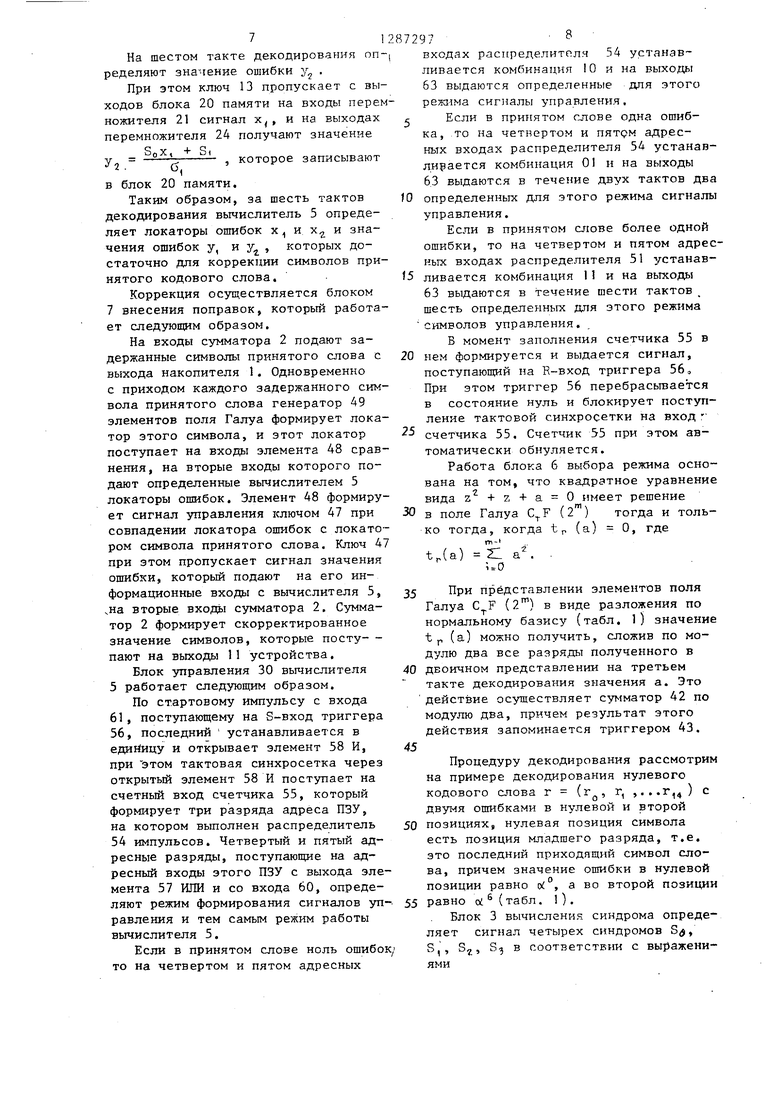

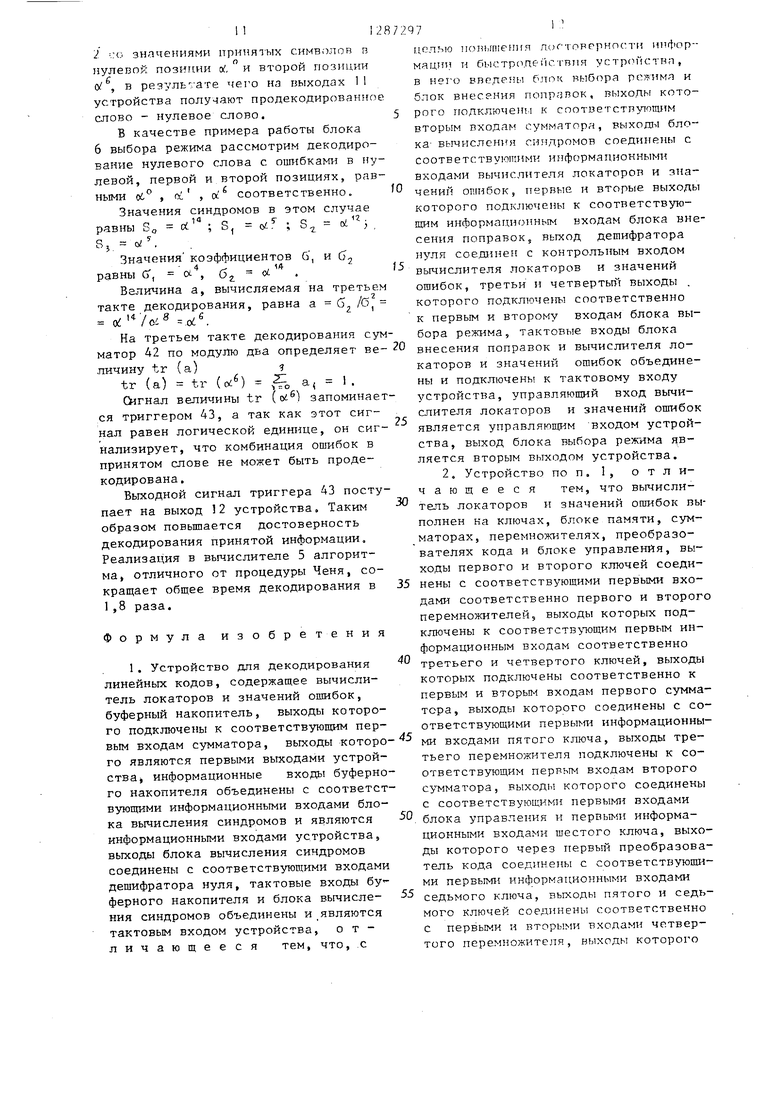

перные - четвертые и 1формационные входы 31-34, контрольный, управляющий и тактовый входы 35-37, первые, вторые;, третьи и четвертый выходы 38Блок 6 вь бора режима служит для формирования сигнала отказа от декодирования в случае неисправимых ошибок и выполнен (фиг, 3) на сумматоре Ш 42 и триггере 43, На фиг. 3 обозначены первые и второй входы 44 и 45 и выходы 46 о

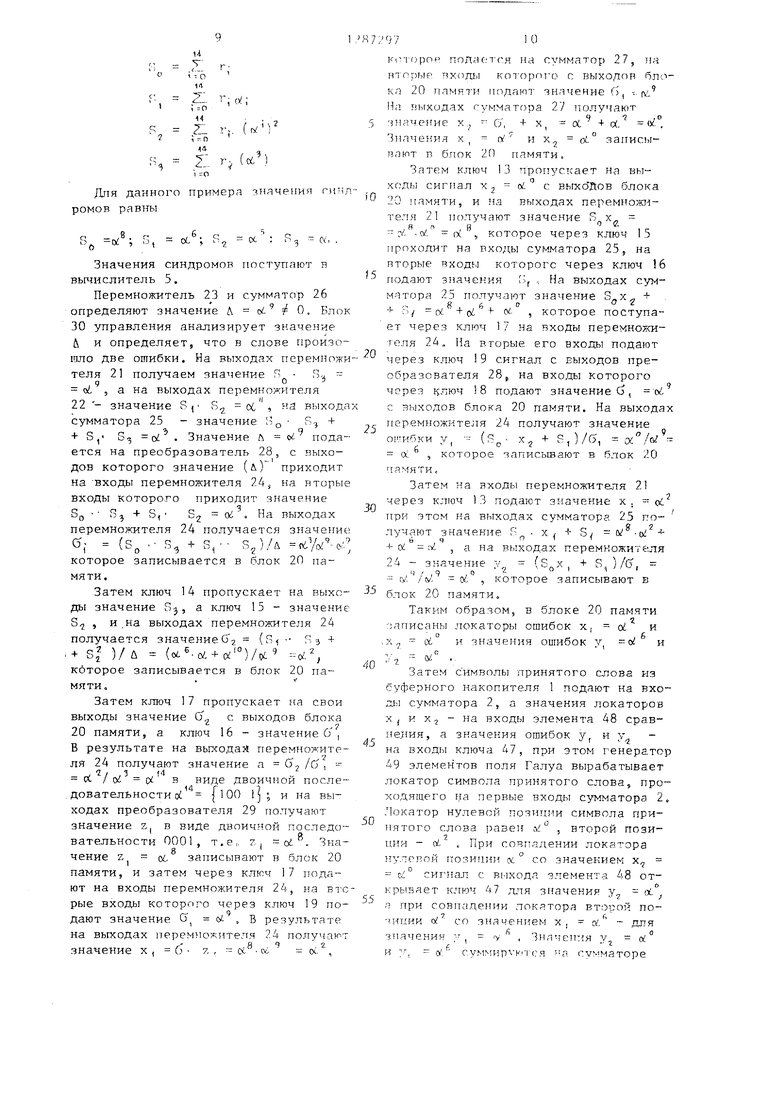

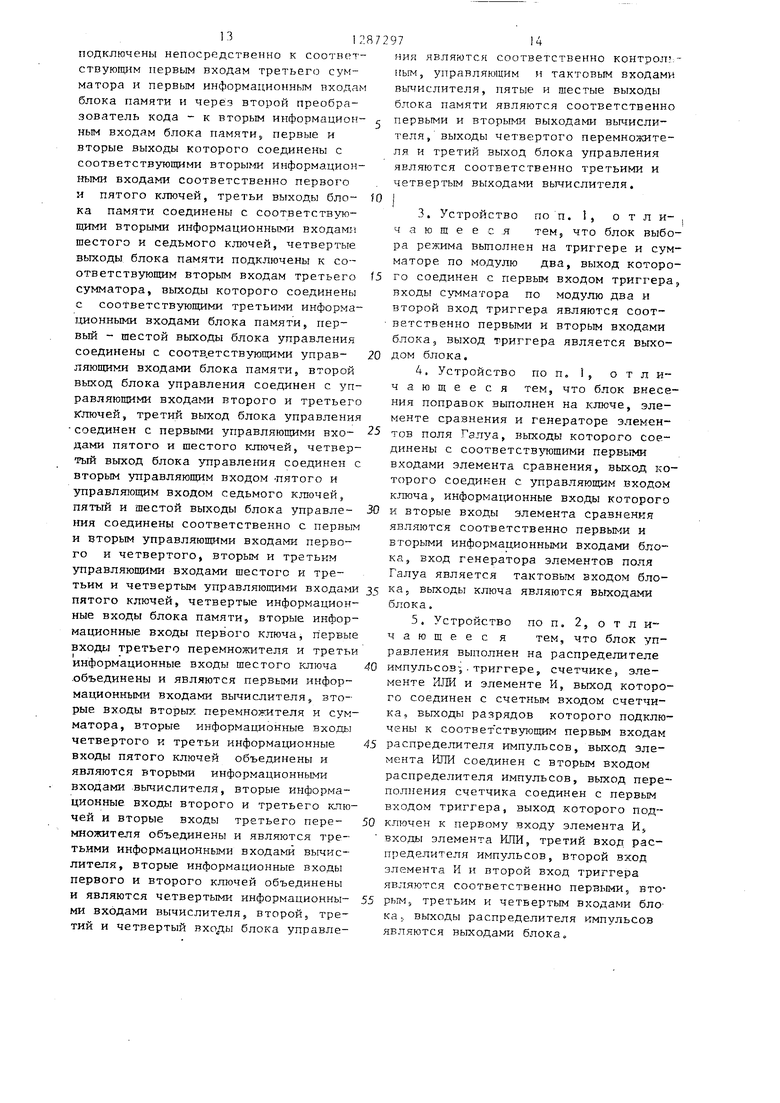

Блок 7 внесения поправок формирует

сигналы, с помощью которых производит- внесения поправок; на фиг, 5 - схема 5 ся исправление ошибок. Этот блок блока управления; на фиг, 6 - схема (фиг 4) выполнен на ключе 47, элементе 48 сравнения и генераторе 49 элементов поля Галуа, На фиг 4 обозначены первые и вторые информационвторого преобразователя кодов в вычислителе локаторов и значений ошибок.

Устройство дпя декодирования ли- 20 лые входы 50 и 51 тактовьп вход 52

нейных кодов содержит буферный накопитель ij сумматор 2, блок 3 вычисления синдромов 9 дешифратор 4 нуля вычислитель 5 локаторов и значений ошибок, блок 6 выбора режима и блок 7 внесения поправок о На фиг„ 1 обозначены также информационные входы 8, тактовый и управляющий входы 9 и 10, первые и вторые выходы П и 12„

В вычислителе 5 перемножители 2 24 и сумматоры 25-27 осуществляют соответсавующие операции в поле Галуа C,.F (2 ), Блок 30 управления включает Б себя (фиг, 5/ распределитель 54 рмпульсов, счетчик 55, триггер 56, элемент 57 ИЛИ и четвертый 58 I. На фиг, 5 обозначены первые второй;,

вьтолнен на m разрядных параллельных регистрах, где m - разрядность символа входного кода о

Сумматор 2 является сумматором з поле Галуа (2).

Блок 3 вычисления синдромов ствляет определение синдромов ошибок

40

Буферный накопитель 1 предназна- - третий и четвертый входы 59-62 и вы- чен дпя задержки входных символов на ходы 63 блока 30„ Первый преобразова- требуемое число т актов и может тель 28 кода осуществляет полутчеиие

обратного элемента поля Галуа, если на его входы поступает код ot Бпок 35 20 памяти выполнен на ОЗУ, преобразователь 28 кода и распределитель 54 импульсов выполнены на постоянньгк запоминающих устройствах (ПЗУ). Второй преобразователь 29 кода (фиг, 6)

во входном слове в соответствии с Бьmoлнeн на сумматорах 64 по модулю проверочными уравнениями используемого кода Блок 3 может быть выполнен ка пар - ллельных регистрах с сумматорами по модулю два,.включенными в цепи обратной связи этих регистров, Дешифратор 4 нуля индицирует отсутствие ошибок во входном слове (равенство всех синдромов нулю) и представляет собой элемент ИЛИ,

Вычислитель 5 локаторов и значений 50 сумматором но модулю два. ошибок для случая кода Ри,ца Соломона Работу устройства опишем на при- (15, 11) выполнен (фиг, 2) на первом- мере декодирования кода Рида-СоЛомо- седьмом ключах 13-195 блоке 20 памяти, первом - четвертом перемножителях 21-24, первом, втором и третьем сумматорах 25-27, первом и втором преобразователях 28 и 29 кода и блоке 30 управления. На фиг, 2 обозначены

два, ,

В блоке 6 выбора режимасумматор 42 осуществляет суммирование по модулю два разрядов, посТупаюш 5х на. его входы.

В блоке 7 внесения поправок генератор 49 элементов поля Галуа выполнен на кольцевом регистре СДВИГР. с

на (, 55 П) над полем Галуа C,.F (2), исправляющего две ошибки, В дальнейшем считаем, что тактовая синхрокк- лация установлена и тактовая синхро- сетка поступает на тактовый вход 9 у г: трои с ТВ а .

12872972

перные - четвертые и 1формационные входы 31-34, контрольный, управляющий и тактовый входы 35-37, первые, вторые;, третьи и четвертый выходы 38Блок 6 вь бора режима служит для формирования сигнала отказа от декодирования в случае неисправимых ошибок и выполнен (фиг, 3) на сумматоре 42 и триггере 43, На фиг. 3 обозначены первые и второй входы 44 и 45 и выходы 46 о

Блок 7 внесения поправок формирует

и выходы 53,

В вычислителе 5 перемножители 2 24 и сумматоры 25-27 осуществляют соответсавующие операции в поле Галуа C,.F (2 ), Блок 30 управления включает Б себя (фиг, 5/ распределитель 54 рмпульсов, счетчик 55, триггер 56, элемент 57 ИЛИ и четвертый 58 I. На фиг, 5 обозначены первые второй;,

третий и четвертый входы 59-62 и вы- ходы 63 блока 30„ Первый преобразова- тель 28 кода осуществляет полутчеиие

Бьmoлнeн на сумматорах 64 по модулю

два, ,

В блоке 6 выбора режимасумматор 42 осуществляет суммирование по модулю два разрядов, посТупаюш 5х на. его входы.

В блоке 7 внесения поправок генератор 49 элементов поля Галуа выполнен на кольцевом регистре СДВИГР. с

сумматором но модулю два. Работу устройства опишем на при- мере декодирования кода Рида-СоЛомо-

на (, 55 П) над полем Галуа C,.F (2), исправляющего две ошибки, В дальнейшем считаем, что тактовая синхрокк- лация установлена и тактовая синхро- сетка поступает на тактовый вход 9 у г: трои с ТВ а .

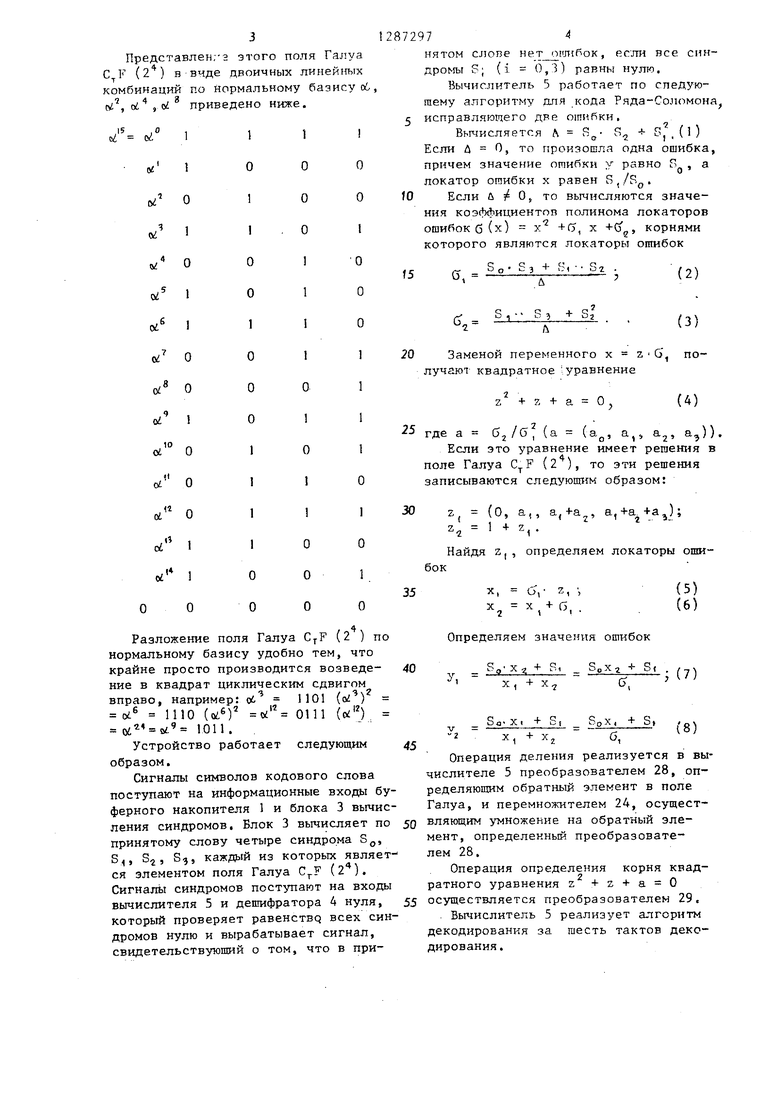

Представлен,2 этого поля Галуа (2 ) в виде двоичных лиией1шх комбинаций по нормальному базису об, Cii , Ы , oi приведено ниже.

,011.

Разложение поля Галуа C,F (2 ) по нормальному базису удобно тем, что крайне просто производится возведе- кие в квадрат циклическим сдвигом вправо, например: 1101 (oi) Ы (ui) ы 0111 (ci)

следующим

45

о X I + Ь X, + X,

G,

Устройство работает образом.Операция деления реализуется в выСигналы символов кодового словачислителе 5 преобразователем 28, оппоступают на информационные входы бу-ределяющим обратный элемент в поле

ферного накопителя 1 и блока 3 вычис-Галуа, и перемножителем 24, осущестления синдромов. Блок 3 вьтисляет по 50вляющим умножение на обратный элепринятому слову четыре синдрома S,мент, определенный преобразоватеБ, Sj) БЭ каждый из которых являет-лем 28.

ся элементом поля Галуа (2). Операция определения корня квадСигналь синдромов поступают на входыратного уравнения z + z + а О

вычислителя 5 и дешифратора 4 нуля, 55осуществляется преобразователем 29, который проверяет равенствд всех син- Вычислитель 5 реализует алгоритм

дромов нулю и вырабатывает сигнал,декодирования за тесть тактов декосвидетельствуюший о том, что в при-дирования.

287297

нятом слове нет)1 Л1бок, ес ли все син- ApoNibt S; (i 0,3) равны нулю.

Вычислитель 5 работает по спедую- гаему алгоритму для кода Ряда-Соломона 5 исправляющего две ошибки.

Вычисляется А S + SJ,(l) Если Д О, то произошла одна ошибка, причем значение отибкн у равно S , а локатор ошибки х равен S , /R. fO Если Л г QS то вычисляются значения коэффициентов полинома локаторов ошибок G (х) х +5, X , корнями

которого являются локаторы ошибок

G,

.

+

S.

(2) (3)

20

Заменой переменного х z О , по5

лучакп квадратное .уравнение

+ a 0j где а (J , (а - (а, а,.

2

(А) а,)).

0

Если это уравнение имеет решения в поле Галуа С F (2 ), то эти решения записываются следующим образом:

Z, (о, а,, а,+а, а,,); Z, - 1 Z,.

Найдя Z,, определяем локаторы ошибок

2

Z,

Jl

х,-Ь5

(5) (6)

Определяем значе.чия ошибок

+ S,

:, + X,

SpX + 5(

;(7)

о X I + Ь X, + X,

+ S,

G,

(8)

Операция деления реализуется в вы

51287297

такте декодирования на перемножителя 23 подают

мя

сигнал с синдрома

на BTOphte входы сигнал Sj. Сигнал произведения Bjj с выходов перемножителя 23 rif) дают на входы сумматора 26, на вторые входы которого приходит сигнал S , что обеспечивается соответст-- вующей коммутацией разрядов, вторых входов 32„

Таким образом5 на выходе сумма-тора 11 образован сигнал & , которьш анализируется на равенство нулю блоком 30 управления.

В случае одной ошибки (и О) блок 30 управления вырабатывает сигнал записи в блок 20 памяти значения ошибки у SP и вырабатывает также сигналы управления ключами 16-18, так что на выход- ключа 17 проходит сигнал Б., с блока 3 вычисления синдромов , на выход ключа 19 проходит сигнал с выхода преобразователя 28, на выход ключа 18 проходит сигнал с блока 3 вычисления синдромов. Таким образом, на входы перемножителя 24 приходят сигнал S, с выхода ключа 17 и сигнал (S) с выхода ключа 19, и на выходах перемножителя 24 образуется сигнал локатора ошибки х который на втором такте декодирования записывается в блок 20 памяти по сигналу блока 30 управления.

Если сигнал & т О, то вычислитель 5 реализует алгоритм декодирования по пп 2-5 формулы.

На первом также вычисляют величину (j| . На первые входы перемножителя

21подают сигнал S, а на вторые его входы через ключ I3 подают сигнал S. На первые входы перемножителя 22 приходит сигнал Sj, на вторые входы - сигнал S через ключ 14 Сигналы произведений Sg S и S, х X Sg с выходов перемно)снтеля 21 и

22через ключи 15 и 16 подают на входы сумматора 25, с выходов которого полученный сигнал суммы Я х

X S + S, S через тслюч 17 поступает на первые входы перемножителя 24. На вторые входы перемножителя 24 через ключ 19 подают сигнал с выходов преобразователя 28, причем сигнал поступает на входы преобразователя 28 через ключ 8 с выходов сумматора 26..

С выходов перемн ожителя 24 снимаю

сигнал O j (Sj

)/Д

: Г1Т1исьтают зиачепие (5, в блок 20 памяти .

На втором такте декодирования Bbiчмсляют величину и.

При этом ключи

14 и 15 переключаются, и на входы пе- ремноясителя 22 приход)1т сигнал 3, через ключам, а на входы сумматора 25 - сигнал S через ключ 15, На выходах сумматора 25 получагот величину S, х

L гX .,, + S,,, 24 - значение

а на выходах перемножителя ) ( S Т + F ) /U

) - - I M 7. .)

которое записывают в блок 20 памяти.

На третьем такте декодирования вычисляют величину

а,,

8. + а +а.

При зтом с выхода блока 20 памяти на первые входы перемножителя 24 через ключ 17 проходит сигнал б , а на входы преобразователя 28 через ключ 18 поступает сигнал б, „ С выходов перемножителя 24 величина а поступает на входы преобра- зователя 29, на выходах которого получают величину Z, 5 которую и записывают в блок 20 памяти с

На четвертом такте декодирования находят локаторы ошибок х , к х„. При этом с выходов блока 20 памяо-и через ключ 17 на первые входы перемножите- ля 24 проходит сигнал г , а на вторые его входы через ключ 19 проходит сигнал б, с выходов блока 20 памяти,

С выходов перемножителя 24 сигнал X, G, S, поступает ка входы блока 20 памяти и на входы сумматора 27 на другие входы которого с выходов блока

0

5

0

5

20 памяти подают сигнал G , Таким образом fi-a выходах сум1 1атора 27 полу- чак1Т значение х х, -i-G, . Значения XJ и х записывают в блок 20 памяти,

На пятом такте декодирования определяют значение ошибки у,. При этом с выхода блока 20 памяти через ключ 3 на входы перемножителя 21 подают сигнал х, на входы преобразователя 28 через ключ 18 сигнал G, , , я. на входы сумматора 25 - сигнал S,, 1Сг:юч 15 пропускает на другие входь; с.угтма- тора 25 сигнал с выходов перемножителя 215 на входы перемножителя 24 проходят сигналы с выходов сумматора 25 Ч13ре:; ключ 17 и с выходов праобразова- 28 через ключ IB В результате jia выходах перемножителя 24 получают

SeXfe S, „

значение у. -:--„, Это значение

О,

записывается в блок 20 памяти

На тестом такте декодирования определяют значение ошибки у

При этом ключ 13 пропускает с выходов блока 20 памяти на входы пере ножителя 21 сигнал х, и на выходах перемножителя 24 получают значение

SoX, + S( у р , которое записывают

в блок 20 памяти.

Таким образом, за шесть тактов декодирования вычислитель 5 определяет локаторы ошибок х и х и значения ошибок у, и у , которых достаточно для коррекции символов принятого кодового слова.

Коррекция осуществляется блоком 7 внесения поправок, который работает следующим образом.

На входы сумматора 2 подают задержанные символы принятого слова с выхода накопителя 1. Одновременно с приходом каждого задержанного символа принятого слова генератор 49 элементов поля Галуа формирует локатор этого символа, и этот локатор поступает на входы элемента 48 сравнения, на вторые входы которого подают определенные вычислителем 5 локаторы ошибок. Элемент 48 формирует сигнал управления ключом 47 при совпадении локатора ошибок с локатором символа принятого слова. Ключ 4 при этом пропускает сигнал значения ошибки, который подают на его информационные входы с вычислителя 5, на вторые входь сумматора 2. Сумматор 2 формирует скорректированное

значение символов, которые посту

пают на выходы 11 устройства.

Блок управления 30 вычислителя 5 работает следуюпщм образом.

По стартовому импульсу с входа 61, поступающему на S-вход триггера 56, последний устанавливается в единицу и открывает элемент 58 И, при этом тактовая синхросетка через открытый элемент 58 И поступает на счетный вход счетчика 55, который формирует три разряда адреса ПЗУ, на котором выполнен распределитель 54 импульсов. Четвертый и пятый адресные разряды, поступающие на адресный входы этого ПЗУ с выхода элемента 57 ИПИ и со входа 60, определяют режим формирования сигналов управления и тем самым режим работы вычислителя 5,

Если в принятом слове ноль ошибок то на четвертом и пятом адресных

87297 В

входах распределитпл.ч 54 устанавливается комбинация 10 и на выходы 53 выдаются определенные для этого реямма сигналы управления. Если в принятом слове одна ошибка, .то на четвертом и пятрм адресных входах распределителя 54 устанав- ли ается комбинация 01 и на выходы 63 выдаются в течение двух тактов два

10 определенных для этого режима сигналы управления.

Если в принятом слове более одной ошибки, то на четвертом и пятом адресных входах распределителя 51 устанав15 ливается комбинация 11 и на выходы 63 выдаются в течение шести тактов шесть определенных для этого режима символов управления,

В момент заполнения счетчика 55 в

20 нем формируется и выдается сигнал, поступаюшр й на R-вход триггера 56, При этом триггер 56 перебрасьгаается в состояние нуль и блокирует поступление тактовой синхросетки на вход

5 счетчика 55. Счетчик 55 при этом автоматически обнуляется.

Работа блока 6 выбора режима основана на том, что квадратное уравнение вида Z + Z + а О имеет решение

в поле Галуа (2 ) тогда и только тогда, когда tp (а) О, где

m-t

t(a)

При представлении элементов поля Галуа (2) в виде разложения по нормальному базису (табл. l) значение tp (а) можно получить, сложив по модулю два все разряды полученного в

двоичном представлении на третьем такте декодирования значения а. Это действие осуществляет сумматор 42 по модулю два, причем результат этого действия запоминается триггером 43.

Процедуру декодирования рассмотрим на примере декодирования нулевого кодового слова г (о i «-г,4) двумя ошибками в нулевой и второй

позициях, нулевая позиция символа есть позиция младшего разряда, т,е, зто последний приходящий символ слова, причем значение ошибки в нулевой позиции равно iX°, а во второй позиции

равно О|1(табл. 1).

Блок 3 вычисления синдрома опредеяет сигнал четырех синдромов S, S,, S, 83 в соответствии с выражениями

Для данного примера значения гннл- .

ромов равны

(х:

Значения синдромов поступают в вычислитель 5.

Перемножитель 23 и сумматор 26 определяют значение Л 06 0. Блок 30 управления анализирует значение U и определяет, что в слове произошло две ошибки. На выходах перемпожителя 21 получаем значение

р oi

3

а на выходах перемножителя

22 - значение S, S о(, сумматора 25 - значение + S,

Ы

Значение л

на выхода

о oi пода Г э

ется на преобразователь 28, с выходов которого значение (л) приходит на ВХОДЫ перемножителя 24j на вторые входы которого приходит значение

S,

;

На выходах

перемножителя 24 получается значение GI (Б„ . S + S,-- S,)/u ( которое записывается в блок 20 памяти.

Затем ключ 14 пропускает на выходы значение S, а ключ 15 - значение

Э и.на выходах перемножителя 24

получается значение G j

+ S;

)/ u (о.-(У.+ )/pi

которое записывается в блок 20 памяти.

Затем ключ 17 пропускает на свои

выходь значение СУ, с выходов блока

J 20 памяти, а ключ 16 - значение О ,

В результате на выходам перемножителя 24 получают значение а б. /(j , 14

в виде двоичной после J I f и ( L

в виде двоичной последо- od. Зна CX ,, . , довательности oi. | 100 i ; и на выходах преобразователя 29 получают значение z

вательности 0001, т,е„ z

я

чение Z , записывают в блок 20

памяти, и затем через ключ 17 подают на входы перемножителя 24, на вт С рые входы которого через ключ 19 подают значение G Ы , В результате на выходах перемяожителя 24 получают значение х , 6 z , - сх . oi сх .

Kivrrjpoe. non;-U-;T r.H на сумматор 27, па рп опые пход1 1 которп1-о с выходгж бло- кп 20 памяти подают значение б, На выходах сумматора 27 получают

г

,9

значение х

G, + X,

Л

и к,, ГА.

+ л «..

записыЗначенил х , и

впют в блок 2П памяти.

Затем ключ 13 пропускает на выходы сигнал X, oi с выхо Дов блока

памяти.

2 и на

выходах перемножи5

0

5

0

5

0

5

0

5

.

теля ZI получают значение у, .о(. Ы , которое через ключ 15 проходит на входы сумматора 25, на пторые входы которого через ключ 6 подают значения ;, , На выходах сумматора 25 получают значение о.х +

R f, Dо

- Я/ (У. + oi (Х- , которое поступает через ключ 17 на входы перемножи- ГЙ.ЛЯ 24. На вторые его входы подают г)ерез ключ 19 сигнал с выходов преобразователя 28J на входа которого через 18 подают значение Cj, СУ. с выходов блока 20 памяти. На выходах перемножителя 24 получают значение

ошибки V и

(Я,

Q /5

L-, ; о - т csi

(X , которое таписьшают в блок 20 памяти.

Затем на входы перемножителя 21 через ключ 13 подают значение х. - oi при этом на выходах сумматора 25 получают значение

b

+ (У .

X

+ S ь

на выходах перемножителя

У, (5„х, S,)/6, - У. /v: СУ, , которое записывают в блок 20 памяти.

Таким образом, в блоке 20 памяти ;;лписаны локаторы ошибок х, oi и .х (V, и значения ошибок у, о и

о

; - УЗатем с имволы принятого слова из буферного накопителя 1 подают на вхо- сумматора 2, а значения локаторов Xj и Xj - на входы элемента 48 сравнения, а значения ошибок у, и у - на входы ключа 47, при этом генератор 49 элементов поля Галуа вырабатывает локатор символа принятого слова, проходящего на первые входы сумматора 2. Локатор нулевой позтщии символа принятого слова равен л/ , второй позиции - и . При совпадении локатора нулевой ггознции к ° со значением х к сигнал с выхода элемента 4 крынает ключ 47 для значения у,, , п при совпадетши локатора второй по- .иции У со значением х , а , - для

значения у -у , Знлченмя у, «:

с

и ; , - сУ cyMS HpvK i (.4 а сумматоре

I ;« значениями принятых симв;гпов в нулевой позиции af, и второй позиции (У , в резуль гате чего на выходах 1 1 устройства получают продекодированно слово - нулевое слово.

В качестве примера работы блока 6 выбора режима рассмотрим декодирование нулевого слова с ошибками в нулевой, первой и второй позициях, равными об , Ос , сх соответственно.

Значения синдромов в этом случае равны So rt ; S, ы ; S oi S , Sj o/

Значения коэффициентов Q , и равны cr, ex , 6, oi .

Величина a, вычисляемая на третьем такте декодирования, равна а G, /б

(Vi« .od

На третьем такте декодирования сумматор 42 по модулю два определяет ве- личину tr (а)

tr (а) tr (oi) - ,„ а, - 1 .

Оигнал величины tr (oi) запоминается триггером 43, а так как этот сигнал равен логической единице, он сиг нализирует, что комбинация ошибок в принятом слове не может быть проде- кодирована.

Выходной сигнал триггера 43 поступает на выход 12 устройства. Таким образом повышается достоверность декодирования принятой информации. Реализация в вычислителе 5 алгоритма, отличного от процедуры Ченя, сокращает общее время декодирования в 1,8 раза.

Формула изобретения

1. Устройство для декодирования линейных кодов, содержащее вычислитель локаторов и значений ошибок, буферный накопитель, выходы которого подключены к соответствующим первым входам сумматора, выходы которо

го являются первыми выходами устройства информационные входы буферного накопителя объединены с соответствующими информационными входами блока вычисления синдромов и являются

информационными входами устройства, выходы блока вычисления синдромов соединены с соответствующими входами дешифратора нуля, тактовые входы буферного накопителя и блока вьмисле- ния синдромов объединены и являются тактовым входом устройства, отличающее ся тем, что, с

5

О

-5

25

35

40

45

50

55

;слью попьш1епия Л(к-торррнп(-ти информации и быстродеГю.твпя устрс Лстна, в нет о введены блок ныбпра режнмя и блок внесения поправок, выходы которого подключены к соответстпутощим вторым входам сумматора, выход блока- вычисления сиидро юв соединены с соответствующими информационными входами вычислителя локаторов и значений ошибок, первые н вторые выходы которого подключены к соответствующим информационным входам блока внесения поправок, выход дешифратора нуля соединен с контрольным входом вычислителя локаторов и значений ошибок, третьи и четвертый выходы . которого подключены соответственно к первым и второму входам блока выбора режима, тактовые входы блока внесения поправок и вычислителя локаторов и значений ошибок объединены и подключены к тактовому входу устройства, управляющий вход вьми- слителя локаторов и значений ошибок является управляющим входом устройства, выход блока выбора режима является вторым выходом устройства.

2, Устройство по п. 1, отличающееся тем, что вычислитель локаторов и значений ошибок выполнен на ключах, блоке памяти, сум маторах, перемножителях, преобразователях кода и блоке управления, выходы первого и второго ключей соединены с соответствующими первыми входами соответственно первого и второго перемножителей, выходы которых подключены к соответствующим первым информационным входам соответственно третьего и четвертого ключей, выходы которых подключены соответственно к первым и вторым входам первого сумматора, выходы которого соединены с соответствующими первы ш информационными входами пятого ключа, выходы третьего перемножителя подключены к соответствующим первым входам второго сумматора, выходы которого соединены с соответствующими первыми входами

. блока управления и первыми информационными входами шестого ключа, выходы которого через первый преобразователь кода соединены с соответствующими первы П1 информационными входами седьмого ключа, выходы пятого и седьмого ключей соединены соответственно с первыми и вторыми входами четвертого перемножителя, выходы которого

подключены непосредстветшо к соответствующим первым входам третьего сумматора и первым информационным входам блока памяти и через второй преобразователь кода - к вторым информацион- ным входам блока памяти первые и вторые выходы которого соединены с соответствующими втopы ш информационными входами соответственно первого и пятого ключей, третьи выходы бло- ка памяти соединены с соответствующими вторыми информационными входамя шестого и седьмого ключей, четвертые выходы блока памяти подключены к соответствующим вторым входам третьего сумматора, выходы которого соединены с соответствующими третьими информационными входами блока памяти, первый - шестой выходы блока управления соединены с соотв.етствующими управ- ляющими входами блока памяти, второй выход блока управления соединен с управляющими входами второго и третьего Ключей, третий выход блока управления соединен с первыми управляющими вхо дами пятого и шестого ключей, четвертый выход блока управления соединен с вторым управляющим входом лятого и управляющим входом седьмого ключей, пятый и шестой выходы блока управле- кия соединены соответственно с первым и вторым управляющими входами первого и четвертого, вторым и третьим управляющими входами шестого и третьим и четвертым управляющими входами пятого ключей, четвертые информационные входы блока памяти, вторые инфор- г-1ационные входы первого ключа, первые входы третьего перемножителя и третьи информационные входы шестого ключа .объединены и являются первыми информационными входами вычислителя, вторые входы вторых перемножителя и сумматора, вторые информационные входы четвертого и третьи информационные входы пятого ключей объединены и являются вторыми информационными входами вычислителя, вторые информационные входы второго и третьего ключей и вторые входы третьего пере- множителя объединены и являются третьими информационными входами вычислителя, вторые информационные входы первого и второго ключей объединены и являются четвертыми информационны- ми входами вычислителя, второй, третий и четвертый входы блока управления являются соответственно контрольным, управляющим и тактовым входами вычислителя, пятые и шестые выходы блока памяти являются соответственно первыми и вторыми выходами вычислителя, выходы четвертого перемножителя и третий выход блока управления являются соответственно третьими и четвертым выходами вычислителя.

3,Устройство по п. , о т л и- ч а ю щ е е с .я тем, что блок выбора режима выполнен на триггере и сумматоре по модулю два, выход которого соединен с первым входом триггера входы сумматора по модулю два и второй вход триггера являются соответственно первыми и вторым входами блока, выход триггера является выходом блока,

4,Устройство по п« , отличающееся тем, что блок внесения поправок выполнен на ключе, элементе сравнения и генераторе элементов поля Галуа, выходы которого соединены с соответствующими первыми входами элемента сравнения, выход которого соединен с управляющим входом ключа, информационные входы которого и вторые входы элемента сравнения являются соответственно первьп- И и вторыми информационными входами блока, вход генератора элементов поля Галуа является тактовым входом блока, выходы ключа являются выходами блока.

5,Устройство по п. 2, о т л и- чающеес я тем, что блок управления выполнен на распределителе импульсов 5.триггере, счетчике, элементе 1-ШИ и элементе И, выход которого соединен с счетным входом счетчика, выходы разрядов которого подключены к соответ ствующим первым входам распределителя импульсов, выход элемента ИЛИ соединен с вторым входом распределителя импульсов, выход переполнения счетчика соединен с первым входом триггера, выход которого подключен к первому входу элемента И, ВХО/1Ы элемента ИЛИ, третий вход распределителя импульсов, второй вход элемента И и второй вход триггера являются соответственно первыми, вто- рыМэ третьим и четвертым входами блока, выходы распределителя импульсов являются выходами блока.

й f

«M

«5

50

Фг/г. 3

Л

47

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для декодирования кодов Боуза-Чоудхури-Хоквингема | 1982 |

|

SU1168946A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для декодирования кодов Рида-Соломона | 1985 |

|

SU1309317A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для декодирования кода Рида-Соломона /15,12/ | 1985 |

|

SU1290540A1 |

| Вычислитель ошибок помехоустойчивого декодера | 1985 |

|

SU1295532A1 |

Изобретение относится к вычислительной технике. Его использование в системах обработки и передачи цифровой информации позволяет повысить достоверность декодируемой информации и быстродействие устройства, которое содержит буферный накопитель 1, сумматор 2, блок 3 вычисления синдромов, дешифратор 4 нуля и вычислитель 5 локаторов и значений ошибок . Благодаря введению блока 7 внесения поправок и блока 6 выбора режима, а также соответствующего выполнения вычислителя 5 обеспечивается формирование сигнала отказа от декодирования в случае неисправимых ошибок, а также сокращение времени вычисления поправок, 4 з.п.ф-лы, 6 ил., 1 табл. Я 0 Х чд 12 фиг.1

51

5Z

we. 5

«

Составитель О, Тюрина Редактор Т. Парфенова Техред Л.Сердюкова Корректор С. Шекмар

Заказ 7730/59

Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

6

ф

Фиг.6

| Патент США № 4142174, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-13—Подача