ченм со i зе сгненно к шине нулевого потенциала, первому входу первого сумматора по модулю два группы и выходом всех сумматоров по модулю два группы, выход-1 кольцевого регистра сдвига и третьего преобразователя кода подключены соответственно к третьим и четвертым информационным входам второю мультиплексора, о т - личаюгцееся тем, что, с целью повышения достоверности устройства, в него введены элементы ИЛИ и блок ключей, в вычислитель локато- ров и значений ошибок введены четвер тый-шестой преобразователи коца$ третий блок памяти, первый и второй триггеры, второй элемент И и второй дешифратор, входы которого и первые входы кольцевого регистра сдвига

объединены и подключены к выходам триггеров группы, выход первого дешифратора подключен к первому входу второго элемента И, выход которого соединен с установочным входом счет- чика, выход второго дешифратора подключен к S-входу второго триггера, .прямой выход которого соединен с вторым входом второго элемента И, вход обнуления счетчика и R-входы

первого г второго триггеров объединены и подключены к входу Сброс устройства, входы четвертого, пятого и шестого преобразователей кода подключены к выходам соответственно пер- вого и второго блоков памяти и счет- чшса, вьгходы четвертого преобразователя кода подключены соответственно к первому входу первого и вторым входам всех сумматоров по модулю два

группы и к четвертым информационным входам первого мультиплексора, выходы третьего блока памяти и пятого преобразователя кода соединены с пятыми информационными входами соответственно первого и второго мульти- плексоров, вых:од первого триггера соединен с вторым входом первого элемента И, первые выходы шестого преобразователя кода соединены с вторыми входами кольцевого регистра сдвига вторые выходы шестого преобразователя кода подключены к вторым управляющим входам вычислителя элементарных симметрических функций, управляющий выход которого соединен с S-входом первого триггера вычислителя локаторов и значений ошибок, первые и вторые информационные выходы вычислителя Элементарных симметрических функций подключены к гаестым информационным входам соответственно первого и второго мультиплексоров, вычислителя локаторов и значений ошибок, третий выход первого преобразователя кода вычислителя локаторов и значений ошибок и второй выход дешифратора ошибок соединены с входами элемента ИЛИ, выход которого подключен к управляющему входу блока ключей, второму управляющему входу буферного накопителя и является контрольным выходом устройства, информационные входы блока ключей подключены к выходам блока сумматоров по модулю двд, выходы блока ключей являются соответствующими информационными выходами ;отройст- ва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для вычисления локаторов ошибок | 1990 |

|

SU1728972A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для декодирования кода Рида-Соломона /15,12/ | 1985 |

|

SU1290540A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| ВЫЧИСЛИТЕЛЬ ОШИБОК ПОМЕХОУСТОЙЧИВОГО ДЕКОДЕРА | 1999 |

|

RU2152130C1 |

Цель изобретения - повышение достоверности устройства. Устройство содержит запоминающий блок, буферный накопитель, генератор синдромов, накопитель синдромов, дешифратор ошибок и блок сумматоров по модулю два. В устройство введены элементы ИЛИ и блок ключей, в вычислитель локаторов и значений ошибок введены четвертый - шестой преобразователи кода, третий блок памяти, первый и второй триггеры, второй элемент И и второй дешифратор.

Изобретение относится к вычислительной технике и может использоваться i; системах хранения, пере дачи и обработки информации,

Цель изобретения - повышение дос- товернос и декодирования.

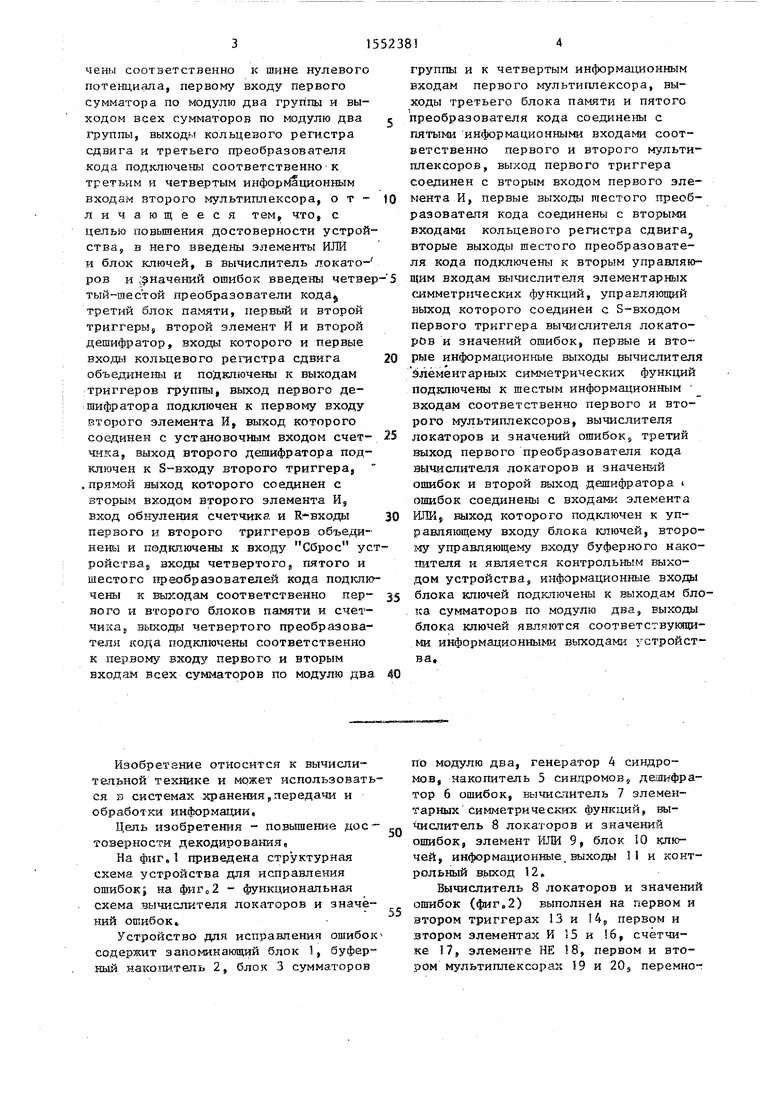

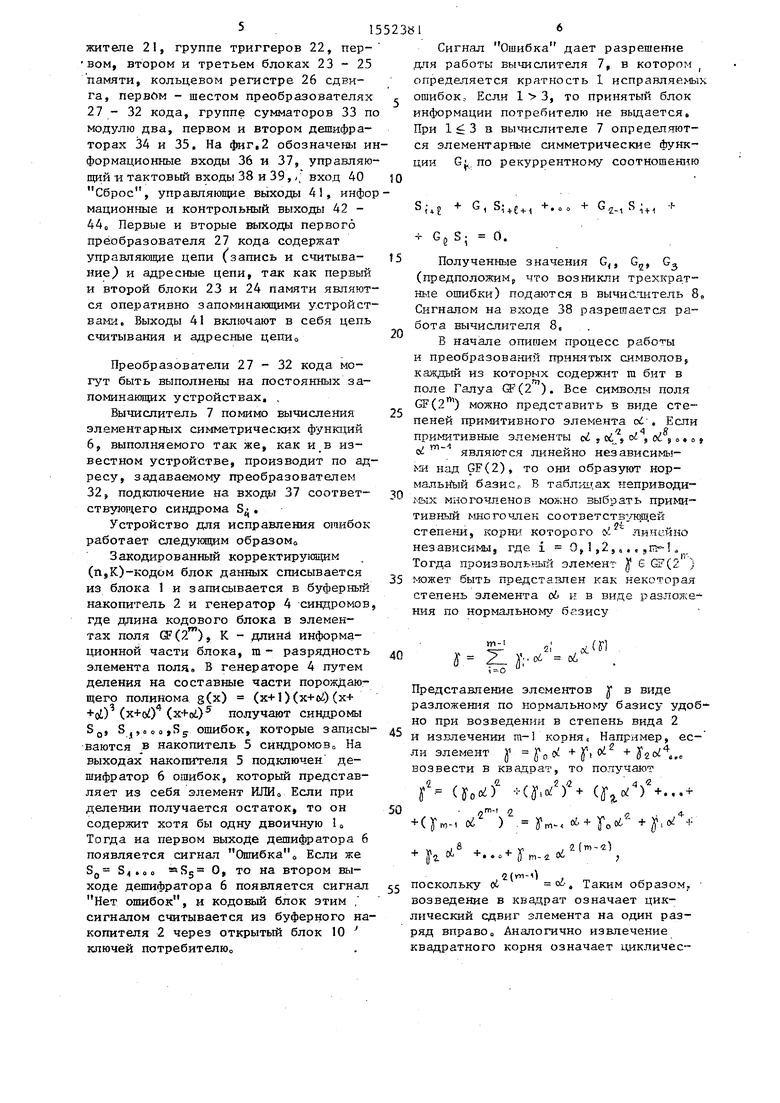

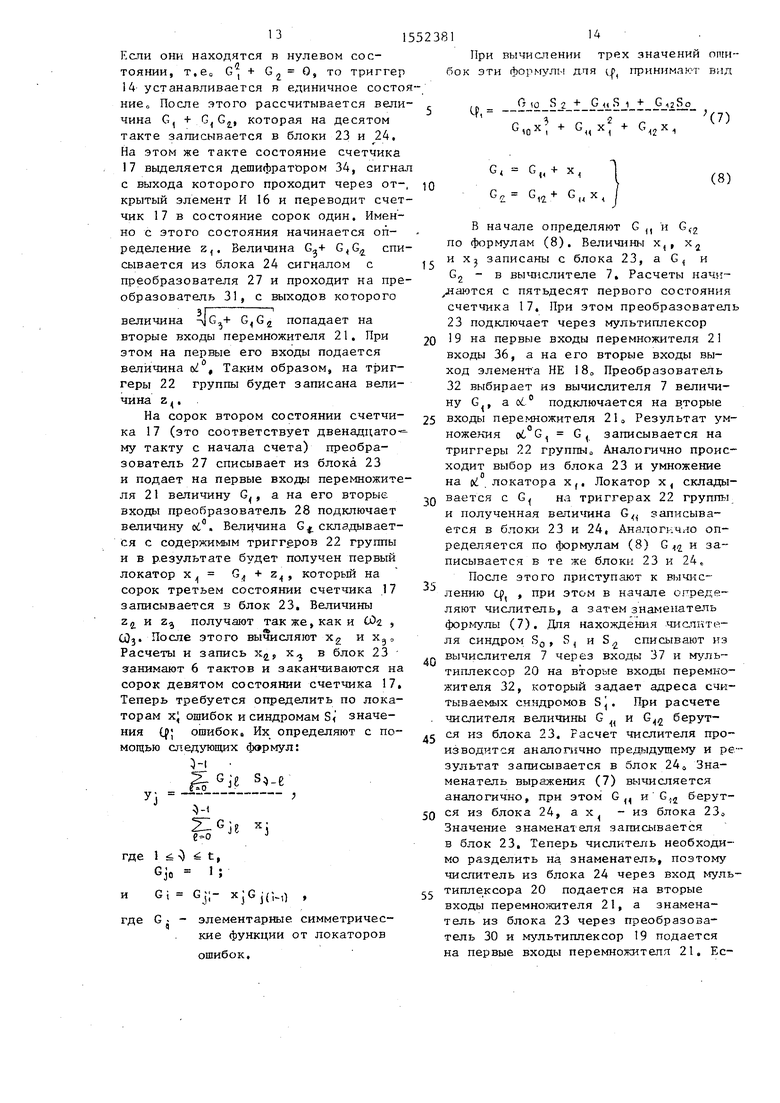

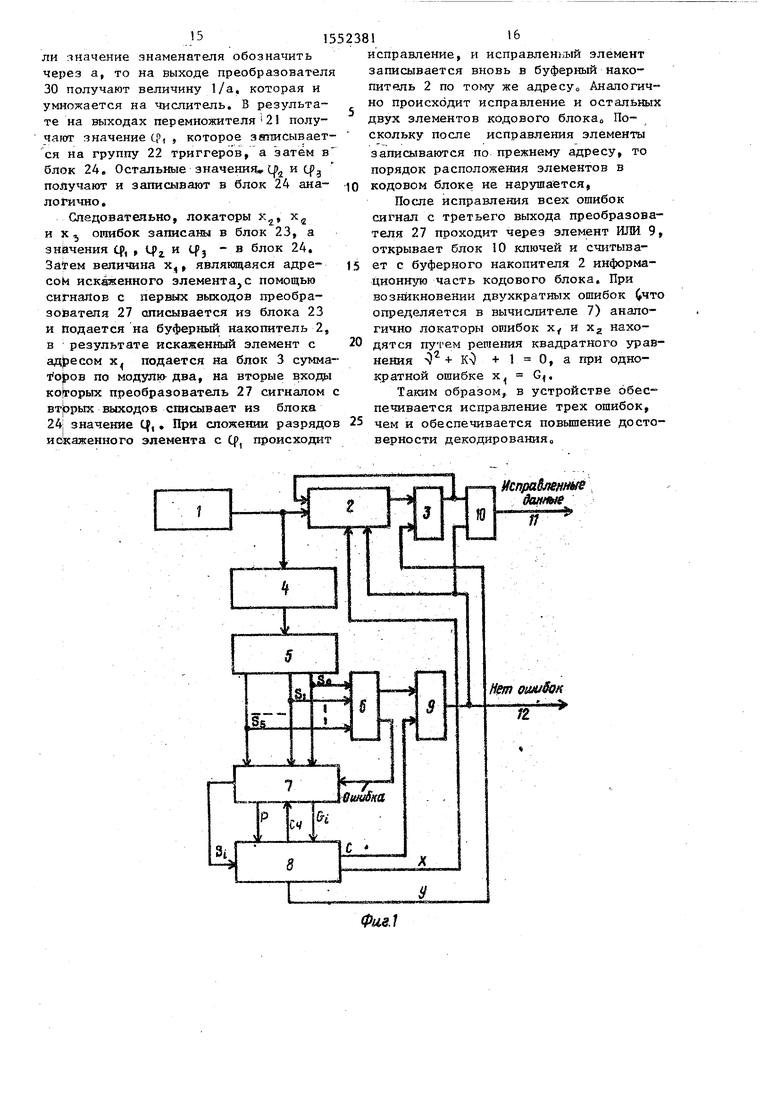

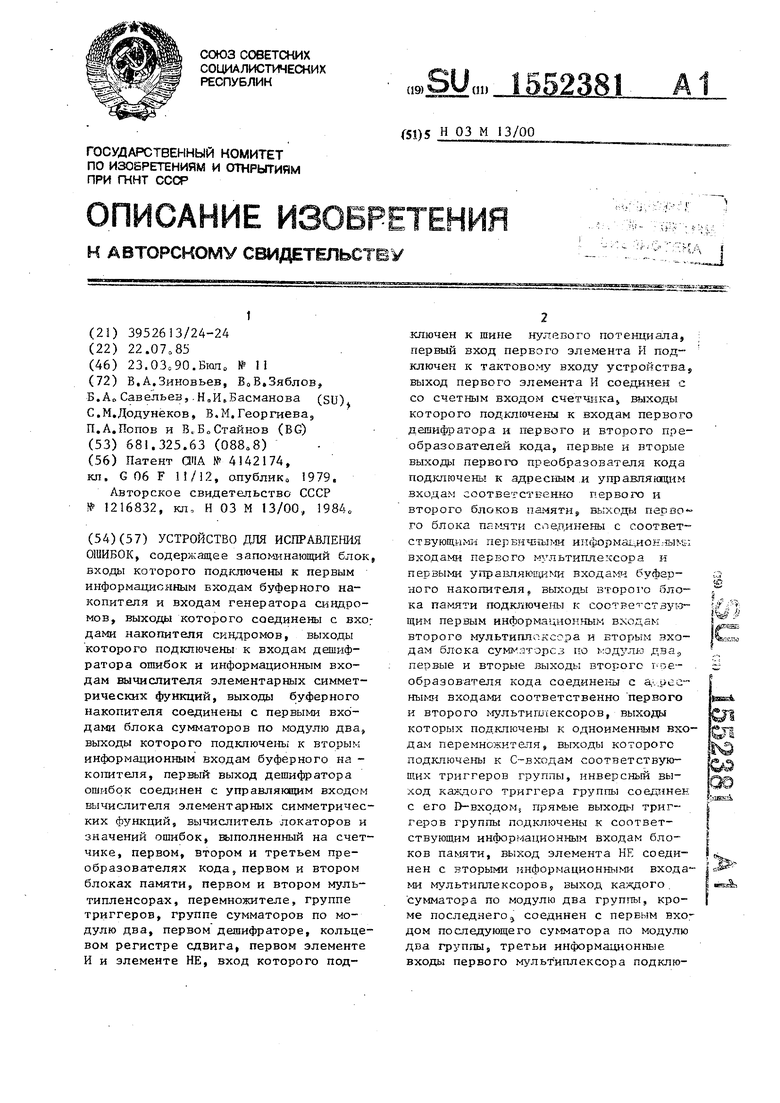

На фнг.1 приведена структурная схема устройства для исправления ошибок; на фиг„2 - функциональная схема вычиглителя локаторов и значений ошибок.

Устройство для исправления ошибок содержит запоминающий блок 1, буферный накочитель 2, блок 3 сумматоров

по модулю два, генератор 4 синдромов, накопитель 5 синчромов, дешифратор 6 ошибок, вычислитель 7 элементарных симметрических функции, вы- числитель 8 локаюров и значений ошибок, элемент ИЛИ 9, блок 10 ключей, информационные.выходы 11 и контрольный выход 12.

Вычислитель 8 локаторов и значений ошибок (фиг.2) выполнен на первом и втором триггерах 13 и 14, первом и втором элементах И 15 и 16, счетчике 17, элементе НЕ 18, первом и втором мультиплексорах 19 и 20, перемно5

515523

жителе 21, группе триггеров 22, пер20

вом, втором и третьем блоках 23 - 25 памяти, кольцевом регистре 26 СДРИ- га, первом - шестом преобразователях , 27-32 кода, группе сумматоров 33 по модулю два, первом и втором дешифраторах 34 и 35. На фиг.2 обозначены информационные входы 36 и 37, управляющий и тактовый входы 38 и 39 ,, вход 40 Ю Сброс, управляющие выходы 41, инфор- мацношше и контрольный выходы 4 - 44„ Первые и вторые выходы первого преобразователя 27 кода содержат управляющие цепи (запись и считыва- 15 ние,) и адресные цепи, так как первый и второй блоки 23 и 24 памяти являются оперативно запоминающими устройствам:. Выходы 41 включают в себя цепь считывания и адресные цепи

Преобразователи 27-32 кода могут быть выполнены на постоянных запоминающих устройствах.

Вычислитель 7 помимо вычисления25

элементарных симметрических функций 6, выполняемого так же, как и в известном устройстве, производит по адресу, задаваемому преобразователем 32, подключение на входи 37 соогвет- чп ствукнчего синдрома S,; .

Устройство для исправления ошибок работает следующим образом

Закодированный корректирующим (п,К)-кодом блок данных списывается из блока 1 и записывается в буферный накопитель и генератор 4 синдромов, где длина кодового блока в элементах поля GF(2 ), К - длинй информационной части блока, m - разрядность элемента поля. В генераторе 4 путем деления на составные части порождающего полинома g(x) (х+1)(х+0ч) (х+ +oi) (х+Ы)4 (x+oi)5 получают синдромы

Сигнал Ошибка дает разрешение для работы вычислителя 7, в котором определяется кратность 1 нспрпвлчгмыч ошибок Если 1 3, то принятый блок информации потребителю не выдается. При 1 Ј 3 н вычислителе 7 определится элементарные симметрические функции GL по рекуррентному соотношению

- G

+ G i SUE-M +- О.

GЈ-iS1+,

2s;

Полученные значения G,, G, G (предположим, что возникли трехкоат- ные ошибки) подаются в вычисчитепь 8, Сигналом на входе 38 разрешается работа вычислителя 8.

В начале опишем процесс и преобразований принятых символов, каждый из которых содержит m бит в поле Галуа GF(2 ). Все CHMBOTI пол ч GF(2m) можно представить в виде степеней примитивного элемента оЈ . Кепи

примитивные элементы сЈ , of. 1, , ofg, , а t I m-i

«являются линейно независимыми нлд GF(2), то они образуют нор- млпьный базис, В габл птах чеприводи- лчх Многочленов выгорать тинный нcт-pчлeн соответст i -Ksoei

, г

степени, корни которого

независимы, где i О,1,2,,.,, Тогда чpuизвoл riын олегел- ft i СГ(Г 35 ножет быть представлен гак степень элемента об i в виде pa j-oe- ния по нормальному 5, зису

m-i

J

:n

oi об

Представление элементов J в виде разложения по нормальному базису удобно при возведении в степень вида 2

.Я- ошибок, которые записы- ль,

5ц- и извлечении tn-1 корня, Например, еспи элемент у f p gL + Jf, oi +J2o/4,., юзвести в квадрат , то получаю

О S j , в о о

ваются в накопитель 5 синдромоч„ На выходах накопителя 5 подключен дешифратор 6 ошибок, который представляет из себя элемент ИЛИ0 Если при делении получается остаток, то он содержит хотя бы одну двоичную 1„ Тогда на первом выходе дешифратора 6 появляется сигнал Шгибка 0 Если же S0 S.oo «Sg3 0, то на втором выходе дешифратора 6 появляется сигнал Нет ошибок, и кодовый блок этим сигналом считывается из буферного накопителя 2 через открытый блок 10 ключей потребителю

50

I (у0ог)

2т 2 + (т , )

ку.г)а +

+ У т-2 , 2(wiav +

2 fm

$г

4) +...+

J, с/

od

)

55

поскольку .. Таким образом, возведение в квадрат означает циклический сдвиг элемента на один разряд вправо о Аналогично извлечение квадратного корня означает цикличесСигнал Ошибка дает разрешение для работы вычислителя 7, в котором определяется кратность 1 нспрпвлчгмыч ошибок Если 1 3, то принятый блок информации потребителю не выдается. При 1 Ј 3 н вычислителе 7 определится элементарные симметрические функции GL по рекуррентному соотношению

+ G i SUE-M +- О.

GЈ-iS1+,

s;

Полученные значения G,, G, G (предположим, что возникли трехкоат- ные ошибки) подаются в вычисчитепь 8, Сигналом на входе 38 разрешается работа вычислителя 8.

В начале опишем процесс и преобразований принятых символов, каждый из которых содержит m бит в поле Галуа GF(2 ). Все CHMBOTI пол ч GF(2m) можно представить в виде степеней примитивного элемента оЈ . Кепи

примитивные элементы сЈ , of. 1, , ofg, , а t I m-i

«являются линейно независимыми нлд GF(2), то они образуют нор- млпьный базис, В габл птах чеприводи- лчх Многочленов выгорать тинный нcт-pчлeн соответст i -Ksoei

, г

степени, корни которого

независимы, где i О,1,2,,.,, Тогда чpuизвoл riын олегел- ft i СГ(Г ножет быть представлен гак степень элемента об i в виде pa j-oe- ния по нормальному 5, зису

m-i

J

:n

oi об

0

I (у0ог)

2т 2 + (т , )

ку.г)а +

+ У т-2 , 2(wiav +

2 fm

$г

4) +...+

J, с/

od

)

5

поскольку .. Таким образом, возведение в квадрат означает циклический сдвиг элемента на один разряд вправо о Аналогично извлечение квадратного корня означает циклический сдвиг эпемента на один разряд влево.

Сущность способа и работу устройства рассмотрим при исправлении трех- кратных ошибок, на наличие которых указывает вычислитель 70 Для нахождения локаторов ошибок х,, х2, хэ нужно решить кубическое уравнение

G(x) (х+х,)(х+х2)(х+х5) х3+ G,xV°

+ +

3

где С х,+ х2+ х3,

G2 х, х2+ ,+ х2х

2ЛЭ1

G х,х2хэ.

Корни уравнения хэ + G,x2+ GЈx + и являются локаторами х, х i и х 3 оиибок.

Путем замены х уравнению

G i + z приходят

(С + G2)z + (G3+ G,G2)

Проверяют равенство G( + Если оно удовлетворяется, ют уравнение

О. (О

О то реша -

z3 G}+ G 4 Ga

При га четном поле GF(2 ) содержит все корни третьей степени из 1, поэтому требуется определить только один корень zt последнего уравнения. Остальные корни равны

г oi

oi

2-1/5

Подставляя их в уравнение х Of+ z, находят х,, х2 и х, При G,+ в уравнении (.) делают замену z

(2

AtpCG, GZ) и получают уравнение

ц + (j + к

о

где

„ GJ+ GjG2

Tel Тс /

Производят еще две замены

Q +

и оо N . В результате получают уравнение г + KV 1 0, которое приводится к каноническому виду заменой KU(„ В результате получают

ч

Если обозначить )f окончательно получают

При га четном требуется определить только один корень последнего уравнения, который равен

u, (o.jf.. У + Ь + ут., .

у.+у«

(5)

где У, - разряды элемента поля GF(2m).

По U, находят СА),

Остальные корни, поскольку поле GF(2) содержит корни третьей степени из единицы, равны

25

W2 U,ot

С0} С02 oi

По корням СО, , 0г , СО 5 находят корни х(, хг, хэ исходного уравнения

30 (I):

х

03

G4 +(G| + Gfy (со

+ «V ).

(6)

35

40

45

50

55

Эти корни и являются локаторами ошибок. Итак, локаторы х(, х и х3 ошибок определяются в вычислителе 8, работу которого рассматривают при m 8. По сигналу на входе 38 в вычислителе 8 срабатывает триггер 13 который открывает элемент И 15 и на счетчик 17 подаются тактовые импульсы с входа 39.

Расчет начинается при проверке равенства G 2. - 0. На первом такте состояние счетчика 17 попадает на преобра- зователи 28 и 32. Преобразователь 28 подключает на первые входы перемножителя 21 через мультиплексор 19 входы 36, а на вторые входы через мультиплексор 20 - выход элемента НЕ 18,, Преобразователь 32 по своим выходам 4 41 подает в вычислитель 7 адрес, по которому записана величина G, и сигнал ее считывания„ В результате на первые входы перемножителя 21 подается величина G, на вторые - ьЈ

9

I. Поэтому на выхоце перемножителя 21 получают величину Ы. Г,, - С( , которая записывается на триггеры 22 группы. Триггеры 22 работают в режи- ме счета по модулю два, для чего инверсный выход каждого из них соедине со своим С-входом.

Из втором такте величина GJ переписывается с триггеров 22 группы в firioK 24 с помощью сигнала записи ч пи адресу, задаваемым с вторых выходов преобразователя 27. На третьем такте преобразователь 28 подключает через мультиплексор 20 на вторые

входы перемножителя 21 выходы блока 24, на который подается одновременно сигнал считывания преобразователя 27 а на первые входы остается подключенной величина С,. Преобразователь 32 считывает из вычислителя 7 величину GJ, которая и подается на первые входы перемножителя 2 i, на вторы входы которого из блока 24 списывается величина С.. На выходах перемно- жителя 21 получено произведение G4 G,, G,, которое записывается на триггеры 22 группы.

Ча четверто такте преобра ова- тель 32 подает на первые входы пере- множителя 21 величину G2, а преобразователь 2Ь подключает на его вторые вход величину с о Полученное произведение od n + G2 G2 складывается по модулю два с величиной С,, хранящейся на триггерах 22 группы. В результате получают сумму С + G2 На следующем такте {пятом} проверяют состояние триггеров 22 группы с

2

помощью дешифратора 35. Если G , +

+ G4 О, то сигнапом с выхода дешифратора 35 триггер 14 устанавливается в единичное состояние. Содержимое триггеров 22 группы записывается с помощью сигнала с первого вы- хода преобразователя 32 в регистр 26.

Далае осуществляется вычисление G.+ G Ges На шестом такте преобразователь 32 списывает из вычислителя 7 величину С f и подает ее на первый перемножителя 21, а преобразователь 28 подключает на вторые входы перемножителя 2 через мультиплексор 20 выход элемента НЕ 18, т0е„ вели- чину . На выходах перемножителя 21 получают величину oi G $ G3, которая на седьмом такте переписывается в блок Далее на восьмом и

1Ю

девятом тактах аналогично предыдущему вычисляют значение G9 + Г, Г, , которое на десятом такте аписычается в блоки 23 и 24.,

Предположим вначале, ч-г G + + GЈ40 и необходимо гппеделить локаторы ошибок через урарнение (3)„ Величина G, + G2 была записан-. в регистр 26, ее нужно преобра IB ITJ, в значение ( Г-2) . На отшн -,а- том такте с преобразоватепч 32 по второй цепи на соответствующим vnu-n тяющий вход регистра 26 подается -ьг- нал сдвига влево, в результ ITQ что в регистре 26 получаю Bfmmniv

f/2

(G1 + G2) . Поскольку эта липр, необходима для даль етинх расчет ив, то ее необходимо записать в 23, Поэтому ка двенадцатом такте преобразователь 28 подключает на первые входы перемножителя 21 через мультиплексор 19 выход элемента НЕ 18, я на вторые входы - выходы регистра 26„ В результате на триггерах 22 группы будет записана величина (Gf + G) которая с помощью сигнала с ВЫХОДСР преобразова ге-тя 7.1 на тринадцатом такте зат-сн ается н Тчгк- 33 Операция делания в формуле ( i , ,а екялг г- на операцию умнолетлп и ь/т очроf vi

rt11/)

возведения (С, « C; / , ку .

ОСУЩРСТВЛЯ ТСЯ С П МОЦЬИ вателя 29. Значс ( С - („ г , ч, писанное в регист± t i, ,, (я а/ -- ресом для преобразите t п 2° ь зультате чего на выхода. : псг появляется записи тч т ч нем ич т адресу величина

1

А

(G + С,) Л

На четырнадцатом такте на псрлые входы перемножителя 21 подключаются выводы блока 23, а , пюрые входы - выход преобразователя 29. Преобразователь 27 считывает из блока 23 и подает на перемнсжитель 21 геличину G-+ , а на вторые входы перемножителя 21 подается величина А„ В результате на выходах перемножителя 21 будет получена величина К, которая записывается на группу триггеров 22 и на пятнадцатом такте переписывается в блоки 23 i- 24о

Дальше необходимо получить величину ft 1/К о На шестнадцатом такте

преобразователь 28 подключает на первые и вторые входы перемножителя 21 соответственно выходы блоков 23 и 24у преобразователь 27 списывает из этих блоков величину К, Таким образом, на выходах перем1 жителя 21 получают

л

величину К , которая записывается на группу триггеров 22 и на семнадцатом такте переписывается н блок 23, На следующей восемнадцатом такте преобразователь 28 подключает на первые входы перемножителя 21 шину, содержащую 0 по первой цепи, второй выход преобразователя 30 по второй цепи и выходных цепей группы сумматоров 33 по модулю два, а на вторые входы - величину К из блока 24 Преобразователь 27 сигналом со своей первой выходной шины списывает и:4

Ј

блока 23 величину К , которая является адресом для преобразователя 30, по которому в нем записана величина 1/Кг у „ Эта величина, яа исключением первого разряда, пудает- сч на группу сумматоров 33 по модулю два,содержащую т-2 сумматоров, i

В результате на первые входы пе

ре множителя 2i будет подана величина

U

4

полученная в соответствии с формулой (5), а на вторые входы из блока 2 1 - величина К0 На выходах перемножителя 21 получают величину К U, которая на девятнадцатом такте переписывается Б блок 240

Дальше получают величину сО, о На двадцатом такте преобразователь 28 подключает на первые входы перенножи теля 21 величину Ы. , а на вторые ЕХОДЫ - выходы преобразователя 3L Преобразователь 27 сигналами с вторых выходов выбирает из блока 24 величину К U, , которая задает адрес дл

преобразователя 31, по которому тапи11

сана ве-шчина - KU( 00, „ В результате на вторые аходы перемнолителя подается Q, и на его выходах получают величину oi° СО, w которая записывается на триггеры 22

11

1руппч.

На двадцать первом такте СО, переписывается в блок 23 и остается н.м триггерах 22 группыо На двадцать втором такте на первые входы перемножителя 21 подключаются выходы преобразимте ля 30, а на вторые входы - величина od° . Преобразователь 27 выбирает из Слока 23 величину СО, , которая обеспечивает получение на выходах преоб

разователя 30 величины 1/60,. На выходах перемножителя 21 получают величину 1/СО, i которая складывается по модулю два с величиной G), , записанной , на триггерах 22 группы Полученная сумма СО, - 1/СА, на двадцать третьем Тс-кте переписывается в блок 24Ь

Локатор х, ошибок получают путем вычисления по формуле (.6), величина

/С, + G4)хранится в блоке 230 На

двадцать четвертом такте преобразователь 28 подключает1 выходы блоков 23 и 24 соответственно на первые л вторые входы перемножителя 21, а пре- обрззоьателъ 27 выбирает из них величины СО, + 1/W, и (С G,), Укачанные пеличичч перемножаются и записываются на триггери 22 группы. После этого на ь пятом такте из блока 24 выбирается и подается на первые в.соды гафемножигеля 21 величина G,, л на вторые входы преобразова- 5 т ель 28 подключает величину оСо о Полученная на выходах перемножителя 21 величина G( с лад дваетсл с содержимым триггеров 22 группы, в резуль5

0

тате величина ч

на двадцать шестом

такге переписошаетсн г блок 23,

Для нахождения х требуется вычислить величину СО , которая при m 8 равна Сх) d), - Величина

В5 оЈ записана в блоке 25, а величина

KUf - в блоке 24 о Поэтому на двадцать седьмом такте преобразователь 28 подключает выходы блока 25 на первые входы перемножителч 21„ а выходы блока 24 - на вторые влодьк В результате на выходах перемножителя 21 получают произведение

Wt KU cyL8j

которое записывается на триггегь 22 группы. На двадцать восьмом такте величина 00 записываетсн в блоки 23 и 24 и остается на триггерах 11,

Дальне локатор х,, величина Сх) 5 и локатор х вычисляются аналогично„ Всего на это тратится вместе с за- чисью лх в блок 23 двенадцать тактов. Таким образом, поело сорокового

ха и х,

такта локаторы ч( ются запис1ННЫМИ в блоке 23. В том случае, когда G,+ Gg

оказываО,

корень z находится HJ уравнения (2). На пятом такте дешифратором 35 проверяется состояние руппы триггеров 22.

Кепи они находятся в нулевом сос- ,4

2 -, то триггер в единичное состоятоянии, т.е, G, + , 14 устанавливается ние, После этого рассчитывается величина G, + r Gi которая на десятом такте записывается в блоки 23 и 24. На этом же такте состояние счетчика 17 выделяется дешифратором 34, сигнал с выхода которого проходит через от-, крытый элемент И 16 и переводит счетчик 17 в состояние сорок один. Именно с этого состояния начинается определение z,. Величина Gj+ G,G2 списывается из блока 24 сигналом с преобразователя 27 и проходит на преобразователь 31, с выходов которого

величина G,G2 попадает на вторые входы перемножителя 21. При этом на первые его входы подается величина oZ t Таким образом, на триггеры 22 группы будет записана величина z

На сорок втором состоянии счетчика 17 (это соответствует двенадцатое му такту с начала счета) преобразователь 27 списывает из блока 23 и подает на первые входы перемножителя 21 величину G , а на его вторые входы преобразователь 28 подключает величину Ы.°. Величина Gt складывается с содержимым триггеров 22 группы и в результате будет получен первый

локатор х

ГЧ

-t- z

который на

сорок третьем состоянии счетчика 17 записывается в блок 23. Величины z4 и гъ получают так же, как и СОг , С03. После этого вычисляют х2 и х,, Расчеты и запись хг, х в блок 23 занимают 6 тактов и заканчиваются на сорок девятом состоянии счетчика 17. Теперь требуется определить по локаторам xj ошибок и синдромам S значения (J) ошибок. Их определяют с помощью следующих формул:

Эн

)

где

G G j|- x|G

jli-0

Gi элементарные симметрические функции от локаторов

ошибок.

55238114

При вычислении трех значений пши

ОК ЭТИ формул ДЧЯ (Р ГфИНИМЛЬ ЬИД

Lf,

47)

С, С

(8)

5

0

В начале определяют G п и G,2 по формулам (8). Величины х(, х2 их; записаны с блока 23, a G и G2 - в вычислителе 7. Расчеты начн- лаются с пятьдесят первого состояния счетчика 17. При этом преобразователь 23 подключает через мультиплексор 19 на первые входы перемножителя 21 входы 36, а на его вторые входы выход элемента НЕ 18„ Преобразователь 32 выбирает из вычислителя 7 величину a oi ° подключается на вторые 5 входы перемножителя 21„ Результат умножения o6°G, G, записывается на триггеры 22 группы,, Аналогично происходит выбор из блока 23 и умножение на U локатора х(. Локатор х, складывается с С на триггерах 22 групггч и полученная величина записывается в блоки 23 и 24, А 1ллогкчло определяется по формулам (8) G 2 и -записывается в те же блою: 23 и 24, После этого приступчют к вычислению , при этом в начале . гре;, «- ляют числитель, а затем знаменатель формулы (7). Для нахождения числн - ля синдром S0, S и S списывают г ч вычислителя 7 черьз входы 37 и мультиплексор 20 на второе входы перемпо- жителя 32, который задает адреса считываемых синдромов SJ. При расчете

0

3

0

5

0

5

числителя величины

G « и

42

берутся из блока 23. Расчет числителя производится аналогично предыдущему и ре эультат записывается в блок 24„ Знаменатель выражения (7) вычисляется аналогично, при этом GH и G,2 берутся из блока 24, а х - из блока 23,, Значение знаменателя записывается в блок 23. Теперь числитель необходимо разделить на знаменатель, поэтому числитель из блока 24 через вход мультиплексора 20 подается на вторые входы перемножителя 21, а знаменатель из блока 23 через преобразователь 30 и мультиплексор 19 подается на первые входы перемножителт 21. Еели шачение знаменателя обозначить через а, то на выходе преобразователя 30 получают величину 1/а, которая и умножается на числитель. В результате на выходах перемножителя 21 получают значение t,i , которое записывается на группу 22 триггеров, а затем в блок 24. Остальные значения и cf3 получают и записывают в блок 24 аналогично.

Следовательно, локаторы х2, хг и х ошибок записаны в блок 23, а значения Cf, , (jz и - в блок 24. Затем величина х,, являющаяся адресом искаженного элементаус помощью сигналов с первых выходов преобразователя 27 описывается из блока 23 и подается на буферный накопитель 2, в результате искаженный элемент с адресом х. подается на блок 3 сумма- fopoB по модулю два, на вторые входы которых преобразователь 27 сигналом с вторых выходов списывает из блока

24 значение Cf, . При сложении разрядов 25 чем и обеспечивается повышение досто- искаженного элемента с tp, происходит верности декодирования,,

Si

&L

к

исправление, и исправленный элемент записывается вновь в буферный накопитель 2 по тому же адресу,, Аналогично происходит исправление и остальных двух элементов кодового блока,, Поскольку после исправления элементы записываются по прежнему адресу, то порядок расположения элементов в кодовом блоке не нарушается,

После исправления всех ошибок сигнал с третьего выхода преобразователя 27 проходит через элемент ИЛИ 9, открывает блок 10 ключей и считыва- 5 ет с буферного накопителя 2 информационную часть кодового блока. При возникновении двухкратных ошибок Јчто определяется в вычислителе 7) аналогично локаторы ошибок х, и xz находятся пум ем решения квадратного уравнения Зг + lO + 1 0, а при однократной ошибке х С.

Таким образом, в устройстве обеспечивается исправление трех ошибок,

0

ю

ИспраЬленные

fatttMf

П

Нет ошибок

-

И

| Патент ША № 4142174, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

Авторы

Даты

1990-03-23—Публикация

1985-07-22—Подача