Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки и передачи информации.

Цель изобретения - повышение быстродействия и упрощение устройства.

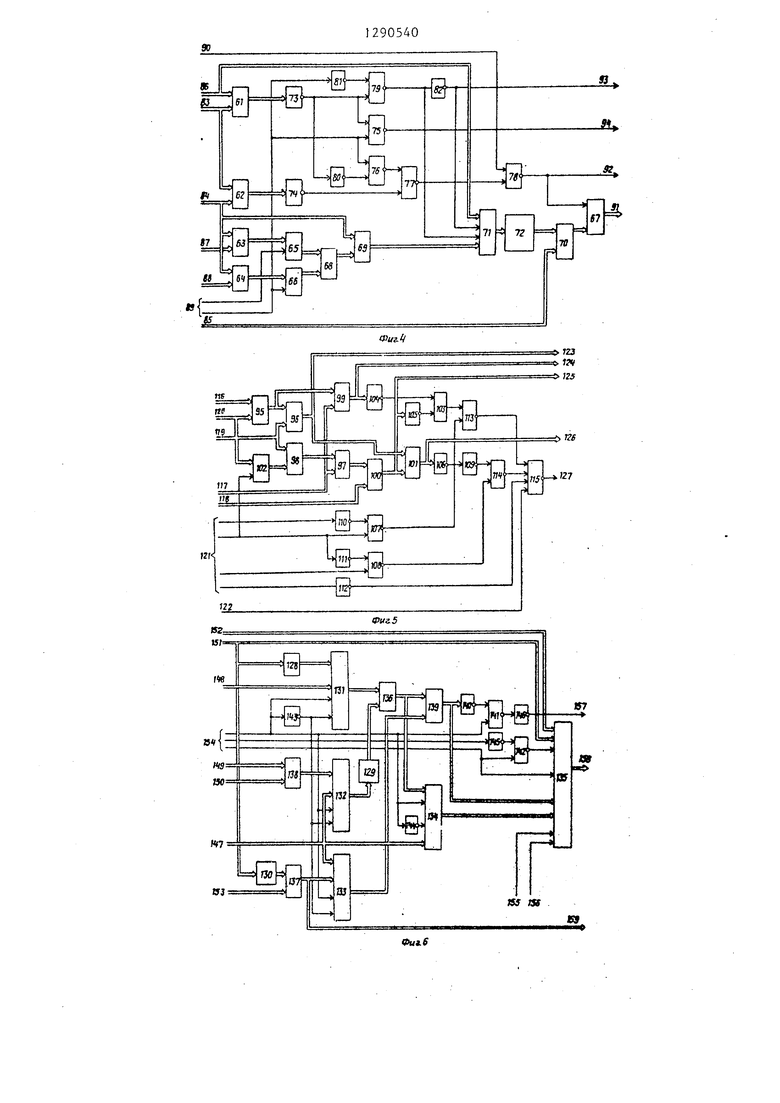

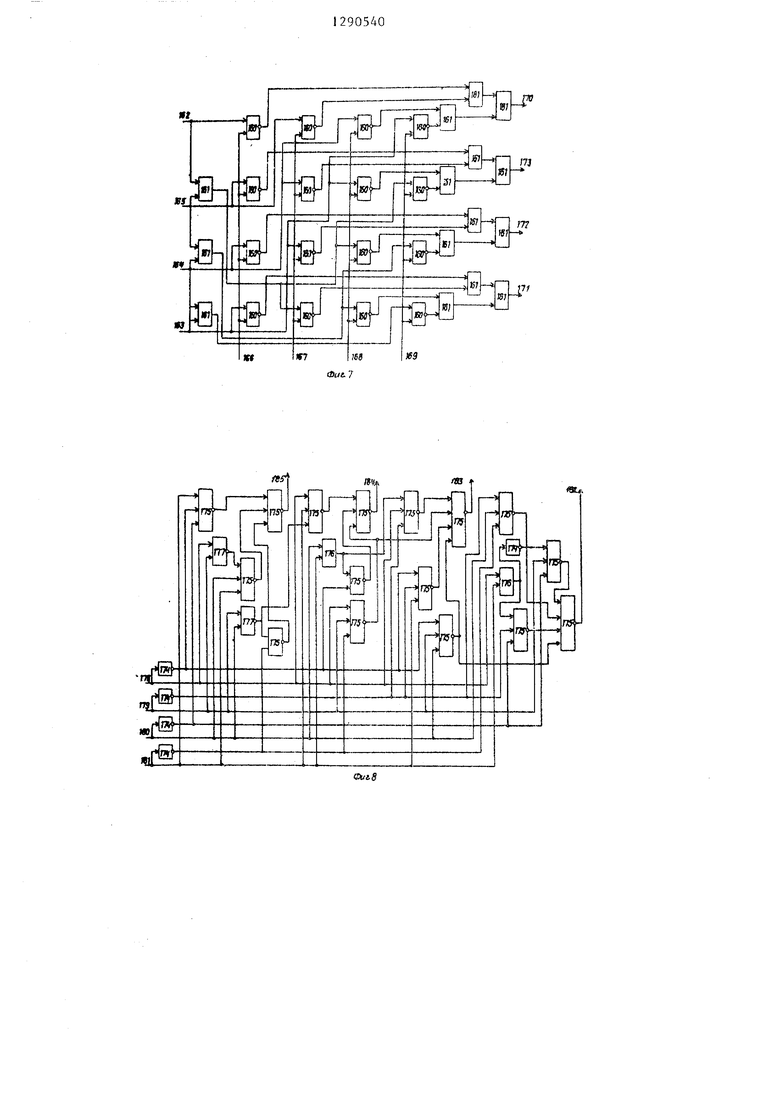

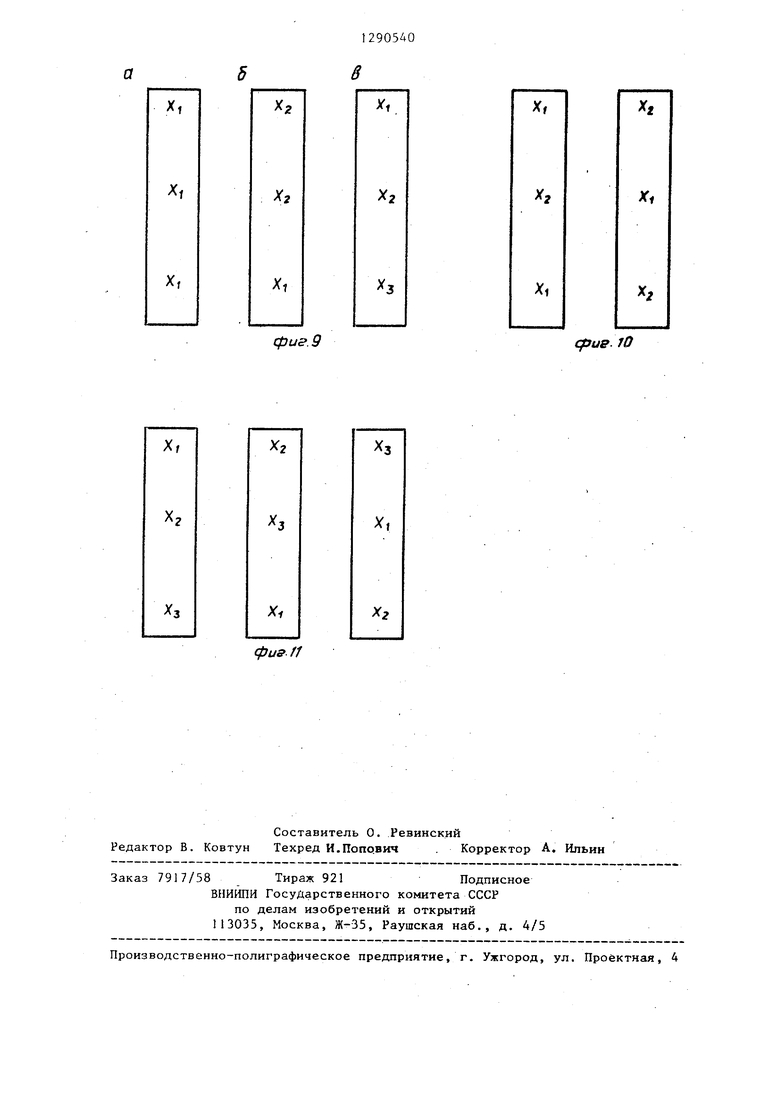

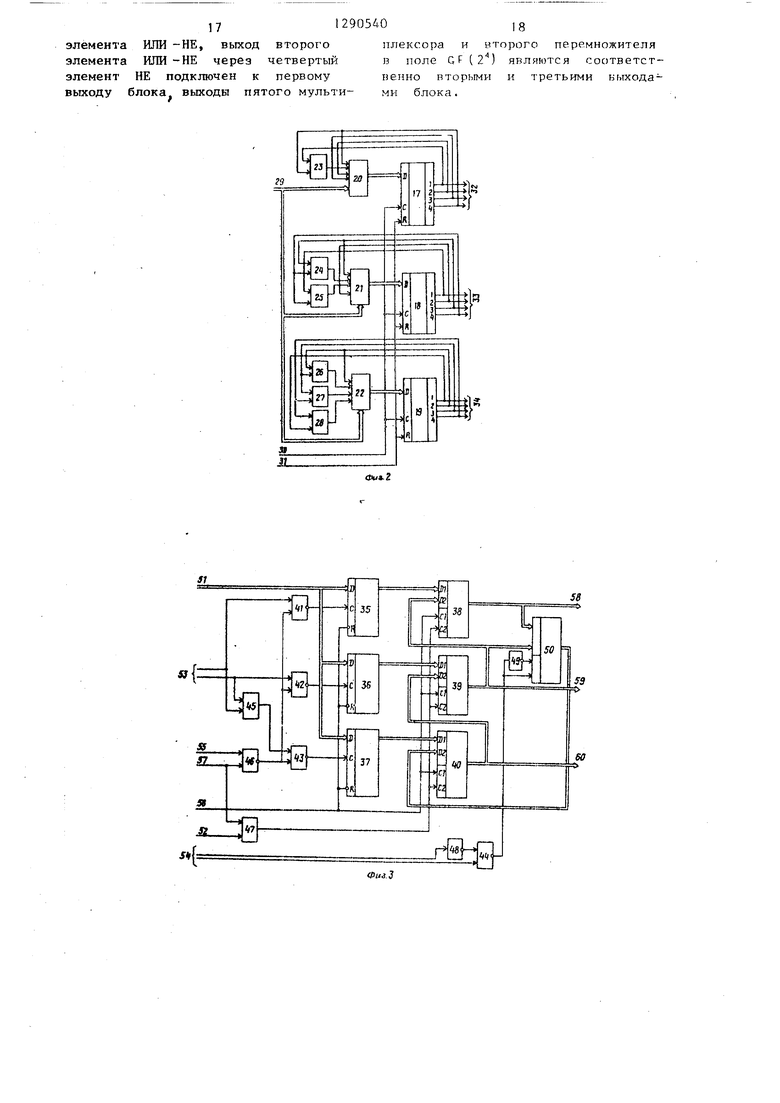

На фиг. 1 приведена блок-схема устройства; на фиг, 2-6 - функциональные схемы соответственно блока вычисления синдромов,- кольцевого блока регистров, блока вычисления поправок, блока выбора режима и блока вычисления локатора ошибки; на фиг. 7 и 8 - принципиальные схемы возможного вьтолнения перемножителя в поле GF(2) и преобразователя в обратный код; на фиг. 9 - порядок записи локаторов стираний в кольцевой блок регистров; на фиг. 10, 11 - порядок сдвига этих локаторов в кольцевом блоке регистров.

Устройство для декодирования кода Рида-Соломона (15,12) содержит первый -блок 1 регистров, сумматор 2, генератор 3 элементов поля GF(2 ), блок 4 вычисления поправок, счетчик 5, кольцевой блок 6 регистров, блок 7 выбора режима, блок 8 вычисления синдромов, второй блок 9 регистров и блок 10 вычисления локатора ошибки На.фиг. J обозначены также информационные входы 11, вход 12 сигнала стираний, входы 13, 14 блочной и тактовой синхронизации, первые и второй выходы 15,16.

Первый блок 1 регистров выполнен на пятнадцати 4-разрядных регистрах, выходы каждого предыдущего регистра соединены с соответствующими информационными входами последующего. Информационные входы первого из этих регистров являются информационными входами блока входы синхронизации всех регистров объединены и являются тактовым входом блока, выходы пятнадцатого регистра являются выходами блока,

Сумматор 2 осуществляет поразрядное суммирование двух 4-разрядных символов в поле GF(2 ) и состоит из четырех сумматоров по модулю два, первые и вторые входы которых являются соответствующими входами сумматора, а выходы всех сумматоров по модулю два - его выходами.

Генератор 3 элементов поля GF{2 ) представляет собой 4-разрядный кольцевой регистр сдвига с сумматором

по модулю два, иключеииым между третьим и четвертым разрядами, выход четвертого разряда соединен с вторым входом сумматора по модулю два. Выходы разрядов этого регистра являются выходами генератора.

Счетчик 5 - 4-разрядный на D-триг- герах, причем информационный вход первого разряда триггера соединен с

шиной логической единицы. Управляющий и счетный входы счетчика подключены к входам элемента И, выход которого соединен с тактовыми входами всех разрядов.

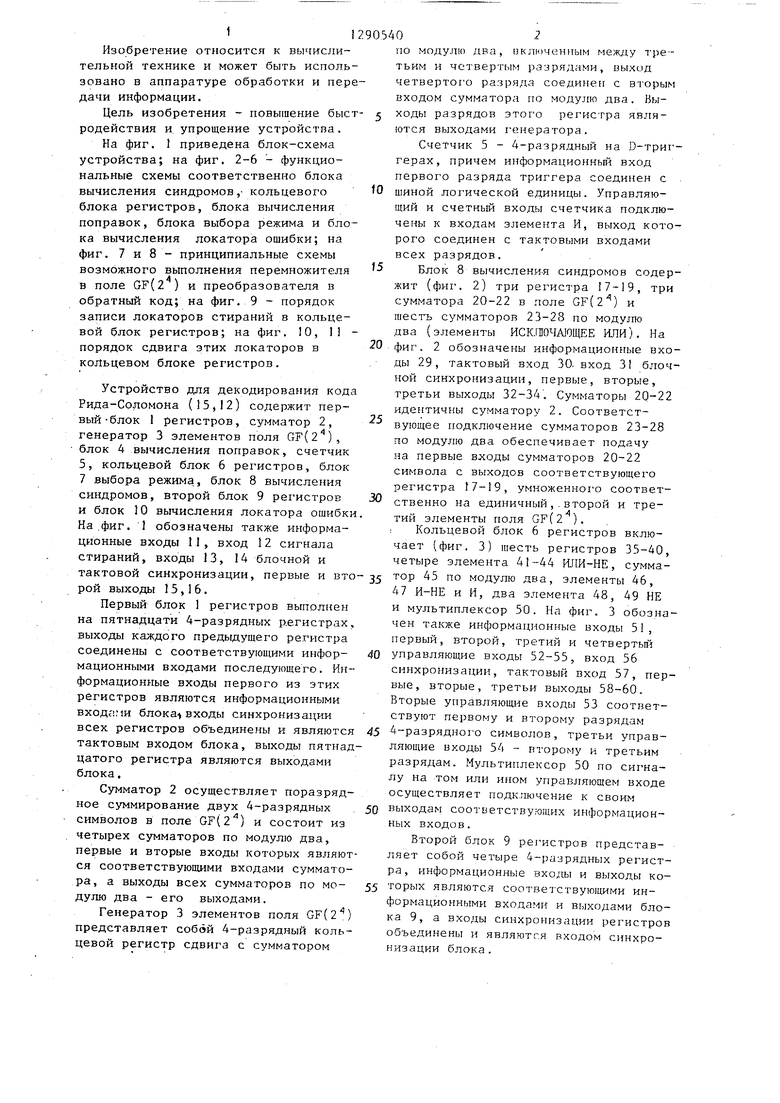

Блок 8 вычислени-я синдромов содержит (фиг. 2) три регистра 17-19, три сумматора 20-22 в поле GF(2 ) и шесть сумматоров 23-28 по модулю два (элементы ИСК.ПЮЧА10ЩЕЕ ИЛИ). На

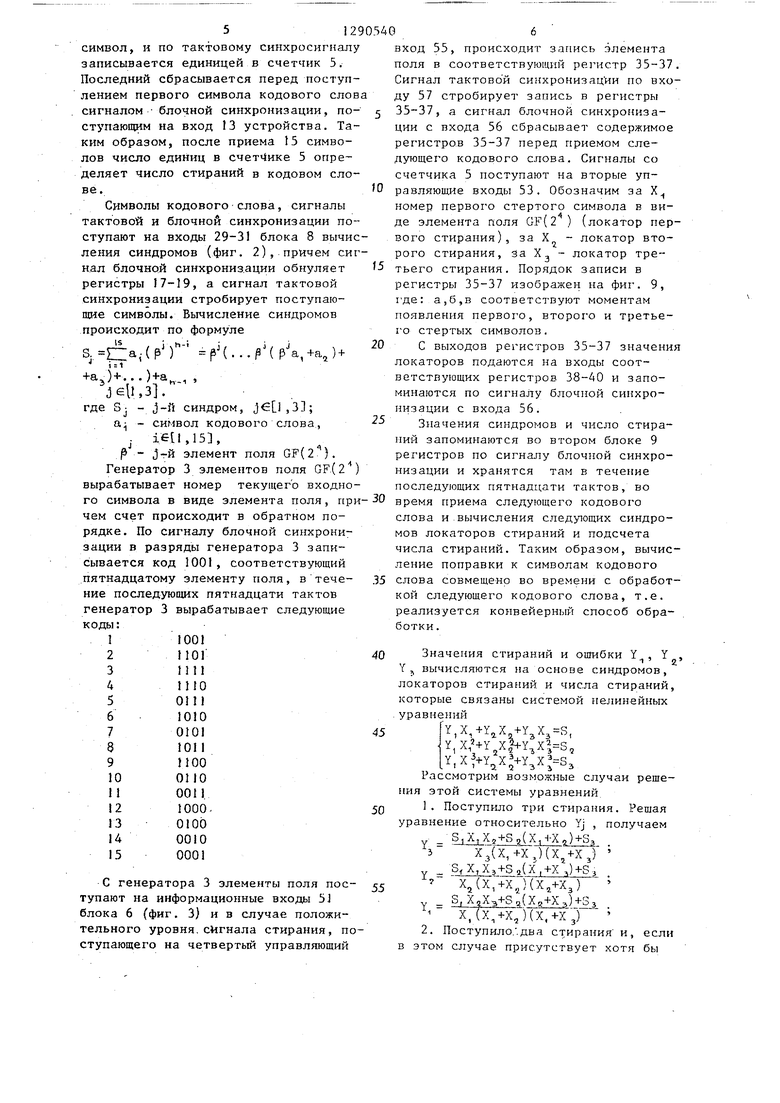

фиг. 2 обозначены информационные входы 29, тактовый вход 30. вход 31 блочной синхронизации, первые, вторые, третьи выходы 32-34. Сумматоры 2Q-22 идентичны сумматору 2. Соответствующее подключение сумматоров 23-28 по модулю два обеспечивает подачу на первые входы сумматоров 20-22 символа с выходов соответствующего регистра 17-19, умноженног о соответственно на единичный,.второй и третий элементы поля GF(2 ). Кольцевой блок 6 регистров включает (фиг. 3) шесть регистров 35-40, четыре элемента 41-44 ИЛИ-НЕ, сумматор 45 по модулю два, элементы 46, 47 И-НЕ и И, два элемента 48, 49 НЕ и мультиплексор 50. На фиг. 3 обозначен также информационные входы 51, первый, второй, третий и четвертьй

управляющие входы 52-55, вход 56

синхронизации, тактовый вход 57, первые, вторые, третьи выходы 58-60. Вторые управляющие входы 53 соответствуют первому и второму разрядам

4-разрядного символов, третьи управляющие входы 54 - второму и третьим разрядам. Мультиплексор 50 по сигналу на том или ином управляющем входе осуществляет подключение к своим

выходам соответствующих информационных входов.

Второй блок 9 регистров представляет собой четыре 4-разрядных регистра, информационные входы и выходы которых являются соответствующими информационными входами и выходами блока 9, а входы синхронизации регистров объединены и являются входом синхронизации блока.

Блок 4 вычисления поправок содержит (фиг. 4) сумматоры 61-64 в поле GF(2), коммутаторы 65-67, перемножители 68-70 в поле GF(2 ), мультиплексор 71, преобразователь 72 в обратный код, элементы 73-78 ИЛИ-НЕ, элемент 79 И-НЕ и элементы 80-82 ПЕ. На фиг. 4 обозначены также информационные входы 83-88 с первых по шестые, первые и второй управляющие входы 89,90, первые, второй, третий и четвертый выходы 91-94-. Первые управляющие входы 89 соответствуют второму и третьему разрядам 4-разрядного символа. Мультиплексор 71 иденти- f5 блока 6 сумматоры 138, I39 в ноле

20

,-25

чен мультиплексору 50 блока 6, сумматоры 61-64 идентичны сумматору 2. Коммутатор 67 выполнен на четырех элементах И,-первые входы которых являются информационными, а объединенные вторые - управляющими входами коммутатора. В коммутаторах 65 и 66 в отличие от коммутатора 67 четвертый элемент И заменен на элемент ИЛИ, первый вход которого является четвер тым разрядом информационных входов коммутатора, а к его второму входу через элемент НЕ подключен управляющий вход коммутатора.

Блок 7 выбора режима содержит (фиг. 5) перемножители 95-97 в поле GF(2), сумматоры 98-101, коммутатор 102, сумматор 103 по модулю два, элементы 104-108 ИЛИ-НЕ, элементы 109- 112.НЕ, и элементы 113-115 И-НЕ. На фиг. 5 обозначены также, информационные входы 116-120 с первых по нятые, первые и второй управляющие входы 121, 122, первые, вторые, третьи, - четвертые и пятый выходы 123-127. 40 Сумматоры 98-101 в иоле GF(2 ) идентичны сумматору 2, а коммутатор 102. - коммутатору 67 блока 4.

GF(2 ) идентичны сз мматору 2,

Перемножители 68-70, 95-97, 136 137 в поле GF(2) блоков 4,7,10 мо быть выполнены (фиг. 7) на элемент 160 И-НЕ и сумматорах 161 по модул два. На фиг. 7 обозначены поразря но первые входы 162-165, вторые вх 166-169 и выходы 170-173.

Преобразователи 72, 129 и 130 б ков 4,10 могут быть . выполнены . (фиг. 8) на элементах 174 НЕ, элем тах 175 И-НЕ, сумматорах 176 по мо дулю два и сумматорах 177 по модул два с инверсией (элементах эквива30 лентности) . На фиг. 8 обозначены п разрядно входы 178-181 и выходы 18 185.

Устройство для декодирования ко Рида-Соломона (15,12) .работает сле 35 дующим образом.

Кодовое слово состоит из пятнад цати символов, двенадцать из которых - информационные, а три - нров рочные. Каждый символ - 4-разрядны что обусловливает разрядность вход и выходов соответствующих блоков и элементов устройства. Кодовое слов поступает последовательно, символ символом, на информационный вход 1 с которого символы поступают на ин формационные входы первого блока 1 регистров и блока 8 вычисления синдромов. Каждый входной символ сопровождается по входу 14 сигнало тактовой синхронизации, по котором происходит запись символа в блоке и сдвиг ранее записанных в него символов. .Таким образом, через пят надцать тактов записанный символ поступает на выход первого блока I

Блок 10 вычисления локатора ошибки содержит (фиг. 6) квадратор 128, преобразователи 129, 130 в обратньш код, мультиплексоры 131-135, перемножители 136, 137 в поле GF(2), сумматоры 138, 139 в поле GF(2), элементы 140-142 ИЛИ-НЕ и элементы 143- 146 НЕ. На фиг. 6 обозначены также информационные входы 147-153 с первых по седьмые, первые, второй и третий управляющ11е входы 154-156, первый, вторые, и третьи выходы 157- 159. Первые управляющие входы 154 соответствуют первому, второму и третьему разрядам 4-разрядного символа.

Квадратор 128 выполнен на двух сумматорах по модулю два, первые входы которых являются соответственно нер- . выи и вторым разрядами входов у квадратора, а выходы - первым и третьим разрядами со его входов, третий входной разряд квадратора подключен ко второму входу первого сумматора но модулю два и второму выходному разряду, четвертый входной разряд соединен со вторым входом второго сумматора по модулю два и четвертым выходным разрядом квадратора. Мультиплексоры 131-1-35 налогичны мультиплексору 50

f5 блока 6 сумматоры 138, I39 в ноле

20

25

,

, 40

GF(2 ) идентичны сз мматору 2,

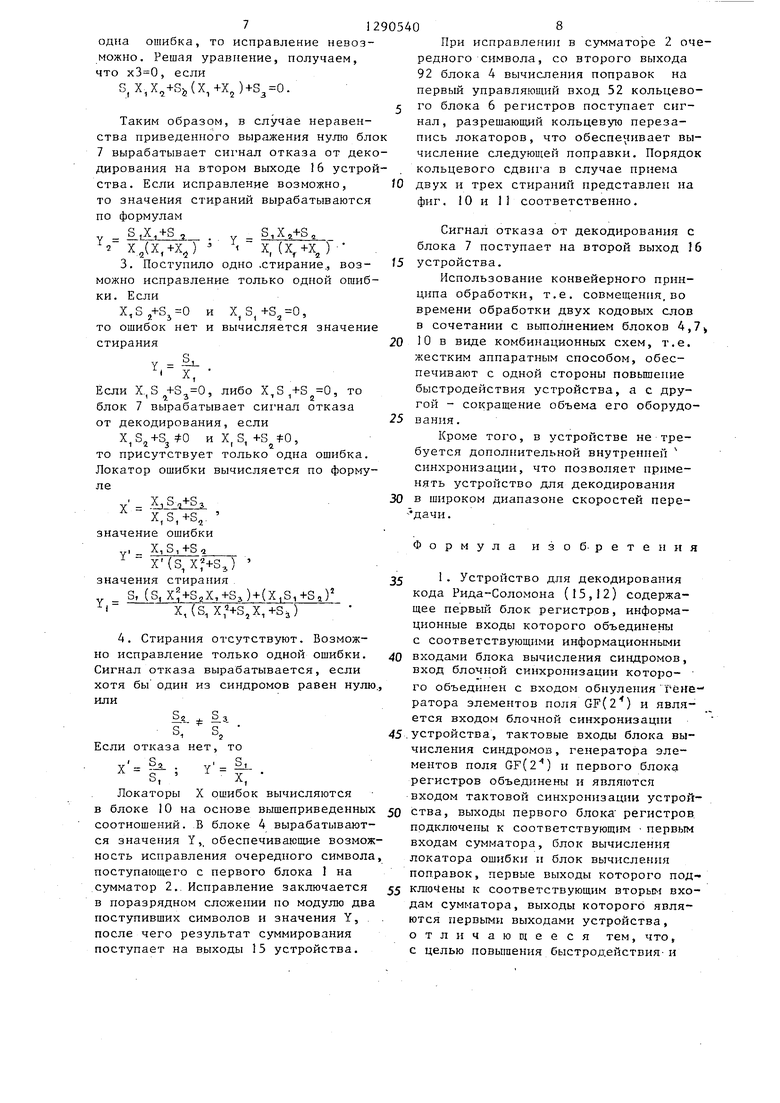

Перемножители 68-70, 95-97, 136, 137 в поле GF(2) блоков 4,7,10 могут быть выполнены (фиг. 7) на элементах 160 И-НЕ и сумматорах 161 по модулю два. На фиг. 7 обозначены поразрядно первые входы 162-165, вторые входы 166-169 и выходы 170-173.

Преобразователи 72, 129 и 130 блоков 4,10 могут быть . выполнены . (фиг. 8) на элементах 174 НЕ, элементах 175 И-НЕ, сумматорах 176 по модулю два и сумматорах 177 по модулю два с инверсией (элементах эквива. 30 лентности) . На фиг. 8 обозначены по- разрядно входы 178-181 и выходы 182- 185.

Устройство для декодирования кода Рида-Соломона (15,12) .работает сле- 35 дующим образом.

Кодовое слово состоит из пятнадцати символов, двенадцать из которых - информационные, а три - нрове- рочные. Каждый символ - 4-разрядный, что обусловливает разрядность входов и выходов соответствующих блоков и элементов устройства. Кодовое слово поступает последовательно, символ за символом, на информационный вход 11, с которого символы поступают на информационные входы первого блока 1 регистров и блока 8 вычисления синдромов. Каждый входной символ сопровождается по входу 14 сигналом тактовой синхронизации, по которому происходит запись символа в блоке 1 и сдвиг ранее записанных в него символов. .Таким образом, через пятнадцать тактов записанный символ поступает на выход первого блока I.

45

50

55

Сигнал стирания поступает на вход 12 устройства положительным уровнем, ; сопровождая очередной 1зводимый

символ, и по тактовому синхросигналу записывается единицей в счетчик 5. Последний сбрасывается перед поступлением первого символа кодового слов сигналом блочной синхронизации, по- ступающим на вход 13 устройства. Таким образом, после приема 15 символов число единиц в счет ике 5 определяет число стираний в кодовом слове.

Символы кодового слора, сигналы тактовой и блочной синхронизации поступают на входы 29-31 блока 8 вычисления синдромов (фиг. 2), причем сигнал блочной синхрониз.ации обнуляет регистры 17-19, а сигнал тактовой синхронизации стробирует поступающие символы. Вычисление синдромов происходит по формуле

S: E:::a,(p r рЧ...(,).

+а ) + ...)+а., ,

5elЬЗ.

где Sj - j-й синдром, , а - символ кодового слова,

j ,15, .р - Jтй элемент поля GF(2 ). Генератор 3 элементов поля GF(2 вырабатывает номер текущего входного символа в виде элемента поля, при чем счет происходит в обратном порядке. По сигналу блочной синхронизации в разряды генератора 3 записывается код 1001, соответствующий пятнадцатому элементу поля, в тече- ние последующих пятнадцати тактов генератор 3 вырабатывает следующие коды:

11001

2ПОГ

3ПП

41110

50111

61010

70101

81011

10ОНО

11ООП

121000-

130100

140010

150001

С генератора 3 элементы поля поступают на информационные входы 5 блока 6 (фиг. 3) и в случае положительного уровня,сигнала стирания, поступающего на четвертый управляющий

5

-5

0 5

0

5

0

5

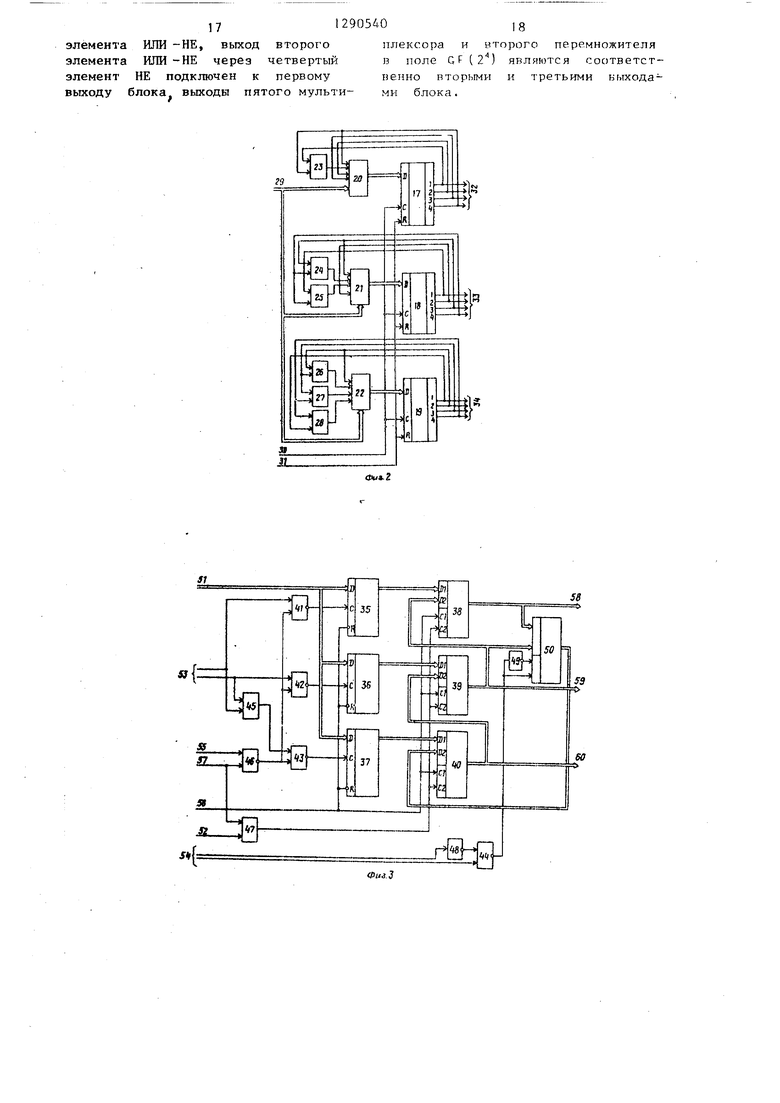

вход 55, происходит запись элемента поля в соответствующий регистр 35-37. Сигнал тактовой синхронизац ии по входу 57 стробирует запись в регистры 35-37, а сигнал блочной синхронизации с входа 56 сбрасывает содержимое регистров 35-37 перед приемом следующего кодового слова. Сигналы со счетчика 5 поступают на вторые уп- равляюЕще входы 53. Обозначим за Х номер первого стертого символа в виде элемента поля GF(2 ) (локатор первого стирания), за X - локатор второго стирания, за Х - локатор третьего стирания. Порядок записи в регистры 35-37 изображен на фиг. 9, 1 де : а, б,в соответствуют моментам появления первого, второго и третьего стертых символов.

С выходов регистров 35-37 значения локаторов подаются на входы соответствующих регистров 38-40 и запоминаются по сигналу блочной синхронизации с входа 56.

Значения синдромов и число стираний запоминаются во втором блоке 9 регистров по сигналу блочной синхронизации и хранятся там в течение последующих пятнадцати тактов, во время приема следующего кодового слова и вычисления следующих синдромов локаторов стираний и подсчета числа стираний. Таким образом, вычисление поправки к символам кодового слова совмещено во времени с обработкой следуЕошего кодового слова, т.е. реализуется конвейерный способ обработки.

Значения стираний и ошибки Y, Y , Yj вычисляются на основе синдромов, локаторов стираний и числа стираний, которые связаны системой нелин-ейных уравнений

Y,X H-Y.X +Y,X,S, Y,X,,X,S, Y,,, Рассмотрим возможные случаи реше- 1ия этой системы уравнений

1. Поступило три стирания. Решая уравнение относительно Yj , получаем у SiX,X,(X,+Xo)+S, S Хз(Х,+Х,)(,) Y :S,,i( J+Sj Х,(Х,+Х,)(Х,+Хз) S, Х Хз+5а(Х,;+Хз)+Зз

х,(х,+х,)(х,+Хз)

2. Поступило..два стирания и, если в этом случае присутствует хотя бы

71290540

одна ошибка, то исправление невозможно. Решая уравнение, получаем, что , если

S, X,(X,+XJ+S 0.

Таким образом, в случае неравенства приведенного выражения нулю бл 7 вырабатывает сигнал отказа от декдирования на втором выходе 16 устроства. Если исправление возможно, то значения стираний вырабатываются по формулам

Y бд.+д. . Y

xjx,+x,) 1 X, (x,+xj -

3. Поступило одно .стирание., возможно исправление только одной ошибки. Если

X,S, и ,, то ошибок нет и вычисляется значени стирания

S,

,

Если X. S +S,0, либо X S +S 0, то

1 3 12

блок 7 вырабатывает сигнал отказа от декодирования, если

X S +S 0 и X, S. +S 0,

U

то присутствует только одна ошибка. Локатор ошибки вычисляется по формуле

Y - bAitSi X,l5,+S,.

значение ошибки у1 X, Si +S а

X {S Xf+Sj значения стирания

S, (S, xt-+s,x,+sj+(x,s,+sj

X, (S, ХЧЗ,Х,+Зз)

4. Стирания отсутствуют. Возможно исправление только одной ошибки. Сигнал отказа вырабатывается, если хотя бы один из синдромов равен нул или

S.2. ф §.3.

S, 8, Если отказа нет, то

Y -

X.

.., X ошибок вычисляются

в блоке 10 на основе вышеприведенных 50 ства, выходы первого блока регистров соотношений. В блоке 4 вырабатывают- подключены к соответствующим Первым ся значения Y,, обеспечивающие возмож- входам сумматора, блок вычисления ность исправления очередного символа, поступающего с первого блока 1 на

сумматор 2. Исправление заключается 5 клю 1ены к соответствующим вторым вхо- в поразрядном сложении по модулю два дам сумматора, выходы которого являются первыми выходами устройства, отличающееся тем, что, с целью повышения быстродействия-и

локатора ошибки и блок вычисления поправок, первые выходы которого подпоступивших символов и значения Y, после чего результат суммирования поступает на выходы 15 устройства.

При исправлении в сумматоре 2 очередного символа, со второго выхода 92 блока 4 вычисления поправок на первый управляющий вход 52 кольцевого блока 6 регистров поступает сигнал, разрешающий кольцевую перезапись локаторов, что обеспе П1вает вычисление следующей поправки. Порядок кольцевого сдвига в случае приема двух и трех стираний представлен на фиг. 10 и 11 соответственно.

Сигнал отказа от декодирования с блока 7 поступает на второй выход 16 устройства.

Использование конвейерного принципа обработки, т.е. совмещения, во времени обработки двух кодовых слов в сочетании с вьшолнением блоков 4,7 10 в виде комбинационных схем, т.е. жестким аппаратным способом, обеспечивают с одной стороны повьшение быстродействия устройства, а с другой - сокращение объема его оборудо- вания.

Кроме того, в устройстве не требуется дополнительной внутренней синхронизации, что позволяет применять устройство для декодирования в широком диапазоне скоростей пере- дачи.

Формула изоб-рете{1ия

1 Устройство для декодирования кода Рида-Соломона (15,12) содержащее первьш блок регистров, информационные входы которого объединены с соответствующими информационными

входами блока вычисления синдромов, вход блочной синхронизации которо- го объединен с входом обнуления Генератора элементов поля GF(2) и является входом блочной синхронизации

устройства, тактовые входы блока вычисления синдромов, генератора элементов поля GF(2) II первого блока регистров объединены и являются входом тактовой синхронизации устройства, выходы первого блока регистров подключены к соответствующим Первым входам сумматора, блок вычисления

локатора ошибки и блок вычисления поправок, первые выходы которого подупрощения устройства, в него ВЕзедены счетчик, второй блок регистров, блок выбора режима и кольцевой блок регистров, выходы генератора элементов поля GF(2 ) подключены к соответстfO

15

вующим информационным входам кольцевого блока регистров и первым информационным входам блока йычисления поправок, второй выход которого соединен с первым управляющим входом кольцевого блока регистров, первые выходы которого соединены с соответствующими вторьпии информационными входами блока вычисления поправок, выходы счетчика подключены к соответ- 1ствующим вторым управляющим входам .кольцевого блока регистров и первым информационным входам второго блока регистров, первые, вторые и третьи выходы блока вычисления синдромов 20 соединены соответственно с вторыми, третьими и четвертыми информационнь ми входами второго блока регистров, первые выходы которого подключены к со- отвествующим третьим управляющим . . 25 входам кольцевого блока и первым управляющим входам блока вычисления поправок, блока выбора режима и блока вычисления локатора ошибки, первый выход которого соединен с вторым 30 управляющим входом блока выбора режима, вторые, третьи и четвертые выходы второго блока регистров подключены соответственно к первым, вторым и третьим информационным входам блока 35 выбора режима и блока вьиисления локатора ошибки, вторые и третьи выходы которого соединены соответственно с третьими и четвертыми информационными входами блока вычисления попра- 40 вок, третий и четвертый выходы которого подключены соответственно к второму и третьему управляющим входам блока вычисления локатора ощибки, вторые выходы кольцевого блока реги- 45 стров подключены к соответствующим пятым информационным входам блока вычисления поправок и четвертым инфор- . мационным входам блока выбора режима, третьи выходы кольцевого блока 50 регистров соединены с соответствующими шестыми информационными входами блока вычисления поправок и пятыми информационными входами блока выбора

1290540 0

жима подключен к второму управляющему входу блока вычисления поправок и является вч орым выходом устройства, информационные входы первого блока регистров являются информационными входами устройства, входы синхронизации второго и кольцевого блоков регистров и вход обнуления счетчика подключены к входу блочной синхронизации устройства, счетный вход счетчика и тактовый вход кольцевого блока регистров подключены к входу тактовой синхронизации устройства, управляющий вход счетчика и четвертый управляющий вход кольцевого блока регистров объединены и являются }зходом сигнала стирания устройства.

2. Устройство по п. 1, о т л и - чающееся тем, что блок вычисления синдромов выполнен на первом, втором и третьем регистрах, сумматорах по модулю два с первого по шестой и первом, втором и третьем сумматорах в поле GF(2), выходы которых подключены к соответствующим информационным входам соответствующих регистров, выходы с первого по четвертый каждого регистра являются соответствующими разрядами соответствующих выходов блока, первый выход первого регистра соединен с первым входом первого сумматора по модулю два, четвертьй выход первого регистра соединен с первым входом первой первого сумматора в поле и вторым входом первого сумматора по модулю два, выход которого подключен к второму входу первой Г руппы первого сумматора в поле C-F(2)., второй и третий выходы первого регистра соединены соответственно с третьим и четвертым входами первой группы первого сумматора в поле GF(2), третий выход второго регистра подключен к первому входу первой группы второго сумматора в поле GF( тора

соединен с вторым входом первой группы второг о сумматора в поле GF(2), первый выход второго регистра подключен к первому входу третьего сумматора по модулю два, выход которого

группы GF(2

/ и первому входу второго сумма- по модулю два, выход которого

режима, первые - четвертые выходы ко- 55 соединен с третьим входом первой

торого подключены соответственно к четвертым - седьмым информационным входам блока вычисления локатора ошибки, пятый выход блока выбора ре2. Устройство по п. 1, о т л и - чающееся тем, что блок вычисления синдромов выполнен на первом, втором и третьем регистрах, сумматорах по модулю два с первого по шестой и первом, втором и третьем сумматорах в поле GF(2), выходы которых подключены к соответствующим информационным входам соответствующих регистров, выходы с первого по четвертый каждого регистра являются соответствующими разрядами соответствующих выходов блока, первый выход первого регистра соединен с первым входом первого сумматора по модулю два, четвертьй выход первого регистра соединен с первым входом первой первого сумматора в поле и вторым входом первого сумматора по модулю два, выход которого подключен к второму входу первой Г руппы первого сумматора в поле C-F(2)., второй и третий выходы первого регистра соединены соответственно с третьим и четвертым входами первой группы первого сумматора в поле GF(2), третий выход второго регистра подключен к первому входу первой группы второго сумматора в поле GF( тора

соединен с вторым входом первой группы второг о сумматора в поле GF(2), первый выход второго регистра подключен к первому входу третьего сумматора по модулю два, выход которого

группы GF(2

/ и первому входу второго сумма- по модулю два, выход которого

группы GF(2),

BTopoi o сумматора в поле

второй выход второго регистра соединен с четвертым 8xoдo i пер- BOI1 1 руппы второго сумматора в поле

GF(2) , четвертый выход второт о регистра подключен к втормы входам второго и третьего сумматоров по модулю два, первый выход третьего регистра соединен с первым входом шестого сумматора по модулю два, второй выход третьего регистра соединен с первым входом первой группы третьего сумматора в поле GF(2) и первым входом четвертого сумматора по модулю два, выход которого соединен с вторым входом первой группы третьего сумматора в поле GF(2), третий выхо третьего регистра подключен к второму входу четвертого и первому входу пятого сумматоров по модул о два, четвертый выход третьего регистра соединен с вторыми входами пятого и шестого сумматоров по модулю два, выходы которых подключены соответственно к третьему и четвертому входам первой группы третьего сумматора в поле GF(2), входы второй группы всех сумматоров в поле GF(2) соответственно обьединены и являются соответствующими -информационными входами блока, входы синхронизации и входы обнуления всех регистров соответственно объединены и являются соответственно тактовым входом и входом блочной, синхронизации блока.

ч а

3, Устройство по п. 1 тем, что

о т л и ю щ е е с я тем, что кольцевой блок регистров выполнен на регистрах, 5 второй вход элемента И-ПЕ является

30 .ляющими входами кольцевого блока р гистров, вход первого элемента НЕ второй вход четвертого элемента 11П НЕ являются третьими управляющими входами кольцевого блока регистров

мультиплексоре, элементах ИЛИ-НЕ, элементах НЕ, элементе И, сумматоре по модулю два и элементе И-НЕ, выход которого соединен с первыми входами первого, второго и третьего элементов ИЛИ-НЕ, выходы которых подключены к входам синхронизации соответствующих регистров, выходы которых подключены к соответствующим первым информационным входам .соответственно четвертого, пятого и шестого рег ист- ров, лервые входы синхронизации которых объединены с входами обнуления первого, второго и третьего регистров и являются входом синхронизации кольцевого блока регистров, выход сумматора по модулю два соединен, с вторым входом третьего элемента ИЛИ- НЕ, выход элемента И подключен к вторым входам синхронизации четвертого, пятого и шестого регистров, - выходы четвертого регистра соединены с соответствующими первыми информа- ционными входами- мультиплексора.

четвертым управляющим входом кольце вого блока регистров, выходы четве того, пятого и шестого регистров яв ляются соответственно первыми, вто- 40 рыми и третьш И выходами кольцевого блока регистров.

4. Устройство по п. 1 , о т л и чающееся тем, что блок вы45- числения поправок выполнен на сумм торах в поле GF(2 ), перемножителях в поле GF(2), мультиплексореj прео разователе в обратный код, коммутаторах, элементах ИЛИ-НЕ, элементах

50 ИЕ и элементе И-НЕ, выходы первого и второго сумматоров в поле GF(2 ) соединены с соответствующими входам соответствующих элементов ИЛИг-НЕ, выходы .третьего и четвертого сумма55 торов в поле GF(2) подключены к с ответствуюа1им информационным входам соответствен}ю первого и второго коммутаторов, выходы которых соедин ны соответственно с первыми и вторы

{290540

12

второй вход элемента И-ПЕ является

выходы пятого регистра подключены к соответствующим вторым информационным входам четвертого регистра и мультиплексора, выходы которого соединены с соответствующими вторыми информационными входами шестого регистра, выходы которого подключены к соответствующим вторым информационным входам пятого регистра, выход первого элемента НЕ соединен с первым входом четвертого элемента ИЛИ-НЕ,выход которого подключен к первому управляющему входу мультиплексора и через второй элемент НЕ - к второму управляющему входу мультиплексора, информационные входы первого, йторого и третьего регистров соответствешю объединены и являются соответствую- шлми информационными входами кольцевого блока регистров, первые входы элементов И и И-НЕ объединены и являются тактовым входом кольцевого блока регистров, второй вход элемента И является первым управляющим входом кольцевого блока регистров, вторые входы первого и второго элементов ИЛИ-НЕ объединены соответственно с первым и вторым входами сумматора по модулю два и являются вторыми управ.ляющими входами кольцевого блока регистров, вход первого элемента НЕ и второй вход четвертого элемента 11ПН- НЕ являются третьими управляющими входами кольцевого блока регистров.

четвертым управляющим входом кольцевого блока регистров, выходы четвертого, пятого и шестого регистров являются соответственно первыми, вто- 40 рыми и третьш И выходами кольцевого блока регистров.

4. Устройство по п. 1 , о т л и - чающееся тем, что блок вы45- числения поправок выполнен на сумматорах в поле GF(2 ), перемножителях в поле GF(2), мультиплексореj преобразователе в обратный код, коммутаторах, элементах ИЛИ-НЕ, элементах

50 ИЕ и элементе И-НЕ, выходы первого и второго сумматоров в поле GF(2 ) соединены с соответствующими входам1Г соответствующих элементов ИЛИг-НЕ, выходы .третьего и четвертого сумма55 торов в поле GF(2) подключены к со- ответствуюа1им информационным входам соответствен}ю первого и второго коммутаторов, выходы которых соединены соответственно с первыми и вторы-

15

20

25

ми входами первого перемножителя в поле GF(2), выходы которого подключены к соответствующим первым входам второго перемножителя в поле GF(2 ), выходы которого соединены с соответ- ствующими первыми информационными входами мультиплексора, выход первого элемента ИЛИ-НЕ подк,лючен к первым входам элемента И-НЕ и третьего элемента ИЛИ-НЕ и через первый эле- Ш мент НЕ - к первому входу четвертого элемента ИПИ-НЕ, выходы второго и четвертого элементов ИЛИ-НЕ соедине-- ны с входами пятого элемента ИЛИ-НЕ, выход которого подключен к первому входу шестого элемента ИЛИ-НЕ, выход которого соединен с управляющим входом третьего коммутатора, выход второго элемента НЕ соединен с вторым входом элемента И-НЕ , выход KOTopof o непосредственно и через третий элемент НЕ подключен соответственно к первому и второму управляющим входам мультиплексора, выходы которого через преобразователь в обратный код подключены к соответствующим первым входам третьего перемножителя в поле GF(2), выходы которого соединены с соответствующими информационными входами третьего коммутатора,, первые 30 входы первого и второго сумматоров в поле GF(2) соответственно объединены и являются первыми ипформацион- ньми входами блока, вторые входы вторых сумматоров и перемножителя 35 в поле GF(2) и первые входы третьего и четвертого сумматоров в поле GF(2) соответственно объединены и являются вторыми входами блока, вторые входы третьего перемножителя в 40 поле GFCZ) являются третьими инфор- мaциoннымkвходами блока, вторые входы первого сумматора в поле GFfZ) и вторые информационные входы мультиплексора соответственно объединены 45 и являются четвертыми информационными входами блока, вторые входы третьего и четвертого сумматоров в поле GF(2 ) являются соответственно пятыми и шестыми информационными входами блока, 50 управляющий вход первого коммутатора и управляющий вход второго коммутатора, объединенный с входом второго элемента НЕ и вторыми входами третьего и четвертого элементов ИЛИ-НЕ, 55 являются первыми управляющими входами блока, второй вход шестого элемента ИЛИ-НЕ является вторым управляющим входом блока, выходы третьего комму1290540 . 1/,

татора являются первыми выходами блока, выходы шестог О элементг) ИЛИ-НЕ, третьего элемента НЕ и третьего элемента ИЛИ-НЕ являются соответственно вторым, третьим и четвертьм выходами блока.

:з .

чаю ра режим

Устройство по п щ е е с я тем,

, 1 , о т л и - что блок выбовыполнен -на сумматорах в

поле GF(2), перемножителях в поле

. .

GF(2 ), коммутаторе, sjTBMeHTax ИЛИ- НЕ, элементах И-НЕ, элементах НЕ и сумматоре по модулю два, выходы коммутатора соединены с соответствуюищми первыми входами первого сумматора в поле GF(2 ), выходы первого перемножителя в поле G(2) подключены к соответствующим первь м входам вторых перемнох ителя и сумматора в поле GF(2 j, выходы которого соединены с входами первого элемента , выходы первого сумматора з поле GF(2) подключены к соответстзующнм первьм в ходам третьего перемножителя в поле GF(2), выходы которого соединены с соответствующими первыми входами третьего сумматора в поле GF{2 ). выходы которого подключены к соответ- в ующим входам второго элемента {-ШИ- НЕ и первым входам четвертого сумматора в поле GF(2), выходы которого соединены с входами третьего элемента , выходы первого и второго элементов ИЛИ-НЕ подключены к соответствующим входам суьматора по модулю два, выход которого соединен с первым входом первого элемента И-НЕ, выход третьего элемента .ВДИ-НЕ через первр ш элемент НЕ подключен к первому входу второго элемента И-НЕ, выходы второго и третьего элементов НЕ соединены с первьыи входами соответственно четвертого и ттого элемен- то)з гШ И-НЕ, выходы которых подключены к вторым входам соответствеино первого и второго элементов И-НЕ, зьг- ходы которых и выход четвертого эле- м ента НЕ соединены соответственно с первым, вторым и третьим входами третьего элемента И-НЕ, вторые входы первого перемножителя в поле GF(2 ) являются первыми информапион- нымн входами блока, вторые входы третьего перемножителя и второго сумматора в поле GF(2) соответствен- ко объединены и являются вторыми информационными входами блока, вторые Бходь третьего сумматора в поле

:з .

чаю ра режим

Устройство по п щ е е с я тем,

, 1 , о т л и - что блок выбовыполнен -на сумматорах в

поле GF(2), перемножителях в поле

. .

GF(2 ), коммутаторе, sjTBMeHTax ИЛИ- НЕ, элементах И-НЕ, элементах НЕ и сумматоре по модулю два, выходы коммутатора соединены с соответствуюищм первыми входами первого сумматора в поле GF(2 ), выходы первого перемножителя в поле G(2) подключены к соответствующим первь м входам вторых перемнох ителя и сумматора в поле GF(2 j, выходы которого соединены с входами первого элемента , выходы первого сумматора з поле GF(2) подключены к соответстзующнм первьм в ходам третьего перемножителя в поле GF(2), выходы которого соединен с соответствующими первыми входами третьего сумматора в поле GF{2 ). выходы которого подключены к соответ в ующим входам второго элемента {-ШИ- НЕ и первым входам четвертого сумматора в поле GF(2), выходы которог соединены с входами третьего элемента , выходы первого и второго элементов ИЛИ-НЕ подключены к соответствующим входам суьматора по модулю два, выход которого соединен с первым входом первого элемента И-НЕ, выход третьего элемента .ВДИ-НЕ через первр ш элемент НЕ подключен к первому входу второго элемента И-НЕ, выходы второго и третьего элементов НЕ соединены с первьыи входами соответственно четвертого и ттого элемен- то)з гШ И-НЕ, выходы которых подключены к вторым входам соответствеино первого и второго элементов И-НЕ, зьг ходы которых и выход четвертого эле- м ента НЕ соединены соответственно с первым, вторым и третьим входами третьего элемента И-НЕ, вторые входы первого перемножителя в поле GF(2 ) являются первыми информапион- нымн входами блока, вторые входы третьего перемножителя и второго сумматора в поле GF(2) соответствен- ко объединены и являются вторыми информационными входами блока, вторые Бходь третьего сумматора в поле

10

GF(2) являются третьими информационными входами блока, вторые входы второго неремножителя и первогю сумматора в поле. GF(2 ) соответствен1то объединены и являются четвертыми информационными входами блока, вторые входы первого перемножителя в поле GF(2) и информационные входы коммутатора соответственно объединены и являются пятыми информационными входами блока, вход второго элемента НЕ, управляющий вход коммутатора, объединенный с вторым входом четвертого элемента ИЛИ-НЕ и входом третьего элемента НЕ, второй вход пятого элемента ИЛИ-НЕ и вход четвертого элемента НЕ являются соответствующими первыми управляющими входами блока, четвертый вход третьего элемента И-НЕ является вторым управляющим вхо-20 тыми информационными входами блока, дом блока, выходы второго перемножи- выходы подключены к соответствующим теля в поле GF(2), выходы второго, вторым информационным входам третьего мультиплексора, вторые информационные входы пятого мультиплексора

входами BTopoi o и первыми информационными входами третьего мультиплек соров и являются первыми информацион ными входами блока, вторые информационные входы первого мультиплексора и первые и вторые входы первого сум матора в поле GF(2) являются соответственно вторыми, третьими и че т- вертыми информационными входами блока, входы квадратора, второго преобразователя в обратный код и первые информационные входы пятого мультиплексора соответственно объединены и являются пятыми информационными 5 входами блока, выходы второго преобразователя в обратный код соединены . с соответствующими первьп и входами второго перемножителя в поле GF(2), вторые входы которого являются шестретьего и четвертого сумматоров в поле GF(2) и выход третьего элемента И-НЕ являются соответственно первыми, вторым, третьими, четвертыми и пятым выходами блока.

6. Устройство по п. 1,.о т л и -.

25

являются седьмыми информациониыш- входами блока, выходы второго сумматора в поле GF(2) подключе к соответствующим входам первого элемента ИЛИ-НЕ и третьим информационявляются седьмыми информациониыш- входами блока, выходы второго сумматора в поле GF(2) подключе к соответствующим входам первого элемента ИЛИ-НЕ и третьим информациончающееся тем , что блок вычис-30 ным входам пятого мультиплексора, вы- ления локатора ощибки вьшолнен на ходы четвертого мультиплексора соединены с соответствующими четвертыми информационными входами пятого мульмультиплексорах, преобразователях в

обратный код, сумматорах в поле

GF(2), перемножителях в поле GF(2), типлексора, выход первого элемента

элементах ИЛИ-НЕ, элементах НЕ и 35 ИЛИ-НЕ соединен с первым входом втоквадраторе, выходы которого соединены рого элемента 1ШИ-НЕ, выход третьего

с соответствующими первыми, информа- элемента 1-ШИ-НЕ подключен к первому

управляющему входу пятого мультиплексора, второй вход второго элемента соответствующим первым входам перво- 40 ИЛИ-НЕ, объединенньш с первыми управ- го перемножителя в поле GF(2 ), вы- . ляющими входами первого, второго, ходы первого сумматоре в поле GF(2 ) третьего и четвертого мультиплексоров и входами первого и второго элемента НЕ, вход третьего элемента 45 НЕ и первый вход третьего элемента ИЛИ-НЕ, объединенный с вторым управляющим входом пятого мультиплексора, являются первыми управляющими входами блока, третий и четвертый управционными входами первого мультиплексора, выходы которого подключены к

соединены с соответствующими первыми информационными входами второго мультиплексора, выходы, которого через первый преобразователь в обратный код подключены к соответствующим входам первого перемножителя в поле GF(2 ), выходы третьего мультиплексора соединены с соответствующими 50 ляющие входы пятого мульт11плексора первыми входами второго сумматора являются соответственно вторым и в поле GF(2), выходы первого перемножителя в поле GI (2 ) подключены

третьим управляющими входами блока выход первого элемента НЕ подключе к вторым управляющим входам первого

третьим управляющими входами блока, выход первого элемента НЕ подключен к вторым управляющим входам первого

к соответствующим вторым входам второго сумматора в поле GF(2 ). и пер- 55 второго и третьего мультиплексоров.

вым информационным входам четвертого мультиплексора, вторые информационные входы которого объединены с соответствующими вторыми информационными

0

0 тыми информационными входами блока, выходы подключены к соответствующим вторым информационным входам третьего мультиплексора, вторые информационные входы пятого мультиплексора

входами BTopoi o и первыми информационными входами третьего мультиплексоров и являются первыми информационными входами блока, вторые информационные входы первого мультиплексора и первые и вторые входы первого сумматора в поле GF(2) являются соответственно вторыми, третьими и че т- вертыми информационными входами блока, входы квадратора, второго преобразователя в обратный код и первые информационные входы пятого мультиплексора соответственно объединены и являются пятыми информационными 5 входами блока, выходы второго преобразователя в обратный код соединены . с соответствующими первьп и входами второго перемножителя в поле GF(2), вторые входы которого являются шестыми информационными входами блока, выходы подключены к соответствующим вторым информационным входам третьего мультиплексора, вторые информационные входы пятого мультиплексора

являются седьмыми информациониыш- входами блока, выходы второго сумматора в поле GF(2) подключе к соответствующим входам первого элемента ИЛИ-НЕ и третьим информационным входам пятого мультиплексора, вы- ходы четвертого мультиплексора соединены с соответствующими четвертыми информационными входами пятого мульляющие входы пятого мульт11плексора являются соответственно вторым и

третьим управляющими входами блока, выход первого элемента НЕ подключен к вторым управляющим входам первого.

второго и третьего мультиплексоров.

выходы второго и третьего элементов НЕ соединены соответственно с вторым управляющим входом четвертого мультиплексора и вторым входом третьего

П12905ДО

ИЛИ -НЕ, выход второго ИЛИ -НЕ через четвертый НЕ подключен к первому

в

выходу блока выходы пятого мульти- ми блока.

плексора и второго перемножителя в поле GF (2) являются соответственно вторыми н третьими ьыхода

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования кодов Рида-Соломона | 1985 |

|

SU1309317A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для вычисления локаторов ошибок | 1990 |

|

SU1728972A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

Изобретение относится к вычислительной технике. Его иснользование 13 аппаратуре обработки и передачи информации позволяет повысить быстродействие и сократить объем оборудования. Устройство содержит первый блок регистров 1, сумматор 2, генератор 3 элементов поля GF (2), блок 4 вычисления поправок, блок 8 вычисления синдромов и блок 10 вычисления локатора ошибки. Введение счетчика 5, кольцевого блока регистров, блока 7 выбора режима и второго блока регистров 9 обеспечивает кон- вейерныр принцип обработки, т.е. совмещение во времени обработки двух кодовых слов, а выполнение блоков 4, 7,10 в виде комбинационных схем позволяет сократить объем оборудования. 5 3.п. ф-лы. II ил. ю rs3 О О О c-fJuej

S8

Фиа.З

а

j

.rz3 r

JS5

«U

фиг. 9

физП

сриг гО

| YEEE Spectrum | |||

| V | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Блох Э.Л | |||

| , Зяблов В.В | |||

| Обобщеи- ные каскадные коды | |||

| Статистическая теория связи, вып., 5 М | |||

| : Связь, 1976, с | |||

| Шкив для канатной передачи | 1920 |

|

SU109A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-15—Публикация

1985-09-30—Подача