Изобретение относится к автоматике и вычис-пительной технике и может быть использовано при реализации технических средств систем контроля и регулирования параметров, преобразуемых в частоту следования импульсов.

Цель изобретения - повышение точности сравнения за счет возможности сравнения импульсных последовательностей с равномерным законом распределения случайных периодов следования импульсов.

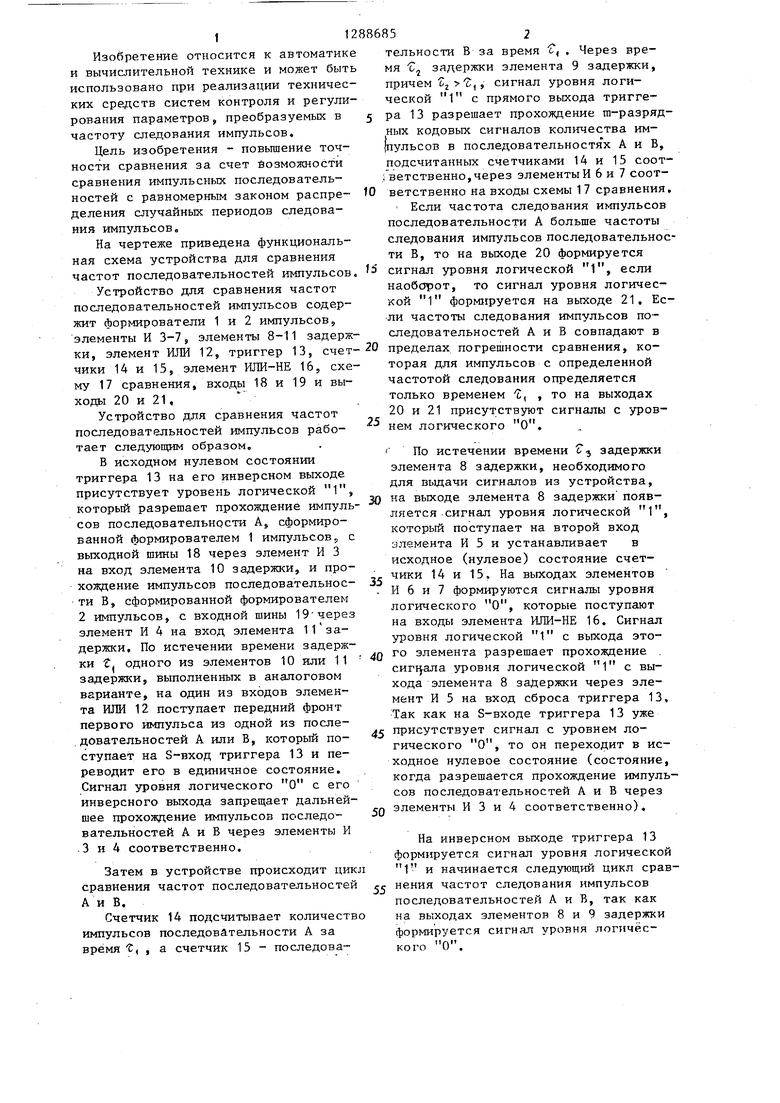

На чертеже приведена функциональная схема устройства для сравнения частот последовательностей импульсов.

Устройство для сравнения частот последовательностей импульсов содержит формирователи 1 и 2 импульсов, элементы И 3-7, элементы 8-11 задержтельности В за время Г , Через время о задерткки элемента 9 задержки, причем Cj б,, сигнал уровня логической 1 с прямого выхода тригге5 ра 13 разрешает прохождение га-разрядных кодовых сигналов количества им- {пульсов в последовательностя х А и В, подсчитанных счетчиками 14 и 15 соот- ; ветственно,через элементы И 6 и 7 соот10 ветственно на входы схемы 17 сравнения, Если частота следования импульсов последовательности А больше частоты следования импульсов последовательнос ти В, то на выходе 20 формируется

t5 сигнал уровня логической 1, если наобсзрот, то сигнал уровня логической 1 формируется на выходе 21, Если частоты следования импульсов последовательностей А и В совпадают в

ки, элемент ИЛИ 12, триггер 13, счет-20 пределах погрешности сравнения, ко- чики 14 и 15, элемент ШШ-НЕ 16, схе- торая для импульсов с определенной му 17 сравнения, входы 18 и 19 и вы- частотой следования определяется

только временем l , то на выходах 20 и 21 присутствуют сигналы с уров- 5 нем логического О,

ходы 20 и 21,

Устройство для сравнения частот последовательностей импульсов работает следующим образом,

В исходном нулевом состоянии триггера 13 на его инверсном вьпсоде присутствует уровень логической 1, который разрешает прохождение импульсов последовательности Aj сформированной формирователем 1 импульсов, с выходной шины 18 через элемент И 3 на вход элемента 10 задержки, и прохождение импульсов последовательности В, сформированной формирователем

2импульсов, с входной шины 19 через элемент И 4 на вход элемента 11 задержки. По истечении времени задержки t. одного из элементов 10 или 11 задержки, выполненных в аналоговом варианте, на один из входов элемента ИЛИ 12 поступает передний фронт первого импульса из одной из после.довательностей А или В, который поступает на S-вход триггера 13 и переводит его в единичное состояние. Сигнал уровня логического О с его инверсного выхода запрещает дальнейшее прохождение импульсов последовательностей А и В через элементы И

3и 4 соответственно.

Затем в устройстве происходит цикл сравнения частот последовательностей А и В,

Счетчик 14 подсчитывает количество импульсов последовательности А за время С, , а счетчик 15 - последова35

40

45

50

По истечении времени сГ, задержки элемента 8 задержки, необходимого для выдачи сигналов из устройства, на выходе элемента 8 задержки появляется сигнал уровня логической 1, который поступает на второй вход элемента И 5 и устанавливает в исходное (нулевое) состояние счетчики 14 и 15, На выходах элементов И 6 и 7 формируются сигналы уровня логического О, которые поступают на входы элемента ИЛИ-НЕ 16, Сигнал уровня логической 1 с выхода этого элемента разрешает прохождение . уровня логической 1 с выхода элемента 8 задержки через элемент И 5 на вход сброса триггера 13. Так как на S-входе триггера 13 уже присутствует сигнал с уровнем логического О, то он переходит в исходное нулевое состояние (состояние, когда разрешается прохождение импульсов последовательностей А и В через элементы И 3 и 4 соответственно).

На инверсном выходе триггера 13 формируется сигнал уровня логической 1 и начинается следующий цикл срав- 5 нения частот следования импульсов последовательностей А и В, так как на выходах элементов 8 и 9 задержки формируется сигнал уровня логического О,

тельности В за время Г , Через время о задерткки элемента 9 задержки, причем Cj б,, сигнал уровня логической 1 с прямого выхода триггера 13 разрешает прохождение га-разрядных кодовых сигналов количества им- {пульсов в последовательностя х А и В, подсчитанных счетчиками 14 и 15 соот- ; ветственно,через элементы И 6 и 7 соответственно на входы схемы 17 сравнения, Если частота следования импульсов последовательности А больше частоты следования импульсов последовательности В, то на выходе 20 формируется

сигнал уровня логической 1, если наобсзрот, то сигнал уровня логической 1 формируется на выходе 21, Если частоты следования импульсов последовательностей А и В совпадают в

5

0

5

0

По истечении времени сГ, задержки элемента 8 задержки, необходимого для выдачи сигналов из устройства, на выходе элемента 8 задержки появляется сигнал уровня логической 1, который поступает на второй вход элемента И 5 и устанавливает в исходное (нулевое) состояние счетчики 14 и 15, На выходах элементов И 6 и 7 формируются сигналы уровня логического О, которые поступают на входы элемента ИЛИ-НЕ 16, Сигнал уровня логической 1 с выхода этого элемента разрешает прохождение . уровня логической 1 с выхода элемента 8 задержки через элемент И 5 на вход сброса триггера 13. Так как на S-входе триггера 13 уже присутствует сигнал с уровнем логического О, то он переходит в исходное нулевое состояние (состояние, когда разрешается прохождение импульсов последовательностей А и В через элементы И 3 и 4 соответственно).

На инверсном выходе триггера 13 формируется сигнал уровня логической 1 и начинается следующий цикл срав- 5 нения частот следования импульсов последовательностей А и В, так как на выходах элементов 8 и 9 задержки формируется сигнал уровня логического О,

31288685

ормула изобретения

вх вы гр хо ро че не со вы ин вт ди мы пе

Устройство для сравнения частот последовательностей импульсов, содержащее первый и второй формирователи импульсов, первый, второй и третий элементы И, первый и второй элементы задержки, триггер,, причем вход первой последовательности импульсов устройства через первый формирователь импульсов соединен с первым входом первого элемента И.и вход второй по- .следовательности импульсов устройства через второй формирователь импульсов соединен с первым входом второго элемента И, отличающееся тем, что, с целью повьппения точности сравнения за счет возможности сравнения импульсных последовательностей с равномерным законом распределения случайных периодов следования импуль .сов, в него введены элементы ИЛИ-НЕ, элемент ИЛИ, третий и четвертый элементы задержки, первый и второй счетчики, первая и вторая группы элемен- тов И, схема сравнения, причем выход первого элемента И через первый элемент задержки соединен с первым входом элемента ИЛИ и со счетным входом первого счетчика, выходы разрядов ко торого соединены с информационными

Редактор О.Головач Заказ 7809/47

Составитель В.Козлов Техред В.Кадар

Корректор В

Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

O

0 5 0,ки ков

входами элементов И первой группы, выходы которых соединены с первой группой входов схемы сравнения, выходы которой являются выходами устройства, выход второго элемента И через второй элемент задержки соединен с вторым входом элемента ИЛИ и со счетным входим второго счетчика, выходы разрядов которого соединены с информационными входами элементов И второй группы, выходы которых соединены с второй группой входов схемы сравнения, выходы элементов И первой и второй групп соединены с

5 входами элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего элемента И, выход которого соединен с входом установки в О триггера, инверсный выход которого соединен с вторыми входами первого и второго элементов И, выход элемента ИЛИ соединен с входом установки в единичное состояние триггера, прямой выход которого через третий элемент задержки соединен с управляющими входами элементов И первой и второй групп и через четвертый элемент задержки с вторым входом третьего элемента И и с входоми установ - в о первого и второго счетчиКорректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматический регистратор электрических соединений | 1982 |

|

SU1051467A1 |

| Измеритель временных параметров случайных импульсных потоков | 1988 |

|

SU1575135A1 |

| Реле частоты | 1980 |

|

SU943904A2 |

| Запоминающее устройство | 1985 |

|

SU1325564A1 |

| Фазоимпульсный компаратор | 1986 |

|

SU1370761A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Устройство для моделирования системы связи | 1990 |

|

SU1725225A1 |

| Устройство для защиты трехфазного частотно-регулируемого привода от неполнофазного режима питания | 1985 |

|

SU1377950A1 |

| Устройство для контроля параметров | 1989 |

|

SU1605214A1 |

Изобретение относится к автоматике и-вычислительной технике и может быть использовано при реализации технических средств систем контроля и регулирования параметров, преобразуемых в частоту следования импульсов. Устройство для сравнения частот последовательностей импульсов содержит два формирователя 1, 2 импульсов, три элемента И 3-7, четыре элемента 8, 9, 10 и 11 задержки, два счетчика 14, 15, схему 17 сравнения. Использование этого устройства позволяет производить сравнение частот следования двух последовательностей при изменении длительности импульсов по случайному закону при неизменной частоте их следования. При сравнении частот следования импульсных последовательностей с равномерным законом распределения случайных периодов следования устройство позволяет сравнить средние частоты следования импульсов и оценить соотношение частот хаотических импульсных последовательностей. 1 ил. о S (Л

| Устройство для сравнения частот двух последовательностей импульсов | 1978 |

|

SU767754A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения частот последовательностей импульсов | 1975 |

|

SU570893A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1985-08-19—Подача