Изобретение относится к вычислительной технике, в частности к запоминающим устройствам для накопления результата.

Цсшь изобретения - повышение быстродействия запоминающего устройства,

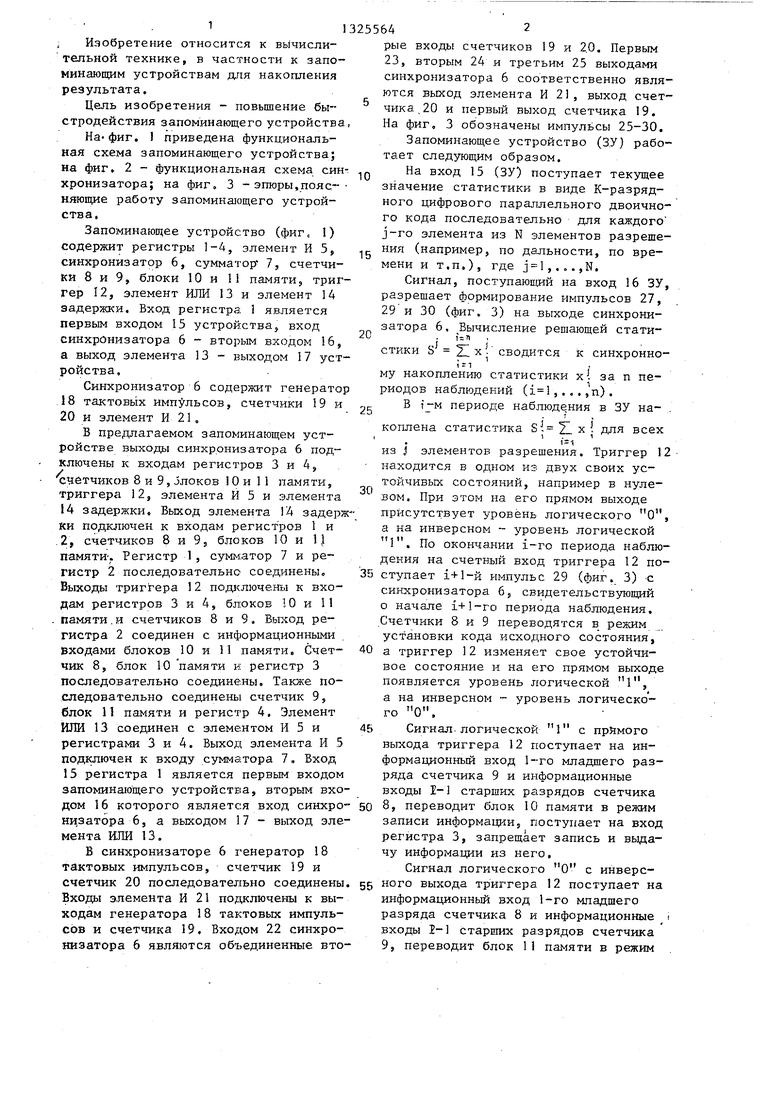

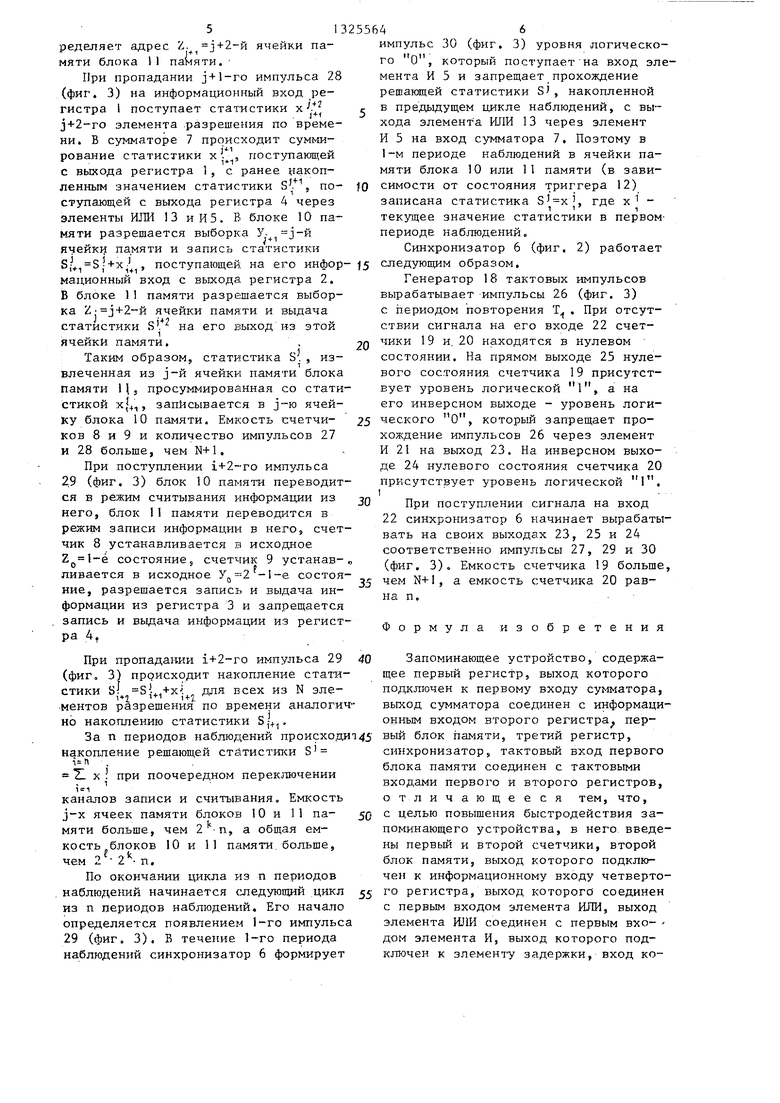

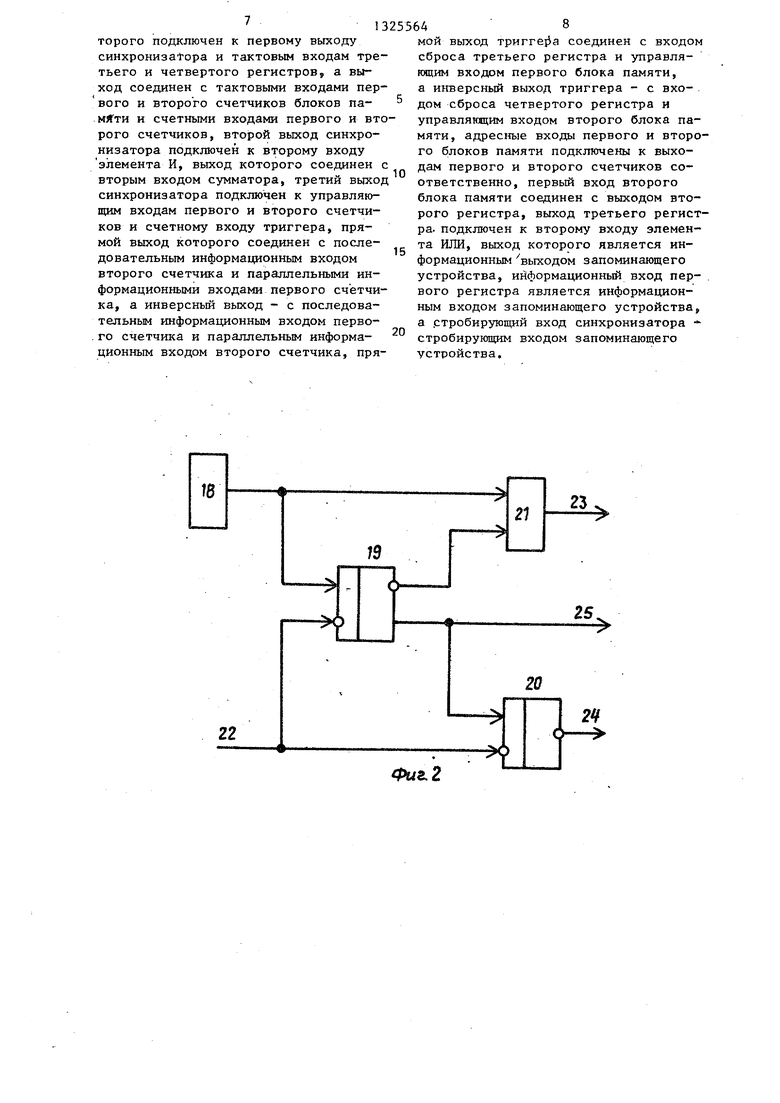

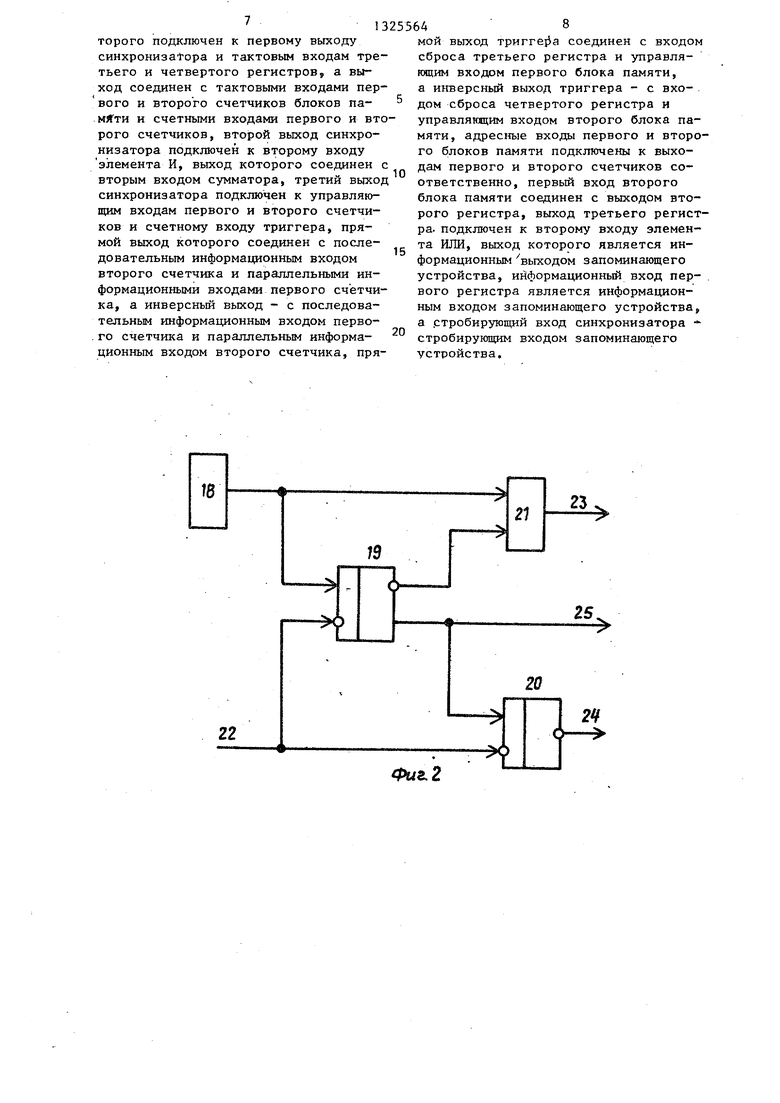

На- фиг, 1 приведена функциональная схема запоминающего устройства; на фиг, 2 - функциональная схема синхронизатора; на фиг, 3 - эпюры,пояс- няющие работу запоминающего устройства.

Запоминающее устройство (фиг. 1) содержит регистры 1-4, элемент И 5, синхронизатор 6, сумматоре 7, счетчики 8 и 9, блоки 10 и П памяти5 триггер 12, элемент ИЛИ 13 и элемент 14 задержки. Вход регистра 1 является первым входом 15 устройства, вход синхронизатора 6 вторым входом 6, а выход элемента 13 выходом I7 устройства.

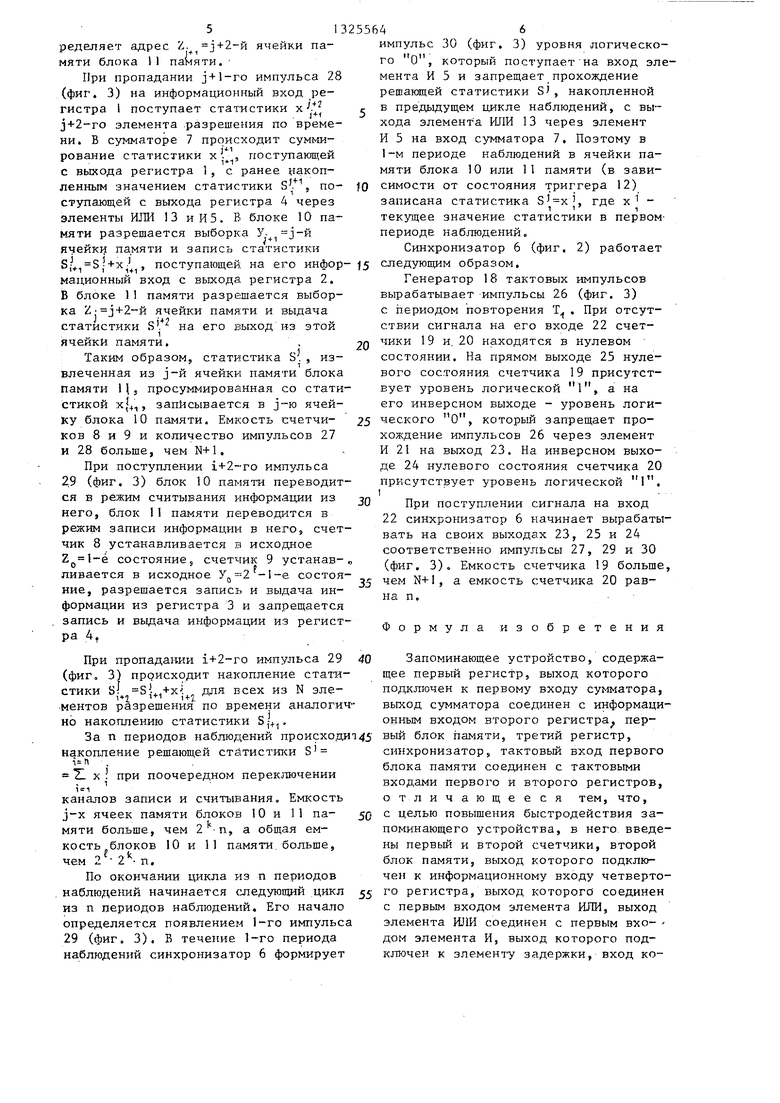

Синхронизатор 6 содержит генератор 18 тактовых импульсов, счетчики 19 и 20 и элемент И 21,

В предлагаемом запоминающем устройстве выходы синхронизатора 6 подключены к входам регистров 3 и 4,

10

/,

30

40

счетчиков 8 и 9,-5локов 10 и 11 памяти, триггера 12, элемента И 5 и элемента 14 задержки. Выход элемента 14 задержки подключен к входам регистров 1 и .2, счетчиков 8 и 9s блоков 10 и 1} памяти-. Регистр 1 , сумматор 7 и регистр 2 последовательно соединены, Выходы триггера 12 подзслючены к входам регистров 3 и 4, блоков 10 и 11 . памяти.и счетчиков 8 и 9. Выход регистра 2 соединен с информационными . входами блоков 10 и 11 памяти. Счетчик 8, блок 10 памяти и регистр 3 последовательно соединены. Также последовательно соединены счетчик 9, блок П памяти и регистр 4, Элемент ИЛИ 13 соединен с элементом И 5 и регистрами 3 и 4, Выход элемента И 5 подключен к входу сумматора 7, Вход 15 регистра 1 является первым входом запоминающего устройства, вторым входом 16 которого является вход синхро- 50 нцзатора 6, а выходом 17 - выкод элемента ИПИ 13,

В синхронизаторе 6 генератор 18 тактовых импульсов, счетчик 19 и

рые входь счетчиков 19 и 2.0, Первым 23, вторым 24 и третьим 25 выходами синхронизатора 6 соответственно являются выход элемента И 21, выход счетчика, 20 и первый выход счетчика 19, На фиг, 3 обозначены импульсы 25-30,

Запоминающее устройство (ЗУ) работает следующим образом.

На вход 15 (ЗУ) поступает текущее значение статистики в виде К-разряд- ного цифрового параллельного двоичного кода последовательно для каждого j-ro элемента из N элементов разреше- j. ния (например, по дальности, по времени и т,п,), где ,,«,,N.

Сигнал, поступающий на вход 16 ЗУ, разрешает формирование импульсов 27, 29 и 30 (фиг. 3) на выходе синхронизатора 6, Вычисление решающей стати- 2D . -п

.,(,:--(.

стики Ь 2- 5 сводится к синхронно -1 ;

му накоплению статистики х: за п периодов наблюдений (,.o,,n),

„(. В i-M периоде наблюдения в ЗУ на- . I ,

коплена статистика Si 2 х для всех .

из i элементов разрешения. Триггер 12

находится в одном из двух своих устойчивых состояний, например в нулевом. При этом на его прямом выходе

tin

присутствует уровень логического О а на инверсном уровень логической I, По окончании i-ro периода наблюдения на счетный вход триггера 12 по- 35 ступает i+1-й импульс 29 (фиг, 3) -с синхронизатора 6, свидетельствующий о начале 1+1-го периода наблюдения. Счетчики 8 и 9 переводятся в режим установки кода исходного состояния, а триггер 12 изменяет свое устойчивое состояние и на его прямом выходе появляется уровень логической l.

45

а на инверсном - уровень логическо- го о,

Сигнал, логической 1 с прймого выхода триггера 12 поступает на информационный вход 1-го младшего разряда счетчика 9 и информационные входы 1-1 старших разрядов счетчика 8, переводит блок 10 памяти в режим записи информации, поступает на вход регистра 3, запрещает запись и выдачу информации из него,

Сигнал логического О с инверссчетчик 20 последовательно соединены, выхода триггера 12 поступает на

Входы элемента И 21 подключены к вы-информационный вход 1-го младшего

ходам генератора 18 тактовых импуль-разряда счетчика 8 и информационные

сов и счетчика 19. Входом 22 синхро-входы 1-1 старишх разрядов счетчика

низатора 6 являются объединенные вто-9, переводит блок 11 памяти в режим

рые входь счетчиков 19 и 2.0, Первым 23, вторым 24 и третьим 25 выходами синхронизатора 6 соответственно являются выход элемента И 21, выход счетчика, 20 и первый выход счетчика 19, На фиг, 3 обозначены импульсы 25-30,

Запоминающее устройство (ЗУ) работает следующим образом.

На вход 15 (ЗУ) поступает текущее значение статистики в виде К-разряд- ного цифрового параллельного двоичного кода последовательно для каждого j-ro элемента из N элементов разреше- ния (например, по дальности, по времени и т,п,), где ,,«,,N.

Сигнал, поступающий на вход 16 ЗУ, разрешает формирование импульсов 27, 29 и 30 (фиг. 3) на выходе синхронизатора 6, Вычисление решающей стати- . -п

.,(,:--(.

стики Ь 2- 5 сводится к синхронно -1 ;

му накоплению статистики х: за п периодов наблюдений (,.o,,n),

В i-M периоде наблюдения в ЗУ на- . I ,

коплена статистика Si 2 х для всех .

из i элементов разрешения. Триггер 12находится в одном из двух своих устойчивых состояний, например в нулевом. При этом на его прямом выходе

40

50

tin

присутствует уровень логического О а на инверсном уровень логической I, По окончании i-ro периода наблюдения на счетный вход триггера 12 по- 35 ступает i+1-й импульс 29 (фиг, 3) -с синхронизатора 6, свидетельствующий о начале 1+1-го периода наблюдения. Счетчики 8 и 9 переводятся в режим установки кода исходного состояния, а триггер 12 изменяет свое устойчивое состояние и на его прямом выходе появляется уровень логической l.

а на инверсном - уровень логическо- го о,

Сигнал, логической 1 с прймого выхода триггера 12 поступает на информационный вход 1-го младшего разряда счетчика 9 и информационные входы 1-1 старших разрядов счетчика 8, переводит блок 10 памяти в режим записи информации, поступает на вход регистра 3, запрещает запись и выдачу информации из него,

Сигнал логического О с инверсчтения информации, поступает на вход регистра 4 и разрешает запись и выдачу информации из него.

При наличии i+1-гс импульса 29 (фиг. 3) синхронизации счетчик 8 г- устанавливается в свое (2-1) исходное состояние, а счетчик 9 - в первое свое исходное состояние. Двоичный 1-разрядный код четчиков 8 и 9 определяет адреса чеек элементов памяти в блоках 10 и 11 памяти соответственно. По окончании импульса 29 счетчики 8 и 9 переходят в режим суммирования импульсов 28, поступающих с элемента 14 задержки (фиг. 3) на их счетные входы. Элементом 14 задержки передний и задний фронты импульсов 27 (фиг.З), вырабатываемых синхронизатором 6, задерживаются на величину, необходимую для передачи информации из блока 10 памяти или 11 в регистр 3 или 4.

В i+1-м периоде .наблюдения вычисение статистики S S +x | для каждого из j элементов разрешения по времени происходит по принципу поточного метода обработки информации, при котором различные узлы схемы выполняют операции, соответствующие различным (соседним) интервалам разрешения по времени. Интервал разрешения по времени определяется периодом Т следования импульсов 27 (фиг. 3). Так как на счетные входы счетчиков 8 и 9 поступают одни и те же импульсы 28 (фиг. 3), У -е состояние счетчика 8 и Zj-e состояние счетчика 9 связывает соотношение ,--2.

Перед появлением j-x импульсов 27 и 28 на выходах синхронизатора 6 и элемента 14 задержки (фиг. 3) на ин- формационньй вход регистра 1 поступает статистика х 1 j-ro элемента разрешения по времени. В сумматоре 7 происходит суммирование статистики X + , поступающей с выхода регистра 1, с ранее накопленным значением ста--, тистики , поступающим с выхода регистра 4 через элементы ИЛИ 13 и И 5. В блоке 10 памяти разрешается выборка У.з-2-й ячейки памяти и запись статистики S, поступающей на его информационный вход с выхода регистра 2, в эту ячейку памяти. В блоке 11 памяти разрешается выборка Z,,-й ячейки памяти и выдача статистики на его выход из этой ячейки памяти.

,

325564. .

При поступлении j-ro импульса 27 (фиг. 3) на тактовый вход регистра 4 в него записывается величина S, поступающая на его информационный вход с выхода блока 11 памяти. В регистр 3 информация не записывается.

При поступлении j-ro импульса 28 (фиг. 3) на тактовые входы регистров I и 2, блока 10 памяти и счетные входы счетчиков 8 и 9 происходит следующее. В блоках 10 и 11 памяти за- |прещается выборка ячеек памяти. В регистр записывается значение статис10

тики X. , поступающей на его инфор

SM мационный вход. Значение статистики

Sl с выхода сумматора 7 записываетг ся в регистр 2, Счетчик 8 переходит в состояние и определяет адрес у, ячейки памяти блока 10 памяти. Счетчик 9 переходит в Z.-e состояние и определяет адрес Z J+l-й ячейки памяти блока 11 памяти.

При пропадании j-ro импульса 28 (фиг. 3) на информационный вход регистра 1 поступает статистика х j+1-го элемента разрешения по времени. В сумматоре 7 происходит суммирование статистики x-t , поступающей с выхода регистра 1, с ранее накоплен- нь1м значением статистики S, поступа- ющей-с выхода регистра 4 через элементы ИЛИ 13 и И 5. В блоке 10 памяти разрешается выборка У- j-1-й.ячейки, памя.ти и запись статистики S ,

S ., поступающей на его информационный вход с выхода регистра 2. В блоке 11 памяти разрешается выборка 2,- + 1-й ячейки памяти и выдача статистики S из этой ячейки памяти.

- При поступлении j+1-го импульса 27 (фиг. 3) на тактовый вход регистра 4 в него записывается величина S , поступающая на его информационный вход с выхода блока 11 памяти.

В регистр 3 информация не записывается.

При поступлении j+1-го импульса 28 (фиг. 3) на тактовые входы регистров 1 и 2, блоков IО и 11 памяти и счетные входы счетчиков 8 и 9 происходит следующее. В регистр 1 записывается значение статистики х., поступающей на его информационньй вход. Значение статистики S|,S,+x , с выхода сумматора 7 записывается в регистр 2. Счетчик 8 переходит в У),-е состояние и определяет адрес У. ячейки памяти блока 10 памяти. Счетчик 9 переходит в состояние и определяет адрес L. j+2-ft ячейки памяти блока 11 памяти,При пропадании j+1-го импульса 28 (фиг. 3) на информационный вход регистра I поступает статистики х . j 4.2-го элемента разрешения по времени. В сумматоре 7 происходит суммирование статистики х ., поступающей с выхода регистра 1 , с ранее tiaKOn- ленным значением статистики поступающей с выхода регистра 4 через элементы ИЛИ 13 и И 5. В блоке 10 памяти разрешается выборка У.З-Й ячейки памяти и запись статистики

S,,S +Х- , поступающей на его инфор

мационный вход с выхода регистра 2. В блоке 11 памяти разрешается выборка Z j+2-й ячейки памяти и выдача

}

:)2

статистики S . на его выход из этой ячейки памяти.

Таким образом, статистика s , извлеченная из j-й ячейки памяти блока памяти J просуммированная со статистикой xj+n записывается в j-ю ячейку блока 10 памяти. Емкость счетчиков 8 и 9 и количество импульсов 27 и 28 больще, чем N+1.

При поступлении i+2-го импульса 2.9 (фиг. 3) блок 10 памяти переводится в режим считывания информации из него, блок 1 памяти переводится в режим записи информации в него, счетчик 8 устанавливается в исходное

9 устанав

состояние 5 счетчик ливается в исходное 7 2-1-6 состояние, разрешается запись и выдача информации из регистра 3 и запрещается запись и вьщача информации из регистра 4,

При пропадании i+2-го импульса 29 40 (фиг, 3) происходит накопление статистики s| 51ч1 5 л для всех из N эле- .ментов разрешения по времени аналогично накоплению статистики S

)

1+1

Запоминающее устройство, содер щее первый регистр, выход которог подключен к первому входу суммато выход сумматора соединен с информ онным входом второго регистра пе

За п периодов наблюдений происходат45 вый блок памяти, третий регистр.

накопление решающей стйтистшси S .

X при поочередном переключении i i

каналов записи и считывания. Емкость J-X ячеек памяти блоков 10 и 11 памяти больше, чем 2 п, а общая ем- кость-блоков 10 и П памяти больще,

чем

г. п.

синхронизатор, тактовый вход перв блока памяти соединен с тактовыми входами первого и второго регистр отличающее ся тем, что

50 с целью повышения быстродействия поминающего устройства, в него, вв ны первый и второй счетчики, втор блок памяти, выход которого подкл чен к информационному входу четве

По окончании цикла из п периодов наблюдений начинается следуюсций цикл из п периодов наблюдений. Его начало определяется появлением 1-го импульса 29 (фиг. 3). В течение 1-го периода наблюдений синхронизатор 6 формирует

импульс 30 (фиг. 3) уровня логического о, который поступает на вход элемента И 5 и запрещает прохождение решающей статистики SJ, накопленной в предыдущем цикле наблюдений, с выхода элемент а ИЛИ 13 через элемент И 5 на вход сумматора 7. Поэтому в 1-м периоде наблюдений в ячейки памяти блока 10 или И памяти (в зависимости от состояния триггера 12) записана статистика , где х - теку)чее значение статистики в первом- периоде наблюдений.

Синхронизатор 6 (фиг. 2) работает

следующим образом.

Генератор 18 тактовых импульсов вырабатывает импульсы 26 (фиг. 3) с периодом повторения Т . При отсутствии сигнала на его входе 22 счетчики 19 и. 20 находятся в нулевом состоянии. На прямом выходе 25 нулевого состояния счетчика 19 присутст

вует уровень логической 1 , а на его инверсном выходе - уровень логи- веского О, который запрещает прохождение импульсов 26 через элемент И 21 на выход 23. На инверсном выходе 24 нулевого состояния счетчика 20 присутствует уровень логической 1.

При поступлении сигнала на вход 22 синхронизатор 6 начинает вырабатывать на своих выходах 23, 25 и 24 соответственно импульсы 27, 29 и 30 (фиг. 3). Емкость счетчика 19 больше, чем N+1, а емкость счетчика 20 равна п.

Формула изобретения

Запоминающее устройство, содержащее первый регистр, выход которого подключен к первому входу сумматора, выход сумматора соединен с информационным входом второго регистра персинхронизатор, тактовый вход первого блока памяти соединен с тактовыми входами первого и второго регистров, отличающее ся тем, что,

с целью повышения быстродействия запоминающего устройства, в него, введены первый и второй счетчики, второй блок памяти, выход которого подключен к информационному входу четвертого регистра, выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соединен с первым вхо- - дом элемента И, выход которого подключен к элементу задержки, вход которого подключен к первому выходу cHHxpoHHsatopa и тактовым входам третьего и четвертого регистров, а выход соединен с тактовыми входами пер- вого и второго счетчиков блоков па- MJfTH и счетными входами первого и второго счетчиков, второй выход синхронизатора подключен к второму входу элемента И, выход которого соединен с вторым входом сумматора, третий выход синхронизатора подключен к управляющим входам первого и второго счетчиков и счетному входу триггера, прямой выход которого соединен с последовательным информационным входом второго счетчика и параллельными информационными входами первого счётчика, а инверсньй выход - с последовательным информационным входом перво- . го счетчика и параллельным информационным входом второго счетчика, пря18

Ч

22

10

2556А

мой выход TpHrrejia соединен с входом сброса третьего регистра и управляющим входом первого блока памяти, а инверсный выход триггера - с входом сброса четвертого регистра н управлянщим входом второго блока памяти, адресные входы первого и второго блоков памяти подключены к выходам первого и второго счетчиков соответственно, первый вход второго блока памяти соединен с выходом второго регистра, выход третьего регистра- подключен к второму входу элемента ИЛИ, выход которого является информационным выходом запоминающего устройства, информационный вход первого регистра является информационным входом запоминающего устройства, а ртробирующий вход синхронизатора - стробируюпщм входом запоминающего устройства.

15

20

21

23

25,

Фиг,2

--4

24

«

1325564 Г,

«JMJllltUlJllUlIUlMJULMMM .rJlMMllJLlJlJL «JUlJimJUUUJLJlJlJlJL

n-1 n 1 Z {,

JL ЛЯЯЛЯЛ

ЪГ

fpu3.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство выделения полезного сигнала | 1984 |

|

SU1236398A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Формирователь кодов радиально-круговой развертки для индикатора кругового обзора | 1986 |

|

SU1401422A2 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

Изобретение относится к вычислительной технике, в частности к за- поминаю1цим устройствам для накопле15 В НИН результата. Цель изобретения - повышение быстродействия запоминающего устройства. Поставленная цель достигается за счет обеспечения многоканальным накапливающим сумматором совмещения операций суммирования, записи и считывания текущей и пре- дьщущей решающей статистики в одних и тех же ячейках ОЗУ для одних и тех же элементов разрешения за h периодов наблюдений в реальном масштабе времени. Устройство содержит регистры 1-4, элемент И 5, синхронизатор 6, сумматор 7, счетчики 8, 9, блоки памяти Ю, 11, триггер 12-, элемент ИЛИ 13, элемент 14 задержки. 3 ил. 17

| Параллельный накапливающий сумматор | 1979 |

|

SU813416A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Акимов П.С | |||

| Основы помехозащиты - М.: МВТУ им | |||

| Н.Э.Баумана, 1980, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

Авторы

Даты

1987-07-23—Публикация

1985-04-02—Подача