Изобретение относится к импульсной технике и может быть использовано для построения высоконадежных цифровых систем, в частности высокочастотных хранителей времени.

Цель изобретения - повышение достоверности функционирования устройства за счет дополнительной стабилизации частоты формируемого сигнала.

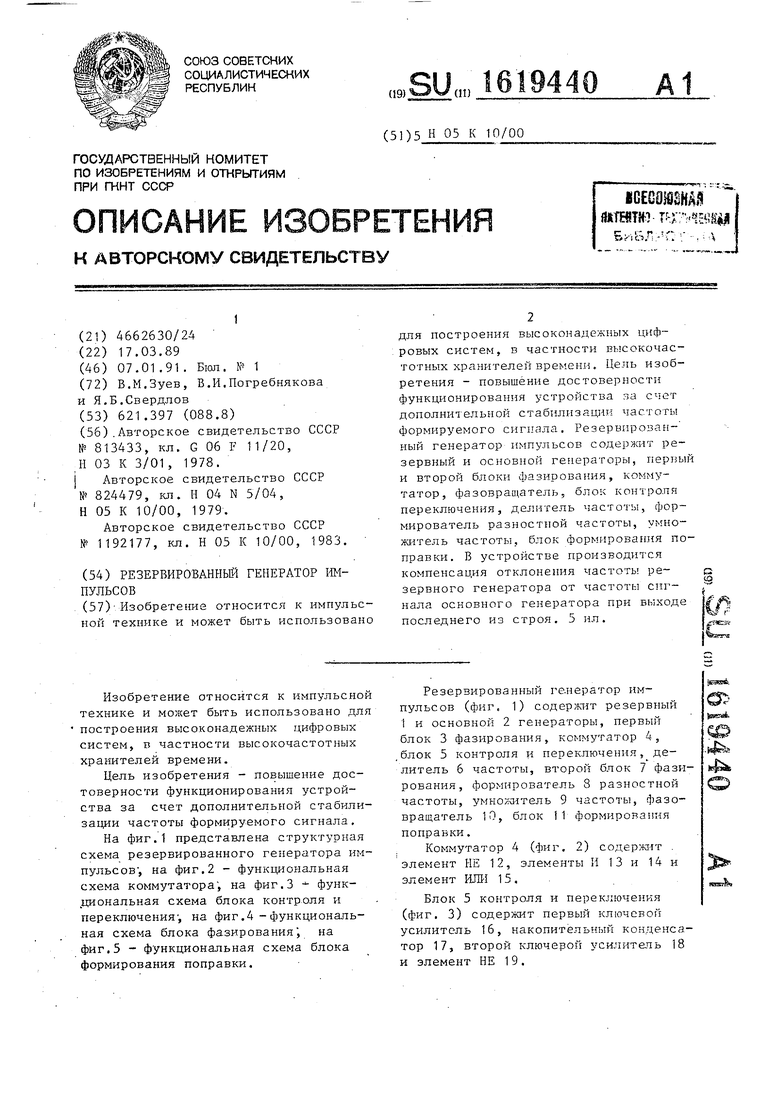

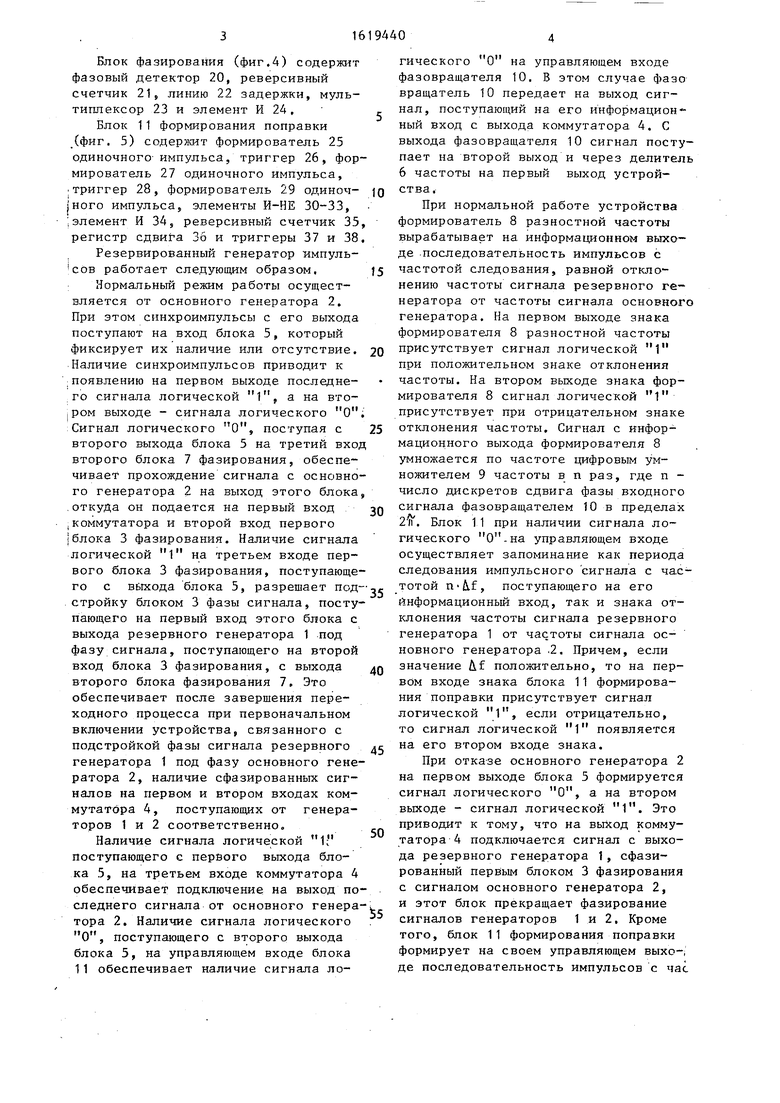

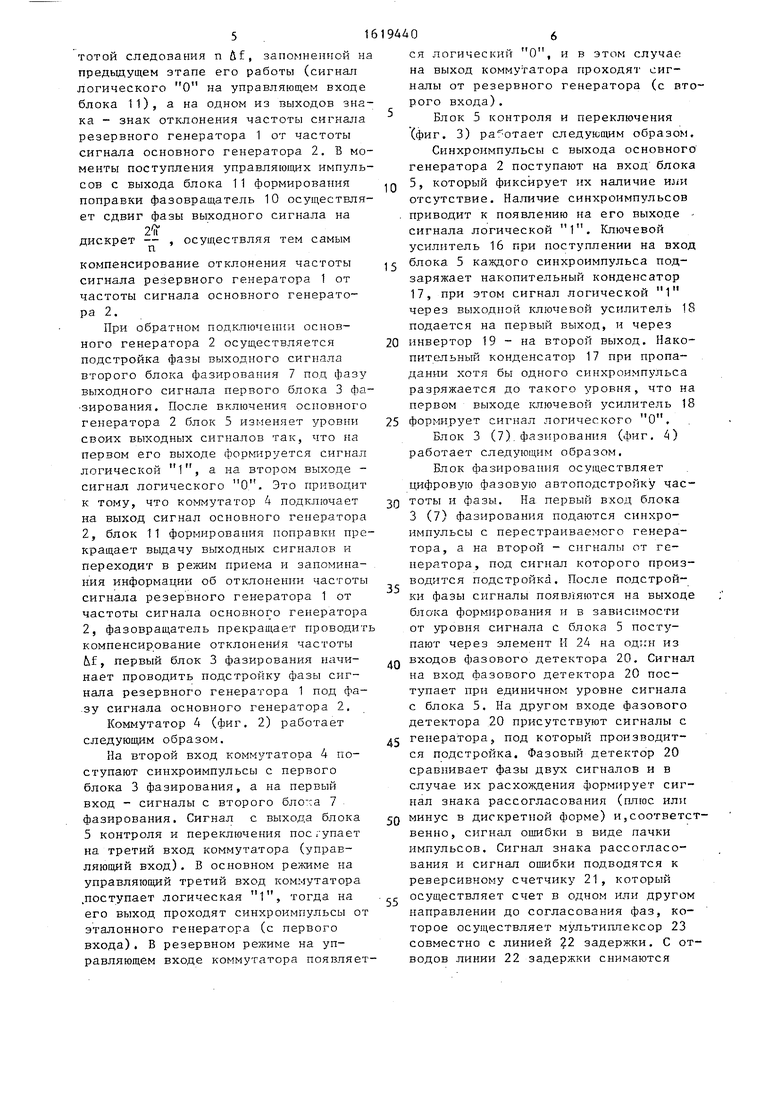

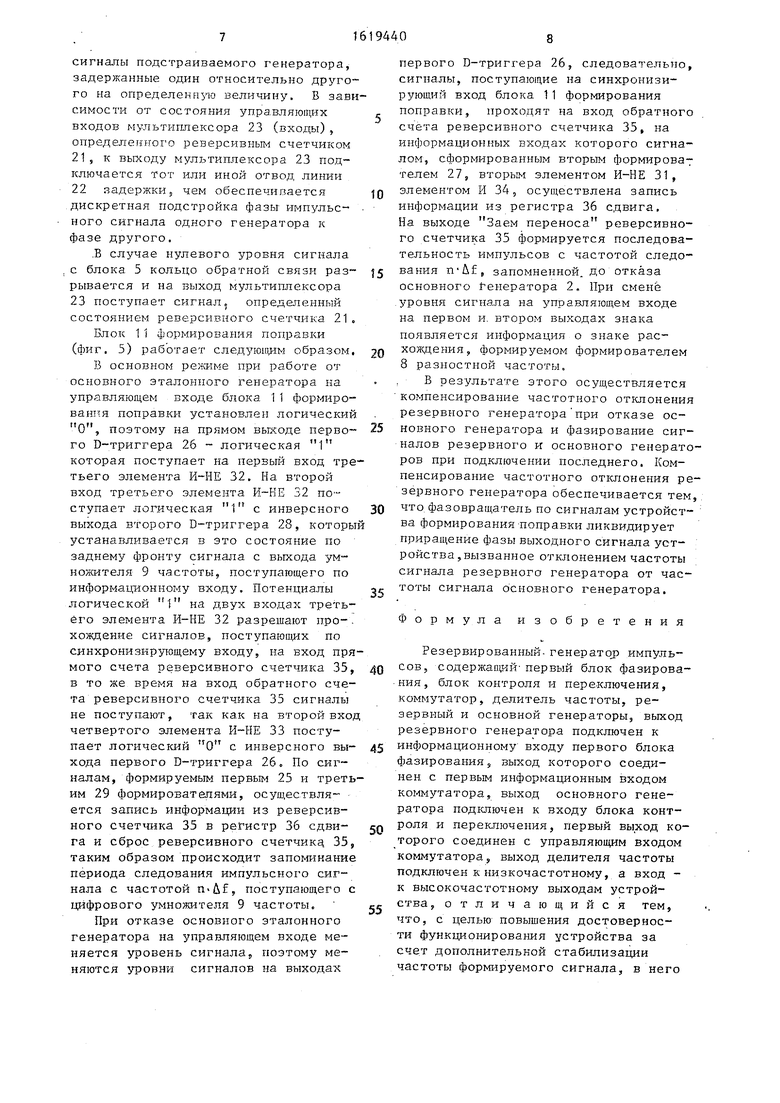

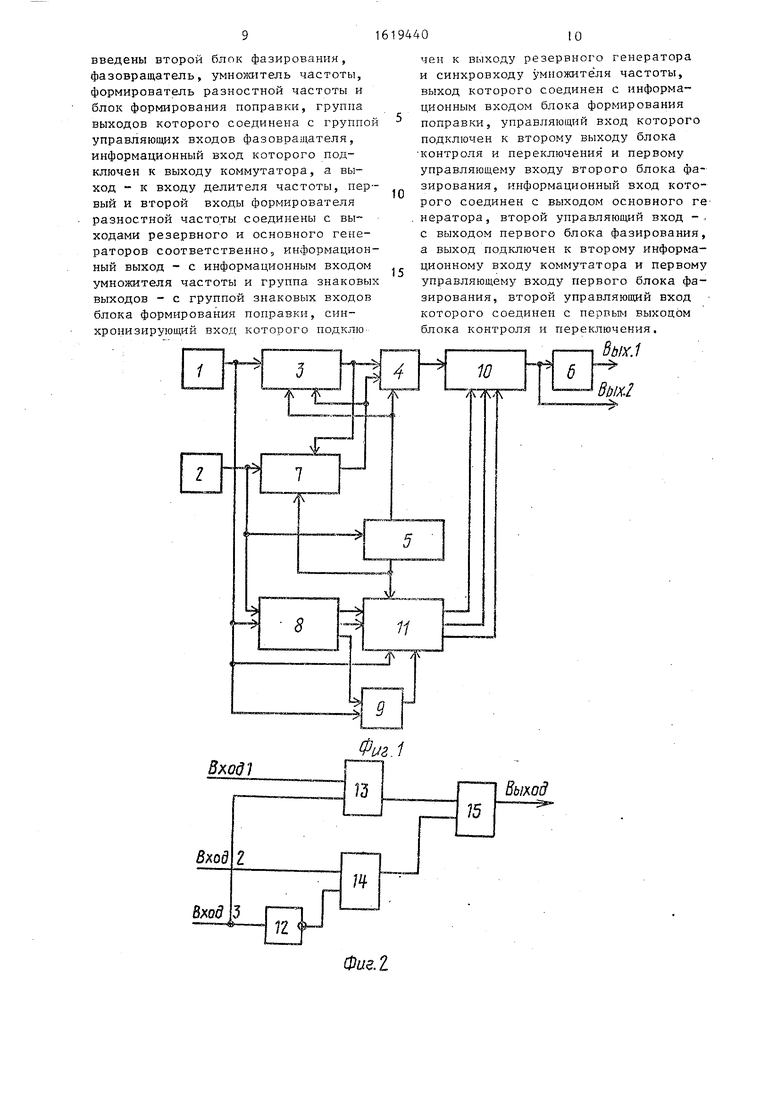

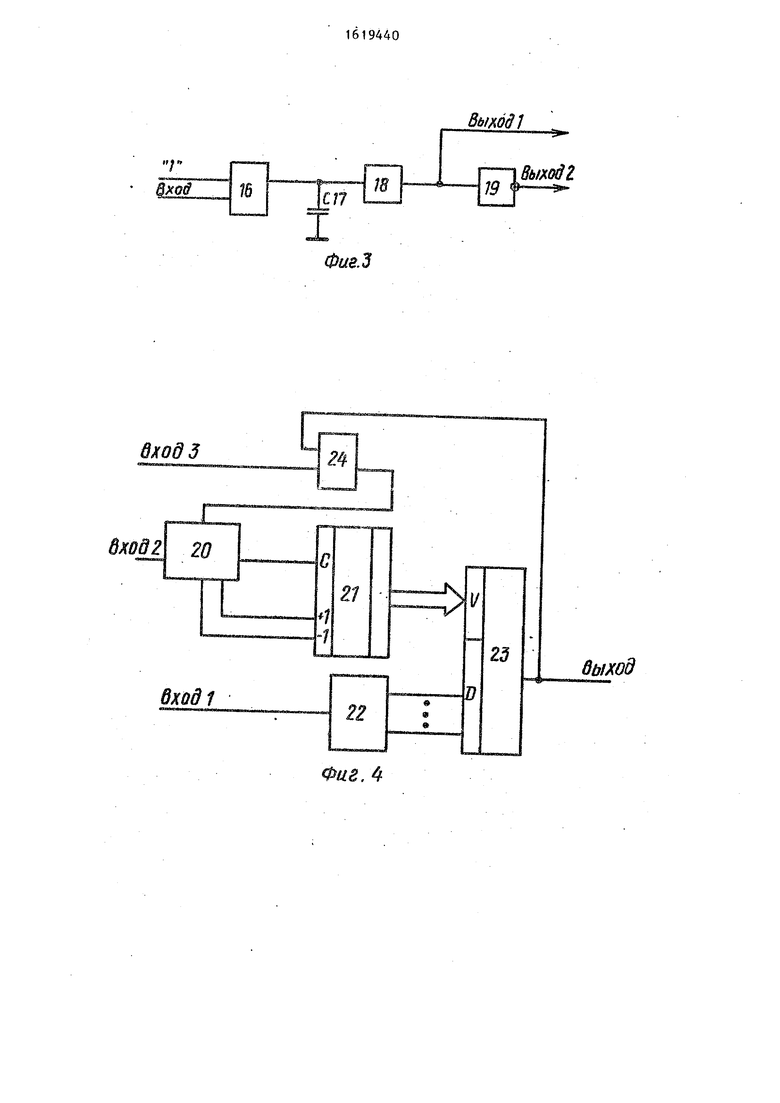

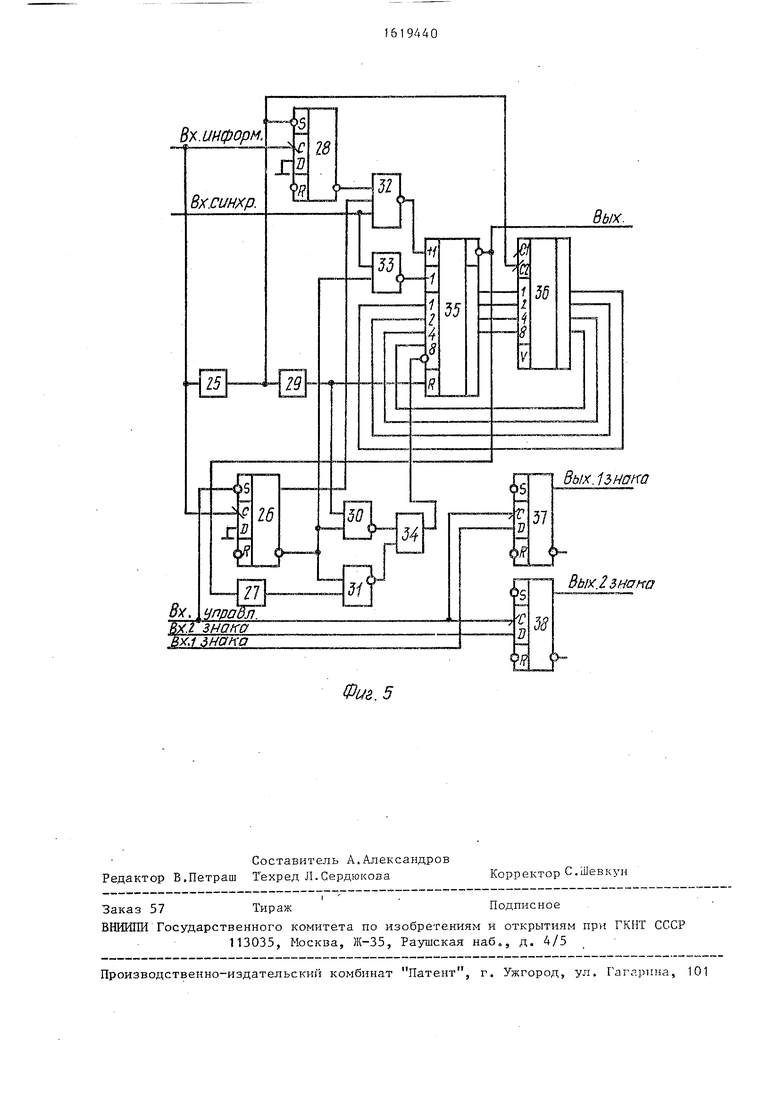

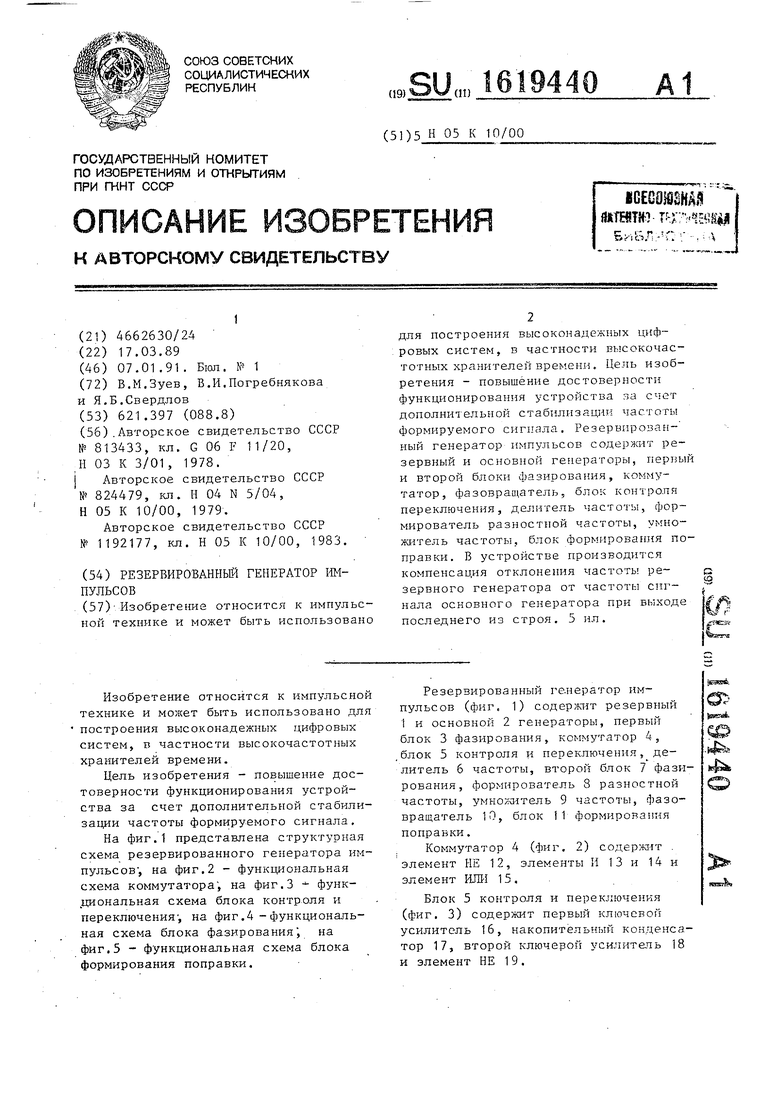

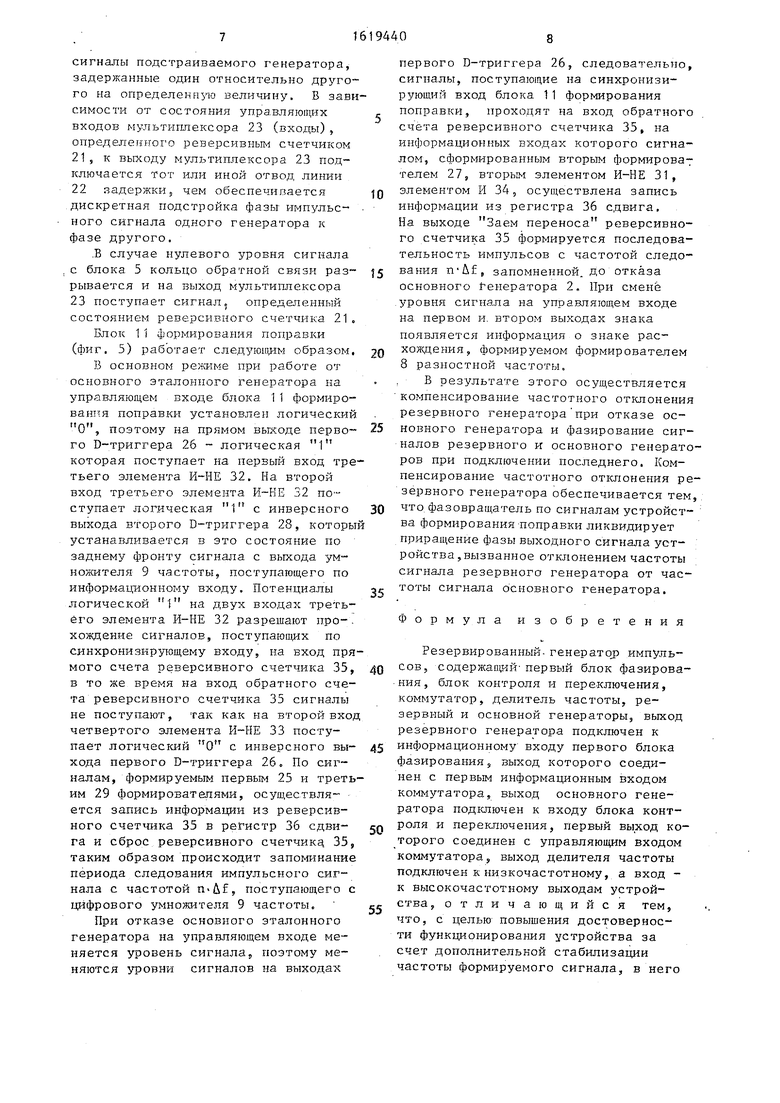

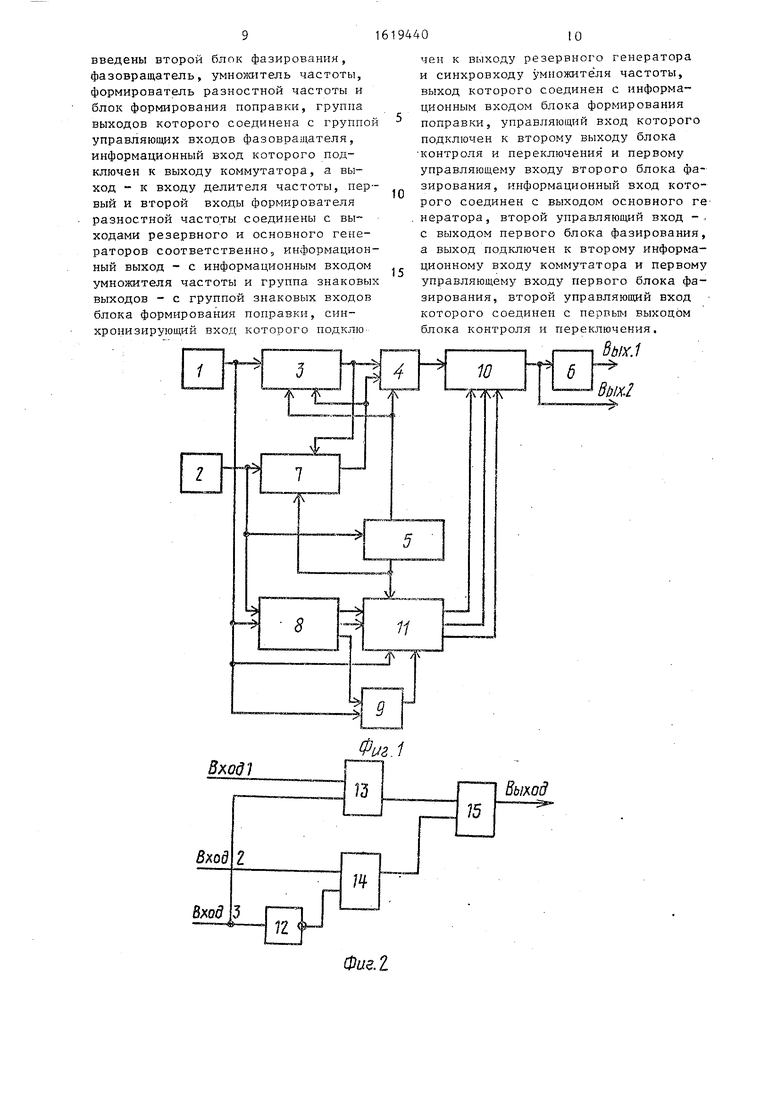

На фиг.1 представлена структурная схема резервированного генератора импульсов , на фиг.2 - функциональная схема коммутатора; на фиг.З - функ- диопальная схема блока контроля и переключения , на фиг.4 - функциональная схема блока фазирования , на фиг,5 - функциональная схема блока формирования поправки.

Резервированный генератор импульсов (фиг. 1) содержит резервный I и основной 2 генераторы, первый блок 3 фазирования, коммутатор 4, .блок 5 контроля и переключенияч делитель 6 частоты, второй блок 7 фазирования, формирователь 8 разностной частоты, умно/ о т ель 9 частоты, фазовращатель 10, блок 11 формирования поправки.

Коммутатор 4 (фиг. 2) содержит элемент НЕ 12, элементы И 13 и 14 и элемент ИЛИ 15.

Блок 5 контроля и переключения (фиг. 3) содержит первый ключевой усилитель 16, накопительный конденсатор 17, второй ключевой усилитель 18 и элемент НЕ 19.

Блок фазирования (фиг.4) содержит фазовый детектор 20, реверсивный счетчик 21, линию 22 задержки, мультиплексор 23 и элемент И 24 ,

Блок 11 формирования поправки (фиг. 5) содержит формирователь 25 одиночного импульса, триггер 26, формирователь 27 одиночного импульса, триггер 28, формирователь 29 одиноч- JHoro импульсаs элементы И-НЕ 30-33, , элемент И 34, реверсивный счетчик 35, регистр сдвига 36 и триггеры 37 и 38. Резервированный генератор импуль- сов работает следующим образом,

Нормальный режим работы осуществляется от основного генератора 2. При этом синхроимпульсы с его выхода поступают на вход блока 5, который фиксирует их наличие или отсутствие. Наличие синхроимпульсов приводит к появлению на первом выходе последнего сигнала логической 1м, а на втором выходе - сигнала логического О. Сигнал логического О, поступая с второго выхода блока 5 на третий вход второго блока 7 фазирования, обеспечивает прохождение сигнала с основного генератора 2 на выход этого блока, откуда он подается на первый вход ,коммутатора и второй вход первого jблока 3 фазирования. Наличие сигнала логической 1 на третьем входе первого блока 3 фазирования, поступающего с выхода блока 5, разрешает под- стройку блоком 3 фазы сигнала, поступающего на первый вход этого блока с выхода резервного генератора 1 под фазу сигнала, поступающего на второй вход блока 3 фазирования, с выхода второго блока фазирования 7, Это обеспечивает после завершения переходного процесса при первоначальном включении устройства, связанного с подстройкой фазы сигнала резервного генератора 1 под фазу основного генератора 2, наличие сфазированных сигналов на первом и втором входах коммутатора 4, поступающих от генераторов 1 и 2 соответственно.

Наличие сигнала логической 1 поступающего с первого выхода блока 5, на третьем входе коммутатора 4 обеспечивает подключение на выход последнего сигнала от основного генератора 2. Наличие сигнала логического О, поступающего с второго выхода блока 5, на управляющем входе блока 11 обеспечивает наличие сигнала ло

Q 5

0 5 о Q 5

0

5

гического О на управляющем входе фазовращателя 10. В этом случае фазо вращатель 10 передает на выход сигнал, поступающий на его информационный вход с выхода коммутатора 4. С выхода фазовращателя 10 сигнал поступает на второй выход и через делитель 6 частоты на первый выход устройства.

При нормальной работе устройства формирователь 8 разностной частоты вырабатывает на информационном выходе последовательность импульсов с частотой следования, равной отклонению частоты сигнала резервного генератора от частоты сигнала основного генератора. На первом выходе знака формирователя 8 разностной частоты присутствует сигнал логической 1 при положительном знаке отклонения частоты. На втором выходе знака формирователя 8 сигнал логической 1 присутствует при отрицательном знаке отклонения частоты. Сигнал с информационного выхода формирователя 8 умножается по частоте цифровым умножителем 9 частоты в п раз, где п - число дискретов сдвига фазы входного сигнала фазовращателем 10 в пределах 2 П. Блок 1 1 при наличии сигнала логического управляющем входе осуществляет запоминание как периода следования импульсного сигнала с частотой пif, поступающего на его информационный вход, так и знака отклонения частоты сигнала резервного генератора 1 от частоты сигнала основного генератора .2. Причем, если значение &f положительно, то на первом входе знака блока 11 формирования поправки присутствует сигнал логической 1, если отрицательно, то сигнал логической 1 появляется на его втором входе знака.

При отказе основного генератора 2 на первом выходе блока 5 формируется сигнал логического О, а на втором выходе - сигнал логической 1. Это приводит к тому, что на выход коммутатора 4 подключается сигнал с выхода резервного генератора 1, сфази- рованный первым блоком 3 фазирования с сигналом основного генератора 2, и этот блок прекращает фазирование сигналов генераторов 1 и 2, Кроме того, блок 11 формирования поправки формирует на своем управляющем выхо-, де последовательность импульсов с час

5

тотой следования n Uf, запомненной н предыдущем этапе его работы (сигнал логического О на управляющем входе блока 11), а на одном из выходов знака - знак отклонения частоты сигнала резервного генератора 1 от частоты сигнала основного генератора 2. В моменты поступления управляющих импульсов с выхода блока 11 формирования поправки фазовращатель 10 осуществляет сдвиг фазы выходного сигнала на

2$

дискрет - , осуществляя тем самым

компенсирование отклонения частоты сигнала резервного генератора 1 от частоты сигнала основного генератора 2.

При обратном подкгпочешга основного генератора 2 осуществляется подстройка фазы выходного сигнала второго блока фазирования 7 под фазу выходного сигнала первого блока 3 фазирования. После включения основного генератора 2 блок 5 изменяет уровни своих выходных сигналов так, что на первом его выходе формируется сигнал логической 1, а на втором выходе - сигнал логического О. Это приводит к тому, что коммутатор 4 подключает на выход сигнал основного генератора 2, блок 11 формирования поправки прекращает выдачу выходных сигналов и переходит в режим приема и запоминания информации об отклонении частоты сигнала резервного генератора 1 от частоты сигнала основного генератора 2, фазовращатель прекращает проводит компенсирование отклонения частоты &f, первый блок 3 фазирования начинает проводить подстройку фазы сигнала резервного генератора 1 под фазу сигнала основного генератора 2,

Коммутатор 4 (фиг. 2) работает следующим образом.

На второй вход коммутатора 4 поступают синхроимпульсы с первого блока 3 фазирования, а на первый вход - сигналы с второго 7 фазирования. Сигнал с выхода блока 5 контроля и переключения поступает на третий вход коммутатора (управляющий вход). В основном режиме на управляющий третий вход коммутатора .поступает логическая 1, тогда на

его выход проходят синхроимпульсы от эталонного генератора (с первого входа). В резервном режиме на управляющем входе коммутатора появляет0

5

0

9440б

ся логический О, и в этом случае на выход коммутатора проходят сигналы от резервного генератора (с второго входа).

Блок 5 контроля и переключения (фиг. 3) работает следующим образом.

Синхроимпульсы с выхода основного генератора 2 поступают на вход блока 5, который фиксирует их наличие или отсутствие. Наличие синхроимпульсов приводит к появлению на его выходе сигнала логической 1. Ключевой усилитель 16 при поступлении на вход блока 5 каждого синхроимпульса подзаряжает накопительный конденсатор 17, при этом сигнал логической 1 через выходной ключевой усилитель 18 подается на первый выход, и через инвертор 19 - на второй выход. Накопительный конденсатор 17 при пропадании хотя бы одного синхроимпульса разряжается до такого уровня, что на первом выходе ключевой усилитель 18 5 формирует сигнал логического О.

Блок 3 (7) фазирования (фиг, 4) работает следующим образом.

Блок фазирования осуществляет цифровую фазовую автоподстройку частоты и фазы. На первый вход блока 3 (7) фазирования подаются синхроимпульсы с перестраиваемого генератора, а на второй - сигналы от генератора, под сигнал которого производится подстройка. После подстройки фазы сигналы появляются на выходе блока формирования и в зависимости от уровня сигнала с блока 5 поступают через элемент И 24 на од;:н из входов фазового детектора 20. Сигнал на вход фазового детектора 20 поступает при единичном уровне сигнала с блока 5. На другом входе фазового детектора 20 присутствуют сигналы с генератора, под который производится подстройка. Фазовый детектор 20 сравнивает фазы двух сигналов и в случае их расхождения формирует сигнал знака рассогласования (плюс или Q минус в дискретной форме) и,соответственно, сигнал ошибки в виде лачки импульсов. Сигнал знака рассогласования и сигнал ошибки подводятся к реверсивному счетчику 21, который осуществляет счет в одном или другом направлении до согласования фаз, которое осуществляет мультиплексор 23 совместно с линией 22 задержки. С отводов линии 22 задержки снимаются

0

5

0

5

5

сигналы подстраиваемого генератора, задержанные один относительно другого на определенную величину. В зависимости от состояния управляющих входов мультиплексора 23 (входы), определенного реверсивным счетчиком 21, к выходу мультиплексора 23 подключается тот или иной отвод линии

22задержкиs чем обеспечивается дискретная подстройка фазы импульсного сигнала одного генератора к

фазе другого.

В случае нулевого уровня сигнала с блока 5 кольцо обратной связи раз- рывается и на выход мультиплексора

23поступает сигнал, определенный состоянием реверсивного счетчика 21.

Блок 11 формирования поправки (фиг. 5) работает следующим образом,

В основном рехиме при работе от основного эталонного генератора на управляющем входе блока 11 формиро- ваш я поправки установлен логический О, поэтому на прямом выходе перво- го D-триггера 26 - логическая 1 которая поступает на первый вход третьего элемента И-ИЕ 32. На второй вход третьего элемента И-ПС 32 поступает логическая 1 с инверсного выхода второго D-триггера 28, которы устанавливается в это состояние по заднему фронту сигнала с выхода умножителя 9 частоты, поступающего по информационному входу. Потенциапы логической 1 на двух входах третьего элемента И-НЕ 32 разрешают прохождение сигналов, поступающих по синхронизирующему входу, на вход прямого счета реверсивного счетчика 35, в то же время на вход обратного счета реверсивного счетчика 35 сигналы не поступают, гак как на второй вход четвертого элемента И-НЕ 33 поступает логический О с инверсного вы- хода первого D-триггера 26. По сигналам, формируемым первым 25 и третьим 29 формирователями, осуществляется запись информации из реверсивного счетчика 35 в регистр 36 сдви- га и сброс реверсивного счетчика. 35, таким образом происходит запоминание периода следования импульсного сигнала с частотой , поступающего с цифрового умножителя 9 частоты.

При отказе основного эталонного генератора на управляющем входе меняется уровень сигналаj, поэтому меняются уровни сигналов на выходах

первого D-триггера 26, следовательно, сигналы, поступающие на синхронизирующий вход блока 11 формирования поправки, проходят на вход обратного счета реверсивного счетчика 35, на информационных входах которого сигналом, сформированным вторым формирова7 гелем 27, вторым элементом И-НЕ 31, элементом И 34, осуществлена запись информации из регистра 36 сдвига. На выходе Заем переноса реверсивного счетчика 35 формируется последовательность импульсов с частотой следования rruf, запомненной, до отказа основного генератора 2, При смене уровня сигнала на управляющем входе на первом и втором выходах знака появляется информация о знаке расхождения, формируемом формирователем 8 разностной частоты.

В результате этого осуществляется компенсирование частотного отклонения резервного генератора при отказе основного генератора и фазирование сигналов резервного и основного генераторов при подключении последнего. Компенсирование частотного отклонения резервного генератора обеспечивается тем что фазовращатель по сигналам устройства формирования поправки ликвидирует приращение фазы выходного сигнала устройства, вызванное отклонением частоты сигнала резервного генератора от частоты сигнала основного генератора.

Формула изобретения

Резервированный генерато р импульсов, содержащий первый блок фазирования, блок контроля и переключения, коммутатор, делитель частоты, резервный и основной генераторы, выход резервного генератора подключен к информационному входу первого блока фазирования, выход которого соединен с первым информационным входом коммутатора, выход основного генератора подключен к входу блока контроля и переключения, первый выход которого соединен с управляющим входом коммутатора, выход делителя частоты подключен к низкочастотному, а вход - к высокочастотному выходам устройства, отличающийся тем, что, с целью повышения достоверности функционирования устройства за счет дополнительной стабилизации частоты формируемого сигнала, в него

введены второй блок фазирования, фазовращатель, умножитель частоты, формирователь разностной частоты и блок формирования поправки, группа выходов которого соединена с группой управляющих входов фазовращателя, информационный вход которого подключен к выходу коммутатора, а выход - к входу делителя частоты, первый и второй входы формирователя разностной частоты соединены с выходами резервного и основного генераторов соответственно, информационный выход - с информационным входом умножителя частоты и группа знаковых выходов - с группой знаковых входов блока формирования поправки, синхронизирующий вход которого подклю

0

чен к выходу резервного генератора и сиихровходу умножителя частоты, выход которого соединен с информационным входом блока формирования поправки, управляющий вход которого подключен к второму выходу блока контроля и переключения и первому управляющему входу второго блока фазирования, информационный вход которого соединен с выходом основного ге нератора, второй управляющий вход - с выходом первого блока фазирования, а выход подключен к второму информационному входу коммутатора и первому управляющему входу первого блока фазирования, второй управляющий вход которого соединен с первым выходом блока контроля и переключения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный генератор импульсов | 1983 |

|

SU1192177A1 |

| Устройство фазирования шкалы времени электронных часов | 1982 |

|

SU1084720A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство синхронизации | 1984 |

|

SU1223390A1 |

| Цифровой фазовращатель | 1986 |

|

SU1372593A1 |

| СПОСОБ ФАЗИРОВАНИЯ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ ЗАДАННОЙ ЧАСТОТЫ В ПРОСТРАНСТВЕННО РАЗНЕСЕННЫХ ЦЕНТРАЛЬНОМ И ОКОНЕЧНОМ ПУНКТАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2057394C1 |

| Радиочастотный преобразователь разности фаз | 1984 |

|

SU1164625A1 |

| Имитатор радиосигналов | 1982 |

|

SU1067526A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1076934A1 |

Изобретение относится к импульсной технике и может быть использовано для построения высоконадежных цифровых систем, в частности высокочастотных хранителей времени. Цепь изобретения - повышение достоверности функционирования устройства та счет дополнительной стабилизациг частоты формируемого сигнала. Резервированный генератор импульсов содержит резервный и основной генераторы, первый и второй блоки фазирования, коммутатор, фазовращатель, блок контропя переключения, делитель частоты, формирователь разностной частоты, умножитель частоты, блок формирования поправки. В устройстве производится компенсация отклонения частоты резервного генератора от частоты сигнала основного генератора при выходе последнего из строя. 5 ил. с S9

Вход

Фиг.1

Фиг.1

Выход

Фиг.З

6x082

ФиВ. 4

Вы ход 1

Вх.информ.

BX.CUHXP.

16

r

ВУ.

упрадл.

ш

знака

ix/ знака

Фиг. 5

J2

o-i

5б/л-.

55

k

Й1

4«

J5

5wx. 1 знака

34

37

Ј

«LfВых.2 знака

38

| Резервированный генератор тактовыхиМпульСОВ | 1978 |

|

SU813433A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровое устройство автоматическойпОдСТРОйКи чАСТОТы и фАзы СиНХРОиМ-пульСОВ | 1979 |

|

SU824479A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-01-07—Публикация

1989-03-17—Подача