Изобретение относится к вычислительной технике и может быть использовано в Ьтатистических анализаторах . случайных процессов.

Целью изобретения является повышение быстродействия.

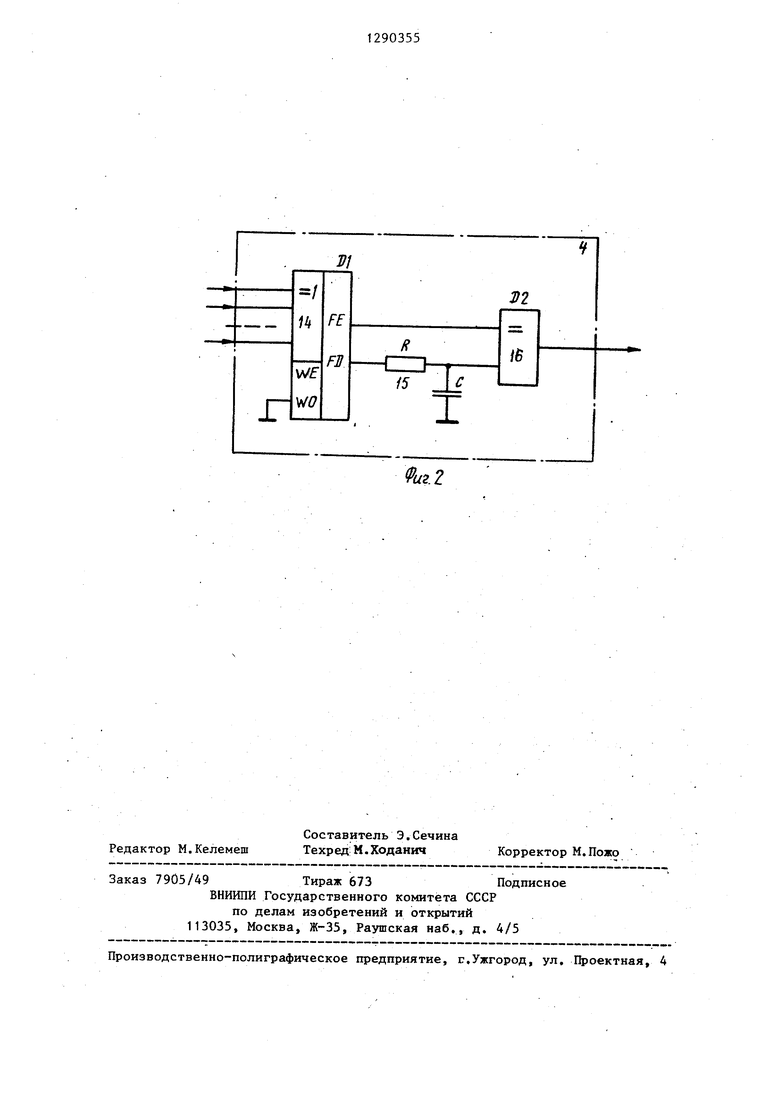

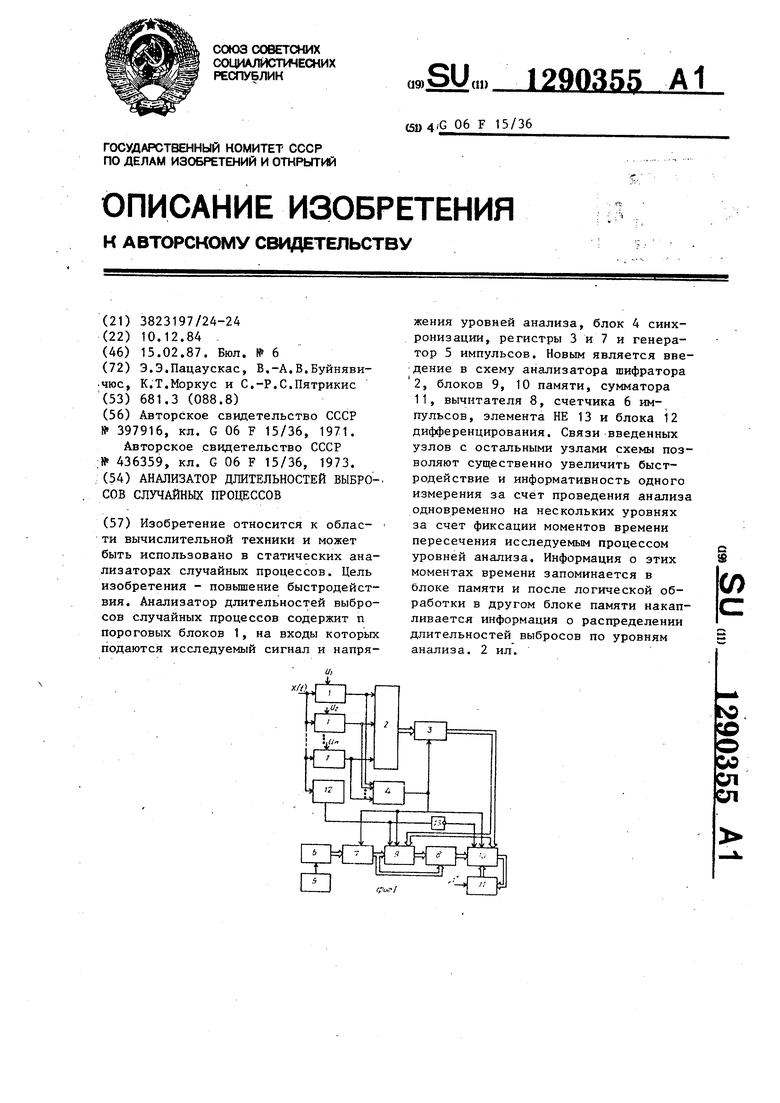

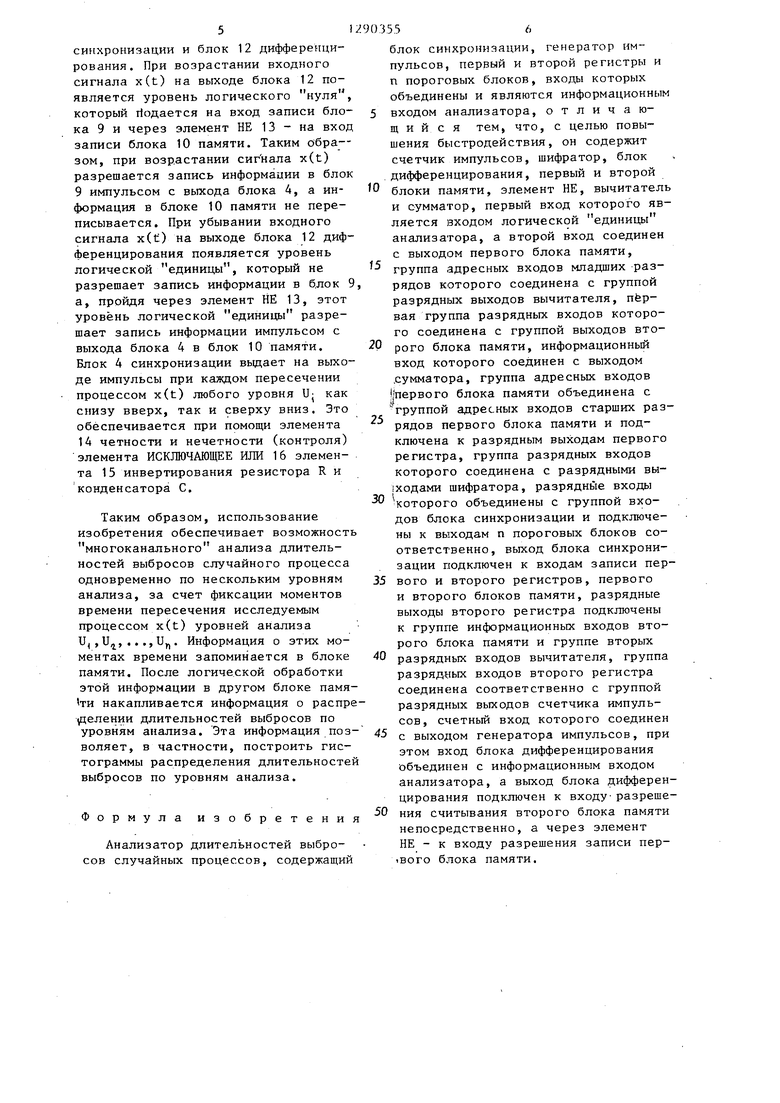

На фиг.1 представлена структурная схема предложенного анализатора; на фиг.2 схема блока синхронизации.

Анализатор содержит п пороговых .блоков 1, число которых определяется числом уровней одновременного анализа случайного сигнала x(t). На одни входы пороговых блоков 1 подается исследуемый x(t), а на другие входы - выбранные уровни анализа. Выходы пороговых блоков 1 соединены с входами шифратора 2, выходы кото- рого соединены с инфо)мадионными входами регистра 3, на вход записи которого подключен выход блока 4 синхронизации, выходы последнего соединены с выходами пороговых блоков 1. Генератор 5 импульсов соединен с входом счетчика 6 импульсов, выходы которого поразрядно соединены с информационными входами регистра 7, вход записи которого подключен к выходу блока 4 синхронизации. Выходы

регистра 7 поразрядно соединены с первыми входами вычитателя 8 и с ин- формационными входами блока 9 памя

гими входами вычитателя 8, выходы которого соединены с младшими адресными входами блока 10 памяти, старшие адресные входы которого поразрядно соединены с выходами регист- о вокупность входных сигналов преобра- ра 3. Выходы блока 10 памяти поразрядно соединены с одними входами

зуется в двоичный код, соответствующий номеру i-ro максимального уровсумматора 11, выходы которого соединены г информационными входами блока 10 памяти. На другой вход сумматора 11 подается напряжение, соот- ветствующее логической единице. На входы разрешения считывания блоков 9 и 10 памяти подключен выход блока 4 синхронизации. В анализаторе имеется блок 12 дифференцирования, на вход которого подается исследуемы случайный сигнал x(t). Выход блока

12дифференцирования соединен непосредственно с входом записи первого блока 9 памяти и через элемент НЕ

13- с входом записи блока 10 памяти Выходы первого регистра 3 поразрядно соединены с информационными вхоO

5 0 5 0

дами блока 9 памяти. Блок 4 синхронизации (фиг.2-) состоит из элемента 14 четности-нечетности, к которому подключены выходы пороговых блоков 1. Выходы элемента 14, один непосредственно, а другой через элемент 15 интегрирования (задержки), соединены с Bxoflai fii элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16, выход которого является выходом блока 4 синхронизации.

Анализатор работает следующим образом.

В начале анализа (исходное состояние анализатора) бчетчик 6 импульсов устанавливается в нулевое состояние, а во все разряды регистра 7 и во все ячейки блоков 9 и 10 памяти записываются нули. Цепи установки исходного состояния узлов 6, 7, 9 и 10 на фиг.1 не показаны. Исходное состояние других узлов и блоков анализатора для его работы значения не

имеет.. .

Напряжение x(t) реализации случайного процесса поступает на первые входа пороговых блоков 1, в которых оно сравнивается с напряжением уровней анализа U- (, 2,..., п причем . . Поскольку в качестве пороговых блоков 1 используются обычные компараторы напряжений, то на выходе i-ro блока напряжение принимает уровень логического нуля

при x(t) Uj и уровень логической 5 единицы - при x(t ), Полученные на выходе блоков 1 логические сигналы в форме натурного кода поступают по п каналам на входы шифратора 2. В приоритетном шифраторе 2 совокупность входных сигналов преобра-

зуется в двоичный код, соответствующий номеру i-ro максимального уровня анализа Uj, выше которого в данный момент находится напряжение

сигнала x(t). Код с выхода шифратора 2 поразрядно (каждый разряд выхода шифратора 2 соединен с входом соответствующего разряда регистра 3) поступает на вход регистра 3. Этот

код записывается в регистр 3 в момент прихода переднего фронта импульса с выхода блока 4 синхронизации, который вьщает на выходе импульсы записи в момент каждого пересечения сигналом x(t) каждого уровня анализа как снизу вверх, так и сверху вниз. Записанный в регистре 3 код сохраняется в нем и передается на выход до момента прихода еле

дующего импульса записи с выхода блока 4, Код с выхода регистра 3 определяет адрес в блоке 9 памяти, соответствующий уровню анализа U;, и по этому адресу в него импульсом с выхода блока 4 записывается содержимое регистра 7. Информация записывается в него передним фронтом импульса . с выхода блока 4 синхронизации с выходов счетчика 6 импульсо который постоянно считывает импульсы генератора 5.

Адрес записываемой в устройстве 9 памяти информации соответствует номеру уровня анализа Uj. Записанная в блок 9 памяти информация соответствует коду момента времени С;, когда сигнал x(t) пересекает уровень анализа U; снизу вверх.

При пересечении напряжением сигнала x(t) снизу вверх другого уровня анализа U,, блоки 1, шифратор 2, регистры 3, 7 и блок 4 синхронизации работают аналогичным образом и в регистре 3 записывается код, соответствующий номеру (i+1)-r уровня анализа. По адресу, опреде- тяемому этим кодом, в блок 9 памяти записывается содержимое регистра 7, соответствующее коду момента време

ни t

1-И

когда сигнал x(t) пересекает уровень анализа U,-, снизу вверх.

Таким образом, с каждым пересечеТаким образом, в блоке 10 пам накапливается информация о расп делении вероятностей длительност выбросов на разных уровнях анали Дискретные значения плотности ра

нием сигналом x(t) любого уровня ана-35 пределения вероятностей выбросов

40

лиза в блоке 9 записывается по новому адресу, соответствующему номеру уровня анализа i, новое состояние счетчика 6.

В случае, когда напряжение сигнала x(t) начинает убывать и пересекает уровень анализа U-, сверху вниз, .блок 1, ши фратор 2, регистры 3 и 7 и блок 4 синхронизации работают ана- 45 логичным образом. При этом в регистр 7 вновь переписываются состояния выходов счетчика 6. Одновременно по адресу, соответствующему номеру (i+1)-ro уровня анализа из регистра 3, из блока 9 считывается записанная раньше (при пересечении сигна - лом x(t) уровня и,-, снизу вверх) информация, соответствующая моменту времени t;, пересечения сигналом x(t) уровня и, снизу вверх. Эта информация поразрядно подается на.

длительноностью Кл Г(гдел ь - пер ;од повторения импульсов генератор на уровне анализа U могут быть о ределены по формуле

w(k.i:, Uj) -. - tu c

. N;

.где - содержимое ячейки блок

50

10, адрес которой определяется ко дом, соответствующим числу k, при ходящим с выхода вычитателя 8, и дом, соответствующим номеру i-ro уровня анализа, приходящим из регистра 3;

NJ - количество выбросов сигна x(t) на i-M уровне анализа. Цепи, обеспечивающие остановку процесса .измерения после обработки заданно 55 количества выборок N; на каждом у не анализа, на функциональной схе (фиг.1) не показаны.

первые входы вычитателя 8, соответствующая моменту времени пере5

О

0

5

0

сечения уровня сверху вниз. Fla выходе вычитателя 8 появляется код, соответствующий длительности выброса

+ ( - Jvi

Этот код с его выхода подается на младшие адресные входы блока 10 памяти, на старшие адресные входы которого подается информация с ре гист- ра 3, соответствующая номеру i-ro уровня анализа. По адресу, определяемому упомянутыми кодами, считывается содержимое блока 10 памяти и с его выхода информация поступает на вход сумматора 11. В последнем к этой информации добавляется единица и с его выхода поступает на информационные входы второго блока 10. Пришедшая новая информация записывается в блок 10 по тому же адресу.

При пересечении напряжением сигнала x(t) уровня анализа Uf сверху вниз все узлы анализатора работают аналогично, и единица добавляется к содержимому блока 10 памяти по адресу, код старших разрядов которого соответствует номеру i-ro уровня анализа, а код младших разрядов - длительности б,- выброса на i-м уровне анализа.

Таким образом, в блоке 10 памяти накапливается информация о распределении вероятностей длительностей выбросов на разных уровнях анализа. Дискретные значения плотности рас5 пределения вероятностей выбросов

длительноностью Кл Г(гдел ь - пери- ;од повторения импульсов генератора 5) на уровне анализа U могут быть определены по формуле

40

w(k.i:, Uj) -. - tu c

. N;

.где - содержимое ячейки блока

10, адрес которой определяется кодом, соответствующим числу k, приходящим с выхода вычитателя 8, и кодом, соответствующим номеру i-ro уровня анализа, приходящим из регистра 3;

NJ - количество выбросов сигнала x(t) на i-M уровне анализа. Цепи, обеспечивающие остановку процесса измерения после обработки заданного количества выборок N; на каждом уровне анализа, на функциональной схеме (фиг.1) не показаны.

Записью - считыванием информации блоков 9, 10 памяти управляют блок i

синхронизации и блок 12 дифференцирования. При возрастании входного сигнала x(t) на выходе блока 12 появляется уровень логического нуля, который г1одается на вход записи блока 9 и через элемент НЕ 13 - на вход записи блока 10 памяти. Таким обра- зон, при возрастании сигнала x(t) разрешается запись информации в блок 9 импульсом с выхода блока 4, а информация в блоке 10 памяти не переписывается. При убывании входного сигнала x(t) на выходе блока 12 дифференцирования появляется уровень логической единицы, который не разрешает запись информации в б.лок 9 а, пройдя через элемент НЕ 13, этот уровень логической единицы разрешает запись информации импульсом с выхода блока 4 в блок 10 памяти. Блок 4 синхронизации выдает на выходе импульсы при каждом пересечении процессом x(t) любого уровня Uj как снизу вверх, так и сверху вниз. Это обеспечивается при помощи элемента 14 четности и нечетности (контроля) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 элемента 15 инвертирования резистора R и конденсатора С.

Таким образом, использование изобретения обеспечивает возможность многоканального анализа длительностей выбросов случайного процесса одновременно по нескольким уровням анализа, за счет фиксации моментов времени пересечения исследуемым процессом x(t) уровней анализа и,и,...,и. Информация о этих моментах времени запоминается в блоке памяти. После логической обработки этой информации в другом блоке памя- ти накапливается информация о распре целении длительностей выбросов по уровням анализа. Эта информация позволяет, в частности, построить гистограммы распределения длительностей выбросов по уровням анализа.

Формула изобретения

Анализатор длительностей выбросов случайных процессов, содержащий

903556

блок синхронизации, генератор импульсов, первый и второй регистры и п пороговых блоков, входы которых объединены и являются информационным 5 входом анализатора, отличающийся тем, что, с целью повышения быстродействия, он содержит счетчик импульсов, шифратор, блок дифференцирования, первый и второй - блоки памяти, элемент НЕ, вычитатель и сумматор, первый вход которого является )зходом логической единицы анализатора, а второй вход соединен с выходом первого блока памяти.

15

группа адресных входов младших разрядов которого соединена с группой разрядных выходов вычитателя, первая группа разрядных входов которого соединена с группой выходов второго блока памяти, информационный вход которого соединен с выходом .сумматора, группа адресных входов ||первого блока памяти объединена с группой адресных входов старших разрядов первого блока памяти и подключена к разрядным выходам первого регистра, группа разрядных входов которого соединена с разрядными вы- 1ходами шифратора, разрядные входы

которого объединены с группой входов блока синхронизации и подключены к выходам п пороговых блоков соответственно, выход блока синхронизации подключен к входам записи первого и второго регистров, первого и второго блоков памяти, разрядные выходы второго регистра подключены к группе информационных входов второго блока памяти и группе вторых

разрядных входов вычитателя, группа разрядных входов второго регистра соединена соответственно с группой разрядных выходов счетчика импульсов, счетньш вход которого соединен с выходом генератора импульсов, при

этом вход блока дифференцирования объединен с информационным входом анализатора, а выход блока дифференцирования подключен к входу разреше- 50 ния считывания второго блока памяти непосредственно, а через элемент НЕ - к входу разрешения записи пер- iBoro блока памяти.

Редактор М.Келемеш

Составитель Э.Сечина Техред: М.Ходаиич

Заказ 7905/49Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, Е.Ужгород, ул. Щ оектная, 4

Корректор М. Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор длительностей выбросов случайных процессов | 1984 |

|

SU1168969A1 |

| Статистический анализатор выбросов и провалов напряжения | 1980 |

|

SU947775A1 |

| Цифровой фильтр | 1986 |

|

SU1387016A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для приема информации | 1987 |

|

SU1509969A1 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| МНОГОУРОВНЕВЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛИТЕЛЬНОСТИ ВЫБРОСОВ И ПРОВАЛОВ НАПРЯЖЕНИЯ | 1991 |

|

RU2054195C1 |

| Анализатор длительностей выбросов случайных процессов | 1981 |

|

SU1001111A1 |

| Статистический анализатор величины и длительности колебаний напряжения | 1979 |

|

SU920741A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

Изобретение относится к облас- ти вычислительной техники и может быть использовано в статических анализаторах случайных процессов. Цель изобретения - повьшение быстродействия. Анализатор длительностей выбросов случайных процессов содержит п пороговых блоков 1, на входы которых подаются исследуемый сигнал и напряжения уровней анализа, блок 4 синхронизации, регистры 3 и 7 и генератор 5 импульсов. Новым является введение в схему анализатора шифратора 2, блоков 9, 10 памяти, сумматора 11, вычитателя 8, счетчика 6 импульсов, элемента НЕ 13 и блока 12 дифференцирования. Связи введенных узлов с остальными узлами схемы позволяют существенно увеличить быстродействие и информативность одного измерения за счёт проведения анализа одновременно на нескольких уровнях за счет фиксации моментов времени пересечения исследуемым процессом уровней анализа. Информация о этих моментах времени запоминается в блоке памяти и после логической обработки в другом блоке памяти накапливается информация о распределении длительностей выбросов по уровням анализа. 2 ил. (Л сд гя

| МНОГОКАНАЛЬНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР РАСПРЕДЕЛЕНИЯ ДЛИТЕЛЬНОСТЕЙ ИЛ\ПУЛЬСНЫХ | 0 |

|

SU397916A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| 1973 |

|

SU436359A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,(54) АНАЛИЗАТОР ДЛИТЕЛЬНОСТЕЙ ВЫБРО- | |||

| СОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | |||

Авторы

Даты

1987-02-15—Публикация

1984-12-10—Подача