оо

00

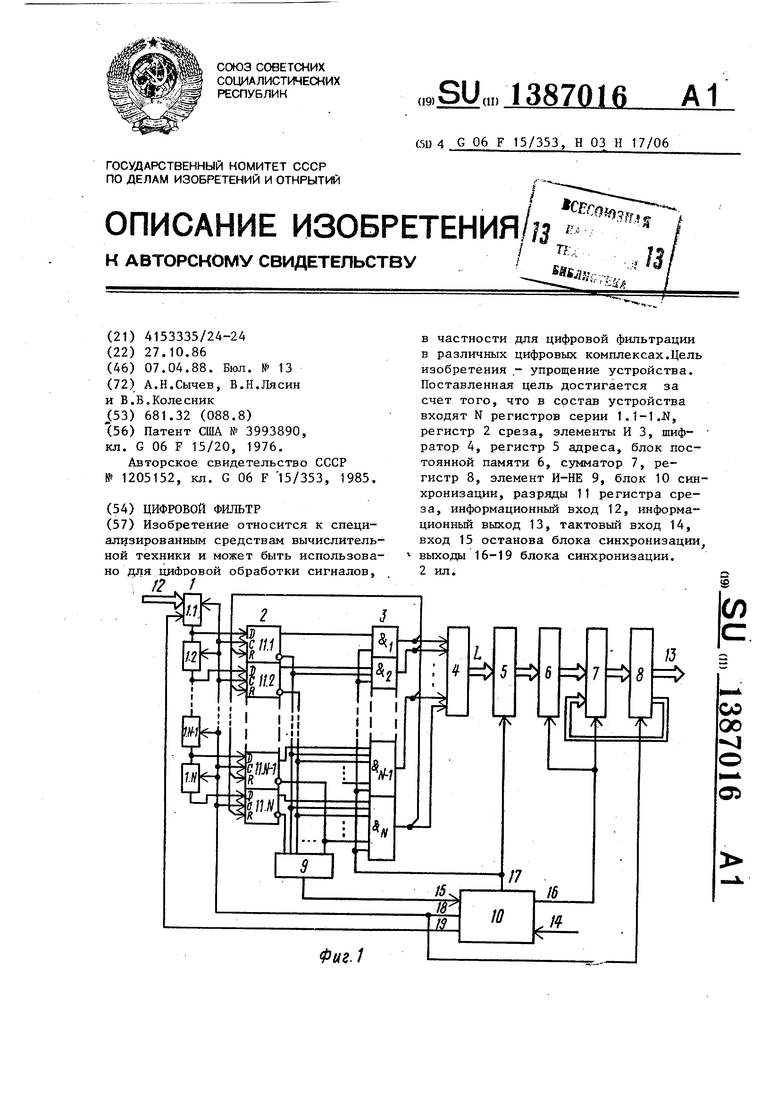

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для цифровой обработка сигналов, в частности для цифровой фильтрации в различных цифровых комплексах.

Цель изобретения - упрощение фильтра.

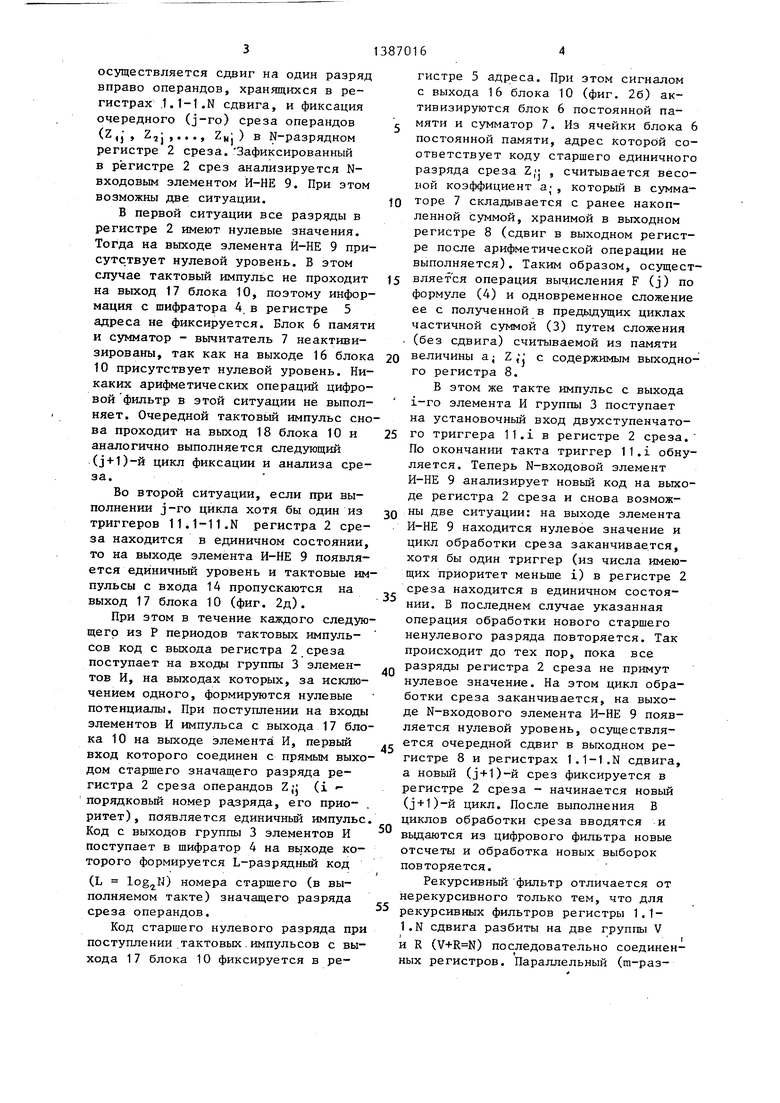

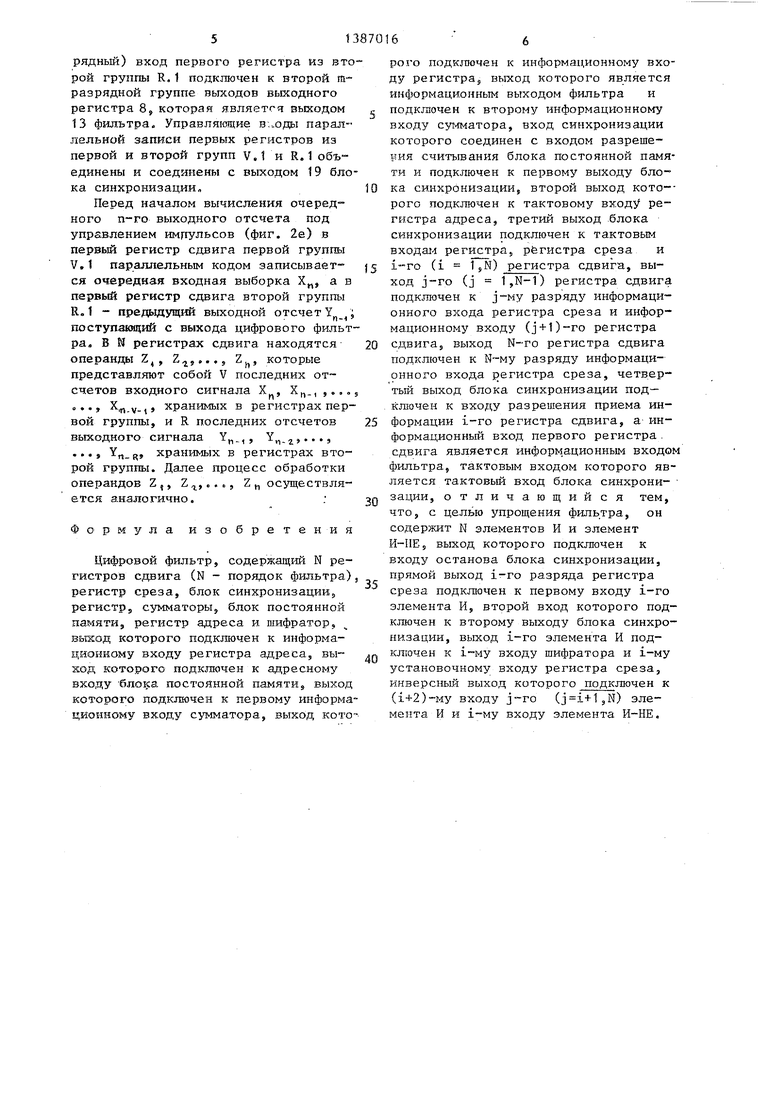

На фиг. 1 приведена функциональ- ная схема цифрового фильтра; на фиг.2 временные диаграммы работы цифрового фильтра.

Цифровой фи.пьтр (фиг. 1) содержит N регистров сдвига 1.1 -. liN, регистр 2 среза, элементы И 3, шифратор 4, регистр 5 адреса, блок 6 постоянной памяти, сумматоры 7, регистр 8 (выходной), элемент И-НЕ 9, блок 10 синхронизации, разряды 11 {)егистра 2 среза, информационные вход 12 и выход 13 цифрового фильтра, тактовый вход 14 фильтра, вход 15 останова блока синхронизации, первый 16, второй 17, третий 18 и четвертый 19, выходы блока синхронизации.

Работа цифрового фильтра опись вается алгоритмом н

Y(n) aj Z.,

-(1)

Y(n) - выходная выборка фильтра

в п-й момент времени; N - число выводов из сдвиговых регистров или число операндов, участвующих в ,с формировании передаточной функции;

а- - коэффициенты, обеспечиваю-, щие требуемую импульсную характеристику или пере- Q даточную функцию фильтра , Z; - представленные в двоичном цифровом коде выборки входного. сигнала X,.; (для нерекурсивного фильт- де ра ,2,...,N, для рекурсивного ,2,...,V) и задержанные выходные ; сигналы (,2,..., ...,R) для рекурсивного

фильтра, .

При представлении выборок входносигнала, а для рекурсивного фильти задержанных выборок выходного нала, В-разрядным (включая знакоразряд) числом в дополнительном е с фиксированной запятой

-J

50

B-t

-Zfo-b Zii-2

(2)

где Zv - двоичные переменные, j

О - (В-1)

Zjo - значение знакового разряда, после перестановки слагаемых в (1) получают алгоритм цифровой фильтра4J /

(3)

) F(j)

0

5 0 5

0

с

Q е

0

()

Цифровой фильтр работает, следующим образом.

Перед началом вычисления очерёдного п-го выходного отсчета в пер- вый регистр 1.1 сдвига под управлением импульсов записи (фиг.2е) вводится очередная выборка входного сигнала Xj,. Импульс записи новых .рандов (фиг. 2е) формируется на выходе 19 блока 10 синхронизации с помощью тактового импульса на входе 14 в том , если прошло В циклов. Импульс с выхода 19 блока 10 синхронизации подается на управлякндие входы параллельной записи первого регистра 1.1 сдвига. Теперь в N регистрах 1.1-1.N сдвига находятся операнды Z,, Zj,..., Z, которые-для рассматриваемого нерекурсивного цифрового фильтра представляют собой N последних отсчетов входного сигнала

V VV

п п-« - ч-N-t

Период вычисления одного выходного отсчета Y(n) по алгоритмам (3) и (4) в предлагаемом цифровом фильтре состоит из В циклов, границы которых показаны пунктирными вертикальньмй линиями .(фиг. 2е).

Окончание очередного цикла происходит тогда, когда на всех входах элемента И-НЕ 9 появляется единичный

потенциал, следовательно, на выходе элемента И-НЕ 9 нулевой потенциал. В эуом случае тактовые импульсы (фиг. 2а) с входа 14 проходят на выход 18 блока 10 (фиг. 2в). По переднему фронту этих импульсов- в каждом очередном j-M (j О-(В-1)) цикле осуществляется сдвиг вправо на один разряд содержимого выходного регистра 8. Таким образом, в соответ- ствии с формулой (3) выполняется умножение на 2 суммы, накопленной в результате обработки предыдущих (с номерами меньше j) разрядов операндов. Этими же импульсами (фиг. 2с)

осуществляется сдвиг на один разряд вправо операндов, хранящихся в регистрах .1 . 1-1 .N сдвига, и фиксация очередного (j-ro) среза операндов (Z,j, Z,j,..., ZNJ ) в N-разрядном регистре 2 среза. Зафиксированный в регистре 2 срез анализируется N- входовым элементом И-НЕ 9. При этом возможны две ситуации.

В первой ситуации все разряды в регистре 2 имеют нулевые значения. Тогда на выходе элемента Й-НЕ 9 присутствует нулевой уровень. В этом случае тактовый импульс не проходит на выход 17 блока 10, поэтому информация с шифратора 4 в регистре 5 адреса не фиксируется. Блок 6 памяти и сумматор - вычитатель 7 неактивизированы, так как на выходе 16 блока 10 присутствует нулевой уровень. Никаких арифметических операций цифровой фильтр в этой ситуации не выполняет. Очередной тактовый импульс снова проходит на выход 18 блока 10 и аналогично выполняется следующий (з+1)-й цикл фиксации и анализа среза.

Во второй ситуации, если при выполнении j-ro цикла хотя бы один из триггеров 11.1-11.N регистра 2 среза находится в единичном состоянии, то на выходе элемента И-НЕ 9 появляется единичный уровень и тактовые импульсы с входа 14 пропускаются на выход 17 блока 10 (фиг. 2д).

При этом в течение каждого следующего из Р периодов тактовых импульсов код с выхода регистра 2 среза поступает на входы группы 3 элементов И, на выходах которых, за исключением одного, формируются нулевые потенциалы. При поступлении на входы элементов И импульса с выхода 17 блока 10 на выходе элемента И, первый вход которого соединен с прямым выходом старшего значащего разряда регистра 2 среза операндов Z;j (i - порядковый номер разряда, его прио- ритет), появляется единичньш импульс Код с выходов группы 3 элементов И Поступает в шифратор 4 на выходе которого формируется L-разрядный код

(L log,N) номера старшего (в выполняемом такте) значащего разряда среза операндов.

Код старшего нулевого разряда при поступлении .тактовых.импульсов с выхода 17 блока 10 фиксируется в регистре 5 адреса. При этом сигналом с выхода 16 блока 10 (фиг. 26) активизируются блок 6 постоянной памяти и сумматор 7. Из ячейки блока 6 постоянной памяти, адрес которой соответствует коду старшего единичного

0

5

5

0

5

0

5

0

5

считывается весо0

разряда среза Z; вой коэффициент а;, который в сумматоре 7 складывается с ранее накопленной суммой, хранимой в выходном регистре 8 (сдвиг в выходном регистре после арифметической операции не выполняется). Таким образом, осуществляется операция вычисления F (j) по формуле (4) и одновременное сложение ее с полученной в предьщущих циклах частичной СУ1Ф10Й (3) путем сложения (без сдвига) считываемой из памяти величины а J Z , j с содержимым выходного регистра 8.

В этом же такте импульс с выхода i-ro элемента И группы 3 поступает на установочный вход двухступенчатого триггера 11.1 в регистре 2 среза. По окончании такта триггер 11.1 обнуляется. Теперь N-ВХОДОВОЙ элемент И-НЕ 9 анализирует новый код на выходе регистра 2 среза и снова возможны две ситуации: на выходе элемента И-НЕ 9 находится нулевое значение и цикл обработки среза заканчивается, хотя бы один триггер (из числа имеющих приоритет меньше 1) в регистре 2 среза находится в единичном состоянии. В последнем случае указанная операция обработки нового старшего ненулевого разряда повторяется. Так происходит до тех пор, пока все разряды регистра 2 среза не примут нулевое значение. На этом цикл обработки среза заканчивается, на выходе N-ВХОДОВОГО элемента И-НЕ 9 появляется нулевой уровень, осуществляется очередной сдвиг в выходном регистре 8 и регистрах 1.1-1.N сдвига, а новый (+1)-й срез фиксируется в регистре 2 среза - начинается новый (з+1)-й цикл. После выполнения В циклов обработки среза вводятся и выдаются из цифрового фильтра новые отсчеты и обработка новых выборок повторяется.

Рекурсивньй фильтр отличается от нерекурсивного только тем, что для рекурсивных фильтров регистры 1.11.N сдвига разбиты на две группы V 1 I

и R () последовательно соединен

ных регистров. Параллельный (т-раз51

рядный) вход первого регистра из втрой группы R.1 подключен к второй Ш разрядной группе выходов выходного регистра 8, которая является выходом 13 фильтра. Управляющие в-.оды параллельной записи первых регистров из первой и второй групп V.t и R. 1 объединены и соединены с выходом 19 блока синхронизации

Перед началом вычисления очеред кого п-го выходного отсчета под управлением имдульсов (фиг, 2е) в первый регистр сдвига первой группы V,1 параллельным кодом записывается очередная входная выборка Х„, а в

первый регистр сдвига второй группы R. 1 - предыдущий выходной отсчет поступающий с выхода цифрового фильтра. В М регистрах сдвига находятся операнды Z,, Z,..., Ъ, которые представляют собой V последних отсчетов входного сигнала Х„, X

,, Х,„,у.,, хранимых в

регистрах первой группы, и R последних отсчетов выходного сигнала У„., Y, „

п-1

..., хранимых в регистрах второй группы. Далее процесс обработки операндов Z,, Z ,., ется аналогично.

Z f, осуществляФормула изобретения

Цифровой фильтр, содержащий N регистров сдвига (N - порядок фильтра), регистр среза, блок синхронизации, регистр, сумматоры, блок постоянной памяти, регистр адреса и шифратор, выход которого подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока постоянной памяти, выход которого подключен к первому информационному входу сумматора, выход кото

6

рого подключен к информационному входу регистра выход которого является информационным выходом фильтра и подключен к второму информационному входу сумматора, вход синхронизации которого соединен с входом разрешения считывания блока постоянной памяти и подключен к первому выходу блока синхронизации, второй выход кото-- рого подключен к тактовому входу регистра адреса, третий выход блока синхронизации родключен к тактовым входа - регистра, регистра среза и

(i 1jN) регистра сдвига, выход j-ro (j 1,N-1) регистра сдвига подключен к j-му разряду информационного входа регистра среза и информационному входу (j+1)-ro регистра

сдвига, выход N-ro регистра сдвига подключен к N-му разряду информационного входа 1)егистра среза, четвертый выход блока синхронизации подключен к входу разрешения приема информации i-ro регистра сдвига, а- информационный вход первого регистра . сдвига является информационным входом фильтра, тактовым входом которого является тактовый вход блока синхрони- зации, отличающийся тем.

что, с целью упрощения фильтра, он содержит N элементов И и элемент И-ИБ, выход которого подключен к входу останова блока синхронизации, прямой выход i-ro разряда регистра среза подключен к первому входу i-ro элемента И, второй вход которого подключен к второму выходу блока синхронизации, выход i-ro элемента И подключен к входу шифратора и i-му установочному входу регистра среза, инверсный выход которого подключен к (i+2)-My входу (j i+l5N) элемента И и i-му входу элемента И-НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1984 |

|

SU1205152A1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1483606A2 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для ЦИФРОВОЙ обработки сигналов, ; /г / в частности для цифровой фильтрации в различных цифровых комплексах.Цель изобретения .- упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят N регистров серии 1.1-1.J, регистр 2 среза, элементы ИЗ, шиф- ратор 4, регистр 5 адреса, блок постоянной памяти 6, сумматор 7, регистр В, элемент И-НЕ 9, блок 10 синхронизации, разряды 11 регистра среза, информационный вход 12, информационный выход 13, тактовый вход 14, вход 15 останова блока синхронизации, выходы 16-19 блока синхронизации. 2 ил. i (Л

| Патент США № 3993890, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой фильтр | 1984 |

|

SU1205152A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-27—Подача