«

ел

Изобретение относится к вычислительной технике и может быть исполь- ,зовано при вьмислении широкого класса функций одного аргумента в высокоскоростных вычислительных системах, .обрабатывающих большие массивы данных .

Цель изобретения - расширение области применения за счет вьмисления широкого класса функций и возможности испсхльзовать операнды, представленные в дополнительном коде.

В устройстве реализуется набор сплайнов N-ro порядка, обеспечиваю- щих высокую точность вычисления функции

Рк(Х)б(х-х.;-6(х-Х.,,, ) .,-Za,j,-x ,

(1)

1 ,если X :}, xi

(2)

О,если X С X

Ik

k 1,2,..., К номер интерполируемой функции;К - число интерпо-

лируейых функций М -- число интервалов интерполяции k-й функции.

Для сведения к минимуму аппаратур- ных затрат и упрощения структурной схемы арифметического блока вьфаже- ние (1) преобразуется с использованием скобок Горнера:

гл«

F(x) (x-Xj)-6(x-Xj + ,K )

Haoix + Х-а

31 +Х(а

liK- zjK

+XUf.,)JK iK).-)Njfc

(3)

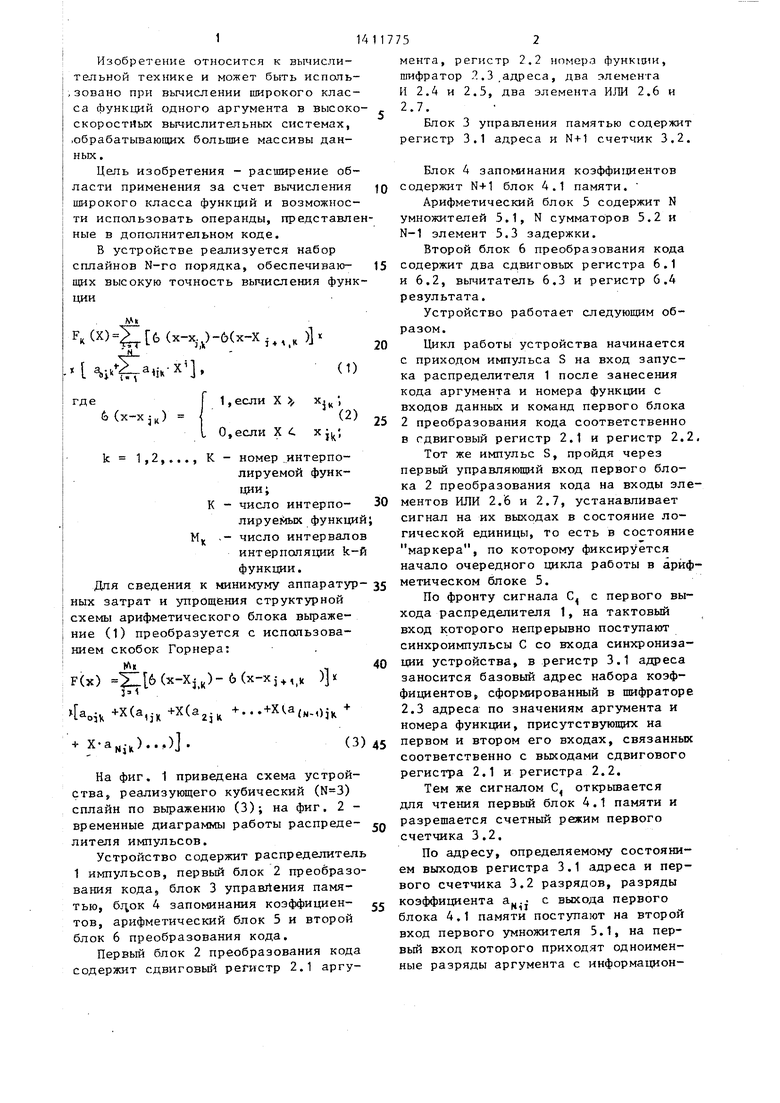

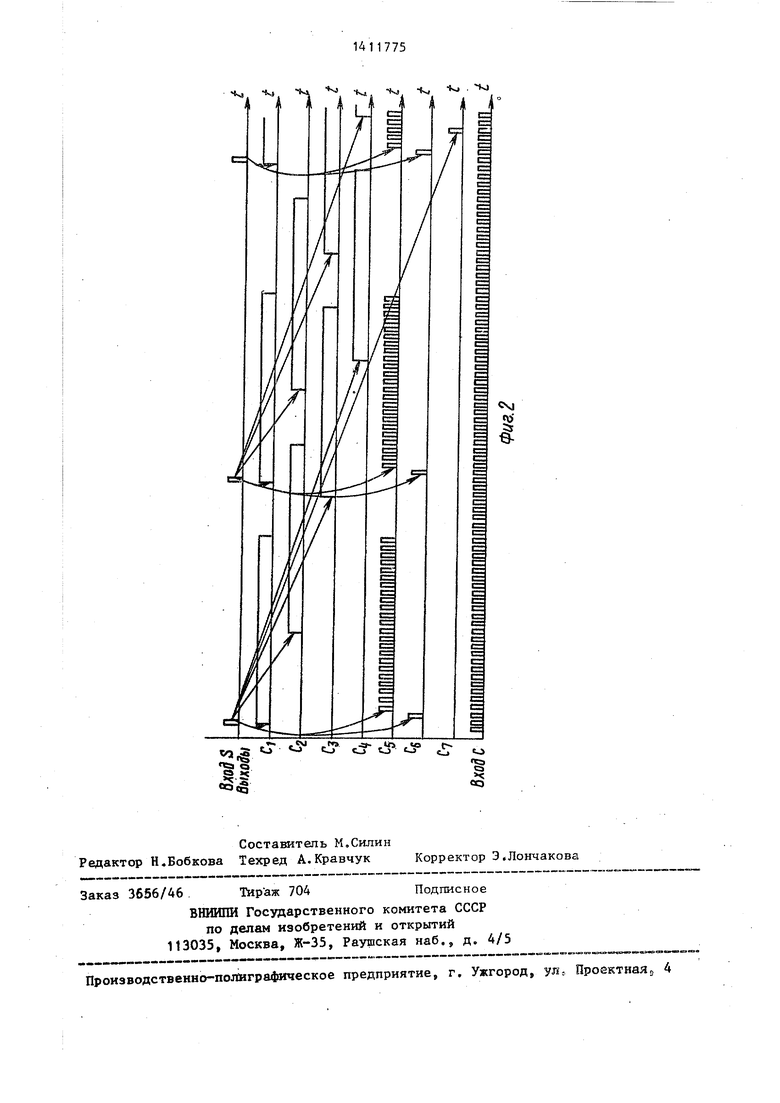

Ha фиг. 1 приведена схема устройства, реализующего кубический () сплайн по выражению (3); на фиг. 2 - временные диаграммы работы распределителя импульсов.

Устройство содержит распределитель 1 импульсов, первый блок 2 преобразования кода, блок 3 управления памятью, 6j;oK 4 запоминания коэффициентов, арифметический блок 5 и второй блок 6 преобразования кода.

Первый блок 2 преобразования кода содержит сдвиговьй регистр 2.1 аргумента, регистр 2.2 номера функции, шифратор 2.3 адреса, два элемента И 2.4 и 2.5, два элемента ИЛИ 2.6 ( 2.7.

Блок 3 управления регистр 3.1 адреса и

памятью содержит N+1 счетчик 3.2.

15

10

20

5

0

5

0

5

0

5

Блок 4 запоминания коэффициентов содержит N+1 блок 4.1 памяти.

Арифметический блок 5 содержит N умножителей 5.1, N сумматоров 5.2 и N-1 элемент 5.3 задержки.

Второй блок 6 преобразования кода содержит два сд,внговых регистра 6.1 и 6.2, вычитатель 6.3 и регистр 6.4 результата.

Устройство работает следуюЕсим образом.

Цикл работы устройства начинается с приходом импульса S на вход запуска распределителя 1 после занесения кода аргумента и номера функции с входов данных и команд первого блока 2 преобразования кода соответственно в сдвиговый регистр 2.1 и регистр 2.2,

Тот же импульс S, пройдя через первый управляющий вход первого блока 2 преобразования кода на входы элементов ИЛИ 2.6 и 2.7, устанавливает сигнал на их выходах в состояние логической единицы. То есть в состояние маркера, по которому фиксируется начало очередного цикла работы в арифметическом блоке 5.

По фронту сигнала С с первого выхода распределителя 1, на тактовый вход которого непрерывно поступают синхроимпульсы С со входа синхронизации устройства, в регистр 3.1 адреса заносится базовый адрес набора коэффициентов, сформированный в щифраторе 2.3 адреса по значениям аргумента и номера функции, присутствующих на первом и втором его входах, связанных соответственно с выходами сдвигового регистра 2.1 и регистра 2.2.

Тем же сигналом С, открывается для чтения первый блок 4.1 памяти и разрешается счетный режим первого счетчика 3.2.

По адресу, определяемому состоянием выходов регистра 3.1 адреса и первого счетчика 3.2 разрядов, разряды

коэффициента а...- с выхода первого

11„

блока 4.1 памяти поступают на второй

вход первого умножителя 5.1, на первый вход которого приходят одноименные разряды аргумента с информадаон314

ного выхода первого блока 2 преобразования кода, в котором знаковый разряд дополнительного кода аргумента по сигналу (N+3)-ro выхода распределителя 1 и myльcoв подается через элемент И 2.5 и элемент ИЛИ 2.7 на шину отрицательньк цифр аргумента, а остальные разряды через элемент И 2.4 и элемент ИЛИ 2.6 подаются на шину положительных цифр аргумента. При этом разряды аргумента последовательно считьшаются с выхода старшего разряда сдвигового регистра 2.1, сдвиг информации в котором производится под действием импульсов С , посту- на его тактовый вход с (N+2)- го выхода распределителя 1 импульсов.

Через К тактов работы устройства на втором выходе распределителя 1 импульсов появляется сигнал С., по которому разрешается счетньй режим второго счетчика 3.2 и открывается второй блок 4.1 памяти, откуда начинается считывание разрядов коэффициента ,).у на второй вход первого сумматора 5.2, на первьй вход которого поступают одноименные разряды произведения а| X, задержанные на К тактов в первом умножителе 5.1.

Еще через Kj тактов разряды резуль тата сложения а.,.. + а.. X приходят на первый, вход второго умножителя 5.1, на второй вход которого поступают соответствующие разряды аргумента, задержанные первым элементом 5.3 задержки.

Следующие каскады арифметического блока 5, блока 4 и блока 3 управления памятью работают аналогично.

Результаты вычислений поступают на вход второго блока 6 преобразования кода, причем положительные и отрицательные разряды результата заносятся в сдвиговые регистры 6.1 и 6.2 соответственно.

Разность положительной и отрицательной 1-разрядных частей результата, сформированная в вычитателе 6.3 в дополнительном двоичном коде, заносится по стробу , с (N+4)-ro выхода распределителя 1 импульсов в регистр 6.4 результата и может быть считана с его выхода в течение сле- дуюших 1 тактов работы устройства в параллельном либо последовательном коде.

11775

Периодичность вычисления значеши функ1ши в режиме конвейерной обработки данных определяется временем счи- - тывания т-разрядного аргумента из сдвигового регистра данных первого блока 2 преобразования кода, которое составляет Т .т, где Т. - период

следования синхроимпульсов С.

10

Формула изобретения

1 . Устройство для вьгчислеш1я функций, содержащее блок запом 1нания коэффициентов, блок управления памятью и арифметический блок, состоящий из N умножителей и N сумматоров, причем первый вход первого умножителя является входом аргумента арифметического

блока, вход первого коэффициента арифметического блока подключен к первому выходу блока запоминания коэффициентов и является вторым входом первого умножителя, первый вход (К+1)-го

умножителя (К 1,...,N-1) подключен к выходу К-го сумматора, выхода а-го умножителя подключен к первому входу а-го сумматора (а 1,...N), второй вход которого подключен к входу (а+1)го коэффициента арифметического блока и к (а+1)-му выходу блока запоминания коэффициентов, а выход N-ro сумматора является выходом арифметического блока, отличающеес я тем, что, с целью ра.сширения области применения за счет вычисления широкого класса функций и возможности использования операндов, представленных в дополнительном коде, в него введены распределитель импульсов, первый и второй блоки преобразования кода, причем входы кода аргумента и кода номера функции устройства подключены к соответствующим входам первого блока преобразования кода, выходы адреса набора коэффициентов и кода аргу-г мента которого подключены соответственно к адресному входу блока управления памятью и к входу аргумента арифметического блока, выход которого подключен к информационному входу второго блока преобразования кода, выход которого является выходом устройства, вход запуска которого подключен к первому управляющему входу первого блока преобразования кола и к входу запуска распределителя импульсов, выходы с первого по (Ы+1)-й которого подключены к соответствую11р1м

.

514

управляющим входам блока управления памятью и блока запом1 нания коэффициентов, N+2 адресных входа которого подключены к соответствующим выходам блока управления памятью, тактовый вход которого является входом синхронизации устройства и подключен к входам синхронизации второго блока преобразования кода и распределителя импульсов, (Ы+2)-й и (М+3)-й выходы которого подключены соответственно к второму и третьему управляюищм входам первого блока преобразования кода, а (Ы+4)-й выход распределителя импульсов подключен к управляющему входу второго блока преобразования кода, арифметический блок дополнително содержит N-1 элемент задержки, причем вход первого элемента задержки подключен к входу аргумента арифметического блока, вход каждого последующего элемента задержки подключен к выходу предьщущег-о элемента задержки и к второму входу соответствующего умножителя, а выход последнего элемента задержки подключен к второму входу N-ro умножителя.

2. Устройство по п. 1, отличающееся тем, что блок управления памятью содержит регистр адреса и N+1 счетчиков, входы сброса которых подключены к соответствующим управляющим входам блока, адресный вход которого подключен к информационному входу регистра адреса, вход записи которого подключен к первому упрвляющему входу блока, выходы с первого по (Н+1)-й которого являются выходами соответствующих счетчиков, счетные входы которых объединены и подключены к входу синхронизации блока, ()-й выход которого подключен к выходу регистра адреса.

3. Устройство по п, 1, отличающееся тем, что блок запоминания коэффициентов с одержит N+1 блоков памяти, вход разрешения считывания и вход адреса разряда каждого из которых подключены к соответствующим управляющим и адресным входам блока, (К+2)-й адресный вход которого подключен к объединенным между собой входам адреса коэффициента каждого блока памяти, выходы которых

5о

являются соответс.твую1цими выхода «и блока.

4.УстроГгство по п. 1,, отличающееся тем, что первый блок преобразования кода содержит шифратор адреса, два элемента И, два элемента ИЛИ, сдвиговый регистр аргумента и регистр номера функции, выходы котоРых подключены соответственно к первому и второму входам шифратора адреса, выход которого является адрес- ньм выходом блока, первый управляющей вход которого подключен к объединенным между собой первым входам первого и второго элементов ИЛИ, выходы которых являются соответственно выходами положительных и отрицательных цифр аргумента и подключены к информационному вькоду блока, второй уп- равляюш11й вход которого подключен к тактовому входу сдвигового регистра аргумента, выход старшего разряда которого подключен к первому входу первого элемента И и прямому входу второго элемента И, инверсный вход которого подключен к второму входу первого элемента И и является третьим управляющим входом блока, входы кода

аргумента и кода номера функции блока подключены соответственно к информационным входам сдвигового регистра аргумента и регистра номера функции, а выходы первого и второго элементов И подключены к вторым входам соответствующих элементов ИЛИ.

5.Устройство по п, 1, отличающееся тем, что второй блок преобразования кода содержит два

сдвиговых регистра, вычитатель и регистр результата, вход записи которого является управляющим входом блока, вход синхронизации которого подключен к объединенным между собой тактовым входам первого и второго сдвиговых регистров, информационные входы которых являются соответственно шинами положительных и отрицательных цифр результата и подключены к информационному входу блока, выход которого является выходом регистра результата, информационный вход которого подключен к выходу вычитателя, первый и второй вхо;;ы которого подключены соответственно к выходам первого и вто

рого слвиговьгх регистроЕ;,

Фиг.1

«ц,, tsj

st:r « c ,;5-t cS

fto )

s ss

2,

-Kj.

-kj -J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для вычисления коэффициентов дискретного преобразования Фурье | 1979 |

|

SU877556A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор функций Уолша | 1984 |

|

SU1241218A2 |

| Генератор функций Уолша | 1984 |

|

SU1166134A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1277135A1 |

Изобретение относится к вычислительной технике и может быть использовано при вычислении широкого класса функций одного аргумента. Целью изобретения является расширение области применения. Устройство содержит первый блок преобразования кода, состоящий из регистра аргумента, регист; ра полин ера функции, шифратора адреса, двух элементов И и двух элементов ИЛИ, блок управления памятью, состоящий из регистра адреса и N+1-го счетчика, блок запоминания коэффициентов, состоящий КЗ N+1-го блока па- мяти, распредилитель :импульсов, арифметический блок и второй блок преобразования кода, Содержащий ,два сдвиговых регистра, вычита- тепь и регистр результата. Поставленная цель достигается за счет введения новых элементов и связей, 4 з.п.ф-лы, 2 ил. СО

| Таблично-алгоритмический функциональный преобразователь | 1979 |

|

SU860079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Каляев А.В | |||

| Многопроцессорные системы с программируемой архитектурой,- М.: Радио и связь, 1984, с | |||

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-04—Подача