Изобретение относится к радиотехнике и может найти применение в устройствах контроля и синтеза прецизионных частотно-модулированных сигналов , в том числе сигналов с линейной частотной модуляцией (ЛЧМ), широко используемых в радиолокации, системах связи и измерительной технике.

Цель изобретения- расширение функциональных возможностей за счет уменьшения времени перестройки измерителя и обеспечения его работы на начальном участке контролируемого сигнала.

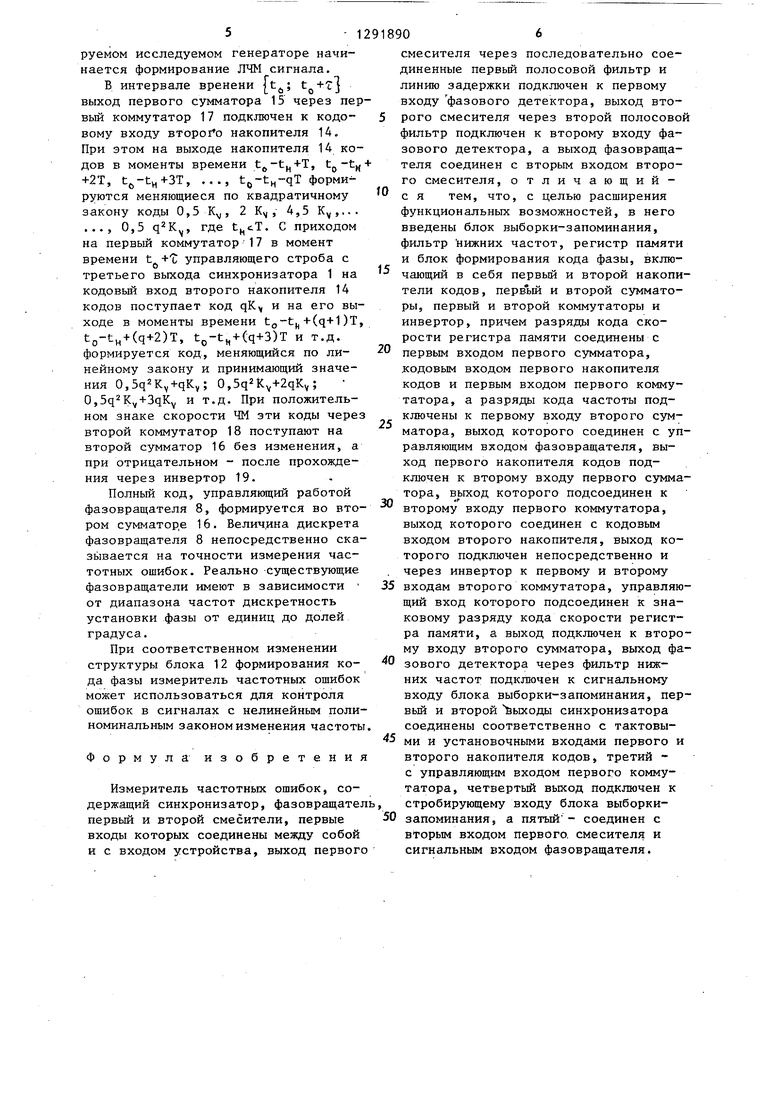

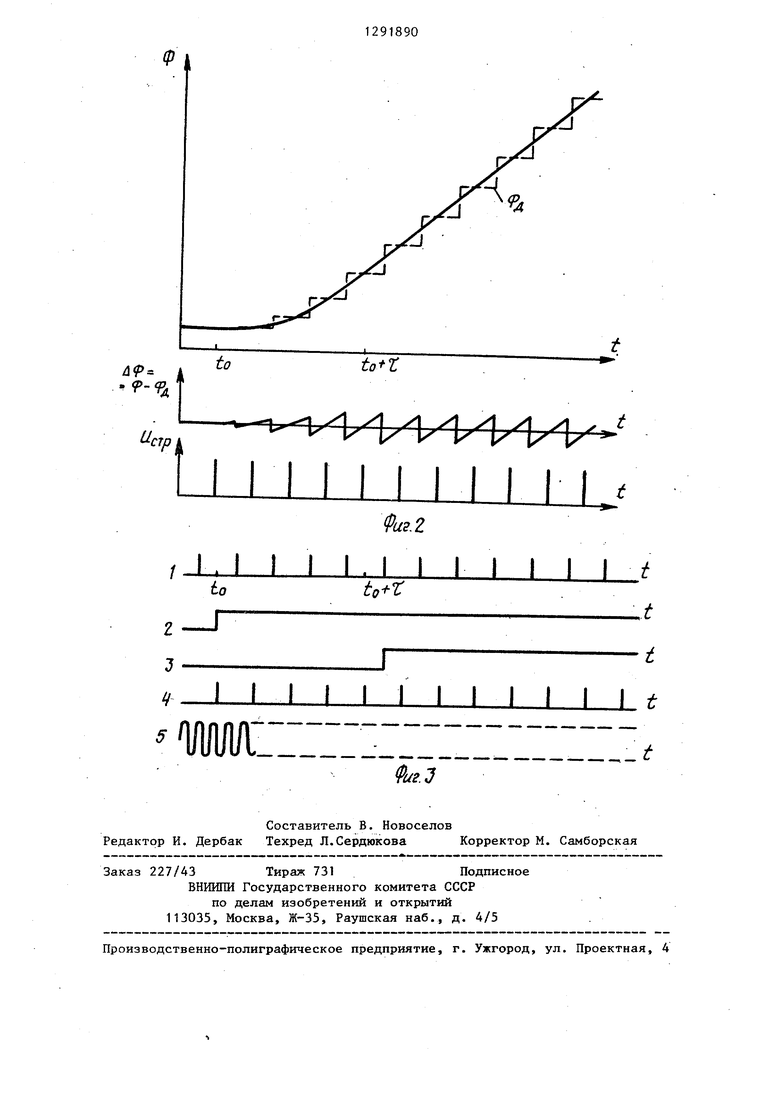

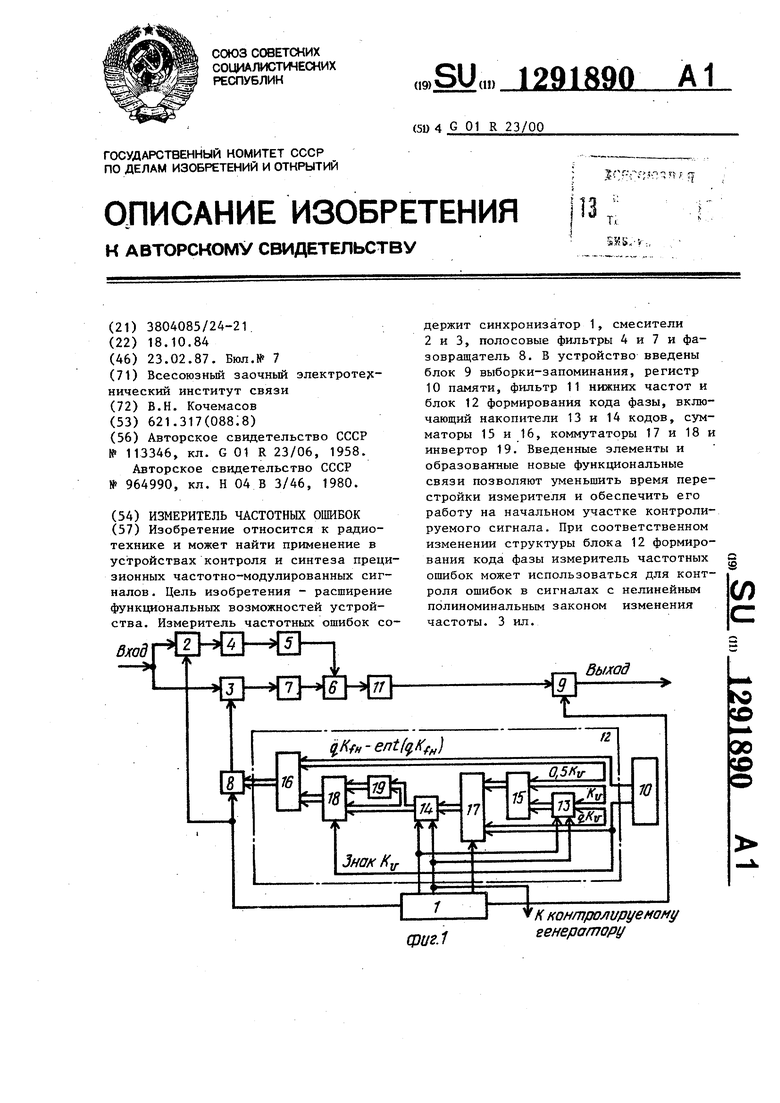

На фиг. 1 представлена функциональная схема измерителя частотных Jошибок; на фиг. 2 - эпюры, поясняющие работу устройства; на фиг. 3 - временные диаграммы сигналов на пяти выходах синхронизатора.

10

15

ду первого сумматора 15, выход которого подсоединен к второму входу первого коммутатора 17, выход которого соединен с кодовым входом второго накопителя 14, выход которого подключен непосредственно и через инвертор 19 к первому и второму входам второго коммутатора 18. Управляющий вход последнего подсоединен к знаковому разряду кода скорости регистра 10 памяти, а выход - к второму входу второго сумматора 16. Вьпсод фазр- вого детектора 6 через фильтр 11 нижних частот подключен к сигнальному входу блока 9 выборки-запоминания. Первьш и второй выходы синхронизатора 1 соединены соответственно с тактовыми и установочными входами первого 13 и второго 14 накопителей

Измеритель частотных ошибок содер- кодов, а третий - с управляющим вхожит синхронизатор 1, первый 2 и второй 3 смесители, первый полосовой фильтр 4, линию 5 задержки, фазовьй детектор 6, второй полосовой фильтр 7, фазовращатель 8, блок 9 выборки- запоминания, регистр 10 памяти, фильтр 11 нижних частот, блок 12 формирования кода фазы, в который входят первый 13 и второй 14 накопители кодов, первый 15 и второй 16 сумматоры, первьш 17 и второй 18 коммутаторы и инвертор 19.

В устройстве первые входы первого 2 и второго 3 смесителей соединены ь-гжду собой и с входом ус тройства,, выход первого смесителя 2 через последовательно соединенные первый полосовой фильтр 4 и линию 5 задержки подключен к первому входу фазового детектора 6, выход второго смесителя 3 через второй полосовой фильтр 7 подключен к второму входу фазового детектора 6, а выход фазовращателя 8 соединен с вторым входом второго смесителя 3. Разряды кода скорости регистра 10 памяти соединены с первым входом первого сумматора 15, кодовым входом первого накопителя 13 кодов и первым входом первого коммутатора 17, а разряды кода частоты подключены к первому входу второго сумматора 16, выход которого соединен с управляющим входом фазовращателя 8, Выход первого накопителя 13 кодов подключен к второму вхоU(t)

,t+Q(t) при tstp ,t+fV(t-t)2 + Xt) при

ду первого сумматора 15, выход которого подсоединен к второму входу первого коммутатора 17, выход которого соединен с кодовым входом второго накопителя 14, выход которого подключен непосредственно и через инвертор 19 к первому и второму входам второго коммутатора 18. Управляющий вход последнего подсоединен к знаковому разряду кода скорости регистра 10 памяти, а выход - к второму входу второго сумматора 16. Вьпсод фазр- вого детектора 6 через фильтр 11 нижних частот подключен к сигнальному входу блока 9 выборки-запоминания. Первьш и второй выходы синхронизатора 1 соединены соответственно с тактовыми и установочными входами первого 13 и второго 14 накопителей

дом первого коммутатора 17, четвертый выход подключен к стробируЮщему входу блока 9 выборки-запоминания, а пятый соединен с вторым входом первого смесителя 2 и сигнальным входом фазовращателя 8.

Входящий в состав измерителя частотных ошибок регистр 10 памяти при измерении ошибок в ЛЧМ сигналах содержит информацию о коде начальной частоты Kf и коде скорости Ку частотной модуляции. В соответствии с этими кодами в блоке 12 формирова- ния кода фазы вырабатьшается код, обеспечивающий автоматическое поддержание нуля измерителя как в режиме контроля начальной частоты, так и при контроле ошибок во время частотной модуляции при любых параметрах модулированного сигнала.

Синхронизатор 1 посредством умножения и деления частоты f опорного колебания вырабатывает высокоЧастот

45

50

55

ное колебание с частотой f , в не-г сколько раз превьппающей максимальнуй девиацию частоты измеряемого сигнала, а также два сигнала тактовой, частоты и два., строба (фиг.З). Строб с второго выхода синхронизатора 1 определяет также начало формирования ЛЧМ сигнала в исследуемом генераторе.

Измеритель частотных ошибок (фиг. 1) работает следующим образом.

На вход измерителя поступает сигнал

где. и - амплитуда исследуемого сигнала;(t) -.фазовая ошибка;

tg - момент начала ЛЧМ сигнала; V - скорость частотной модуляции.

До начала модуляции, т.е. до момента времени t, на входах фазового детектора 6 присутствуют сигналы

U,(t)U, (f,+f)(t-c)+:)(t- t:) ; U2(t)U,()t+9(t) -t-(t)

где

f- - частота колебания на пятом

С

выходе синхронизатора 1; 9(t) - сдвиг фаз, требуемьй для

настройки нуля измерителя.

ния приводит к появлению ошибок измерения, начиная с момента времени tg. Для их исключения после фильтра 11 нижних частот, осуществляющего фильтрацию суммарной частоты постуДля того, чтобы измеритель регист- - пающих на входы фазового детектора 6

рировал частотные ошибки (t)(t)- -(t- t)/ o необходимо до начала модуляции обеспечить в фазовращателе 8 сдвиг фаз

25

сигналов, включен блок 9 выборки- запоминания, стробируемый в моменты времени , где , ±1, ±2, ±3,... ..., т.е. тогда, когда желаемое значение сдвига фазы и значение фазы, реализуемое в фазовращателе 8, одинаковы. Напряжение на выходе блока 9 выборки-запоминания пропорционально отклонению частоты i (t) от закона частотной модуляции, т.е.

9(t)27(()qT

27qKr при ttt,

Ч

(1)

где , ,1,2,3,...

После начала модуляции и до момента времени на входах фазо30

сигналов, включен блок 9 выборки- запоминания, стробируемый в моменты времени , где , ±1, ±2, ±3,.. ..., т.е. тогда, когда желаемое значение сдвига фазы и значение фазы, реализуемое в фазовращателе 8, одинаковы. Напряжение на выходе блока 9 выборки-запоминания пропорционально отклонению частоты i (t) от за кона частотной модуляции, т.е.

него детектора |Налы

6 присутствуют сигe(kT)sot2(kT)j

U,(t)U,(f,+f)(t- )+;)(t-t)l;

и (t)()t+ ;v(t-t ) + +Ф(t)+(t) .

Для правильной работы измерителя частотных ошибок сдвиг фаз на временном интервале t , t,+ с} должен меняться следующим образом:

ф(t) u-(t-to)2-Kp(to) при t +IJit t/)

При t tp + с на входах фазового детектора 6 присутствуют сигналы

и, (t)U, (f H+fp) (t- b) + -KtV(t-tp- )2+(t- ) ;

Uj(t)U2Cos 2 S-(f«+f Jt+ SV(t-t)2 + +9(t) + (t) .

где - коэффициент пропорциональ35 I НОСТИ.

Входящий в измеритель частотных ошибок блок 12 формирования кода фазы работает следующим образом. На первый вход первого сумматора

40 15, кодовый вход первого накопителя 13 и первый вход первого коммутатора 17 поступают соответственно коды О, 5 Ку; qK, причем коды О, и qKy получаются соответст45 вующим сдвигом разрядов кода Ку.

До начала модуляции первый 13 и второй 14 накопители кодов обнулены и на выход блока 12 проходят без изменения дробные разряды кода частоты,

50 т.е. код qK, -ent(qK ). Здесь знак ent () - оператор вьщеления целой части. В момент времени t на уста- новочньш вход блока 12 формирования кода фазы с второго выхода синхрониВ этом случае фазовый сдвиг необ- 55 затора 1 поступает строб, -с приходом которого начинается тактирование первого 13 и второго 14 накопителей кодов. По этому же стробу с второго выхода синхронизатора 1 в контролиходимо менять по закону

ф (t) (t +г)+2 J Vc (t-t.,-7)

при

t .

(3)

2918904

Таким образом, для правильной настройки измерителя частотных ошибок необходимо сформировать код управления фазовращателем 8, который был 5 бы постоянен до начала модуляции (1), менялся поквадратичному закону (2) на интервале t , и был линейным (3), начиная с t.+ с . Соответствующий такому фазовому сдвигу код выра- 0 батывается в блоке 12 формирования кода фазы. В соответствии с этим кодом фаза высокочастотного сигнала с частотой fg дискретно меняется (фиг.- 2). Дискретность этого изменеJ5

ния приводит к появлению ошибок измерения, начиная с момента времени tg. Для их исключения после фильтра 11 нижних частот, осуществляющего фильтрацию суммарной частоты посту

сигналов, включен блок 9 выборки- запоминания, стробируемый в моменты времени , где , ±1, ±2, ±3,... ..., т.е. тогда, когда желаемое значение сдвига фазы и значение фазы, реализуемое в фазовращателе 8, одинаковы. Напряжение на выходе блока 9 выборки-запоминания пропорционально отклонению частоты i (t) от закона частотной модуляции, т.е.

e(kT)sot2(kT)j

руемом исследуемом генераторе начинается формирование ЛЧМ сигнала.

В интервале вренени t.; выход первого сумматора 15 через первый коммутатор 17 подключен к кодовому входу второг о накопителя 14. При этом на выходе накопителя 14 кодов в моменты времени tj,-tj,+T, + +2Т, t -Ц+ЗТ, ..., формируются меняющиеся по квадратичному

К

4,5 К

V

закону коды 0,5 К, 2 ..., 0,5 , где . С приходом на первый коммутатор17 в момент времени t +1; управляющего строба с третьего выхода синхронизатора 1 на кодовьй вход второго накопителя 14 кодов поступает код qK и на его выходе в моменты времени (q+1)Т, to-tH + (q+2)T, tj,-t + (q+3)T и т.д. формируется код, меняющийся по линейному закону и принимающий значения 0,5q2K +qKy; 0,5q2KyH-2qKv ; 0,5q K +3qKY и т.д. При положительном знаке скорости ЧМ эти коды через второй коммутатор 18 поступают на второй сумматор 16 без изменения, а при отрицательном - после прохождения через инвертор 19.

Полный код, управляющий работой фазовращателя 8, формируется во втором сумматоре 16. Величина дискрета фазовращателя 8 непосредственно сказывается на точности измерения частотных ошибок. Реально существующие фазовращатели имеют в зависимости от диапазона частот дискретность установки фазы от единиц до долей градуса.

При соответственном изменении структуры блока 12 формирования кода фазы измеритель частотных ошибок может использоваться для контроля ошибок в сигналах с нелинейным полиноминальным законом изменения частоты

Формула изобретения

Измеритель частотных ошибок, содержащий синхронизатор, фазовращатель, первый и второй смесители, первые 50 входы которых соединены между собой и с входом устройства, выход первого

. 35

5

0

25

50

смесителя через последовательно соединенные первьй полосовой фильтр и линию задержки подключен к первому входу фазового детектора, выход второго смесителя через второй полосовой фильтр подключен к второму входу фазового детектора, а выход фазовращателя соединен с вторым входом второго смесителя, отличающий- с я тем, что, с целью расширения функциональных возможностей, в него введены блок выборки-запоминания, фильтр Нижних частот, регистр памяти и блок формирования кода фазы, включающий в себя первьш и второй накопители кодов, перв ый и второй сумматоры, первый и второй коммутаторы и инвертор, причем разряды кода скорости регистра памяти соединены с первым входом первого сумматора, кодовым входом первого накопителя кодов и первым входом первого коммутатора, а разряды кода частоты подключены к первому входу второго сумматора, выход которого соединен с управляющим входом фазовращателя, выход первого накопителя кодов подключен к второму входу первого сумматора, вьпкод которого подсоединен к второму входу первого коммутатора, выход которого соединен с кодовым входом второго накопителя, выход которого подключен непосредственно и . через инвертор к первому и второму 35 входам второго коммутатора, управляющий вход которого подсоединен к знаковому разряду кода скорости регистра памяти, а выход подключен к второму входу второго сумматора, выход фазового детектора через фильтр нижних частот подключен к сигнальному входу блока выборки-запоминания, первьй и второй выходы синхронизатора соединены соответственно с тактовыми и установочными входами первого и второго накопителя кодов, третий - с управляющим входом первого коммутатора, четвертьй выход подключен к cтpoбиpyющe ry входу блока выборки- запоминания, а пятый - соединен с вторым входом первого, смесителя и сигнальным входом фазовращателя.

30

40

45

4f

и

стр

-ип ффффф

(Pus.2

I.I 1 I I. I I I I I I I t

to

г J

III I I I I I I I I I

,t

t

-i

..,t

Составитель В. Новоселов Редактор И. Дербак Техред Л.Серяюкова Корректор |1.Самборская

Зак1Г227МЗ Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-пол

играфическое предприятие, г. Ужгород, ул. Проектная, 4

(fuz.-S

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель фазочастотных характери-СТиК чЕТыРЕХпОлюСНиКОВ СВч | 1979 |

|

SU836603A1 |

| Измеритель частотных ошибок | 1980 |

|

SU964990A1 |

| Синтезатор частот | 1979 |

|

SU830652A1 |

| СИСТЕМА РАДИОСВЯЗИ | 1993 |

|

RU2085039C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2039365C1 |

| ИНДИКАТОРНОЕ УСТРОЙСТВО | 1991 |

|

RU2005994C1 |

| Устройство выбора каналов для разнесенного приема | 1988 |

|

SU1525925A1 |

| Формирователь частотно-модулированных сигналов | 1980 |

|

SU926756A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

Изобретение относится к радиотехнике и может найти применение в устройствах контроля и синтеза прецизионных частотно-модулированных сигналов . Цель изобретения - расширение функциональных возможностей устройства. Измеритель частотных ошибок соВход держит синхронизатор 1, смесители 2 и 3, полосовые фильтры 4 и 7 и фазовращатель 8. В устройство введены блок 9 выборки-запоминания, регистр 10 памяти, фильтр 11 нижних частот и блок 12 формирования кода фазы, включающий накопители 13 и 14 кодов, сумматоры 15 и 16, коммутаторы 17 и 18 и инвертор 19. Введенные элементы и образованные новые функциональные связи позволяют уменьшить время перестройки измерителя и обеспечить его работу на начальном участке контролируемого сигнала. При соответственном изменении структуры блока 12 формирования кода фазы измеритель частотных ошибок может использоваться для контроля ошибок в сигналах с нелинейным полиноминальным законом изменения частоты. 3 ил. i (Л Выход ГГ-П-4 фиг.1 к контролируемому генератору

| Устройство для снятия характеристик электронной настройки широкополосных генераторов | 1957 |

|

SU113346A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Измеритель частотных ошибок | 1980 |

|

SU964990A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-23—Публикация

1984-10-18—Подача