112

Изобретение относится к вычислительной технике, а именно к информационно-обучающим устройствам на базе микропроцессоров и микроЭВМ, и может быть использовано для отображения статической и динамической информации, в том числе алфавитно-цифровой, графической и произвольно-символьной

Известны устройства для отображения информации на экране электронно- лучевой трубки 1.

Недостатком подобных устройств яв ляется то, что они-предназначены только для отображения статической информации и при использовании их для отображения произвольных динамических объектов объем оборудования . памяти и схем управления существенно возрастает.

Однако .из известных устройств со- держит массивы оперативного запоминающего, устройства (ОЗУ) для хранения информации о требуемом положении объектов по координатам X и У, ОЗУ с адресами объектов в постоянном запо- минающем устройстве (ПЗУ), масштабом и цветом объектов, ПЗУ с информацией о содержании объектов, счетчики фиксации луча на экране трубки по координатам X и У, первый и второй ре- гистры расположения объектов по координатам X и У соответственно, схемы сравнения и видеосумматор 21,

Это устройство обладает существенными недостатками, так, как требуется отдельное ЗУ с адресацией по содержанию для отображения каждого объекта индикации, т,е, при индикации 32 объектов требуется 32 ЗУ с адресацией по содержанию, которые занимают большую площадь при изготовлении на одной подложке, В схеме используются неоднородные ЗУ, увеличивается оборудование в цепях управления,

Наиболее близким к изобретению по технической сущности явЛяется устройство, содержащее ЗУ с адресацией по содержанию, ОЗУ с адресами объектов в ПЗУ, масштабом и цветом объ- ектов, ПЗУ с информацией о содержании объектов, счетчики фиксации луча на экране трубки, регистры расположения объектов, видеосумматор, систему управления при обращении к ОЗУ при индикации малых объектов или группы основных объектов.

Данное устройство обладает следую щими существенными недостатками: ис12

пользуется неоднородная память для реализации требуется большой объем памяти, как оперативной, так и с адресацией по содержанию, объем памяти возрастает при возрастании количеств отображаемых объектов, но функционалные возможности устройства ограничены, так как не удается менять размеры изображений; при высвечивании одного символа требуется многократное обращение к ОЗУ, что снижает надежность устройства.

Цель изобретения упрощение устройства за счет уменьшения объема блока памяти.

Поставленная цель достигается тем что в дисплейный процессор, содержащий первьй блок сопряжения, соединенный с информационной щиной, которая соединена с блоком памяти и втр.- рым блоком сопряжения, один из входов которого соединен с выходом формирователя адреса, первую и вторую схемы сравнения, первые входы которых соединеныс вьгходами первого и второго счетчиков соответственно, вторые входы соединены с выходами первого и второго регистров соответственно, а выходы соединены с первым входом третьего счетчика и первым входом видеосумматора, второй вход которого соединен с первым входом второго счетчика, другой вход которого соеди- нен с вторым входом TfpeTbero счетчика, второй вход которого соединен с одним из входов первого счетчика, содержит первый и второй коммутаторы, блок дешифрации признака наличия символа в данной точке экрана, третий, четвертый и пятый регистры, входы которых соединены с входам/ , первого и второго регистров, третьим входом видеосумматора и выходом второго бло- блока сопряжения, второй вход которого соединен с выходом пятого регистра, четвертым входом видеосумматора, входом формирователя адреса и первым входом перво го коммутатора, второй вход которого соединен с первым входом второго коммутатора и с выходом блока дешифрации признака наличия символа в данной точке экрана, первый вход которого соединен с выходом третьего регистра, второй вход которого соединен с вторым входом блока дешифрации признака наличия символа в данной точке экрана и другим входом третьего счетчика, выход которого соединен с третьи входом первого коммутатора, выход которого соединен с адресной шиной блока памяти, выход четвертого регистра соединен с вторым входом второго коммутатора, выход которого соединен с четвертым входом первого коммутатора, пятый вход которого соединен с внешней адресной шиной, третий вход блока дешифрации признака наличия символа в данной экране соединен с первым входом второго счетчика, а также тем, что блок дешифрации признака наличия символа в данной точке экрана содержит дешифратор, четвертый счетчик,-шестой регистр, первый и второй элементы 2И-ИЛИ, седьмой регистр и третий коммутатор, выход которого соединен с входом четвертого счетчика, выход которого соединен с вторым входом третьего коммутатора и входом шестого регистра, выход которого с входом дешифратора, выход которого соединен с вторым входом второго элемента 2И-ИЛИ, а также тем, что видеосумматор содержит седьмой, восьмой и девятый регистры, регистр сдвига и четвертый ком1 утатор, входы которого соединены с выходом седьмого и восьмого регистров, вход восьмого регистра соединен с входом девятого регистра,- вьпсод которого соединен с . входом регистра сдвига, последовательный выход которого соединен с третьим входом четвертого коммутатора.

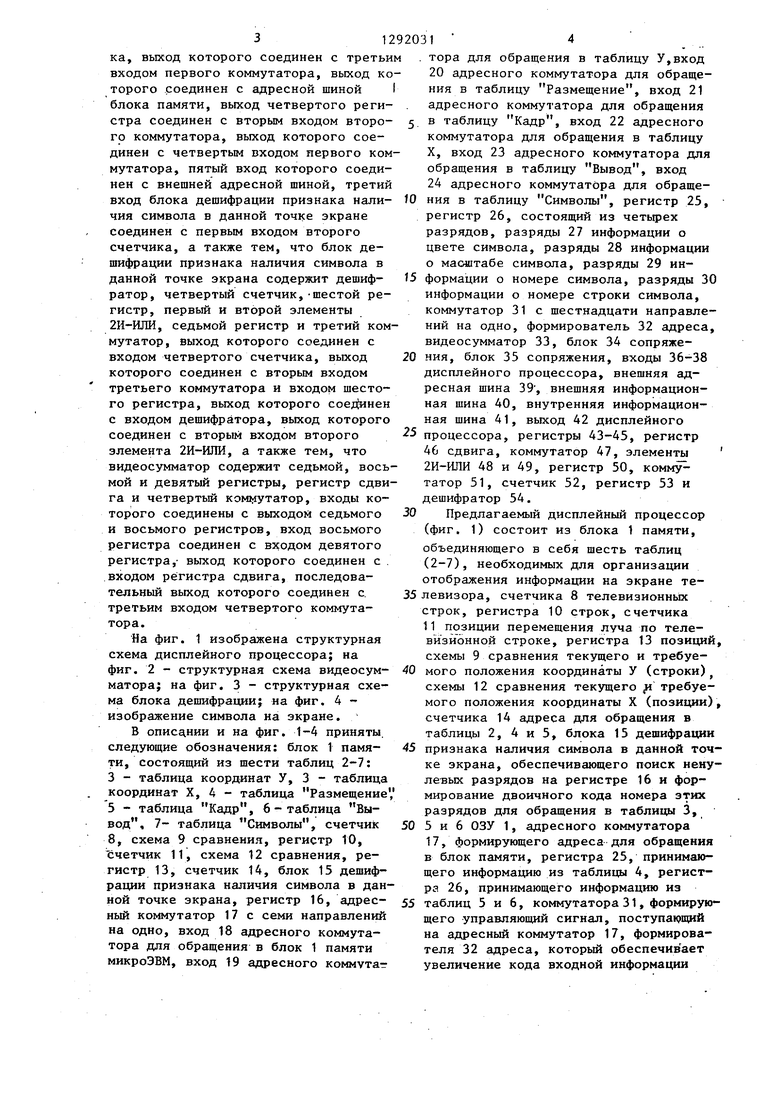

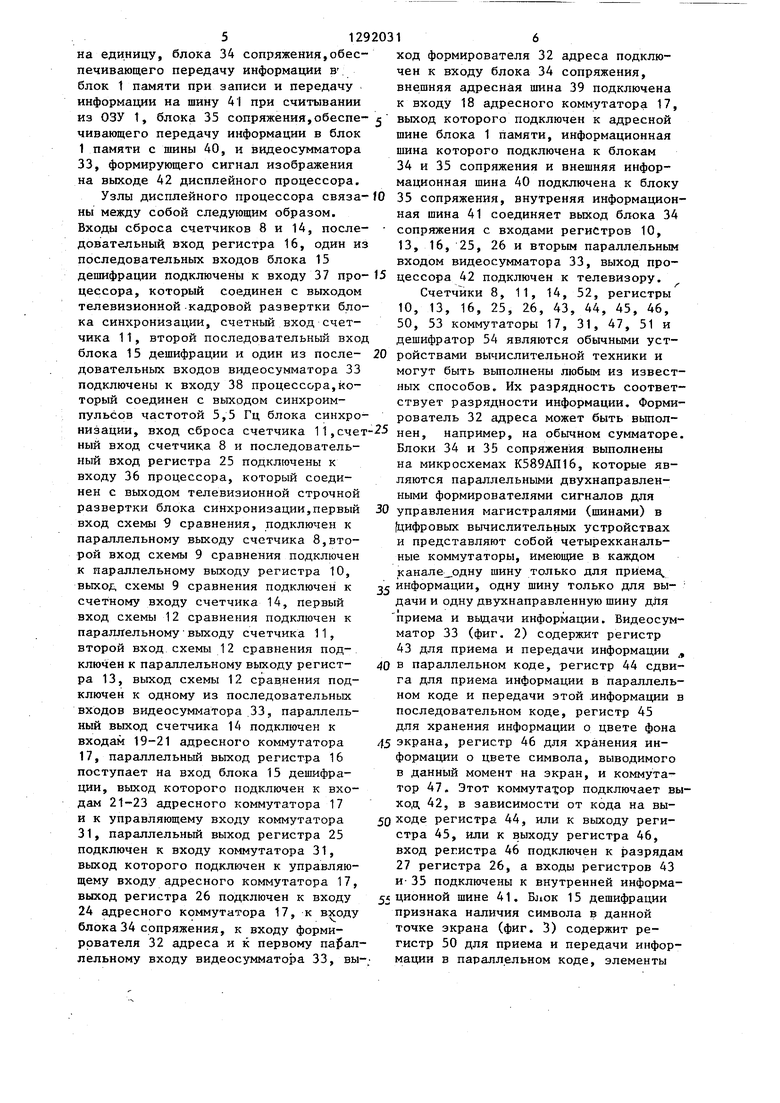

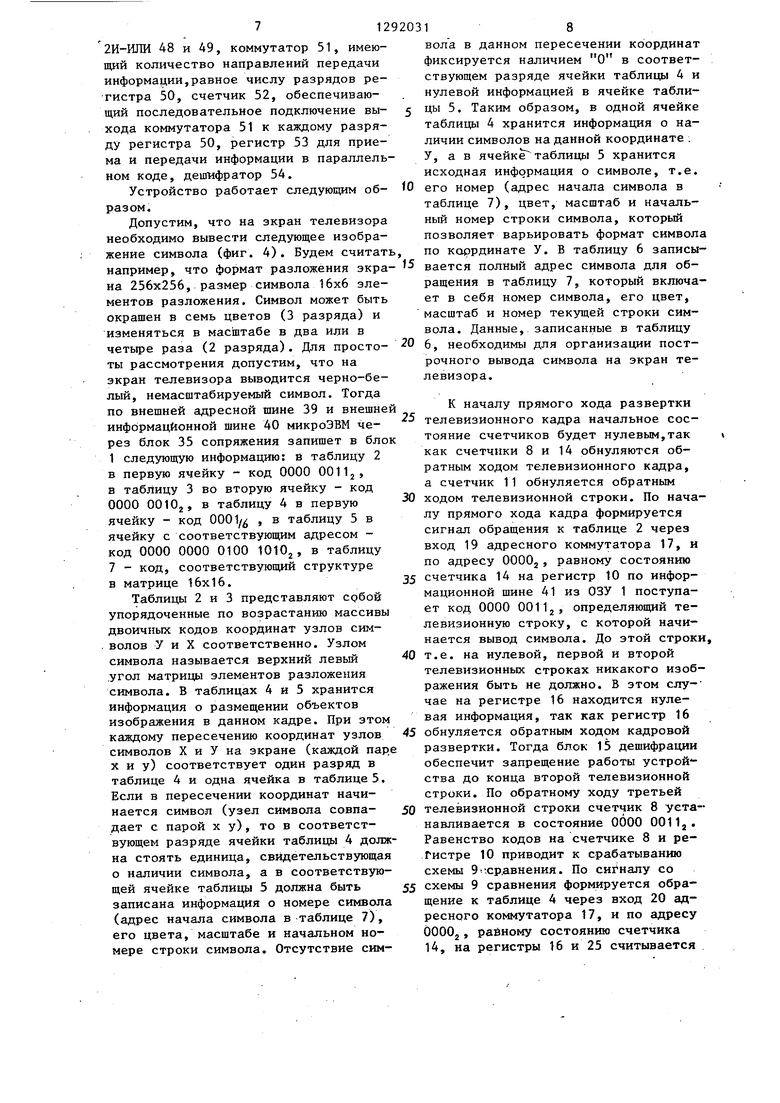

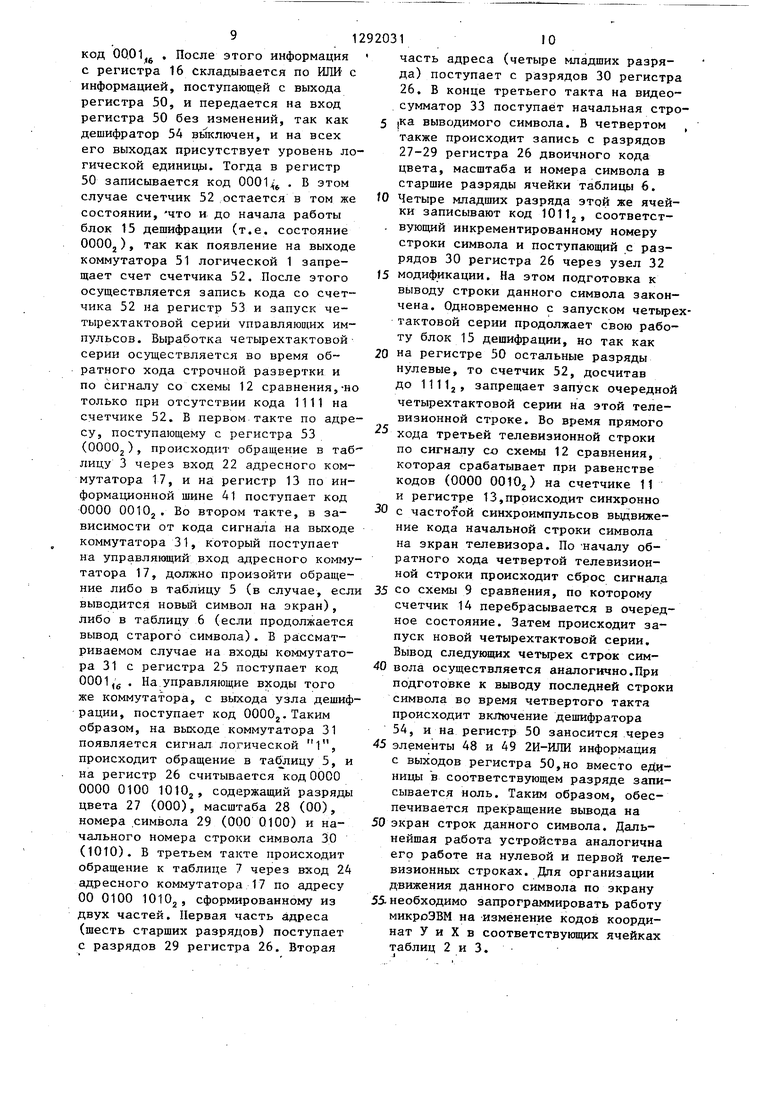

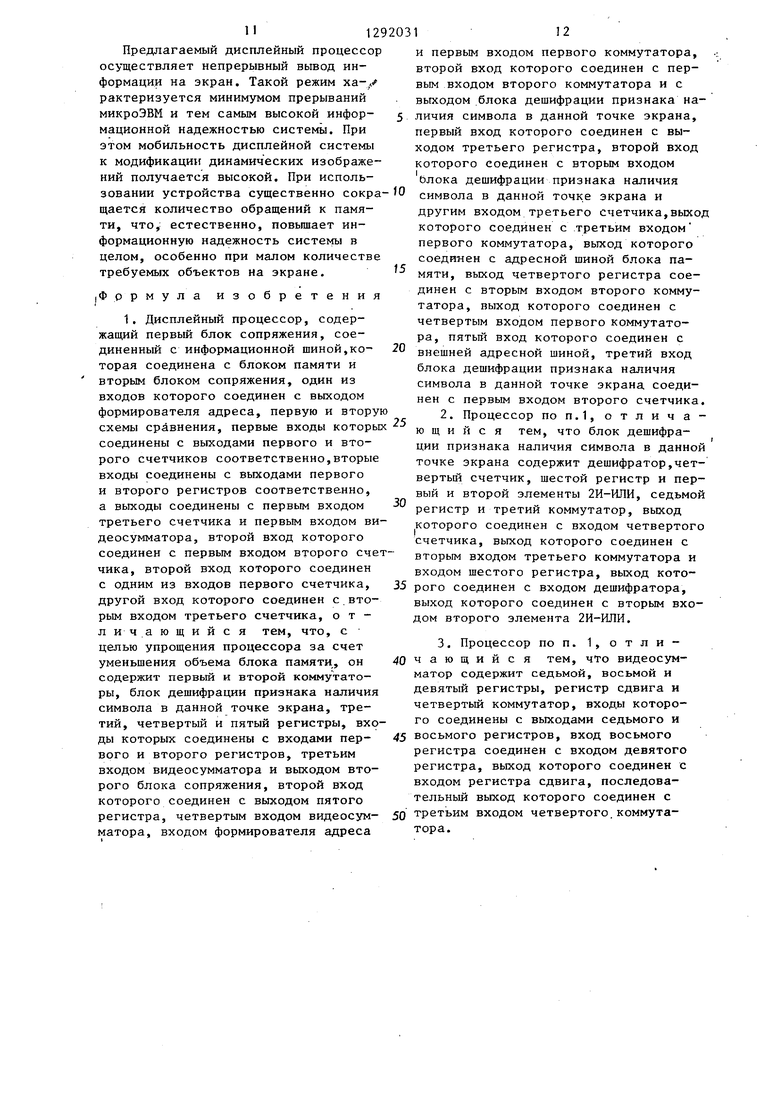

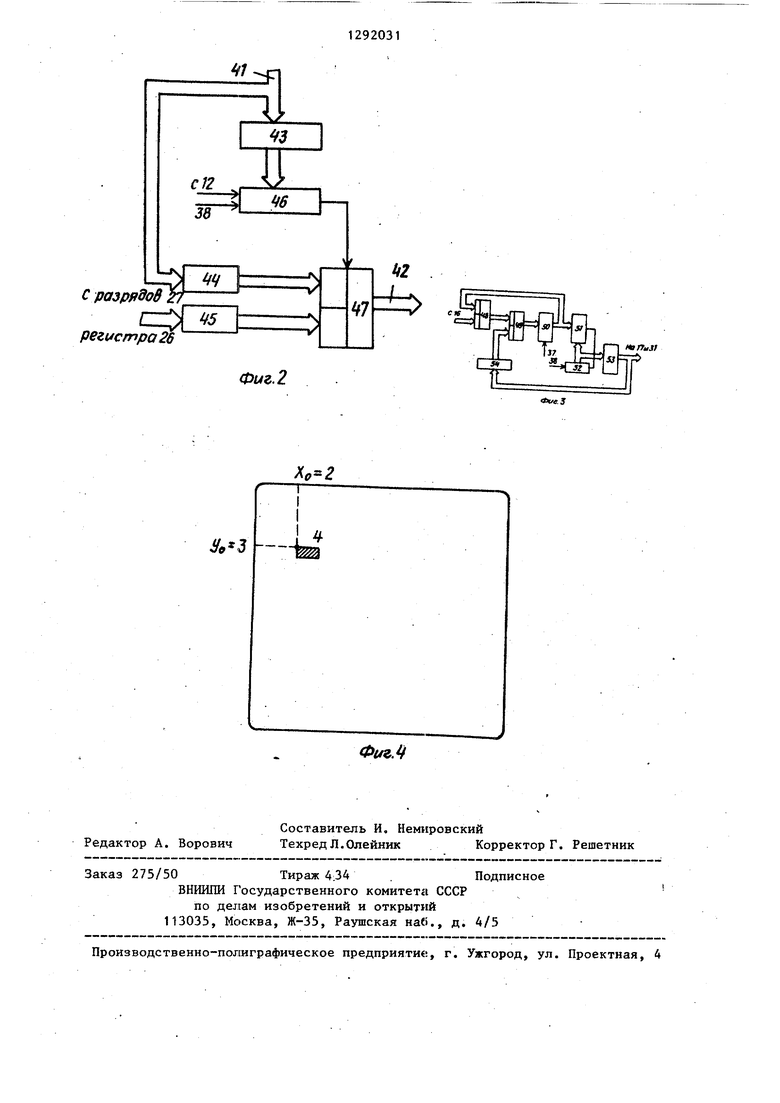

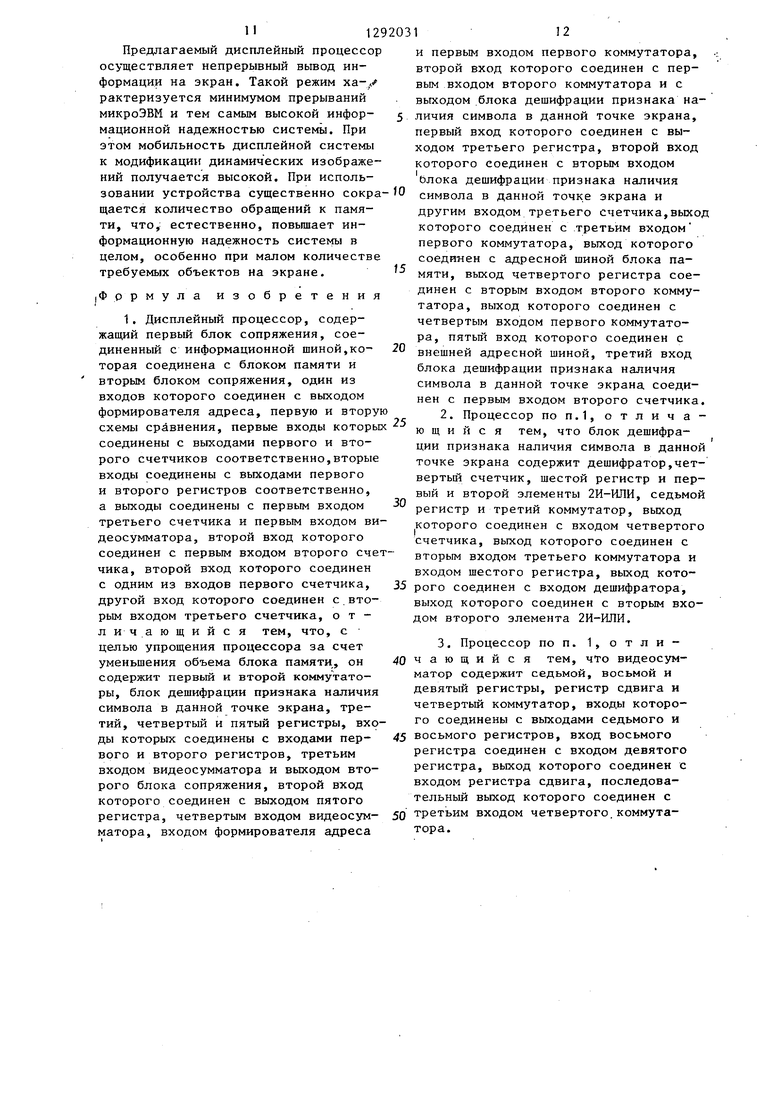

На фиг. 1 изображена структурная схема дисплейного процессора; на фиг. 2 - структурная схема видеосум- матора; на фиг. 3 - структурная схема блока дешифрацииJ на фиг. 4 изображение символа на экране.

В описании и на фиг. 1-4 приняты, следующие обозначения: блок 1 памяти, состоящий из шести таблиц 2-7: 3 - таблица координат У, 3 - таблица координат X, 4 - таблица Размещение 5 - таблица Кадр, 6 - таблица Вывод, 7- таблица Символы, счетчик 8, схема 9 сравнения, регистр 10, счетчик 11, схема 12 сравнения, регистр 13, счетчик 14, блок 15 дешифрации признака наличия символа в данной точке экрана, регистр 16, адресный коммутатор 17 с семи направлений на одно, вход 18 адресного коммутатора для обращения в блок 1 памяти микроэвм, вход 19 адресного коммута0

5

. тора для обращения в таблицу У,вход 20 адресного коммутатора для обращения в таблицу Размещение, вход 21 адресного коммутатора для обращения . в таблицу Кадр, вход 22 адресного коммутатора для обращения в таблицу X, вход 23 адресного коммутатора для обращения в таблицу Вывод, вход 24 адресного коммутатора для обраще0 кия в таблицу Символы, регистр 25, регистр 26, состоящий из четырех разрядов, разряды 27 информации о цвете символа, разряды 28 информации о масштабе символа, разряды 29 ин5 формации о номере символа, разряды 30 информации о номере строки символа, коммутатор 31 с шестнадцати направлений на одно, формирователь 32 адреса, видеосумматор 33, блок 34 сопряжения, блок 35 сопряжения, входы 36-38 дисплейного процессора, внешняя адресная шина 39, внешняя информационная шина 40, внутренняя информационная шина 41, выход 42 дисплейного процессора, регистры 43-45, регистр 46 сдвига, коммутатор 47, элементы 2И-ИЛИ 48 и 49, регистр 50, комму татор 51, счетчик 52, регистр 53 и дешифратор 54.

0 Предлагаемый дисплейный процессор (фиг, 1) состоит из блока 1 памяти,

объединяющего в себя шесть таблиц (2-7), необходимых для организации отображения информации на экране те5 левизора, счетчика 8 телевизионньЬс строк, регистра 10 строк, счетчика 11 позиции перемещения луча по телевизионной строке, регистра 13 позиций, схемы 9 сравнения текущего и требуе0 мого положения координаты У (строки), схемы 12 сравнения текущего требуемого положения координаты X (позиции), счетчика 14 адреса для обращения в таблицы 2, 4 и 5, блока 15 дешифрации

5 признака наличия символа в данной точке экрана, обеспечивающего поиск ненулевых разрядов на регистре 16 и формирование двоичного кода номера этих разрядов для обращения в таблицы 3,

0 5 и 6 ОЗУ 1, адресного коммутатора 17, формирующего адреса для обращения в блок памяти, регистра 25, принимающего информацию из таблицы 4, регистра 26, принимающего информацию из

5 таблиц 5 и 6, коммутатора 31, формирующего управляющий сигнал, поступа1рщий на адресный коммутатор 17, формирователя 32 адреса, который обеспечивает увеличение кода входной информации

на единицу, блока 34 сопряжения,обеспечивающего передачу информации в блок 1 памяти при записи и передачу информации на шину 41 при считывании из ОЗУ 1, блока 35 сопряжения,обеспе- чивакицего передачу информации в блок 1 памяти с шины 40, и видеосумматора 33, формирующего сигнал изображения на выходе 42 дисплейного процессора.

Узлы дисплейного процессора связа-fO 35 сопряжения, внутреняя информационны между собой следующим образом. Входы сброса счетчиков 8 и 14, последовательный вход регистра 16, один из последовательных входов блока 15

ная шина 41 соединяет выход блока 34 сопряжения с входами регистров 10, 13, 16, 25, 26 и вторым параллельным входом видеосумматора 33, выход продешифрации подключены к входу 37 про-15 цессора 42 подключен к телевизору.

цессора, который соединен с выходом телевизионной кадровой развертки блока синхронизации, счетный вход счетчика 11, второй последовательный вход блока 15 дешифрации и один из после- 20 довательных входов вмдеосумматора 33 подключены к входу 38 процессора,который соединен с выходом синхроимпульсов частотой 5,5 Гц блока синхроСчетчики 8, 11, 14, 52, регистры 10, 13, 16, 25, 26, 43, 44, 45, 46, 50, 53 коммутаторы 17, 31, 47, 51 и дешифратор 54 являются обычньми устройствами вычислительной техники и могут быть вьшолнены любым из известных способов., Их разрядность соответствует разрядности информации. Формирователь 32 адреса может быть вьшолнизации, вход сброса счетчика 11,счет-25 нен, например, на обычном сумматоре.

ный вход счетчика 8 и последовательный вход регистра 25 подключены к входу 36 процессора, который соединен с выходом телевизионной строчной развертки блока синхронизации,первый вход схемы 9 сравнения, подключен к параллельному выходу счетчика 8,второй вход схемы 9 сравнения подключен к параллельному выходу регистра 10, выход схемы 9 сравнения подключен к счетному входу счетчика 14, первый вход схемы 12 сравнения подключен к параллельномувыходу счетчика 11, второй вход схемы 12 сравнения подключен к параллельному выходу регистра 13, выход схемы 12 срацнения подключен к одному из последовательных входов видеосумматора .33, параллельный выход счетчика 14 подключен к входам 19-21 адресного коммутатора 17, параллельный выход регистра 16 поступает на вход блока 15 дешифрации, выход которого подключен к входам 21-23 адресного коммутатора 17 и к управляющему входу коммутатора 31, параллельный выход регистра 25 подключен к входу коммутатора 31, выход которого подключен к управляющему входу адресного коммутатора 17, выход регистра 26 подключен к входу 24 адресного коммутатора 17, к входу блока 34 сопряжения, к входу формирователя 32 адреса и к первому параллельному входу видеосуммато1эа 33, вы-Блоки 34 и 35 сопряжения выполнены на микросхемах K589AII16, которые являются параллельными двухнаправлен- ными формирователями сигналов для

30 управления магистралями (шинами) в цифровых вычислительных устройствах и представляют собой четырехканаль- ные коммутаторы, имеющие в каждом канале одну шину только для приема

эг информации, одну шину только для вы- дачи и одну двухнаправленную шину для приема и выдачи информации. Видеосумматор 33 (фиг. 2) содержит регистр 43 для приема и передачи информации

40 в параллельном коде, регистр 44 сдвига для приема информации в параллельном коде и передачи этой .информации в последовательном коде, регистр 45 для хранения информации о цвете фона

5 экрана, регистр 46 для хранения информации о цвете символа, выводимого в данный момент на экран, и коммутатор 47. Этот коммутат;ор подключает выход 42, в зависимости от кода на вы50 ходе регистра 44, или к выходу регистра 45, или к выходу регистра 46, вход регистра 46 подключен к разрядам 27 регистра 26, а входы регистров 43 и-35 подключены к внутренней информа53 ционной шине 41, Блок 15 дешифрации признака наличия символа в данной точке экрана (фиг. 3) содержит регистр 50 для приема и передачи информации в параллельном коде, элементы

ход формирователя 32 адреса подключен к входу блока 34 сопряжения, внешняя адресная шина 39 подключена к входу 18 адресного коммутатора 17, выход которого подключен к адресной шине блока 1 памяти, информационная шина которого подключена к блокам 34 и 35 сопряжения и внешняя информационная шина 40 подключена к блоку

ная шина 41 соединяет выход блока 34 сопряжения с входами регистров 10, 13, 16, 25, 26 и вторым параллельным входом видеосумматора 33, выход проСчетчики 8, 11, 14, 52, регистры 10, 13, 16, 25, 26, 43, 44, 45, 46, 50, 53 коммутаторы 17, 31, 47, 51 и дешифратор 54 являются обычньми устройствами вычислительной техники и могут быть вьшолнены любым из известных способов., Их разрядность соответствует разрядности информации. Формирователь 32 адреса может быть вьшолнен, например, на обычном сумматоре.

Блоки 34 и 35 сопряжения выполнены на микросхемах K589AII16, которые являются параллельными двухнаправлен- ными формирователями сигналов для

30 управления магистралями (шинами) в цифровых вычислительных устройствах и представляют собой четырехканаль- ные коммутаторы, имеющие в каждом канале одну шину только для приема

эг информации, одну шину только для вы- дачи и одну двухнаправленную шину для приема и выдачи информации. Видеосумматор 33 (фиг. 2) содержит регистр 43 для приема и передачи информации

40 в параллельном коде, регистр 44 сдвига для приема информации в параллельном коде и передачи этой .информации в последовательном коде, регистр 45 для хранения информации о цвете фона

5 экрана, регистр 46 для хранения информации о цвете символа, выводимого в данный момент на экран, и коммутатор 47. Этот коммутат;ор подключает выход 42, в зависимости от кода на вы50 ходе регистра 44, или к выходу регистра 45, или к выходу регистра 46, вход регистра 46 подключен к разрядам 27 регистра 26, а входы регистров 43 и-35 подключены к внутренней информа53 ционной шине 41, Блок 15 дешифрации признака наличия символа в данной точке экрана (фиг. 3) содержит регистр 50 для приема и передачи информации в параллельном коде, элементы

fO

20

25

71292031

2И-ИЛИ 48 и 49, коммутатор 51, имею- пщй количество направлений передачи информации,равное числу разрядов ре- истра 50, счетчик 52, обеспечивающий последовательное подключение выхода коммутатора 51 к каждому разряду регистра 50, регистр 53 для приема и передачи информации в параллельном коде, дешифратор 54.

Устройство работает следующим образом.

Допустим, что на экран телевизора необходимо вывести следующее изображение символа (фиг. 4). Будем считать, например, что формат разложения экра- на 256x256, размер символа 16x6 элементов разложения. Символ может быть окращен в семь цветов (3 разряда) и изменяться в масштабе в два или в четыре раза (2 разряда). Для простоты рассмотрения допустим, что на экран телевизора выводится черно-белый, немасштабируемый символ. Тогда по внешней адресной шине 39 и внешней инфЬрмацйонной шине 40 микроЭВМ через блок 35 сопряжения запишет в блок 1 следующую информацию: в таблицу 2 в первую ячейку - код 0000 0011, в таблицу 3 во вторую ячейку - код 0000 00Ю, в таблицу 4 в первую ячейку - код 0001уг , в таблицу 5 в ячейку с соответствующим адресом - код 0000 0000 0100 1010, в таблицу 7 - код, соответствующий структуре в матрице 16x16.

Таблицы 2 и 3 представляют собой упорядоченные по возрастанию массивы двоичных кодов координат узлов сим- волов У и X соответственно. Узлом символа называется верхний левый угол матрицы элементов разложения символа. В таблицах 4 и 5 хранится информация о размещении объектов изображения в данном кадре. При этом каждому пересечению координат узлов символов X и У на экране (каждой паре X и у) соответствует один разряд в таблице 4 и одна ячейка в таблице 5. Если в пересечении координат начинается символ (узел символа совпадает с парой X у), то в соответствующем разряде ячейки таблицы 4 должна стоять единица, свидетельствующая о наличии символа, а в соответствующей ячейке таблицы 5 должна быть 55 записана информация о номере символа (адрес начала символа в таблице 7), его цвета, масштабе и начальном номере строки символа. Отсутствие сим50

е м в л

30

т т к а хо лу си вх п

35 сч ма ет ле на

40 т

те ра ча ва

45 об ра об ст ст те на Ра ги сх сх ще ре OO 14

fO

0

2031

8

вола в данном пересечении координат фиксируется наличием О в соответствующем разряде ячейки таблицы 4 и нулевой информацией в ячейке таблицы 5. Таким образом, в одной ячейке таблицы 4 хранится информация о наличии символов на данной координате . У, а в ячейке таблицы 5 хранится исходная информация о символе, т.е. его номер (адрес начала символа в таблице 7), цвет, масштаб и начальный номер строки символа, который позволяет варьировать формат символа по коррдинате У. В таблицу 6 записывается полный адрес символа для обращения в таблицу 7, который включает в себя номер символа, его цвет, масштаб и номер текущей строки символа. Данные, записанные в таблицу 6, необходимы для организации построчного вывода символа на экран телевизора.

К началу прямого хода развертки телевизионного кадра начальное состояние счетчиков будет нулевым,так как счетчики 8 и 14 обнуляются обратным ходом телевизионного кадра, а счетчик 11 обнуляется обратным ходом телевизионной строки. По началу прямого хода кадра формируется сигнал обращения к таблице 2 через вход 19 адресного коммутатора 17, и по адресу 0000, равному состоянию

счетчика 14 на регистр 10 по информационной шине 41 из ОЗУ 1 поступает код 0000 00112, определяющий телевизионную строку, с которой начинается вывод символа. До этой строки,

т.е. на нулевой, первой и второй

телевизионных строках никакого изображения быть не должно. В этом слу- чае на регистре 16 находится нулевая информация, так как регистр 16

обнуляется обратным ходом кадровой развертки. Тогда блок 15 дешифрации обеспечит запрещение работы устрой ства до конца второй телевизионной строки. По обратному ходу третьей телевизионной строки счетчик 8 устанавливается в состояние 0000 001Ij. Равенство кодов на счетчике 8 и регистре 10 приводит к срабатыванию схемы 9 .срдвнения. По со схемы 9 сравнения формируется обраение к таблице 4 через вход 20 адесного коммутатора 17, и по адресу OOOj, равному состоянию счетчика 14, на регистры 16 и 25 считывается

код 00.01., . После этого информация

Ло

с регистра 16 складывается по ИЛИ с информацией, поступающей с выхода регистра 50, и передается на вход регистра 50 без изменений, так как дешифратор 54 вьпслючен, и на всех его выходах присутствует уровень логической единицы. Тогда в регистр 50 записывается код 0001 . В этом случае счетчик 52 остается в том же состоянии, ЧТО и до начала работы блок 15 дешифрации (т.е. состояние OOOOj), так как появление на выходе коммутатора 51 логической 1 запрещает счет счетчика 52. После этого осуществляется запись кода со счетчика 52 на регистр 53 и запуск четырехтактовой серии упоавляюпшх импульсов. Выработка четьфехтактовой серии осуществляется во время обратного хода строчной развертки и по сигналу со схемы 12 сравнения,-но только при отсутствии кода 1111 на счетчике 52. В первом такте по адресу, поступающему с регистра 53 (OOOOj), происходит обращение в таб лицу 3 через вход 22 адресного коммутатора 17, и на регистр 13 по информационной шине 41 поступает код

0000OOlOj. Во втором такте, в зависимости от кода сигнала на вькоде коммутатора 31, который поступает

на управляющий вход адресного коммутатора 17, должно произойти обращение либо в таблицу 5 (в случае, есл выводится новьш символ на экран), Либо в таблицу 6 (если продолжается вывод старого символа). В рассматриваемом случае на входы коммутатора 31 с регистра 25 поступает код

0001jg . На управляющие входы того

же коммутатора, с выхода узла дешифрации, поступает код 0000. Таким образом, на выходе коммутатора 31 появляется сигнал логической 1, происходит обращение в таблицу 5, и на регистр 26 считывается код 0000 0000 0100 lOIOjj, содержащий разряды цвета 27 (000), масштаба 28 (00), номера символа 29 (000 0100) и начального номера строки символа 30 (1010). В третьем такте происходит обращение к таблице 7 через вход 24 адресного коммутатора 17 по адресу 00 0100 1010, сформированному из двух частей. Первая часть адреса (шесть старших разрядов) поступает с разрядов 29 регистра 26. Вторая

часть адреса (четыре младших разряда) поступает с разрядов 30 регистра 26. В конце третьего такта на видеосумматор 33 поступает начальная стро|Ка выводимого символа. В четвертом , также происходит запись с разрядов 27-29 регистра 26 двоичного кода цвета, масштаба и номера символа в старшие разряды ячейки таблицы 6.

Четыре младших разряда этой же ячейки записывают код 1011, соответст- вующий инкрементированному номеру строки символа и поступающий с разрядов 30 регистра 26 через узел 32

модификации. На этом подготовка к выводу строки данного символа закончена. Одновременно с запуском четьфехтактовой серии продолжает свою работу блок 15 дешифрации, но так как

на регистре 50 остальные разряды нулевые, то счетчик 52, досчитав до Illlj, запрещает запуск очередной четырехтактовой серии на этой телевизионной строке. Во время прямого

хода третьей телевизионной строки по сигналу со схемы 12 сравнения, которая срабатывает при равенстве кодов (0000 0010j) на счетчике 11 и регистре 13,происходит синхронно

с частотой синхроимпульсов выдвижение кода начальной строки символа на экран телевизора. По началу обратного хода четвертой телевизионной строки происходит сброс сигнала

со схемы 9 сравнения, по которому счетчик 14 перебрасывается в очередное состояние. Затем происходит запуск новой четырехтактовой серии. Вывод следующих четырех строк символа осуществляется аналогично.При подготовке к выводу последней строки символа во время четвертого такта происходит вк.гпочение дешифратора 54, и на регистр 50 заносится через

элементы 48 и 49 2И-ИЛИ информация с выходов регистра 50,но вместо единицы в соответствующем разряде записывается ноль. Таким образом, обеспечивается прекращение вывода на

экран строк данного символа. Дальнейшая работа устройства аналогична его работе на нулевой и первой телевизионных строках. Для организации движения данного символа по экрану

необходимо запрограммировать работу микроэвм на изменение кодов координат У и X в соответствующих ячейках таблиц 2 и 3.

II12920

Предлагаемый дисплейный процессор осуществляет непрерывный вывод информации на экран. Такой режим ха-/ рактеризуется минимумом прерываний микроэвм и тем самым высокой информационной надежностью системы. При этом мобильность дисплейной системы к модификации динамических изображений получается высокой. При испольблока дешифрации признака наличи

зовании устройства существенно сокра-fO символа в данной точке экрана и

15

20

щается количество обращений к памяти, что, естественно, повьш1ает информационную надежность системы в целом, особенно при малом количестве требуемых объектов на экране.

|Формула изобретения

1. Дисплейный процессор, содержащий первый блок сопряжения, соединенный с информационной шиной,которая соединена с блоком памяти и вторым блоком сопряжения, один из входов которого соединен с выходом формирователя адреса, первую и вторую схемы сравнения, первые входы которых соединены с выходами первого и второго счетчиков соответственно,вторые входы соединены с выходами первого и второго регистров соответственно, а выходы соединены с первым входом третьего счетчика и первым входом видеосумматора, второй вход которого соединен с первым входом второго счет30

другим входом третьего счетчика, которого соединен с третьим вход первого коммутатора, выход котор соединен с адресной шиной блока мяти, выход четвертого регистра динен с вторым входом второго ко татора, выход которого соединен четвертым входом первого коммутат ра, пятый вход которого соединен внешней адресной шиной, третий в блока дешифрации признака наличи символа в данной точке экрана со нен с первым входом второго счет 2. Процессор ПОП.1, отли ющийся тем, что блок дешиф ции признака наличия символа в д точке экрана содержит дешифратор вертый счетчик, шестой регистр и вый и второй элементы 2И-ИЛИ, сед регистр и третий коммутатор, выхо которого соединен с входом четвер счетчика, выход которого соединен

вторым входом третьего коммутатор входом шестого регистра, выход ко 35 рого соединен с входом дешифратор выход которого соединен с вторым дом второго элемента 2И-ИЛИ.

чика, второй вход которого соединен с одним из входов первого счетчика, другой вход которого соединен с вторым входом третьего счетчика, отличающийся тем, что, с целью упрощения процессора за счет уменьшения объема блока памяти,, он содержит первый и второй коммутаторы, блок дешифрации признака наличия символа в данной точке экрана, третий, четвертый и пятый регистры, входы которых соединены с входами первого и второго регистров, третьим входом видеосумматора и выходом второго блока сопряжения, второй вход которого соединен с выходом пятого

регистра, четвертым входом видеосум- 50 третьим входом четвертого,коммута- матора, входом формирователя адреса тора.

1

12

и первым входом первого коммутатора, второй вход которого соединен с первым входом второго коммутатора и с выходом блока дешифрации признака наличия символа в данной точке экрана, первый вход которого соединен с выходом третьего регистра, второй вход которого соединен с вторым входом

I

блока дешифрации признака наличия

символа в данной точке экрана и

5

0

0

другим входом третьего счетчика,выход которого соединен с третьим входом первого коммутатора, выход которого соединен с адресной шиной блока памяти, выход четвертого регистра соединен с вторым входом второго коммутатора, выход которого соединен с четвертым входом первого коммутатора, пятый вход которого соединен с внешней адресной шиной, третий вход блока дешифрации признака наличия символа в данной точке экрана соединен с первым входом второго счетчика. 2. Процессор ПОП.1, отличающийся тем, что блок дешифрации признака наличия символа в данной точке экрана содержит дешифратор,четвертый счетчик, шестой регистр и первый и второй элементы 2И-ИЛИ, седьмой регистр и третий коммутатор, выход которого соединен с входом четвертого счетчика, выход которого соединен с

вторым входом третьего коммутатора и входом шестого регистра, выход кото- 35 рого соединен с входом дешифратора, выход которого соединен с вторым входом второго элемента 2И-ИЛИ.

3. Процессор по п. 1, отли- 40 чающийся тем, что видеосумматор содержит седьмой, восьмой и девятый регистры, регистр сдвига и четвертый коммутатор, входы которого соединены с выходами седьмого и 45 восьмого регистров, вход восьмого регистра соединен с входом девятого регистра, выход которого соединен с входом регистра сдвига, последовательный выход которого соединен с

Составитель И, Немнровский р„,„„„„„к Техред Л.Олейник Корректор rjj ej ejj««

Редактор А. Ворович

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий . ,,. 113035, Москва, Ж-35, Раушская мае., д.

1;;;:;о;;;в:;;;;-п;;:и;р;;й;:;к;Гпр:дпрй;;й;;: Гужгород, ул. проектная,

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275520A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1985 |

|

SU1280438A1 |

| Устройство для отображения и редактирования информации на экране электронно-лучевой трубки | 1989 |

|

SU1695288A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

Изобретение относится к вычислительной технике, а именно к информационно-обучающим устройствам на базе микропроцессоров и микроЭВМ, и может быть использовано для отображения статической и динамической информации, в том числе алфавитно-цифровой, графической и произвольно-символьной. Цель изобретения - упрощение процессора за счет уменьшения объема блока памяти - достигается введением двух коммутаторов 17 и 31, блока 15 дешифрации признака наличия символа в данной точке экрана, трех регистров 16, 25 и 26 с соответствующими функциональными связями. При использовании процессора существенно сокращается количество обращений к памяти, что, естественно, повышает информационную надежность системы в целом, особенно при малом количестве требуемых объектов на экране, 2з.п.ф-лы 4 ил. (О

| Соловейчик И.Е | |||

| Дисплей в системах с ЭВМ | |||

| М.: Советское радио, 1979 | |||

| Патент США № 4169262,кл.340/744, опублик | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1987-02-23—Публикация

1981-11-04—Подача