адресным входом - с третьим выходом блока регистров активного подканала информационным входом блока коммутации сигналов управления обменом и вторым входом блока дешифрации функциональней переходов, второй и третий выходы которого подключены соответственно к первому и второму информационным входам регистра масо а третий вход - к третьему информационному входу регистра масок и выходу блока коммутации сигналов управления обменом, адресный вход которого соединен с четвертым входом блока дешифрации функциональных переходов, вторым входом блока регистров активного подканала и выходом блока формирования состояни обмена, второй и третий входы которого соединены соответственно с первым информационным входом блока коммутации данных и первым выходом арифме1ико-логического блока и с четвертыг-1 выходом блока регистров активного подканала, третьим входом подключенного к второму выходу блока памяти микропрограммы и первому входу блока регистров информации, второй вход которого соединен с выходом регистра масок, третий вход с выходом блока, коммутации данных, а второй выход и четвертый вход, соответственно с третьим входом и первым выходом блока сопряжения с

7613

оперативной памятью, второй выход которого подключен к второму информационному входу блока коммутации данных, третий информационный вход которого соединен с третьим входом блока мультиплексной памяти и вторым выходом блока регистров информации, а четвертый информационный вход - с выходом блока мультиплексной памяти.

2, Канал non.l, отличающийся тем, что блок формирования состояния обмена содержит счетчик байтов буфера, триггер, элемент сравнения, элемент И-НЕ и элемент НЕ, причем выходы счетчика байтов буфера и триггера образуют выход блока, информационные входы счетчика байтов буфера и триггера и первый вход элемента сравнения образуют второй вход блока, первый вход элемента И-НЕ соединен с выходом элемента сравнения, а .выход - с установочным входом триггера, синхровход которого через элемент НЕ подключен к разрешающему входу счетчика байтов буфера, второй вход элемента сравнения является третьим входом блока, второй вход элемента И-НЕ, синхровход, вход сброса и разрешаю1п;ий вход счетчика буйтов буфера и вход сброса триггера образуют перБЬ й вход блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

1. МУЛЬТИПЛЕКСНЫЙ КАНАЛ, содержащий блок сопряжения с оперативной памятью, группа входов и выходов которого является группой входов и выходов связи с оперативной памятью канала, а первый вход подключен к первому выходу блока памяти микропрограмм, второй выход которого соединен с первыми входами арифметико-логического блока, блока мультиплексной памяти и блока сопряжения с интерфейсом ввода-вывода, первым выходом подключенного к первому входу блока сопряжения с центральным процессором, вторым, входом и выходом - соответственно к входу и выходу связи с внешним устройством канала, а третьим входом - к первому входу блока регистров активного подканала, второму входу блока сопряжения с центральным процео сором и первому выходу арифметико-логического блока, второй вход которого соединен с первыми выходами блока регистров информации, блока регистров активного подканала, третьим входом блока сопряжения с интерфей- , сом ввода-вывода и первым выходом блока сопряжения с центральным процес сором, второй выход и третий вход которого являются соответственно выходом и входом связи с центральным процессором канала, второй вход блока мультиплексной памяти соединен с вторым выходом блока регистров активного подканала, второй выход apифмeтliкo-лoгичecкoгo блока подключен к первому адресному входу бло ка памяти микропрограмм, вторым адресным входом и третьим выходом соединенного соответственно с первыми выходом и входом блока дешифрации функциональных переходов, второй выход которого подключен к управляю(П щему входу блока коммутации сигналов управления обменом, отличающийся тем, что, с целью повышения быстродействия канала, в него введены блок коммутации данных, регистр масок и блок формирования состояния обмена, причем адресный вход блока коммутащ и даноь ных, управляющий вход регистра масок и первый вход блока формировао: ния состояния обмена соединены соот, ветственно с четвертым, пятым и оэ шестым выходами блока памяти микропрограмм, третьим адресным входом и седьмым выходом подключенного соответственно к третьему выходу и четвертому входу блока сопряжения с центральньгм процессором, четвертым адресным входом - с четвертым выходом блока сопряжения с интерфейсом ввода-вывода, восьмым выходом - с вторым входом арифметико-логического блока и вторым входом блока сопряжения с оперативной памятью, а пятым

Нзооретение относится к вычислительной технике, в частности к органи.зации мультиплексных каналов микропрограммньк вычислительных« машин, и может быть использовано для управления обменом информацией между внешними устройствами (ВУ) и процессором.

Известны мультиплексные каналы MJiKpoiiporpaMMHbDC вычислительных машин, содержащие блок памяти микропрограмм, арифметико-логическое устройство, мультиплексную память, блок сопряжения с оперативной памятью, блок сопряжения- с центральHbif-i 1гроцессором, соединенные между собой, с оперативной памятью и центральным процессором системой информационных управляющих шин. Известные каналы при работе в мультиплексном режиме, выполняя обмен информацией между- ВУ и оперативной памятью, считывают для каждого устройства управляющзто информацию операции ввода-вывода из мультиплексной памяти, выполняют обмен информацией между БУ и оперативной памятью, затем запоминают измененную управляющую информацию в мультиплексной памяти 1 .

Недостатками этих каналов являются низкая пропускная способность и производительность вычислительной системы, обусловленные большими затратами времени на выполнение мик программ обслуживания. Наиболее близким к изобретению является мультиплексный канал, содержащий блок памяти микропрограмм, блок процессора, блок оперативной памяти, арифметико-логический блок, блок сопряжения с интерфейсом, блок мультиплексной памяти, блок регистр активного подканала, включающий регистр текущего адреса и регистр последующего адреса, блок дешифрации команд, блок формирования начал ных адресов с триггером загрузки регистров, блок сравнения адресов и блок регистров, причем выходы бло ков оперативной и мультиплексной памяти, блока сопряжения с интерфей сом, блока регистров и блока памяти микропрограмм соединены с соответст вующими входами арифметико-логического блока, выходы которого подключены к первым входам блока регистро блока сопряжения с интерфейсом, бло ка регистров активного подканала и блока мультиплексной памяти, вторые вход и выход которого подключен соответственно к первым выходу и входу блока дешифрации команд, груп па входов и третий выход - к группе выходов и первому входу блока формирования начальных адресов, а четвертый выход - к первым входам блоков мультиплексной и оперативной па мяти, выходы дешифратора команд сое динены с соответствующими входами блока регистров, блока регистров активного подканала, блока сопряжения с интерфейсом, через триггер загрузки регистров с входом блока формирования начальных адресов, входы которого соединены с соответствую1цими выходами блока сопряжения с интерфейсом, н через блок сравнения адресов с выходом блока регистров активного подканала 21. Недостаток этого канала состоит в низком быстродействии. Цель изобретения - повышение быс родействия мультиплексного канала. Поставленная цель достигается тем, что в мультиплексный канал, содержащий блок сопряжения .с оперативной памятью, группа входов и выходов которого является группой входов и выходов связи с оперативной памятью канала, а первый вход подключен к первому выходу блока. 34 памяти микроп1э.ограмм, второй выход которого соединен с первыми входа- . ми арифметико-логического блока, блока мультиплексной памяти и блока сопряжения с интерфейсом вводавывода первым выходом подключенного к первому входу блока сопряжения.с центральным процессором, вторыми входом и выходом - COOT- . ветственно к входу и выходу связи с внешним устройством канала, а третьим входом - к первому входу блока регистров активного подканала, второму входу блока сопряжения с центральным процессором и первому выходу арифметико-логического блока, второй вход которого соединен с первыми выходами блока регистров информации, блока регистров активного подканала, третьим выходом блока сопряжения с интерфейсом вводавывода и первьм выходом блока сопряжения с центральным процессором, второй выход и третий вход которого являются соответственно выходом и входом связи с центральным процессором канала, второй вход блока мультиплексной памяти соединен с вторым выходом блока регистров активного подканала, второй выход арифметико-логического блока подключен к первому адресному входу блока памяти микропрограмм,вторым адресным входом и третьим выходом соединенного соответственно с первыми выходом и входом блока дешифрации функциональных переходов второй выход которого подключен к управляющему входу блока коммутации сигналов управления обменом, введены блок коммутации данных, регистр масок и блок формирования состояния обмена, причем адресный вход блока коммутации данных, управляющий вход регистра масок и первый вход блока формирования состояния обмена соединенъ соответственно с четвертым, пятым и шестым выходами блока памяти микропрограмм, третьим адресным входом и седьмьм выходом подключенного Соответственно к третьему выходу и четвертому входу блока сопряжения с центральным процессором, четвертым адресным входом - с четвертым выходом блока сопряжения с интерфейсом ввода-вывода, восьмым выходо - с вторым входом арифметикологического блока и вторым входом

блока сопряжения с оперативной памятью, а пятым адресным входом с третьим выходом блока регистров активного подканала, информационным входом блока коммутации сигналов управления обменом и вторым входом блока дешифрагдии функциональных переходов, второй и третий выходы которого подключены соответственно к первому и второму информационны входам регистра масок, а третий вход к третьему информационному входу регистра масок и выходу блока коммутации сигналов управления обменом, адресный вход которого соединен с четвертым входом блока дешифрации функдиояальньпс переходов, вторым входом блока регистров активного подканала и выходом блока формирования состоя 1ия обмена, второй и третий входы которого соединены соответственно с, первым информационным входом блока коммутации данных и первым выходом арифметико-логического блока и с четвертым выходом блока регистров активного подканала, третьим входом подключенного к второму выходу блока памяти микропрограммы и первому входу блока регистров информации, второй вход которого соединен с выходом регистра масок, третий вход - с выходом блока коммутации данных, а второй выход и четвертый вход - соответственно с третьим входом и первым выходом блока сопряжения с оперативной памятью, второй выход которого подключен к второму информационному входу блока коммутации данньгх:, третий информационньтй вход которого соединен с третьим входом блока мультиплексной памяти и вторым выходом блока регистров информации, а четвертый информационный вход - с выходом блока-кгультиплексной памяти.

Блок формирования состояния обмена содержит счетчик байтов буфера, триггер, элемент сравнения, элемент И-НЕ и элемент НЕ, причем выходы счетчика байтов буфера и триггера образуют выход блока, информационные входы счетчика байтов буфера и триггера и первый вход элемента сравнения образуют второй вход блока, первый вход элемента И-НЕ соединен с выходом элемента сравнения,а выходс установочным входом триггера, синхровход которого через элемент

НЕ подключен к разрешающему входу счетчика байтов буфера, второй вход элемента сравнения является третьим входом блока, второй вход элемента И-НЕ, синхровход, вход сброса и разрешающий вход счетчика байтов буфера и вход сброса триггера образуют первый вход блока.

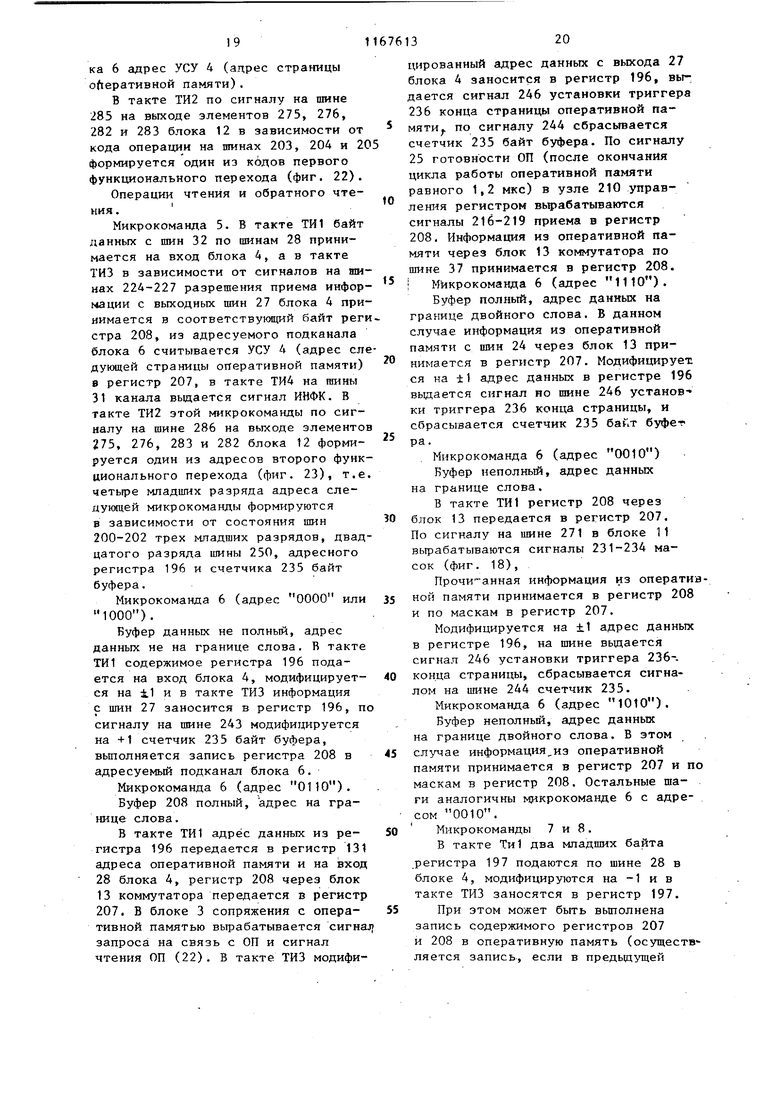

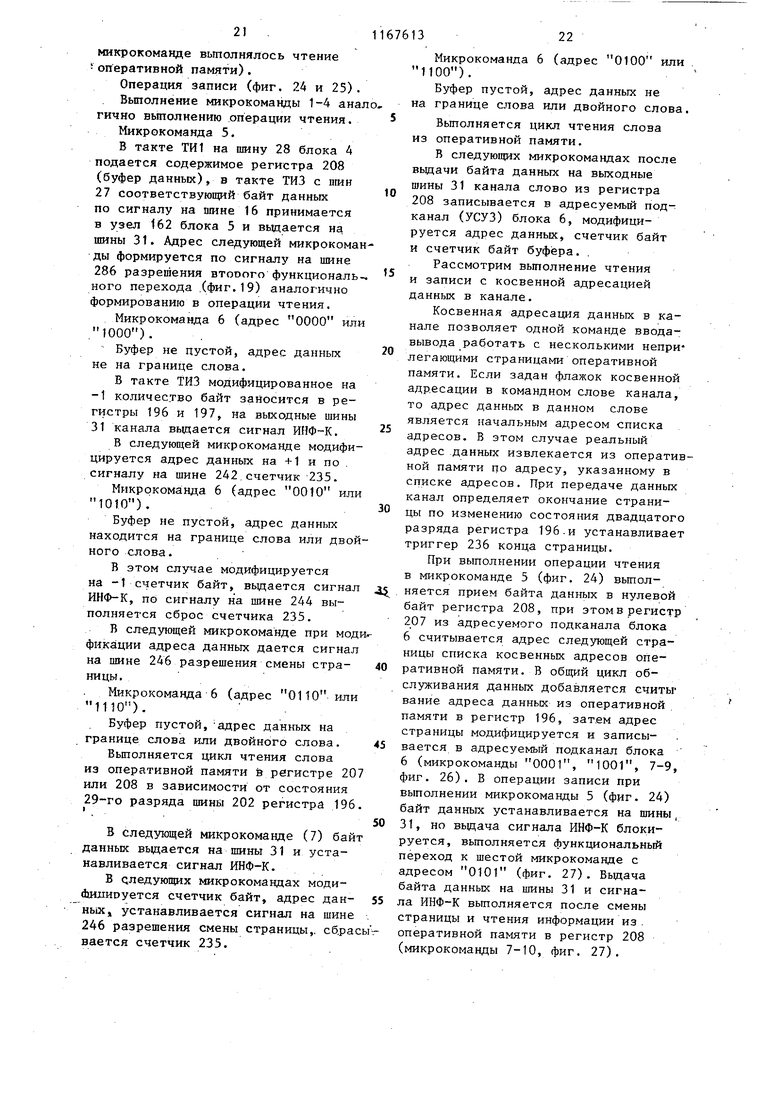

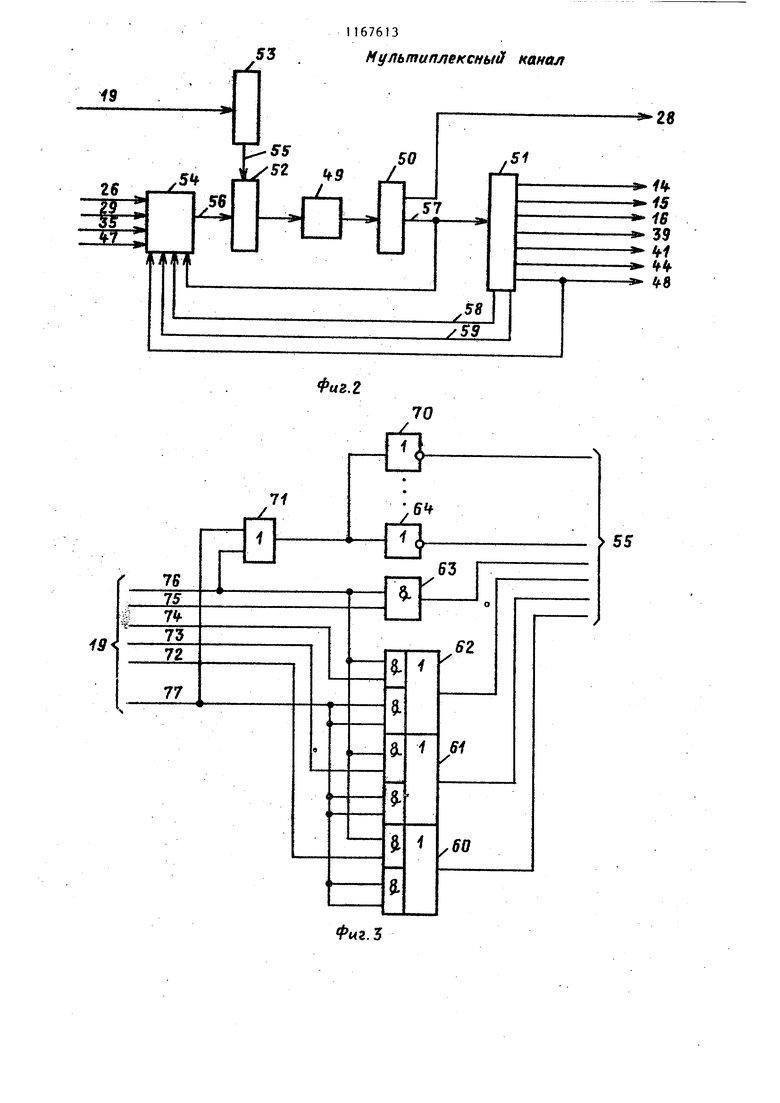

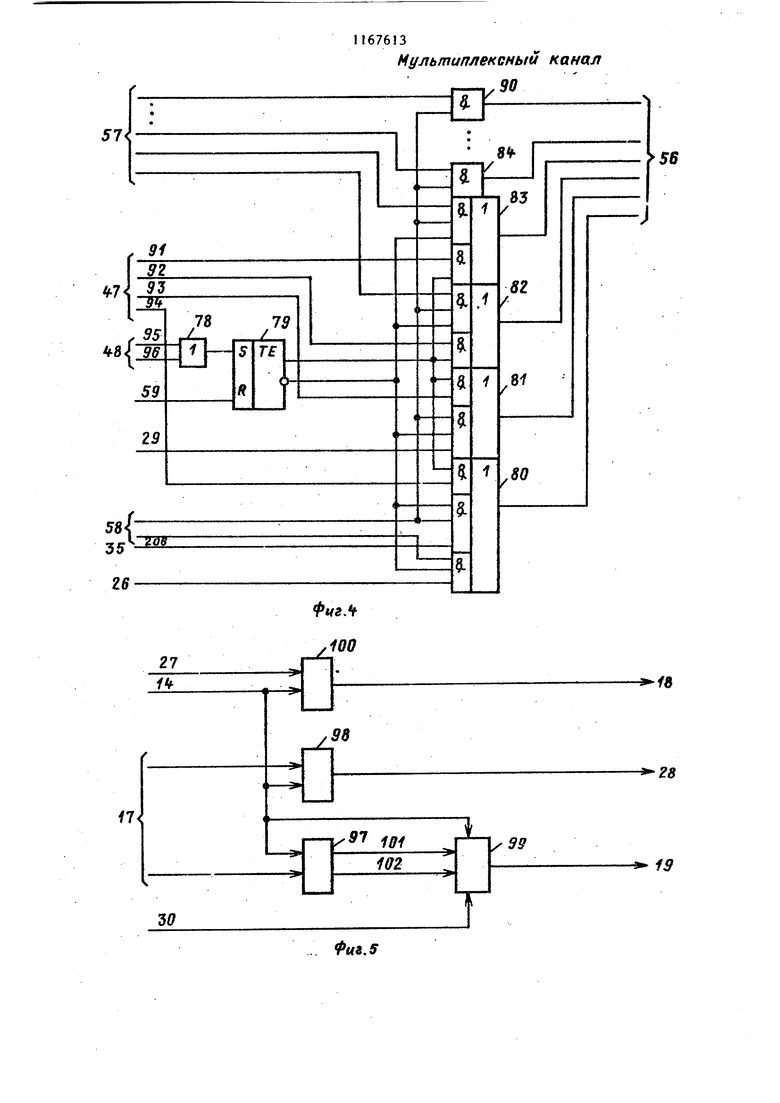

На фиг. 1 представлена блок-схема предлагаемого мультиплексного канала J на фиг. 2 - схема блока памяти микропрограмм) на фиг. 3 - схема узла формирования фиксированного

адреса микрокоманды-, на фиг. 4 схема узла формирования адреса следующей микрокоманды; на фиг. 5 схема блока сопряжения с центральным процессором; на фиг. 6 - схема узла

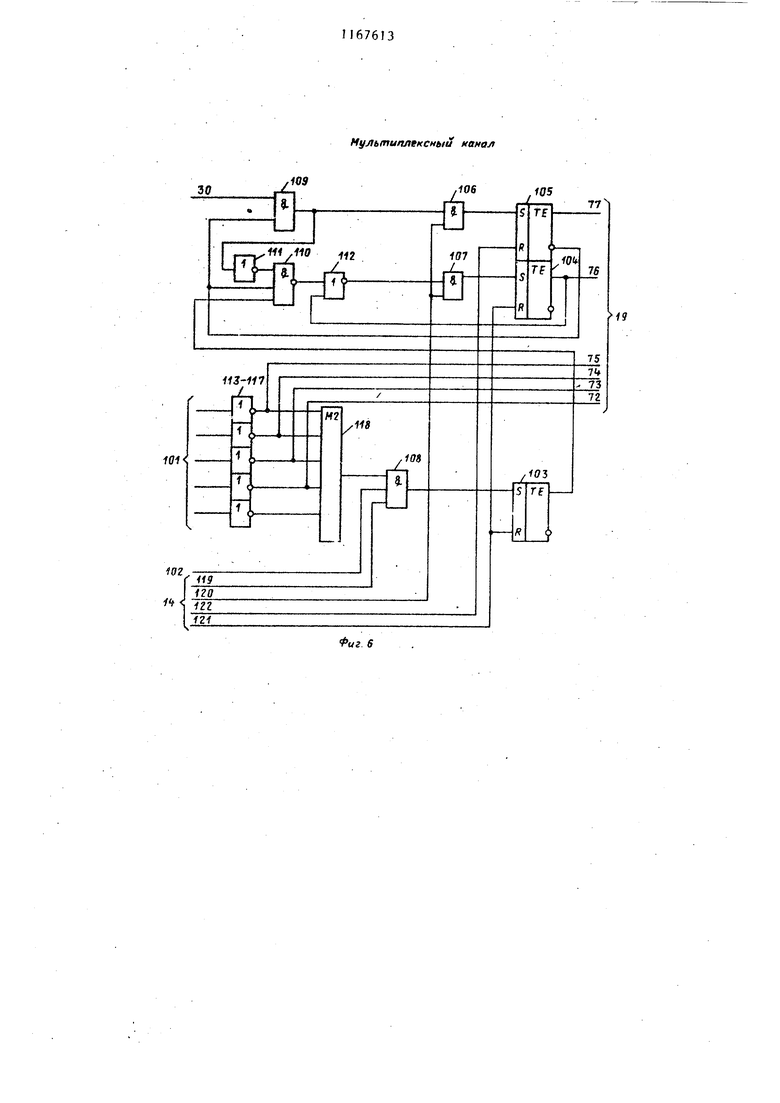

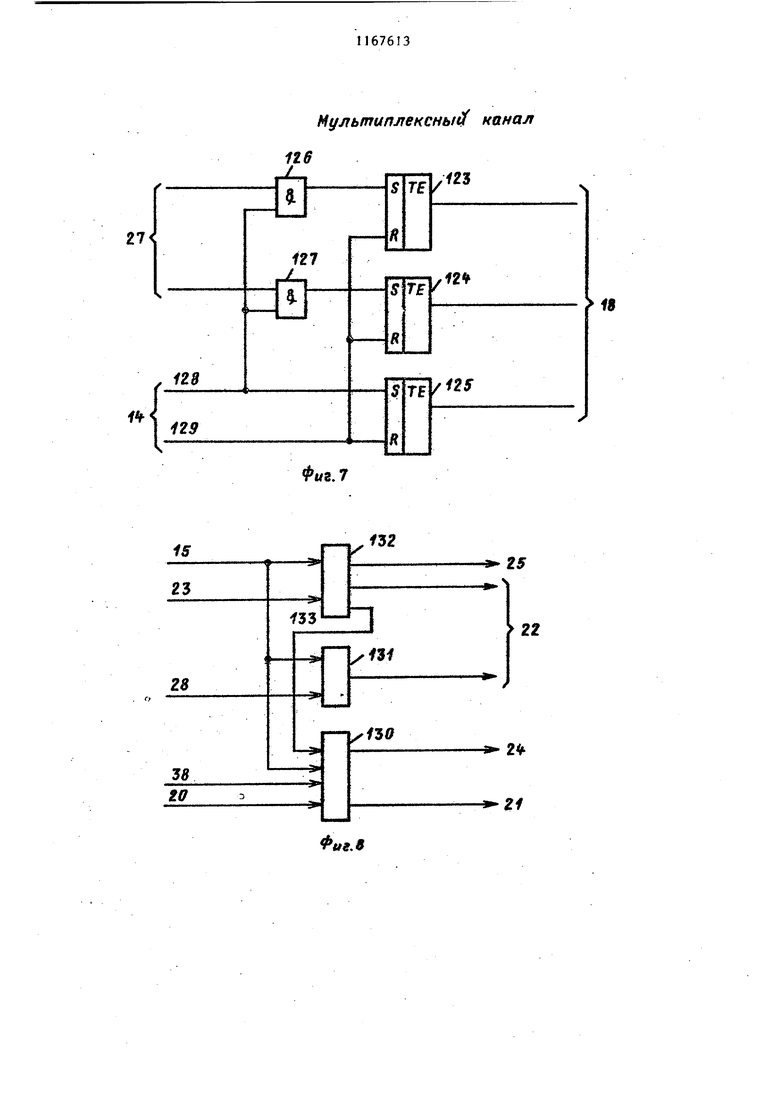

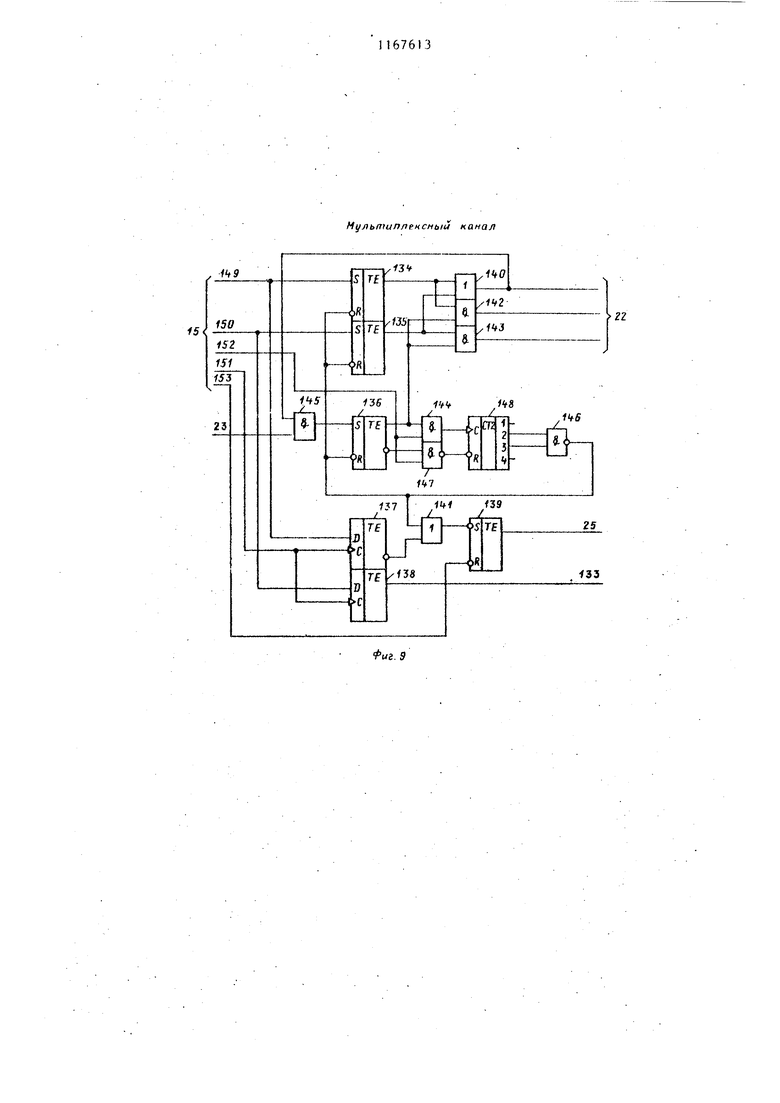

формирования запросов; на фиг. 7 схема узла окончания операции ввода-вырода; на фиг. 8 - схема блока сопряжения с оперативной памятью; на фиг. 9 - схема узла цикла

работы оперативной памяти; на

фиг. 10 - схема арифметико-логического блока , на фиг. 1 1 - схема блока сопряжения с интерфейсом ввода-вывода; на фиг. 12 - схема блока

мультиплексной памяти-, на фиг. 13 схема блока регистров активного подканала; на фиг, 14 - схема блока регистров информации; нафиг. 15 схема узла управления регистром;

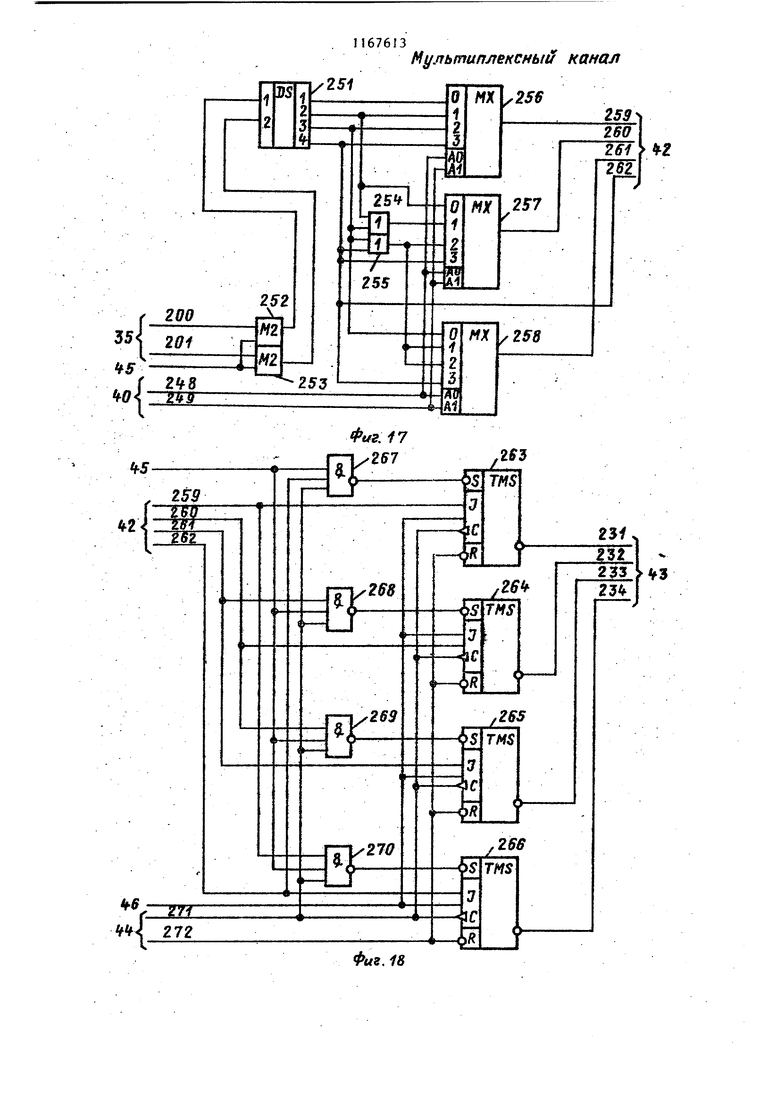

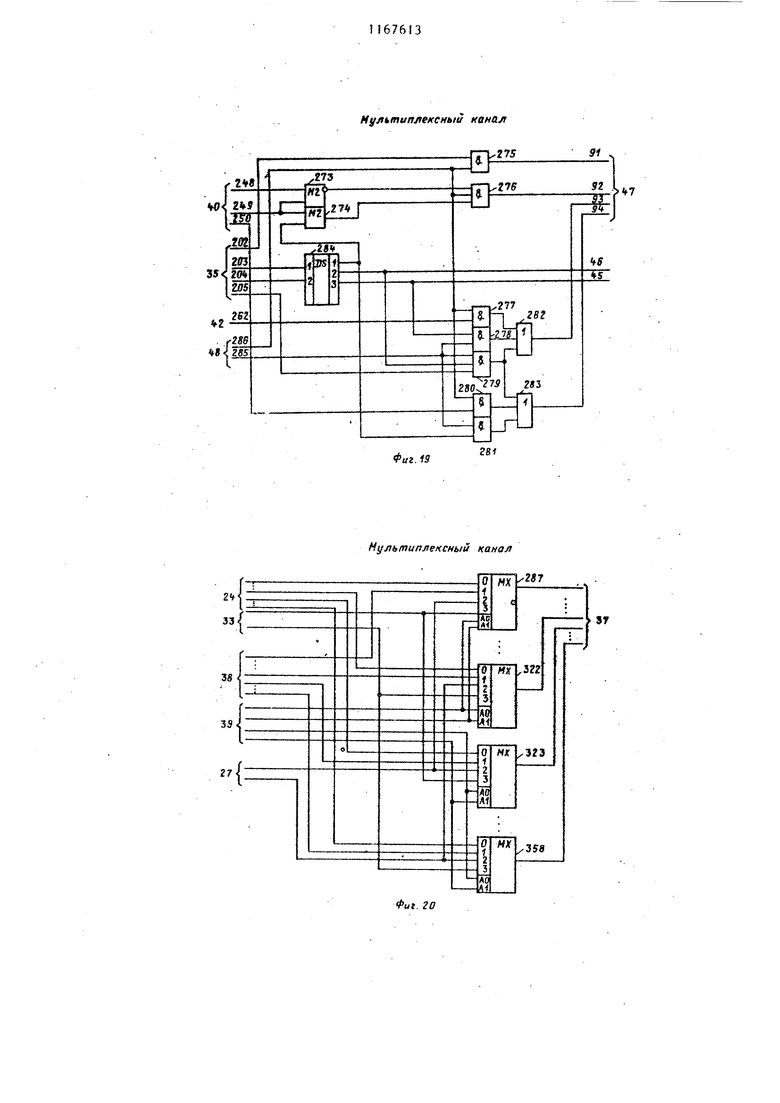

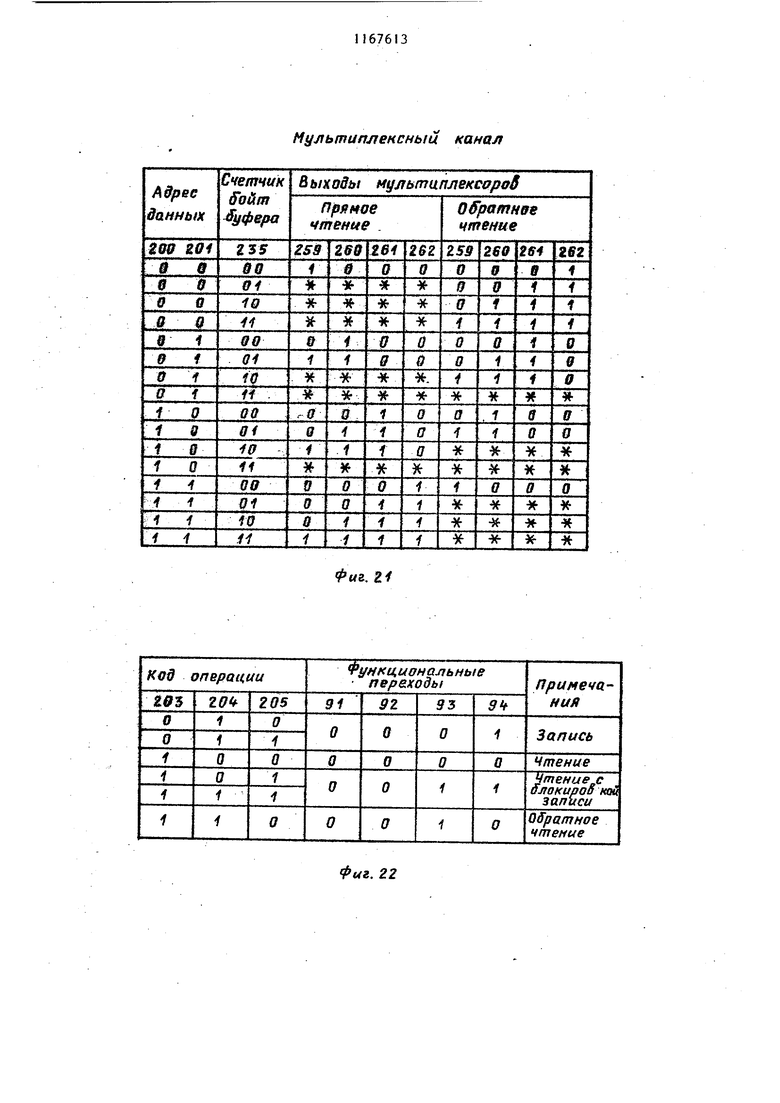

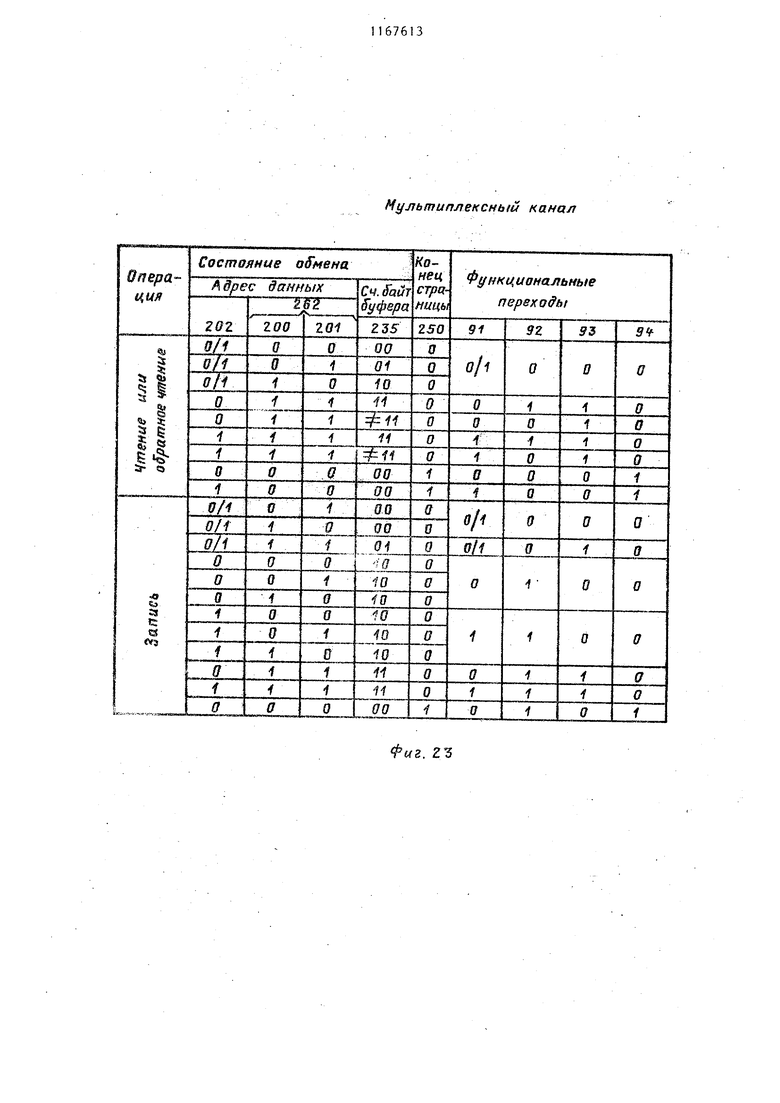

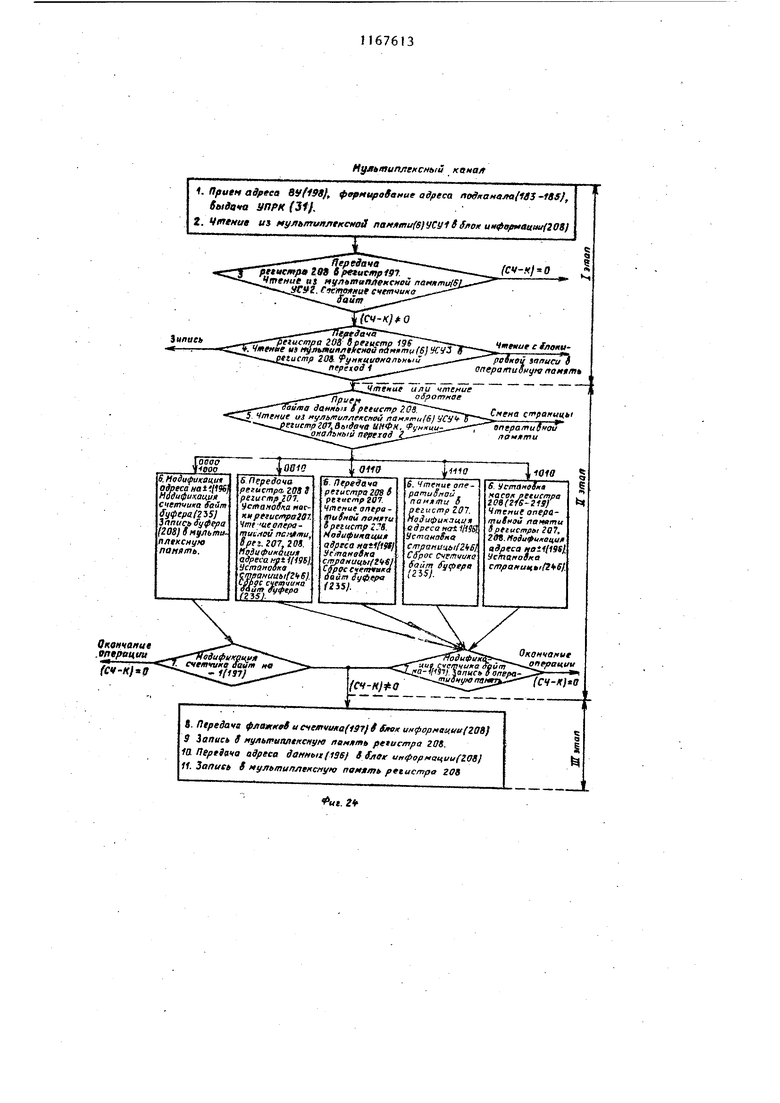

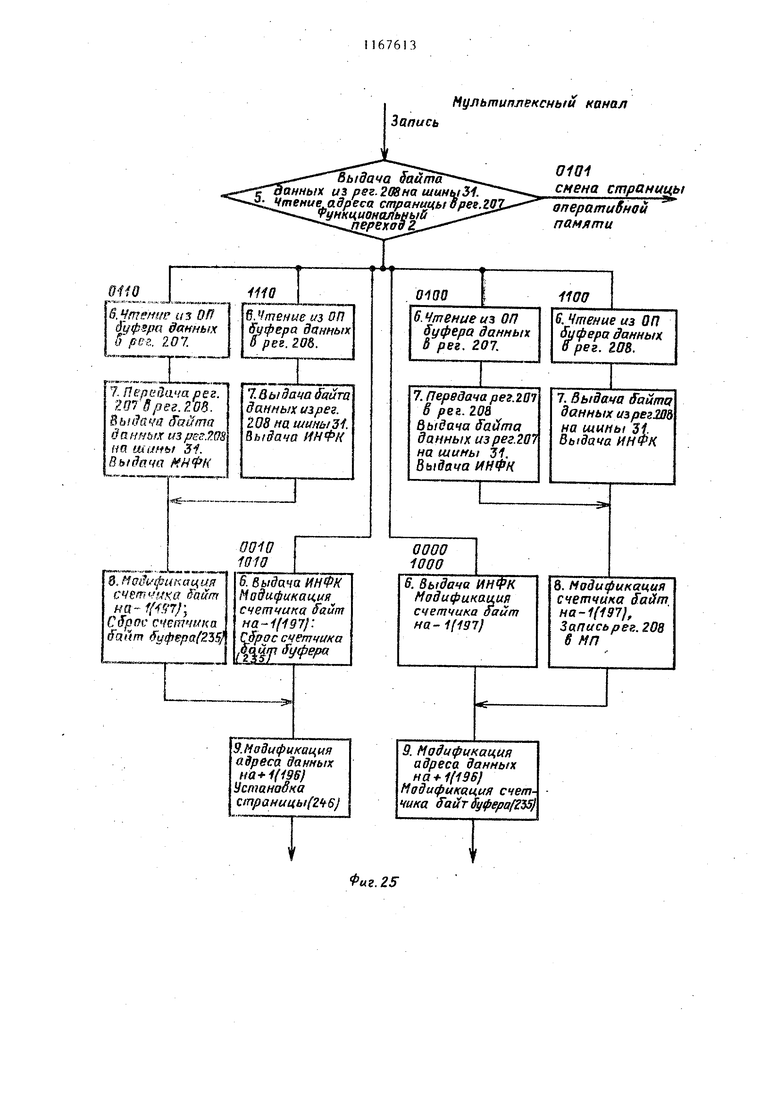

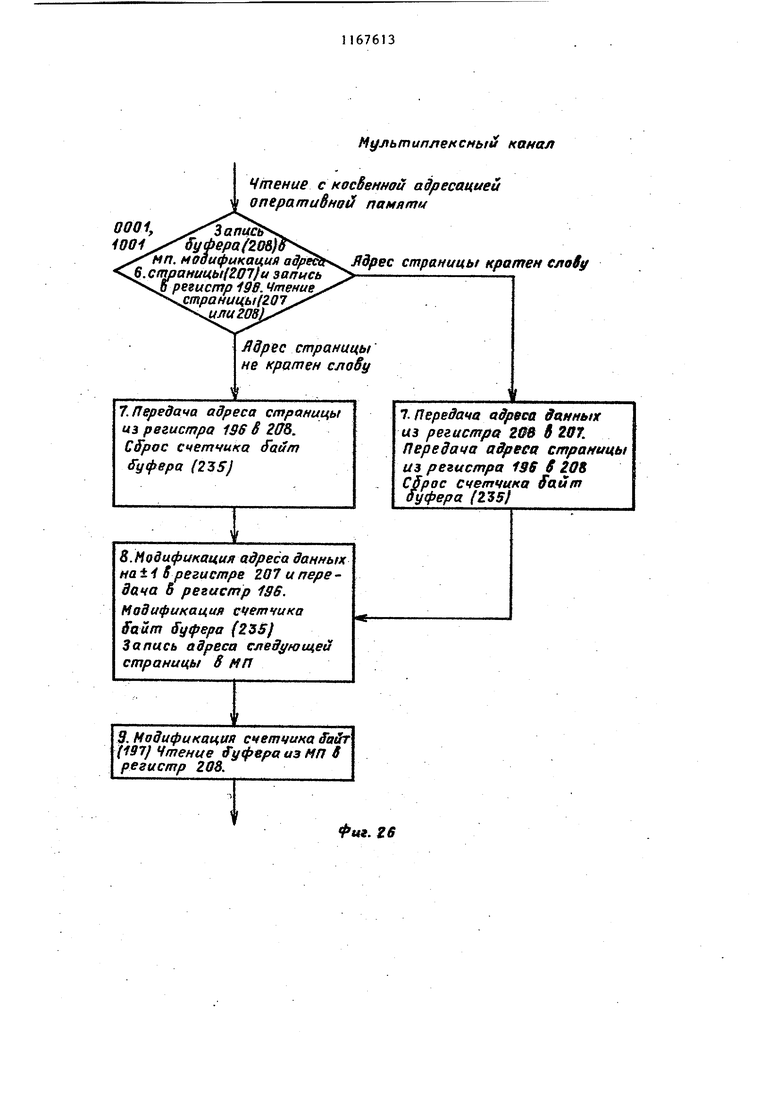

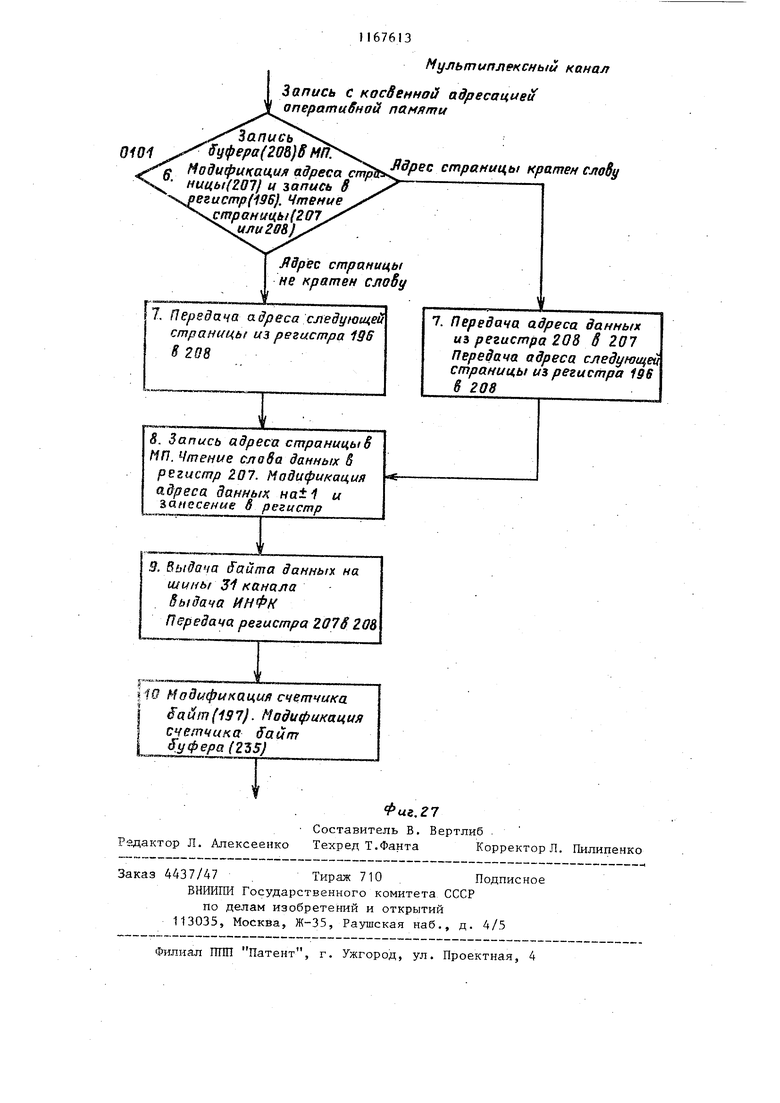

па фиг. 16 - схема блока формирования состояния обмена; на фиг. 17 схема блока коммутации сигналов управления обменом; на фиг. 18 схема регистра масок на фиг. 19 схема блока дешифрации функционального перехода; на фиг. 20 схема блока коммутации данных-, на фиг. 21 - таблица формирования управляющих сигналов блока коммутацни сигналов управления обменом , на фиг. 22 и 23 - таблицы формирования первого и второго функциональных переходов в блоке дешифрации функциональных переходов; на фиг. 24 алгоритм выполненияоперации чтения в мультиплексном режиме работы канала на фиг. 25 - алгоритм выполнения операции записи;-на фиг. 26 алгоритм выполнения операции чтения

с косвенной адресацией данных; на фиг. 27 - алгоритм выполнения операции записи с косвенной адресацией данных.

71

Мультиплексный канал (фиг. 1) содержит блок 1 памяти микропрограм блок 2 сопряжения с центральным процессором, блок 3 сопряжения с оперативной памятью, арифметико-логический блок 4, блок 5 сопряжения с интерфейсом ввода-вывода, блок 6 мультиплексной памяти, блок 7 регистров активного подканала, блок 8 регистров информации, блок 9 формирования состояния обмена, блок 10 коммутации сигналов управления обменом, регистр 11 масок, блок 12 дешифрации функциональных переходов, блок 13 коммутации данных. Блок 1 памяти микропрограмм обеспечивает автоматическое функционирование мультиплексного канала в соответствии с заданными микрокомандами. Шинами 14 и 15 седьмого и первого выходов блок 1 соединен соответственно с блоками 2 и 3, шинами 16 второго выхода - с блоками 4-8.

Блок 2 сопряжения с центральным процессором обеспечивает загрузку по шинам 17 входа связи с центральным процессором канала управляющей информации (кода команды ввода-вывода, адреса внешнего устройства) в канал. Шинами 18 выхода связи с цен тральным процессором блок 2 соедине с центральным процессором, шинами третьего выхода - с блоком 1 памяти микропрограмм.

Блок 3 сопряжения с оперативной памятью предназначен для управления обменом информацией между оперативной памятью и каналом. С оперативной памятью блок соединен информационными шинами 20-23 группы входов и выходов связи с оперативной памятью канала, причем по шинам 20 поступают командные слова канала и данные, по шинам 21 - данные и состояние канала. По шинам 22 из блока 3 в оперативную память поступают адрес, ключ защиты и признаки чтения или записи. По шинам 23 в блок 3 поступают признаки режима работы оперативной памяти. Шинами24 второго выхода блок 3 соединен с блоком 13, шинами 25 первого выхода - с блоком 8.

Арифметико-логический блок 4 предназначен для одновременной обработки трех, двух или одного байта ин- формации. Шиной 26-второго выхода блок 4 соединен с блоком 1, шинами

38

27 первого выхода - с блоками2,5,7, 9, 13, шинами 28 второго входа - с блоками 1-3, 5, 7, 8.

Блок 5 сопряжения с интерфейсом ввода-вывода управляет начальной выборкой внешнего устройства, обменом данными и байтами состояния между каналом и внешним устройством Шинами 29 и 30 четвертого и первого выходов блок 5 соединен соотве-: ствено с блоком 1 памяти микропрограмм блоком 2 сопряжения с центральным процессором,, шинами 31 и 32 вторых вькода и входа - с выходом связи с внешним устройством канала.

Блок 6 мультиплексной памяти содержит всю управляющую информацию о запущенных в канале операциях ввода-вывода. Шинами 33 выхода блок 6 соединен с блоком 13, шинами ЗА второго входа - с блоком 7.

Блок 7 регистров активного подканала хранит на время вьшолнения операции ввода-вывода на адресуемом устройстве информацию: адрес данных адрес командного слова канала, ключ защиты, код операции, флажки и счетчик байт. Соединен блок шинами 35 и 36 третьего и четвертого выходов с блоками 1, 10 12 и 9.

Блок 8 регистров информации хранит рабочую информацию канала во Bgeмя выполнения микропрограмм. Загружается блок по шинам 37 третьего входа с блока 13 коммутации. Шинами 38 выхода блок 8 соединен с блоками 3, 6 и блоком 13, соединенньм шинами 39 адресного входа с блоком 1.

Блок 9 форм фования состояния обмена хранит число-байт в буфере и флажок конца страницы (страница 2048 байт) оперативной памяти. Шинами 40 выхода блок 9 соединен с блоками 7, 10 и 12, шинами 41 первого входа - с блоком 1 памяти микропрограмм.

Блок 10 коммутации сигналов управления обменом формирует прт1знаки блокировки приема информации из оперативной памяти в регистры блока 8 в операциях чтения и чтения в обратном направлении. Блок 10 соединен шинами 42 выхода с блоками 11 и 12.

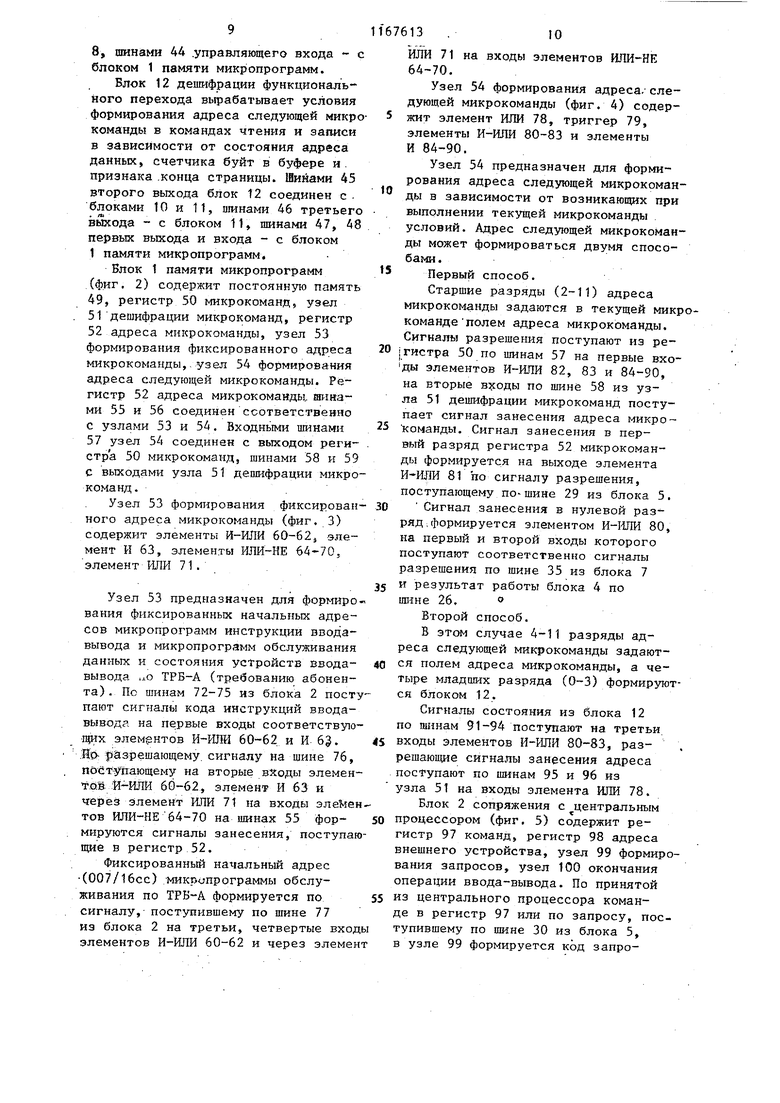

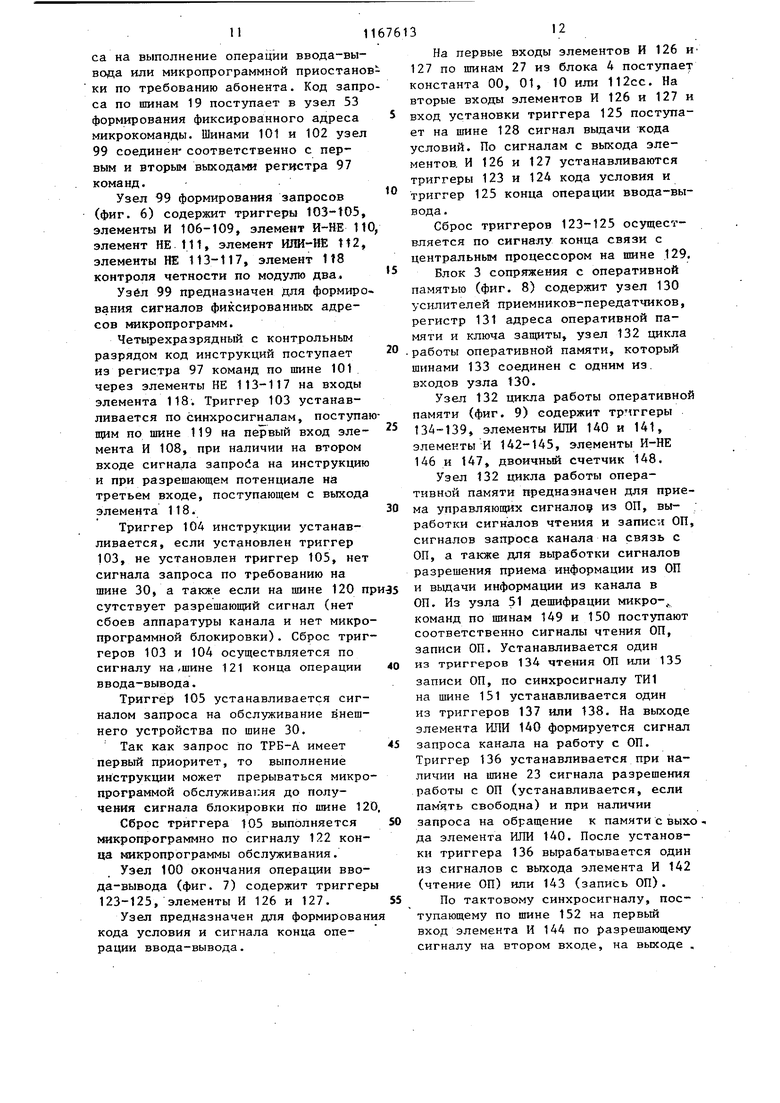

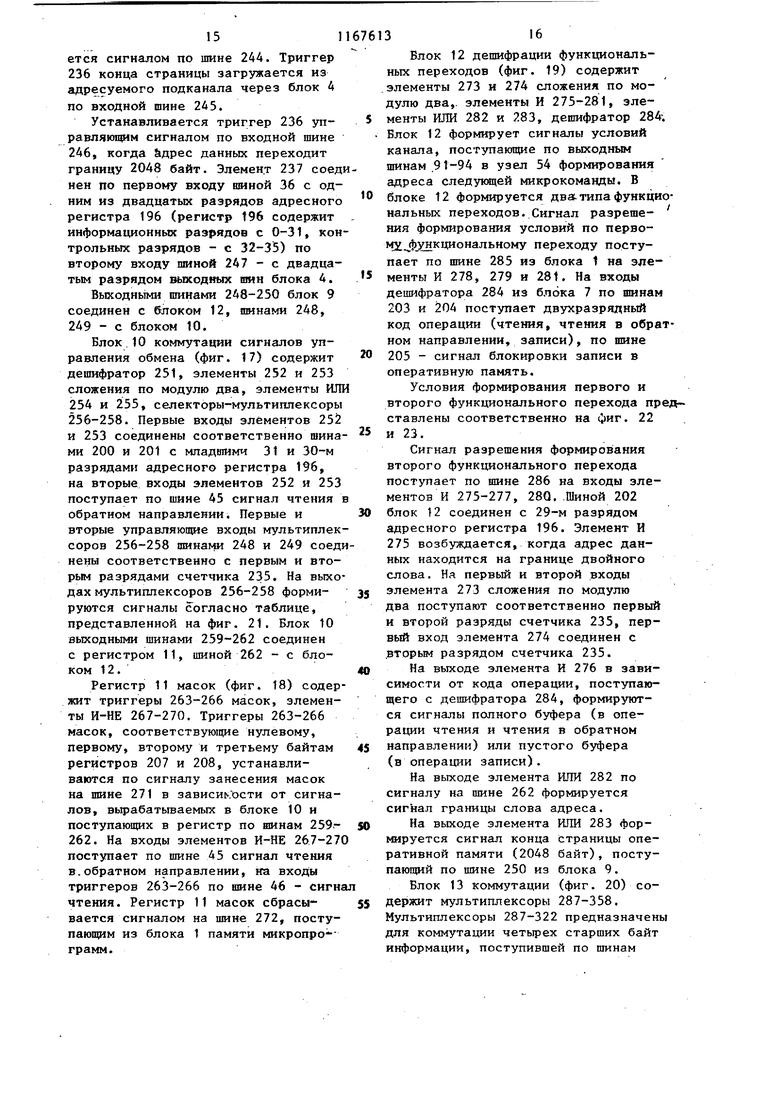

Регистр 11 масок хранит четырехразрядную маску слова оперативной памяти в операциях чтения и чтения в обоатном направлении. Регистр 11 Соединен шинами 43 выхода с блоком 8, шинами 44 .управляющего входа - с блоком 1 памяти микропрограмм. Блок 12 дешифрации функционального перехода вырабатьгеает условия формирования адреса следующей микро команды в командах чтения и записи в зависимости от состояния адреса данных, счетчика буйт в буфере и . признака .конца страницы. Шинами 45 второго выхода блок 12 соединен с блоками 10 и 11, шинами 46 третьего выхода - с блоком 11, шинами 47, 48 первых выхода и входа - с блоком 1 памяти микропрограмм. Блок 1 памяти микропрограмм (фиг, 2) содержит постоянную память 49, регистр 50 микрокоманд, узел 51 дешифрации микрокоманд, регистр 32 адреса микрокоманды, узел 53 формирования фиксированного адреса микрокоманды,.узел 54 формирования адреса следующей микрокоманды. Регистр 52 адреса микрокоманды, шиками 55 и 56 соединен ссответственно с узлами 53 и 54. Входными шинами 57 узел 54 соединен с выходом регистра 50 микрокоманд, шинами 58 и 59 С выходами узла 51 дешифрации микро команд.. Узел 53 формирования фиксирован ного адреса микрокоманды (фиг. 3) содержит элементы И-ИЛИ 60-б2з элемент И 63, элемен.ты ИЛИ-НЕ 64-70, элемент Ш1И 71, Узел 53 предназначен для формиро вания фиксированных начальных адресов микропрограмм инструкции вводавывода и микропрограмм обслуживания данных и состояния устройств вводавывода 1лО ТРБ-А (требованию абонента). По шинам 72-75 из блока 2 пост пают сигналы кода инструкций вводавывода на первые входы соответствую щих элементов И-ИЛЙ 60-62 и И 63. .ЩО: разрешающему, сигналу на шине 76, поетупающему на вторые входы элемен тов Й-ЙЛИ 60-62, элемент И 63 и через элемент ИЛИ 71 на входы элеМе тов ИЛИ-НЕ64-70 на шинах 55 формируются сигналы занесения, поступа щие в регистр 52. Фиксированный начальный адрес (007/16сс) микропрограммы обслуживания по ТРЬ-А формируется по сигналу, поступившему по шине 77 из блока 2 на третьи, четвертые вхо элементов И-ИЛИ 60-62 и через элеме ИЛИ 71 на входы элементов ИЛИ-НЕ 64-70. Узел 54 формирования адреса, следующей микрокоманды (фиг. 4) содержит элемент ИЛИ 78, триггер 79, элементы И-ИЛИ 80-83 и элементы И 84-90. Узел 54 предназначен для формирования адреса следующей микрокоманды в зависимости от возникающих при выполнении текущей микрокоманды условий. Адрес следующей микрокоманды может формироваться двумя способами. Первый способ. Старшие разряды (2-11) адреса микрокоманды задаются в текущей микрокоманде полем адреса микрокоманды. Сигналы разрешения поступают из ре гистра 50 по шинам 57 на первые входы элементов И-ИЛИ 82, 83 и 84-90, на вторые по шине 58 из узла 51 дешифрации микрокоманд поступает сигнал занесения адреса микро- команды. Сигнал занесения в первый разряд регистра 52 микрокоманды формируется на выходе элемента И-ИЛИ 81 по сигналу разрешения, поступающему по-шине 29 из блока 5. Сигнал занесения в нулевой разряд .формируется элементом И-11ПИ 80, на первый и второй входы которого поступают соответственно сигналы разрешения по шине 35 из блока 7 и результат работы блока 4 по шине 26. Второй способ. В этом случае 4-11 разряды адреса следующей микрокоманды задаются полем адреса микрокоманды, а четыре младших разряда (0-3) формируются блоком 12. Сигналы состояния из блока 12 по шинам 91-94 поступают на третьи входы элементов И-ИЛЙ 80-83, разрешающие сигналы занесения адреса поступают по шинам 95 и 96 из узла 51 на входы элемента ИЛИ 78. Блок 2 сопряжения с центральным процессором (фиг. 5) содержит регистр 97 команд, регистр 98 адреса внешнего устройства, узел 99 формирования запросов, узел 100 окончания операции ввода-вывода. По принятой из центрального процессора команде в регистр 97 или по запросу, поступившему по шине 30 из блока 5, в узле 99 формируется код запроса на выполнение операции ввода-вывода или микропрограммной приостано ки по требованию абонента. Код запр са по шинам 19 поступает в узел 53 формирования фиксированного адреса микрокоманды. Шинами 101 и 102 узел 99 соединен- соответственно с первым и вторым выходами регистра 97 команд. Узел 99 формирования запросов (фиг. 6) содержит триггеры , элементы И 106-109, элемент И-НЕ П элемент НЕ 111, элемент ИЛН-НЕ tt2, элементы НЕ 113-117, элемент П8 контроля четности по модулю два. Узел 99 предназначен для формиро вания сигналов фиксированных адресов микропрограмм. Четырехразрядный с контрольным разрядом код инструкций поступает из регистра 97 команд по шине 101 через элементы НЕ 113-117 на входы элемента 118. Триггер 103 устанавливается по синхросигналам, поступа щим по шине 119 на первый вход элемента И 108, при наличии на втором входе сигнала запроса на инструкцию и при разрешающем потенциале на третьем входе, поступающем с выхода элемента 118. Триггер 104 инструкции устанавливается, если установлен триггер 103, не установлен триггер 105, нет сигнала запроса по требованию на шине 30, а также если на шине 120 п сутствует разрешающий сигнал (нет сбоев аппаратуры канала и нет микро программной блокировки). Сброс триг геров 103 и 104 осуществляется по сигналу на ,шине 121 конца операции ввода-вывода. Триггер 105 устанавливается сигналом запроса на обслуживание внешнего устройства по шине 30. Так как запрос по ТРБ-А имеет первый приоритет, то выполнение инструкции может прерываться микро программой обслуживания до получения сигнала блокировки по шине 12 Сброс триггера 105 выполняется микропрограммно по сигналу 122 конца jeiKponpограммы обслуживания. Узел 100 окончания операции ввода-вывода (фиг. 7) содержит триггеры 123-125, элементы И 126 и 127. Узел предназначен для формировани кода условия и сигнала конца операции ввода-вывода. На первые входы элементов И 126 И 127 по шинам 27 из блока 4 поступает константа 00, 01, 10 или 112сс. На вторые входы элементов И 126 и 127 и вход установки триггера 125 поступает на шине 128 сигнал вьщачи кода условий. По сигналам с выхода элементов. И 126 и 127 устанавливаются триггеры 123 и 124 кода условия и триггер 125 конца операции ввода-вывода. Сброс триггеров 123-125 осуществляется по сигналу конца связи с центральным процессором на шине 129. Блок 3 сопряжения с оперативной памятью (фиг. 8) содержит узел 130 усилителей приемников-передатчиков, регистр 131 адреса оперативной памяти и ключа защиты, узел 132 цикла работы оперативной памяти, который шинами 133 соединен с одним из. входов узла 130. Узел 132 цикла работы оперативной памяти (фиг. 9) содержит тр ггеры 134-139, элементы Ш1И 140 и 141, элементы И 142-145, элементы И-НЕ 146 и 147, двоичный счетчик 148. Узел 132 цикла работы оперативной памяти предназначен для приема управляющих сигналов из СП, выработки сигналов чтения и записи СП, сигналов запроса канала на связь с СП, а также для выработки сигналов разрешения приема информации из СП и вьщачи информации из канала в ОП. Из узла 51 дешифрации микрокоманд по шинам 149 и 150 поступают соответственно сигналы чтения ОП, записи ОП. Устанавливается один из триггеров 134 чтения ОП или 135 записи ОП, по синхросигналу ТИ1 на шине 151 устанавливается один из триггеров 137 или 138. На выходе элемента ИЛИ 140 формируется сигнал запроса канала на работу с ОП. Триггер 136 устанавливается при наличии на шине 23 сигнала разрешения работы с ОП (устанавливается, если память свободна) и при наличии запроса на обращение к памяти с выхо да элемента ИЛИ 140. После установки триггера 136 вырабатывается один из сигналов с вьосода элемента И 142 (чтение ОП) или 143 (запись ОП). По тактовому синхросигналу, поступающему по шине 152 на первый вход элемента И 144 по разрешающему сигналу на втором входе, на выходе ,

элемента И 144 формируется сигнал запуска счетчика 148 тактов (цикл ОП 1,2 мкм).

При состоянии счетчика 148, равного 11/2сс, сбрасываются триггеры 134-136. При этом .с выхода элемента ИЛИ 141 при условии установки триггера 137 вырабатывается сигнал установки триггера 139. С.выхода тригге.ра 139 в блок 8 по шинам 25 поступает сигнал разрешения приема информации из ОП в канал. Сигнал разрешения вьздачи информации из канала в ОП поступает с выхода триггера 138. Сброс триггера 139 выполняется по концу связи с ОП по сигналу на пшие 153..

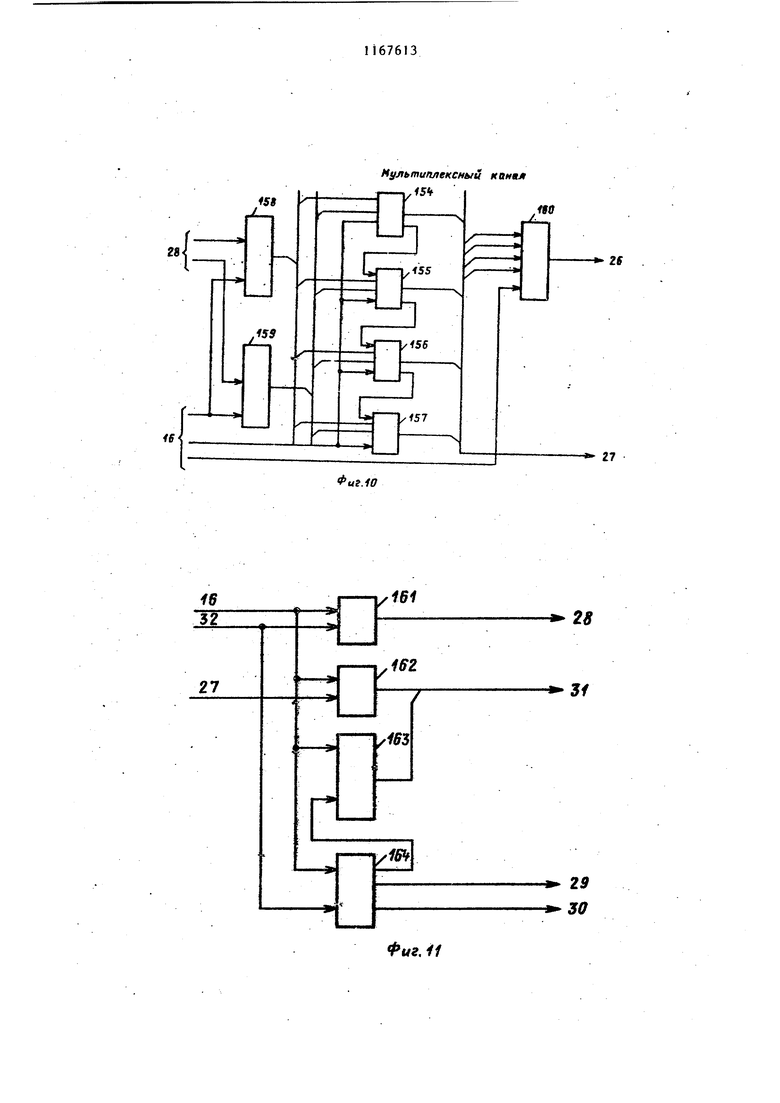

Арифметико-логический блок 4 (фиг. 10) содержит узел 154 сумматора третьего байта, узел 155 сумматора второго байта, узел 156 сумматора первого байта, узел 157 сумматора нулевого байта, регистр 158 первого входа сумматора, регистр 159 второго входа сумматора, коммутатор 160 результата.

Узлы 154-157 сумматоров являются идентичными ипредназначены для побайтной обработки информации, поступающей по шинам 28 на входы регистров 158 и 159.

Блок 5 сопряжения с интенфейсом ввода-вывода (фиг. 11) содержит регистр 161ВХОДНОЙ информации интерфейса, регистр 162 выходной информации интерфейса, регистр 163 управления выходными сигналами интерфейса, регистр 164 управления входными сигналами интерфейса. .

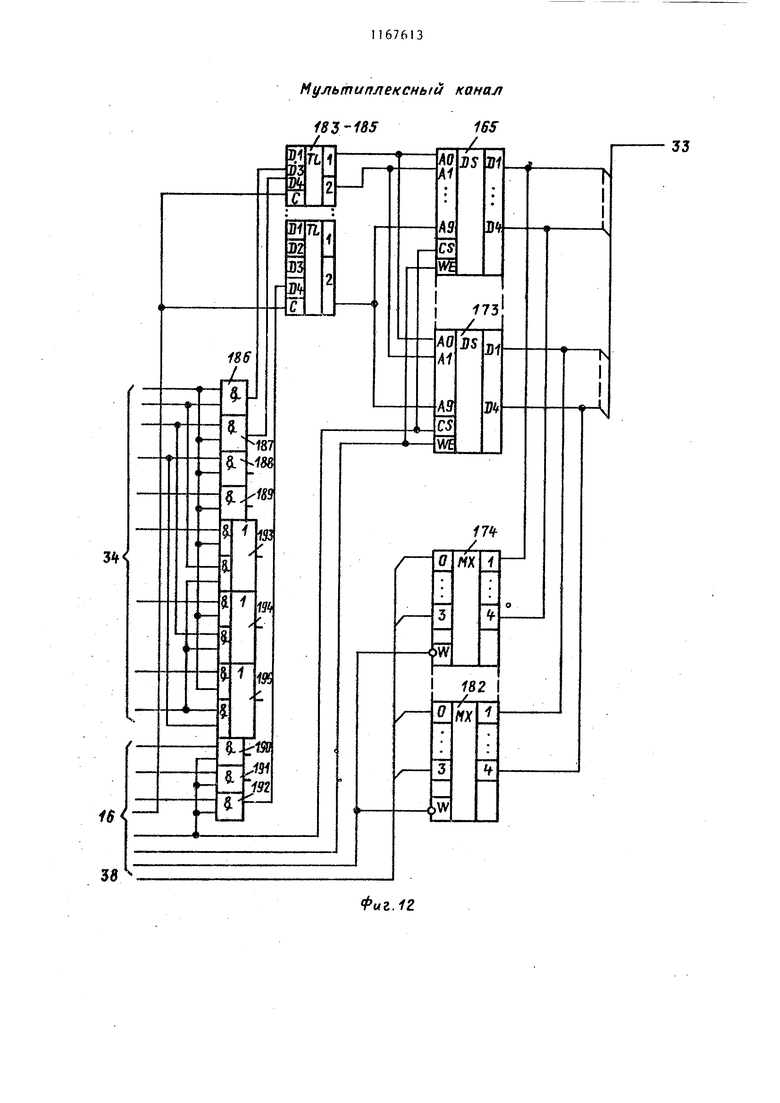

Блок 6 мультиплексной памяти (фиг, 12) содержит оперативные .запоминаюптие элементы 165-173 статического .типа емкостью, например, 4096. тт,, селекторы-мультиплексоры 174-182; триггеры 183-185, элементы И 186-192, элементы И-ИЛИ 193-195 На входы элементов 186-189, 193-195 по шинам 34 из блока 7 поступает адрес внешнего устройства,.по шинам 16 на первые входы элементов 190-192сигналы формирования адреса линейки мультиплексной памяти внутри одного подканала. Один .подканал содержит 8 четырехбайтньк линеек адресов памяти. Триггеры 183-185 адреса мультиплексной памяти по входу соединены с адресными входами элементов 165-173.

Информагщонные входы мультиплексоров 174-182 соединены с выходными шинами 38 блока 8. .

Блок 7 регистров активного подканала (фиг. 13) содержит четырехбайтный регистр 196 адреса и ключа защиты, четырехбайтный регистр 197 состояния канала и счетчика байт /однобайтный регистр 198 адреса внешнего устройства, узел 199 коммутации.

Блок 7 выходными шинами 200 и . . 201 соединен с блоком 10, шинами

202-205 - с блоком 12, шиной 206

5 восьмой разряд регистра 197 соединен с блоком 1. .

Блок 8 регистров .информации (фиг. 14) содержит четырехбайтные регистры 207 и 208 общего назначения, идентичные узла 209 и 210 , управления регистрами, узел 211 коммутации. Регистр 207 по входу соединен шинами .212-215. с выходами узла 209, регистр 208 шинами 216-

219 соединен с вьпсодами узла 210.

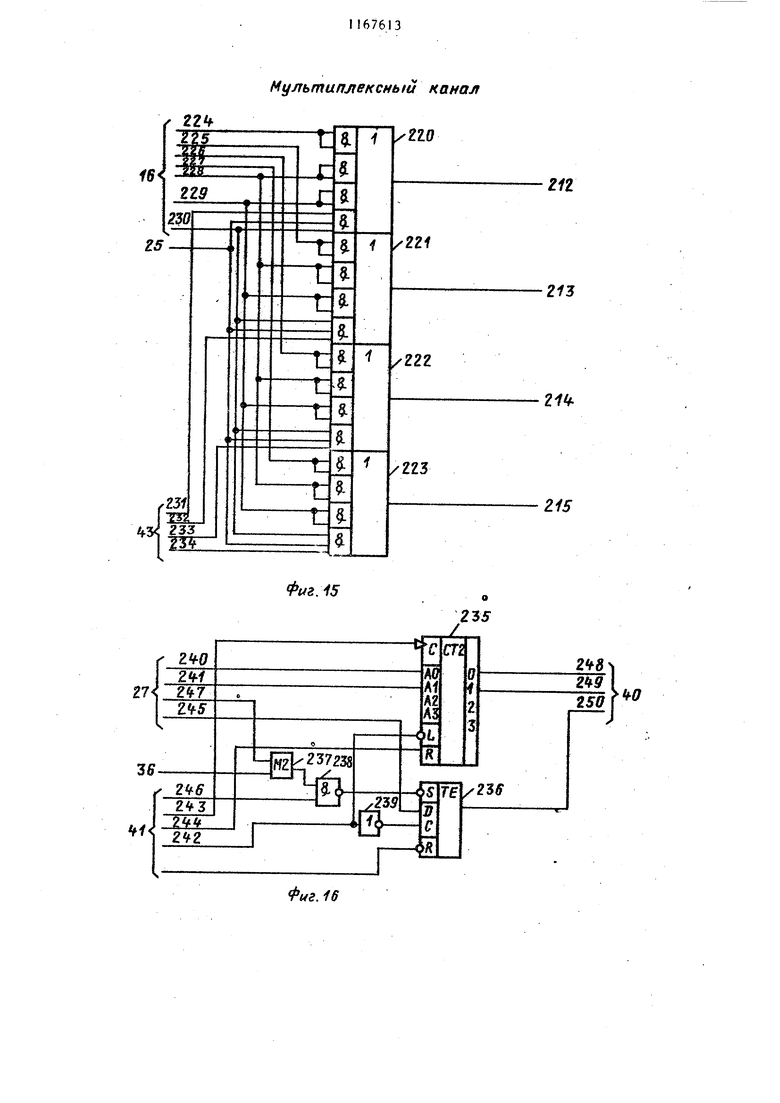

Узел 209 .управления регистрами (фиг. 15) содержит элементы И-ИЛИ 220-223. На первые, вторые входы элементов И-ИЛИ 220-223 по шинам

0 224-227 из блока 1 поступают соответственно сигналы занесения нулевого первого, BToporo,j третьего байта информации с выхода блока 4, на тр.етьи и четвертые входы по шине 228 - сигнал одновременного занесения четырех байт слова из регистра 208, на пятые и шестые входы по шине 229- сигнал занесения четырехбайт слова из блока 6, на седьмые входы по

0 шине 230 поступает сигнал занесения информации из оперативной памяти.

По шинам 231-234 на восьмые входы элементов И-И/М 220-223 поступают сиг налы блокировки приема информации

5 из оперативной памяти, на девятые входы по шине 25 из блока 3 - сиг- , нал готовности .приема информации из оперативной памяти.

Блок 9 формирования состояния

0 обмена (фиг. 16) содержит двоичный счетчик 235 байт буфера, триггер 236 конца страницы, элемент 237 сравнения, элемент И-НЕ 238, элемент ИЛИ-НЕ 239. Счетчик 235 загружается

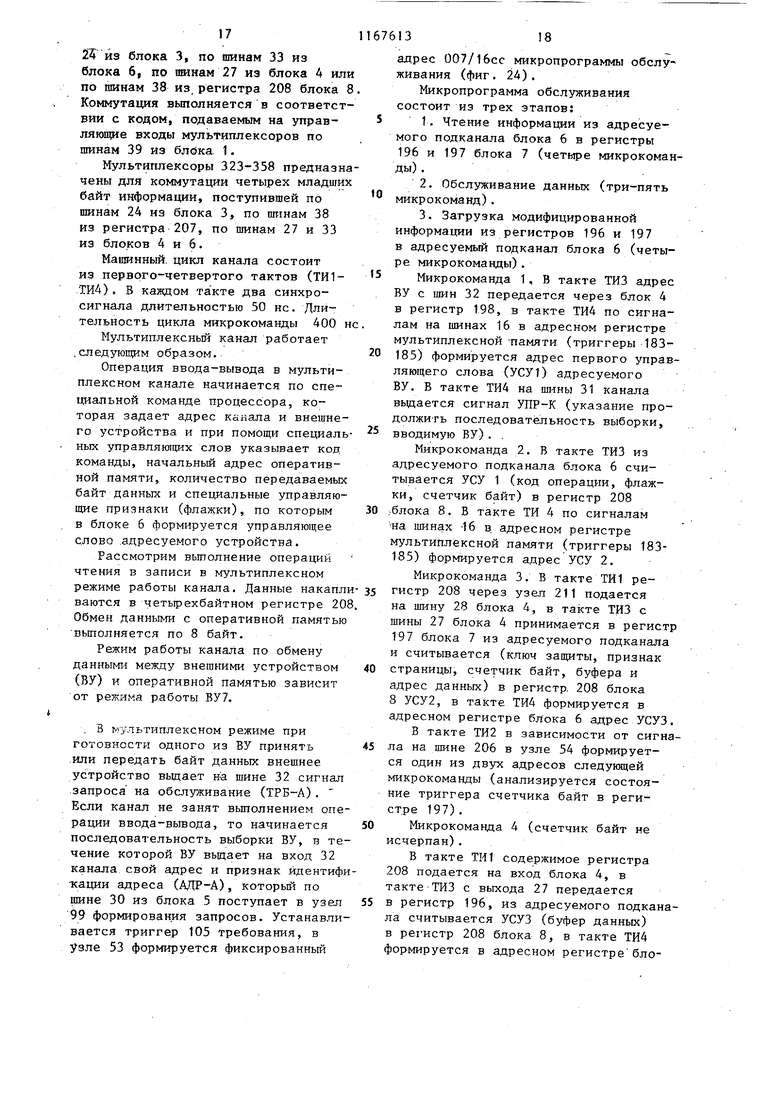

5 по входным шинам 240 и 241 по управляющему сигналу на шине 242. Модифицируется счетчик на +1 сигналом на входной иише 243, сбрасыва 15 ется сигналом по шине 244. Триггер 236 конца страницы загружается из адресуемого подканала через блок 4 по входной шине 245. Устанавливается триггер 236 управляю1ф1м сигналом по входной шине 246, когда &дрес данных переходит границу 2048 байт. Элемент 237 соед нен по первому входу шиной 36 с одним из двадцатых разрядов адресного регистра 196 (регистр t96 содержит информационных разрядов с 0-31, кон трольных разрядов - с 32-35) по второму входу шиной 247 - с двадцатым разрядом выходт 1х птн блока 4. Выходными шинами 248-250 блок 9 соединен с блоком 12, 248, 249 - с блоком 10. Блок 10 коммутации сигналов управления обмена (фиг. 17) содержит дешифратор 251, элементы 252 и 253 сложения по модулю два, элементы ИЛ 254 и 255, селекторы-мультиплексоры 256-258. Первые входы элементов 252 и 253 соединены соответственно шина ми 200 и 201 с младшими 31 и 30-м разрядами адресного регистра 196, на вторые входы элементов 252 и 253 поступает по шине 45 сигнал чтения обратном направлении. Первые и вторые управляющие входы мультиплек соров 256-258 такамк 248 и 249 соед нены соответственно с первым и вторым разрядами счетчика 235, На вьвсо дах мультиплексоров 256-258 формируются сигналы с огласно таблице, представленной на фиг. 21. Блок 10 выходными шинами 259-262 соединен с регистром 11, шиной 262 - с блоком 12. Регистр 11 масок (фиг. 18) содер жит триггеры 263-266 масок, элементы И-НЕ 267-270. Триггеры 263-266 масок, соответствующие нулевому, первому, второму и третьему байтам регистров 207 и 208, устанавливаются по сигналу занесения масок на шине 271 в зависикЪсти от сигналов, вырабатьгеаемых в блоке 10 и поступающих в регистр по шинам 259.262. На входы элементов И-НЕ 267-27 поступает по шине 45 сигнал чтения в.обратном направлении, на входы триггеров 263-266 по шине 46 - сигн чтения. Регистр 11 масок сбрасы вается сигналом на шине 272, поступающим из блока 1 памяти микропро-грамм. 316 Блок 12 дешифрации функциональных переходов (фиг. 19) содержит элементы 273 и 274 сложения по модулю два,, элементы И 275-281, элементы ИЛИ 282 и 283, дешифратор 284; Блок 12 формирует сигналы условий канала, поступающие по выходным шинам 91-94 в узел 54 формирования адреса следукяцей микрокоманды. В блоке 12 формируется два. типа функциональных переходов. Сигнал разрешения формирования условий по первом ф нкциональному переходу поступает по шине 285 из блока 1 на элементы И 278, 279 и 281. На входы дешифратора 284 из блока 7 по шинам 203 и 204 поступает двухразрядный код операции (чтения, чтения в обратном направлении, записи), по шине 205 - сигнал блокировки записи в оперативную память. Условия формирования первого и второго функционального перехода представлены соответственно на фиг. 22 и 23. Сигнал разрешения формирования второго функционального перехода поступает по шине 286 на входы элементов И 275-277, 28Q. .Шиной 202 блок 12 соединен с 29-м разрядом адресного регистра 196. Элемент И 275 возбуждается, когда адрес данных находится на границе двойного слова, На первый и второй входы элемента 273 сложения по модулю два поступают соответственно первый и второй разряды счетчика 235, первый вход элемента 274 соединен с вторьм разрядом счетчика 235. На выходе элемента И 276 в зависимости от кода операхщи, поступающего с дешифратора 284, формируются сигналы полного буфера (в операции чтения и чтения в обратном направлении) или пустого буфера (в операции записи). На выходе элемента ИЛИ 282 по сигналу на шине 262 формируется сигнал границы слова адреса. На выходе элемента ИЛИ 283 формируется сигнал конца Страницы оперативной памяти (2048 байт), поступающий по шине 250 из блока 9. Блок 13 коммутации (фиг. 20) содержит мультиплексоры 287-358. Мультиплексоры 287-322 предназначены для коммутации четырех старших байт информации, поступившей по шинам

171

22f из блока 3, по шинам 33 из блока 6, по шинам 27 из блока 4 или по шинам 38 из, регистра 208 блока 8. Коммутагщя выполняется в соответствии с кодом, подаваемым на управляющие входы мультиплексоров по шинам 39 из блбка. 1.

Мультиплексоры 323-358 предназначены для коммутации четырех младших байт информации, поступившей по шинам 24 из блока 3, по шинам 38 из регистра 207, по шинам 27 и 33 из блоков 4 и 6.

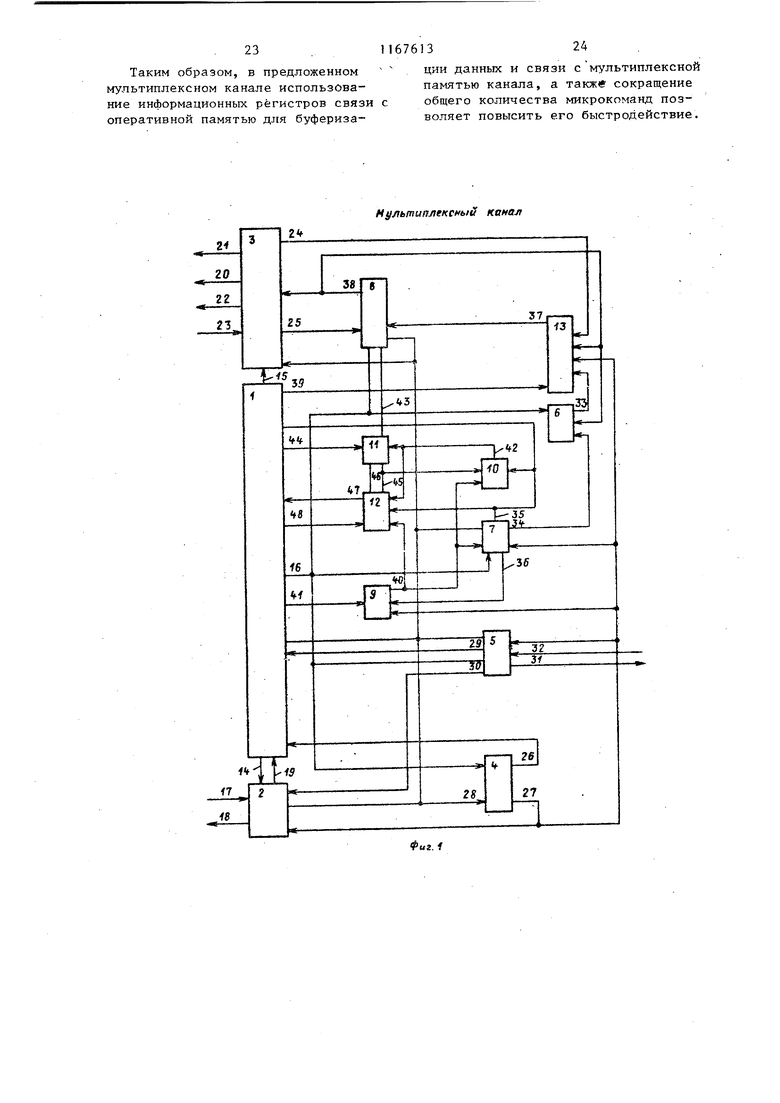

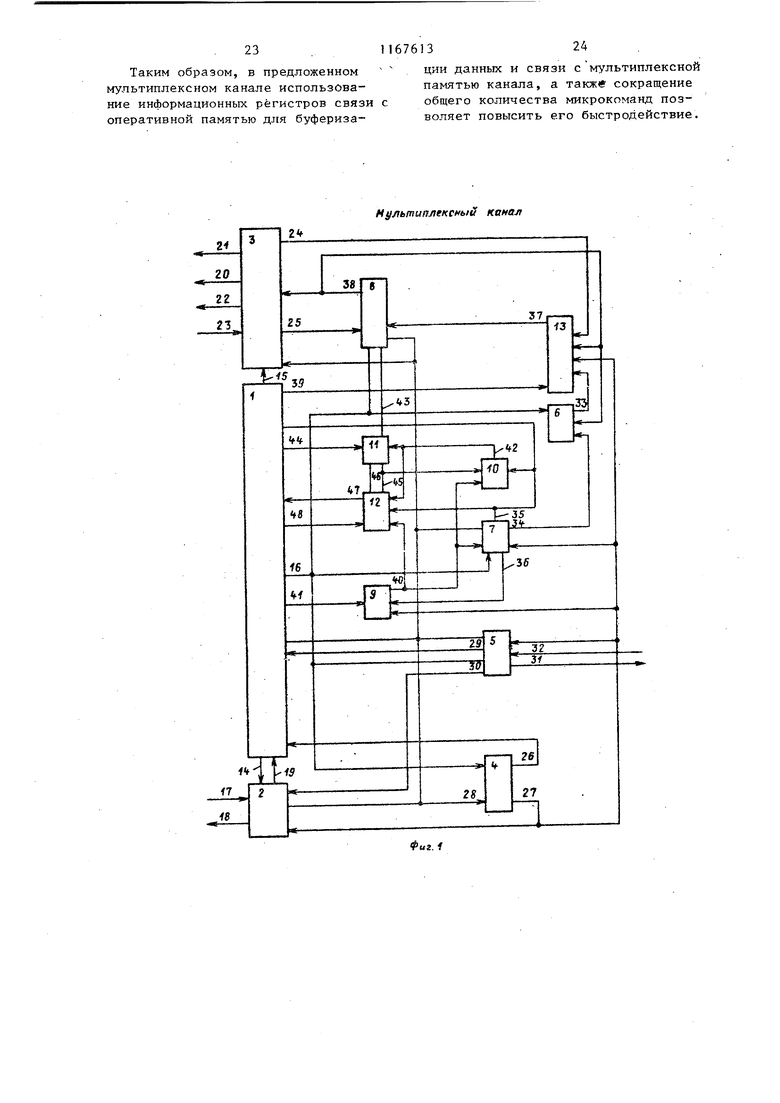

Машинный, цикл канала состоит из первого-четвертого тактов (ТИ1ТИ4) . В каждом такте два синхросигнала длительностью 50 не. Длительность цикла микрокоманды 400 не

Мультиплексный канал работает .следующим образом.

Операция ввода-вывода в мультиплексном канале начинается по специальной команде процессора, которая задает адрес канала и внешнего устройства и при помощи специальных управляющих слов указывает код команды, начальный адрес оперативной памяти, количество передаваемых байт данных и специальные управляющие признаки (флажки), по которым в блоке 6 формируется управляющее слово .адресуемого устройства.

Рассмотрим выполнение операций чтения в записи в мультиплексном режиме работы канала, Данные накапливаются в четырехбайтном регистре 208. Обмен данными с оперативной памятью вьшолняется по 8 байт.

Режим работы канала по обмену данными между внешними устройством (ВУ) и оперативной памятью зависит от режима работы ВУ7.

В г-гультиплексном режиме при готовности одного из ВУ принять .или передать байт данных внешнее устройство вьщает н-а шине 32 сигнал запроса на обслуживание (ТРБ-А) . Если канал не занят вьшолнением операции ввода-вывода, то начинается последовательность выборки ВУ, в течение которой ВУ выдает на вход 32 канала свой адрес и признак йдентифи-кации адреса (АДР-А), который по шине 30 из блока 5 поступает в узел 99 формирования запросов. Устанавливается триггер 105 требования, в Узле 53 формируется фиксированный

6761318

адрес 007/1 бес микропрограммы обслуживания (фиг. 24).

Микропрограмма обслуживания состоит из трех этапов: 5 1. Чтение информации из адресуемого подканала блока 6 в регистры

196и 197 блока 7 (четыре микрокоманды) .

в адресуемый подканал блока 6 (четыре микрокоманды).

5 Микрокоманда 1, В такте ТИЗ адрес ВУ с шин 32 передается через блок 4 в регистр 198, в такте ТИ4 по сигналам на шинах 16 в адресном регистре мультиплексной -памяти (триггеры 18320 185) формируется адрес первого управляющего слова (УСУ1) адресуемого ВУ. В такте ТИ4 на шины 31 канала вьвдается сигнал УПР-К (указание продолжить последовательность выборки,

вводимую ВУ). .

Микрокоманда 2. В такте ТИЗ из адресуемого подканала блока 6 считывается УСУ 1 (код операции, флажки, счетчик байт) в регистр 208

0 ;блока 8. В такте ТИ 4 по сигналам на шинах -16 в. адресном регистре мультиплексной памяти (триггеры 183185) формируется адрес УСУ 2.

Микрокоманда 3. В такте ТИ1 регистр 208 через узел 211 подается на шину 28 блока 4, в такте ТИЗ с шины 27 блока 4 принимается в регистр

197блока 7 из адресуемого подканала и считывается (ключ защиты, признак

0 страницы, счетчик байт, буфера и адрес данных) в регистр. 208 блока 8 УСУ2, в такте ТИ4 формируется в адресном регистре блока 6 адрес УСУЗ. В такте ТИ2 в зависимости от сигнала на шине 206 в узле 54 формируется один из двух адресов следующей микрокоманды (анализируется состояние триггера счетчика байт в регистре 197).

0 Микрокоманда 4 (счетчик байт не исчерпан).

В такте ТИ1 содержимое регистра 208 подается на вход блока 4, в такте ТИЗ с выхода 27 передается

5 в регистр 196, из адресуемого подканала считывается УСУЗ (буфер данных) в регистр 208 блока 8, в такте ТИ4 формируется в адресном регистреблока 6 адрес УСУ 4 (адрес страницы ofiepaTHBHoft памяти) . В такте ТИ2 по сигналу на шине 285 на выходе элементов 275, 276, 282 и 283 блока 12 в зависимости от кода операции на пгинах 203, 204 и 2 формируется один из кбдов первого функционального перехода (фиг. 22). Операции чтения и обратного чтения . Микрокоманда 5. В такте ТИ1 байт данных с шин 32 по шинам 28 принимается на вход блока 4, а в такте ТИЗ в зависимости от сигналов на нм нах 224-227 разрешения приема инфор мации с выходных шин 27 блока 4 при нимается в соответствующий байт рег стра 208, из адресуемого подканала блока 6 считывается УСУ 4 (адрес сл дующей страницы оперативной памяти) в регистр 207, в такте ТИ4 на шины 31 канала выдается сигнал ИНФК. В такте ТИ2 этой микрокоманды по сигналу на шине 286 на выходе элементо 275, 276, 283 и 282 блока 12 формируется один из адресов второго функ ционального перехода (фиг. 23), т.е четыре мпадших разряда адреса следующей микрокоманды формируются в зависимости от состояния шин 200-202 трех младших разрядов, двад цатого разряда шины 250, адресного регистра 196 и счетчика 235 байт буфера. Микрокоманда 6 (адрес 0000 или 1000). Буфер данных не полный, адрес данных не на границе слова. В такте ТИ1 содержимое регистра 196 подается на вход блока 4, модифицируется на ±.1 и в такте ТИЗ информация с шин 27 заносится в регистр 196, п сигналу на шине 243 модифицируется на +1 счетчик 235 байт буфера, вьшолняется запись регистра 208 в адресуемый подканал блока 6. Микрокоманда 6 (адрес 0110). Буфер 208 полный, адрес на границе слова. В такте ТЙ1 адрес данных из регистра 196 передается в регистр 131 адреса оперативной памяти и на вход 28 блока 4, регистр 208 через блок 13 коммутатора передается в регистр 207. В блоке 3 сопряжения с оперативной памятью вырабатывается сигна запроса на связь с ОП и сигнал чтения ОП (22). В такте ТЙЗ модифицированный адрес данных с вькода 27 блока 4 заносится в регистр 196, выдается сигнал 246 установки триггера 236 конца страницы оперативной памяти по сигналу 244 сбрасывается счетчик 235 байт буфера. По сигналу 25 готовности ОП (после окончания цикла работы оперативной памяти равного 1,2 мкс) в узле 210 управления регистром вырабатываются сигналы 216-219 приема в регистр 208. Информация из оперативной памяти через блок 13 коммутатора по шине 37 принимается в регистр 208. I микрокоманда 6 (адрес 1110). Буфер полный, адрес данных на границе двойного слова. В данном случае информация из оперативной памяти с шин 24 через блок 13 прини faeтcя в регистр 207. Модифицирует ся на ±1 адрес данных в регистре 196 выдается сигнал но шине 246 установ- ки триггера 236 конца страницы, и сбрасывается счетчик 235 бакт буфет ра. Микрокоманда 6 (адрес 0010) Буфер неполный, адрес данных на границе слова. В такте ТИ1 регистр 208 через блок 13 передается в регистр 207. По сигналу на шине 271 в блоке 11 вьфабатываются сигналы 231-234 масок (фиг. 18), Прочи-анная информация из оперативной памяти принимается в регистр 208 и по маскам в регистр 207. Модифицируется на +1 адрес данных в регистре 196, на шине выдается сигнал 246 установки триггера 236-. кон.ца страницы, сбрасывается сигналом на шине 244 счетчик 235. Микрокоманда 6 (адрес 1010). Буфер неполный, адрес данных на границе двойного слова. В этом случае информация,из оперативной памяти принимается в регистр 207 и по маскам в регистр 208. Остальные шаги аналогичны макрокоманде 6 с адресом 0010. Микрокоманды 7 и 8. В такте Ти1 два младших байта регистра 197 подаются по шине 28 в блоке 4, модифицируются на -1 ив такте ТИЗ заносятся в регистр 197. При этом может быть выполнена запись содержимого регистров 207 и 208 в оперативную память (осуществ ляется запись, если в предьщущей микрокоманде выполнялось чтение оперативной памяти). Операция записи (фиг. 24 и 25). Выполнение микрокоманды 1-4 ана гично выполнению операции чтения. Микрокоманда 5. В такте ТИ1 на шину 28 блока 4 подается содержимое регистра 208 (буфер данных), в такте ТИЗ с шин 27 соответствующий байт данных по сигналу на шине 16 принимается в узел 162 блока 5 и выдается на шины 31. Адрес следующей микрокома ды формируется по сигналу на шине 286 разрешения втооого функциональ ного перехода .(фиг. 19) аналогично формированию в операции чтения. Микрокоманда 6 (адрес 0000 ил .1000). Буфер не пустой, адрес данных не на границе слова. В такте ТИЗ модифицированное на -1 количество байт заносится в регистры 196 и 197, на выходные шины 31 канала выдается сигнал ИНФ-К. В следующей микрокоманде модифи цируется адрес данных на +1 и по . сигналу на шине 242.счетчик 235. Микрокоманда 6 (адрес 0010 ил 1010). Буфер не пустой, адрес данных находится на границе слова или дво ного слова. В этом случае модифицируется на -1 счетчик байт, выдается сигна ИНФ-К, по сигналу на шине 244 выполняется сброс счетчика 235. В сл-едующей микрокоманде при мо фикации адреса данных дается сигна на шине 246 разрешения смены страницы. Микрокоманда 6 (адрес 0110 ил 1110). Буфер пустой, адрес данных на границе слова или двойного слова. Выполняется цикл чтения слова из оперативной памяти 6 регистре 2 или 208 в зависимости от состояния 29-го разряда шины 202 регистра 19 I В следующей микрокоманде (7) ба данных вьщается на шины 31 и устанавливается сигнал ИНФ-К. В следующих микрокомандах моди(Ьидиоуется счетчик байт, адрес дан Hbix, устанавливается сигнал на шин 246 разрешения смены страницы,, сбр вается счетчик 235. 322 Микрокоманда 6 (адрес 0100 или . 1100). Буфер пустой, адрес данных не на границе слова или двойного слова. Выполняется цикл чтения слова из оперативной памяти. В следующих микрокомандах после вьщачи байта данных на выходные шины 31 канала слово из регистра 208 записывается в адресуемый подканал (УСУЗ) блока 6, модифицируется адрес данных, счетчик байт и счетчик байт буфера. . Рассмотрим вьтолнение чтения и записи с косвенной адресацией данных в канале. Косвенная адресация данных в канале позволяет одной команде вводавывода работать с несколькими наприлегающими страницами оперативной памяти. Если задан флажок косвенной адресации в командном слове канала, то адрес данньсх в данном слове является начальным адресом списка адресов. В этом случае реальный адрес данных извлекается из оперативной памяти по адресу, указанному в списке адресов. При передаче данных канал определяет окончание страницы по изменению состояния двадцатого разряда регистра 196.и устанавливает триггер 236 конца страницы. При выполнении операции чтения в микрокоманде 5 (фиг. 24) вьшолняется прием байта данных в нулевой байт регистра 208, при зтом в регистр 207 из адресуемого подканала блока 6 считывается адрес следующей страницы списка косвенных адресов оперативной памяти. В общий цикл обслуживания данных добавляется считывание адреса данных из оперативной памяти в регистр 196, зат.ем адрес страницы модифицируется и записывается в адресуемый подканал блока 6 (микрокоманды 0001, 1001, 7-9, фиг. 26). В операции записи при выполнении микрокоманды 5 (фиг. 24) байт данных устанавливается на шины, 31, но выдача сигнала ИНФ-К блокируется, вьтолняется функциональный переход к шестой микрокоманде с адресом 0101 (фиг. 27). Выдача байта данных на шины 31 и сигнала ИНФ-К вьтолняется после смены страницы и чтения информации из . оперативной памяти в регистр 208 (микрокоманды 7-10, фиг. 27). 23 , Таким образом, в предложенном мультиплексном канале использование информационных регистров связи оперативной памятью для буферизаМультиплексный канал 116761324 ции данных и связи с мультиплексной памятью канала, а такж сокращение собщего количества микрокоманд позволяет повысить его быстродействие.

55

1167613

Мультиплексный канал

Фиг.Б

Фч8. .iOO

ЪО

Фиг, у

Мультиплексный канцл

Мультиплексный нинал

,109

30

.fffi

7f

75

f

113-117 J. 1

М2

ч

т

ог

19

. 120

121

71

-23

72

,10S

.03

TF

Мультиплексньк канал

Фиг.7

Фиг.9

Мультипленсныи канал

Нулыпиплексныи намел

Фиг. i1

Мультиплексный канал

/

165

33

Фиг.1г

Мультиплексный канал

Фиг. 13

Фиг. f 4

Мультиплексный канал

Фиг. 16

35 Its 0

Фиг. 18

33

Ну/итиплекеный канал

S81

Фиг. IS

Мультиплексный канал

эт

Мультиплексный канал

Фиг, 11

Фиг. 22

Мультиплексный канал

Фиг.

выдача УПрк (31/. Z. Ч пенив us ffyjfA/m/n/reKcmtf naft mufSfffd/fffjpfui afnauaufiOS/

Деревача

petufmfl 199 SpetaemffSJ. Г spetaei Чтение ut ндпыауялекснай nanHmulSj, itZ. ffc/itajtHiif счетчика S«um

ПёреЗача

, регистра 20S Sffiuanp ISf ,

е

. Чтение в (1ф1ьян1ял 6енай памит (6j УСУ2

.

etucmfl 20S. унямионалчнл

-перенаЗ i

Приен

вай/ва ванныг ерееастр .QS. 5. Чтение из уль/чигглгхсяей паняти16) УСУ aetue/npZer.SbifaitO иНФН, Фунхии;:

.JfioinHbiu nffcind Окончание .nttpanuu Ч-К)0

HyMbraunjrexcHiitu канал

(сч-н) о

Г(сч-к)о

Чтение с 1лояирвЛяой записи i аператидную панить

или чтение

Чтение обротнве

Снена страницы

уantpo/nuSHOunoMitmu

N 1авифихдии1 счеягчакв ааит на - 1(137}

b/dava faifma Тонных из рег. 208на шину SI.

J.

Мультиплексный канал

Запись

Oiffi

смена страним

Фиг. 25

Ч прение с косбеннои адресацией on pamaeHoti памяти

0001, ЗапцсбlOOi fyd}epa{20&)l

МП. модификация адрё . .cnwaHut4bifZO7}ti запись Л регистр 198. Чтение mpaHUUbflZO 7 мли 2081

Лдрес страницы не кратен слову

Т. Передача адреса страницы из регистра Iffff S 20В. Cfpoc счетчика faam буфера (235)

8 Модификация адреса данных Ha±i S регистре Z07 и пере дача 6 регистр iS6. Модификаций с /етчика

faufn (fуф ера {2SSJ Запись адреса следуюU4eu страницы 8 НП

$. Модификация счетчика faSf (197} Чтение буфера из МП 8 регистр 208.

Фиг. 26

Мультиплексмьг канал

Лдрес страницы кратен слову

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3675214, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-09—Подача