ы

ОС

31506478

атрибутов, регистры сдвига, блок 12 дешифрации (направления), коммутаторы 13-15 данных, Дешифратор 16 (портов), регистр цвета, коммутатор сиг- с налов, формирователь 19 импульсов и элемент ИЛИ 20. Изобретение обеспечивает достижение поставленной цели за счет обмена с цроцессором ЭВМ словом из двух байтов и за счет выЬорки слова из блока оперативной памяти при регенерации изображения. Это дает возможность обеспечить вывод на экран динамических процессов и объектов с вдвое большей скоростью перемещений и преобразований. 2 з.п.ф-лы, 13 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для межмашинного обмена | 1986 |

|

SU1312589A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

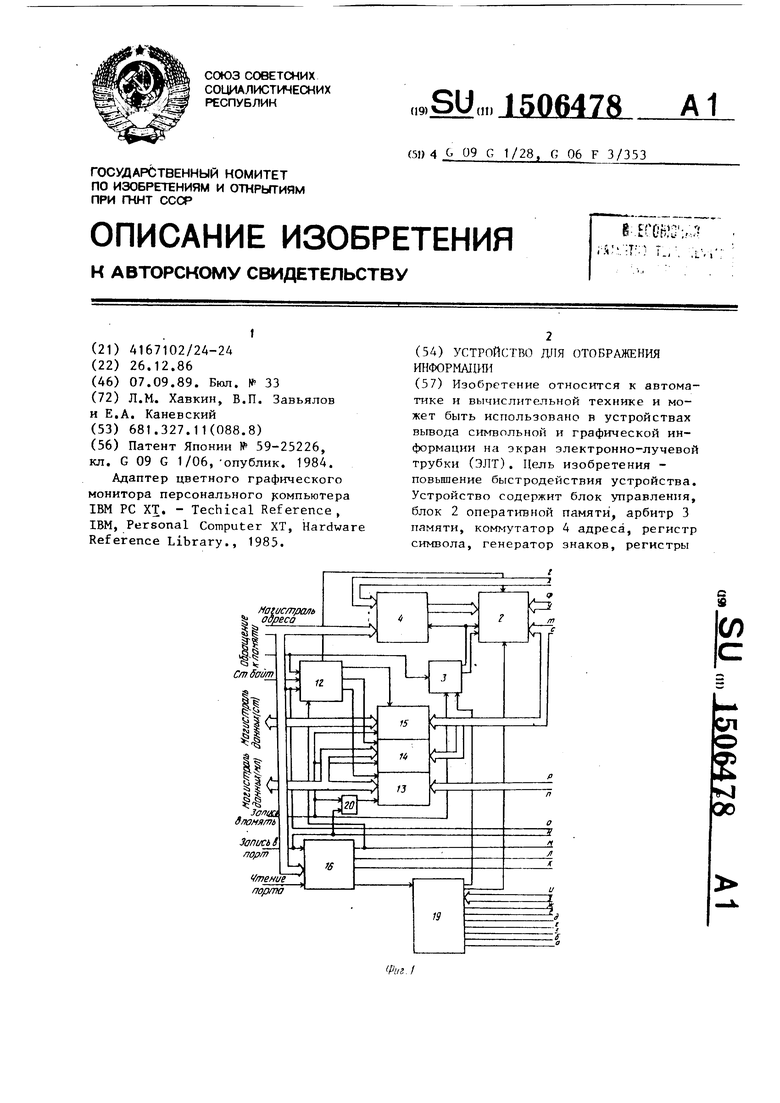

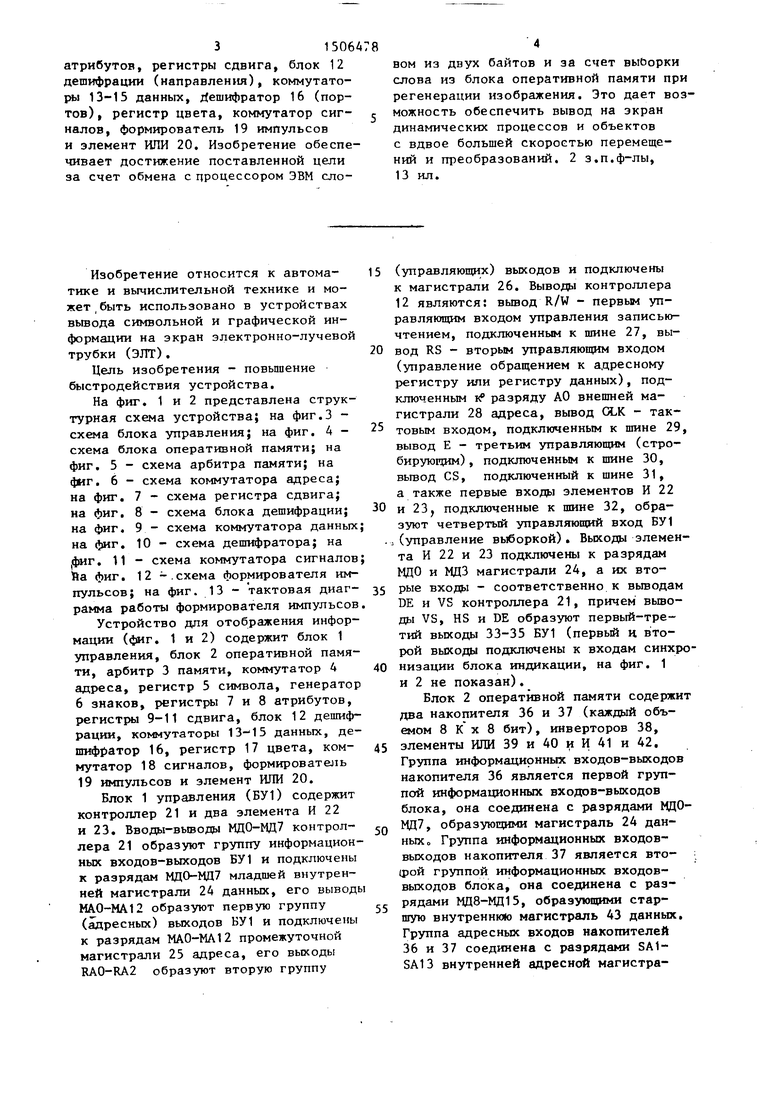

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах вывода символьной и графической информации на экран электронно-лучевой трубки (ЭЛТ). Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 управления, блок 2 оперативной памяти, арбитр 3 памяти, коммутатор 4 адреса, регистр 5 символа, генератор 6 знаков, регистры 7-8 адреса, регистры 9-11 сдвига, блок 12 дешифрации (направления), коммутаторы 13-15 данных, дешифратор 16 (портов), регистр 17 цвета, коммутатор 18 сигналов, формирователь 19 импульсов и элемент ИЛИ 20. Изобретение обеспечивает достижение поставленной цели за счет обмена с процессором ЭВМ словом из двух байтов и за счет выборки слова из блока оперативной памяти при регенерации изображения. Это дает возможность обеспечить вывод на экран динамических процессов и объектов с вдвое большей скоростью перемещений и преобразований. 2 з.п. ф-лы, 13 ил.

Изобретение относится к автома- тике и вычислительной технике и может, быть использовано в устройствах вьшода символьной и графической информации на экран электронно-лучевой трубки (ЭЛТ).

Цель изобретения - повьш1ение быстродействия устройства.

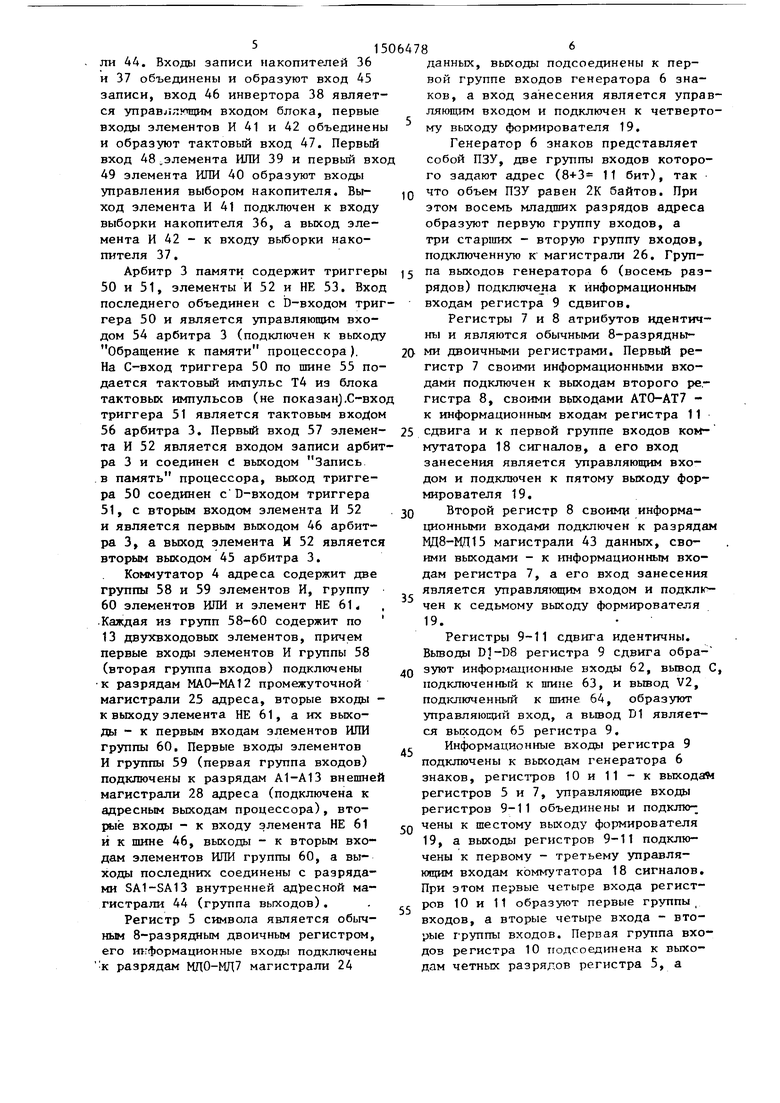

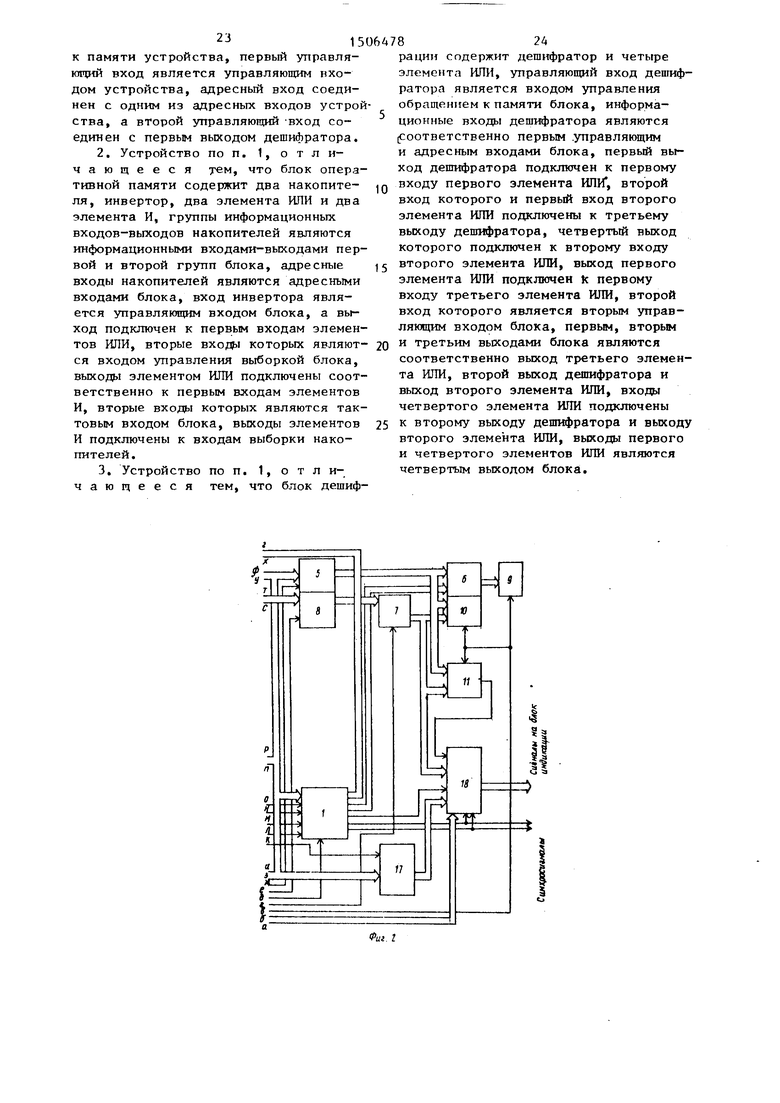

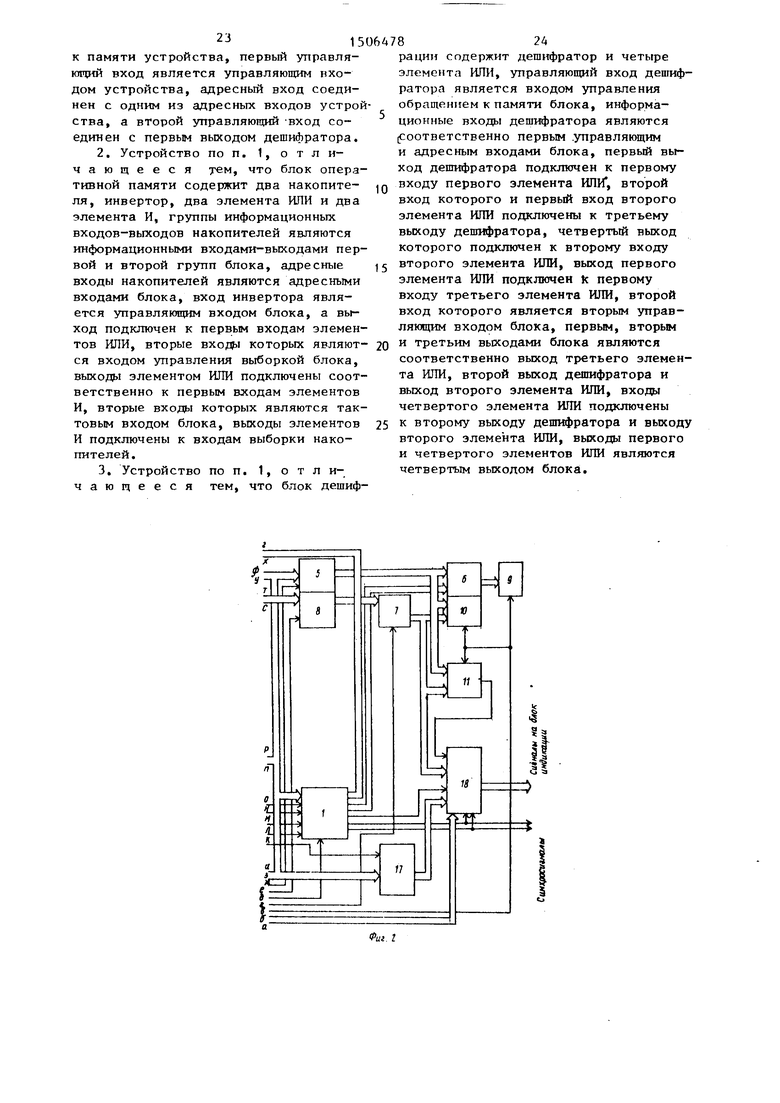

На фиг. 1 и 2 представлена структурная схема устройства; на фиг.З - схема блока управления; на фиг. 4 - схема блока оперативной памяти; на фиг. 5 - схема арбитра памяти; на 4ИГ. 6 - схема коммутатора адреса; на фиг. 7 - схема регистра сдвига; на фиг. 8 - схема блока дешифрации; на фиг. 9 - схема коммутатора данных на фиг. 10 - схема дешифратора; на 1ФИГ. 11 - схема коммутатора сигналов fta фиг. 12 -.схема формирователя импульсов; на фиг. 13 - тактовая диаг- рамма работы формирователя импульсов Устройство для отображения информации (фиг. 1 и 2) содержит блок 1 управления, блок 2 оперативной памяти, арбитр 3 памяти, комг утатор 4 адреса, регистр 5 символа, генератор 6 знаков, регистры 7 и 8 атрибутов, регистры 9-11 сдвига, блок 12 дешифрации, коммутаторы 13-15 данных, дешифратор 16, регистр 17 цвета, ком- мутатор 18 сигналов, формирователь 19 импульсов и элемент ИЛИ 20.

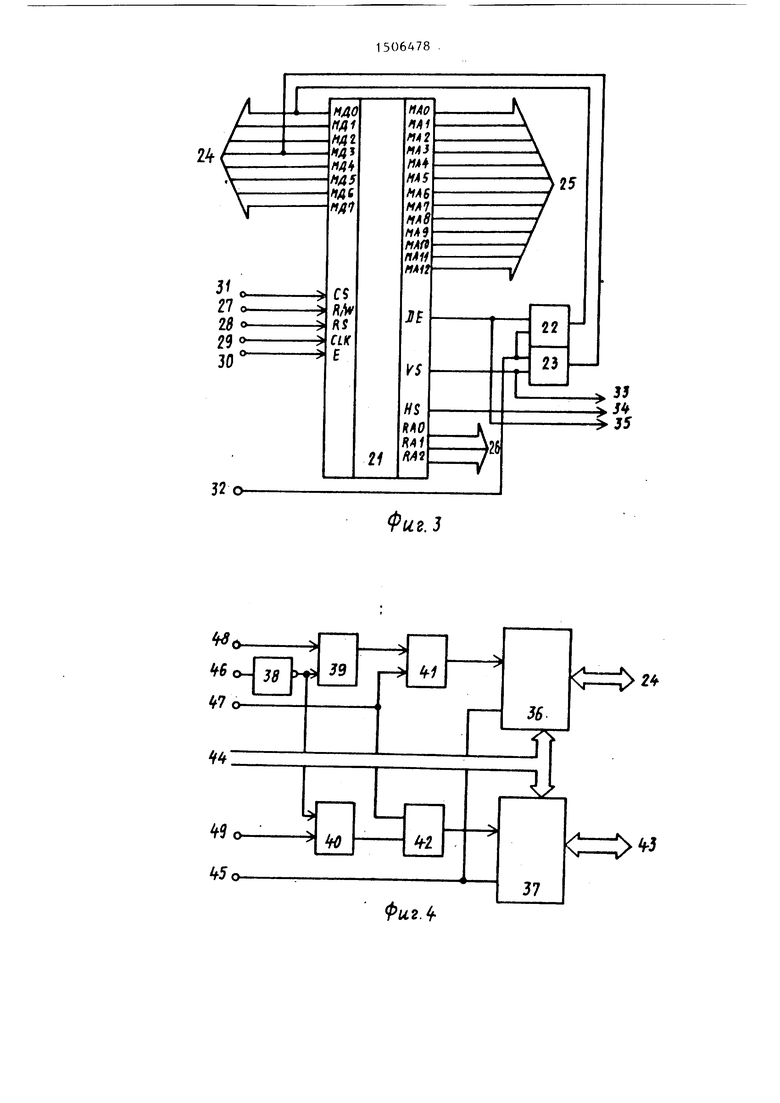

Блок 1 управления (БУ1) содержит контроллер 21 и два элемента И 22 и 23. Вводы-вьгоода МДО-МД7 контрол- лера 21 образуют группу информационных входов-выходов БУ1 и подключены к разрядам МДО-МД7 младшей внутренней магистрали 24 данных, его выводы МАО-МА12 образуют первую группу (адресных) выходов БУ1 и подключены к разрядам МАО-МА12 промежуточной магистрали 25 адреса, его выходы RAO-RA2 образуют вторую группу

(управляюш х) выходов и подключены к магистрали 26. Выводы контроллера 12 являются: вывод R/W - первым упавляющим входом управления записью- тением, подключенным к шине 27, выод RS - вторым управляющим входом (управление обращением к адресному егистру или регистру данных), подключенным 1 разряду АО внешней магистрали 28 адреса, вывод CLK - тактовым входом, подключенным к шине 29, вывод Е - третьим управляющим (стро- бирующим), подключенным к шине 30, вьгеод CS, подключенный к шине 31, а также первые входы элементов И 22 и 23, подключенные к шине 32, образуют четвертый управляющий вход БУ1 (управление выборкой). Выходы элемента И 22 и 23 подключены к разрядам МДО и МДЗ магистрали 24, а их вторые входы - соответственно к выводам DE и VS контроллера 21, причем вьшо- ды VS, HS и DE образуют первый-тре- тий выходы 33-35 БУ1 (первый и второй выходы подключены к входам синхронизации блока индикации, на фиг. 1 и 2 не показан).

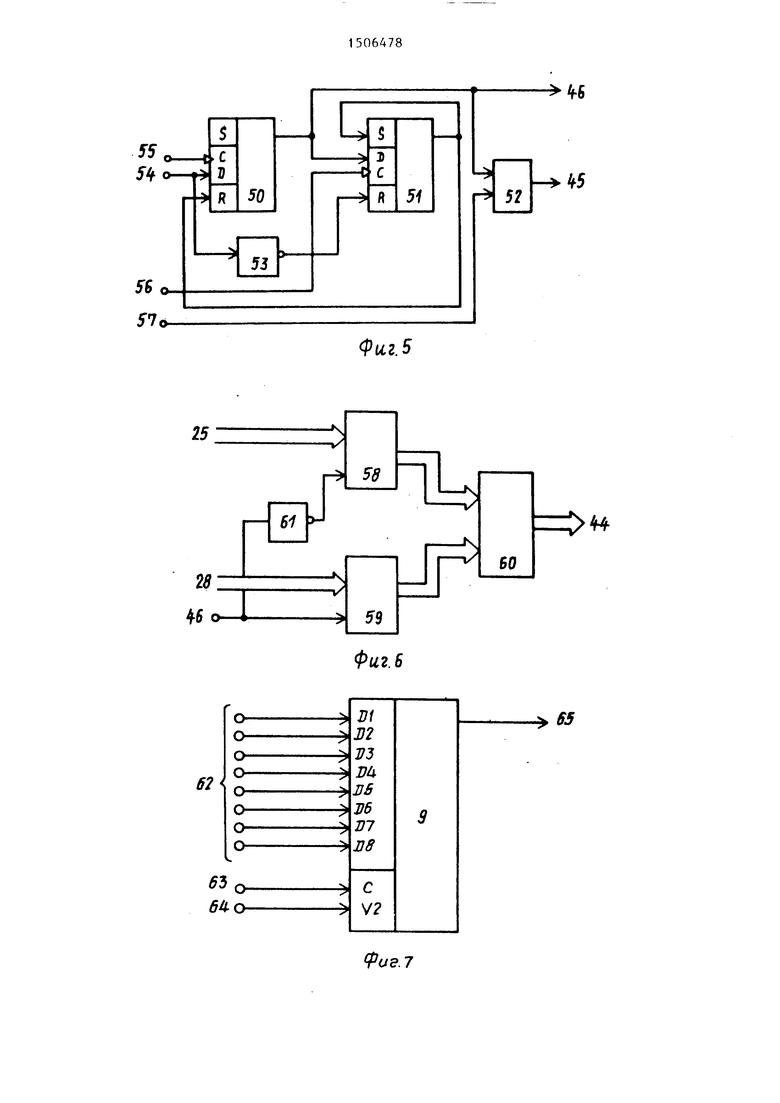

Блок 2 оперативной памяти содержит два накопителя 36 и 37 (каждый объемом 8 К X 8 бит), инверторов 38, элементы ИЛИ 39 и 40 и И 41 и 42. Группа информационных входов-выходов накопителя 36 является первой группой информационных входов-выходов блока, она соединена с разрядами МДО- МД7, образующими магистраль 24 данных о Группа информационных входов- выходов накопителя 37 является вто- рой группой информационных входов- выходов блока, она соединена с разрядами МД8-МД15, образующими старшую внутреннюю магистраль 43 данных. Группа адресных входов накопителей 36 и 37 соединена с разрядами SA1- SA13 внутренней адресной магистрали 44. Входы записи накопителей 36 и 37 объединены и образуют вход 45 записи, вход 46 инвертора 38 является управл/ткчцим входом блока, первые входы элементов И 41 и 42 объединены и образуют тактовый вход 47. Первьй вход 48 ,элемента ИЛИ 39 и первый вход

49элемента ИЛИ 40 образуют входы управления выбором накопителя. Выход элемента И 41 подключен к входу выборки накопителя 36, а выход элемента И 42 - к входу выборки накопителя 37.

Арбитр 3 памяти содержит триггеры

50и 51, элементы И 52 и НЕ 53. Вход последнего объединен с Ь-входом триггера 50 и является управляющим входом 54 арбитра 3 (подключен к выходу Обращение к памяти процессора).

На С-вход триггера 50 по шине 55 подается тактовый импульс Т4 из блока тактовых импульсов (не показан.С-вход триггера 51 является тактовым входом 56 арбитра 3. Первый вход 57 элемента И 52 является входом записи арбитра 3 и соединен с выходом Запись

в память процессора, выход триггера 50 соединен с D-входом триггера 51, с вторым входом элемента И 52 и является первым выходом 46 арбитра 3, а выход элемента И 52 является вторым выходом 45 арбитра 3.

Коммутатор 4 адреса содержит две группы 58 и 59 элементов И, группу 60 элементов ИЛИ и элемент НЕ 61

Каждая из групп 58-60 содержит по 13 двухвходовых элементов, причем первые входы элементов И группы 58 (вторая группа входов) подключены

к разрядам МАО-МА12 промежуточной магистрали 25 адреса, вторые входы - выходу элемента НЕ 61, а их выходы - к первым входам элементов ИЛИ группы 60. Первые входы элементов И группы 59 (первая группа входов) подключены к разрядам А1-А13 внещней магистрали 28 адреса (подключена к адресным выходам процессора), вторые входы - к входу элемента НЕ 61 и к щине 46, выходы - к вторым входам элементов ИЛИ группы 60, а выходы последних соединены с разрядами SA1-SA13 внутренней адресной магистрали 44 (группа выходов).

Регистр 5 символа является обычным 8-разрядным двоичным регистром, его информационные входы подключены

к разрядам МЦО-МД7 магистрали 24

1506478

0

5

5

данных, выходы подсоединены к первой группе входов генератора 6 знаков, а вход занесения является управляющим входом и подключен к четвертому выходу формирователя 19.

Генератор 6 знаков представляет собой ПЗУ, две группы входов которого задают адрес (8+3 11 бит), так что объем ПЗУ равен 2К байтов. При этом восемь младших разрядов адреса образуют первую группу входов, а три старших - вторую группу входов, подключенную к магистрали 26. Группа выходов генератора 6 (восемь разрядов) подключе21а к информационным входам регистра 9 сдвигов.

Регистры 7 и 8 атрибутов идентичны и являются обычными 8-разрядны- 0 ми двоичными регистрами. Первый регистр 7 своими информационными входами подключен к выходам второго ре,- гистра 8, своими вькодами АТО-АТ7 - к информационным входам регистра 11 сдвига и к первой группе входов коммутатора 18 сигналов, а его вход занесения является управляющим входом и подключен к пятому выходу формирователя 19.

Второй регистр 8 своими информационными входами подключен к разрядам НЦ8-ВД15 магистрали 43 данных, своими выходами - к информационным входам регистра 7, а его вход занесения является управляющим входом и подключен к седьмому выходу формирователя 19.

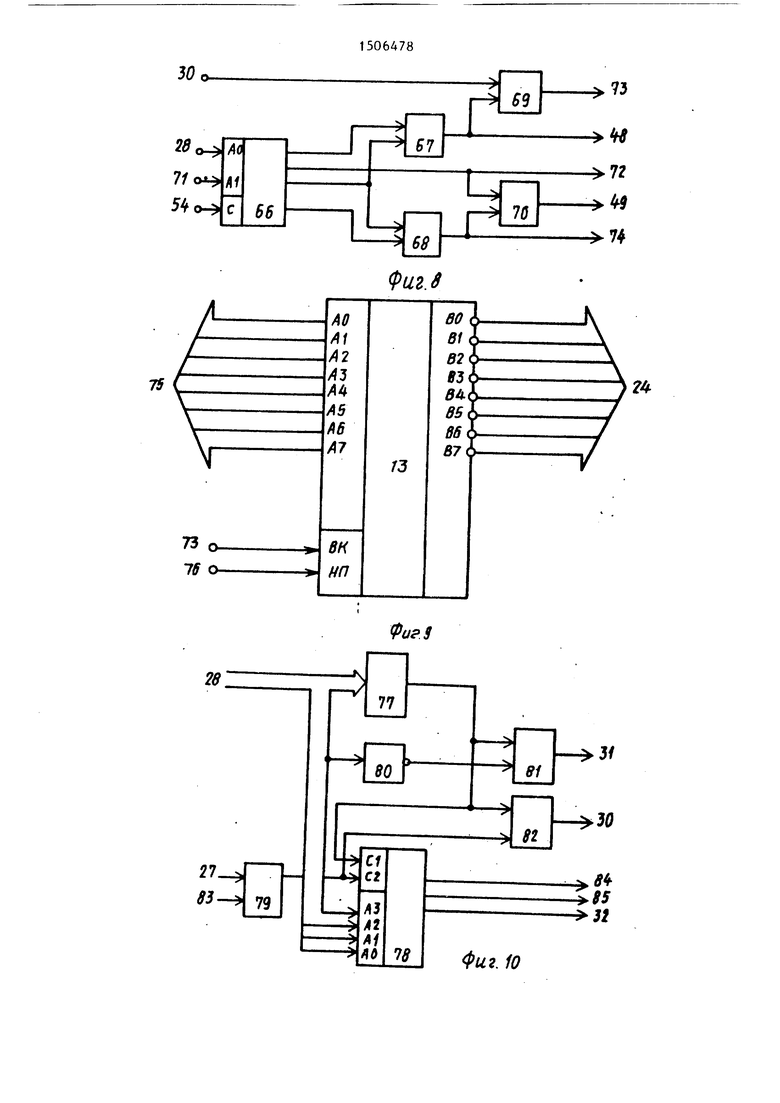

Регистры 9-11 сдвига идентичны. Вьшоды D1-D8 регистра 9 сдвига обра- зуют информационные входы 62, вьгоод С, подключенный к шине 63, и вьшод V2, подключенный к шине 64, образуют управляюпщй вход, а вьшод D1 является выходом 65 регистра 9.

Информационные входы регистра 9 подключены к выходам генератора 6 знаков, регистров 10 и 11 - к вькода регистров 5 и 7, управляющие входы регистров 9-11 объединены и подкгпо-; чены к шестому выходу формирователя 19, а выходы регистров 9-11 подключены к первому - третьему управляющим входам коммутатора 18 сигналов. При этом первые четыре входа регистров 10 и 11 образуют первые группы, входов, а вторые четыре входа - вторые группы входов. Первая группа входов регистра 10 подсоединена к выходам четных разрядов регистра 5, а

0

5

0

5

0

5

первая группа входов регистра 11 к выходам его нечетных разрядов. Вторая группа входов регистра 10 подсоединена к выходам четных разрядов регистра 7, а вторая группа входов регистра 11 - к выходам его нечетных разрядов.

Блок 12 дешифрации содержит обычный дешифратор 66 на два входа и четыре выхода, элементы Ш1И 67-70. Вьгооды дешифратора 66 являются: вывод С - первым входом 54 блока (обращение к памяти), вьшод А1 - вторым (первым управляющим) входом 71 блока (подключен к выходу Старший байт процессора), вьтод АО - третьим его входом (адресным), подключенным к разряду АО внешней магистрали 28 адреса. Выходы дешифратора 66 подключены соответственно: выход 00 - к певому входу элемента ИЛИ 67, выход 01 - к шине 72 (является вторым выходом блока), выход 10 - к вторым входам элементов ИЛИ 67 и 68, выход 11 - к первому входу элемента ИЛИ 68 Выход элемента 67 подключен к первому входу элемента ИЛИ 69, второй вход 30 которого является четвертым (вторым управляющим) входом блока, а выход 73 - первым выходом блока. Выход 74 элемента ИЛИ 68 является третьим выходом блока. Выходы элементов ИЛИ 67 и 70, подключенные к шинам 48 и 49 соответственно, образуют четвертый выход блока.

Коммутаторы 13-15 данных идентичны. Выводы АО-А7 коммутатора 13 данных образуют первую группу входов-выходо коммутатора и подключены к разрядам ДО-Д7 младшей внешней магистрали 75 данных, выводы ВО-В7 образуют вторую группу входов-выходов коммутатора и подключены к разрядам МДО-МД7 магистрали 24 данных, вьшод НП являетс первым управляющим входом 76 (подключен к выходу элемента ИЛИ 20, а его вьгоод ВК - вторым управляющим входом 73.

Первая группа входов-выходов коммутатора 14 подключена к разрядам ДО-Л7 магистрали 75 данных, а первая группа входов-выходов коммутатора 15 - к разрядам Д8-Д15 старшей внешней магистрали данных. Вторые группы входов-выходов коммутаторов 14 и 15 объединены и подключены к разрядам МД8-МД15 магистрали 43 данных. Первые управляющие входы коъту

0

5

0

5

0

5

0

5

Тагоров 14 и 15 объединены с первым входом элемента ИЛИ 20 (второй его вход подключен к шине 27) и подключены шиной 57 к выходу Запись в память процессора, а вторые управляющие входы этих коммутаторов подключены соответственно к выходам 72 и 74 блока 12 дешифрации.

Дешифратор 16 содержит дешифра- тор 77 на шесть входов, дешифратор ,78 на четыре входа и элементы ИЛИ 79, НЕ 80, И 81 и 82. Входы дешифратора /7 подключены к разрядам А4-А9 магистрали 28 адреса, вход элемента НЕ 80 - к разряду A3 этой магистрали, а вьгеоды АО-АЗ дешифратора 78 - к разрядам АО-A3 этой же магистрали, причем все вместе они образуют группу входов дешифратора 16,

Первый вход 27 элемента ИПИ 79 яв ляется первым управляющим входом дешифратора 16 (подключен к выходу Запись в порт процессора), второй вход 83 элемента ИЛИ 79 является вторым управляющим входом дешифратора (подключен к выходу Чтение порта процессора), а выход этого элемента соединен с вьшодом С2 дешифратора 78 и с вторым входом элемента И 82.Единственный выход дешифратора 77 соответствует состоянию 3DH (код 111101), он соединен с первыми входами элементов И 81 и 82 и с выводом С1 дешифратора 78. Последний имеет три вьгаода, которые соответствуют состояниям 8 (1000), 9 (100.1) и А (1010) и подключены соответственно к шинам 84, 85 и 32, образуя адресные комбинации 3D8H, 3D9H и 3DAH. Выход элемента НЕ 80 соединен с вторым входом элемента И 81, а выходы элементов И 81 и 82 подключены к шинам 31 и 30, Выходами дешифратора 16 портов являются: первым - шина 30, вторым - шины. 31 и 32, третьим - шина 85 и четвертым - шина 84,

Регистр 17 цвета является обычным 6-разрядным двоичным регистром, его информационные входы подключены к разрядам Щ9-Щ5 магистрали 24 данных, вход занесения является управляющим входом и подключен к шине 85, а выходы подсоединены к второй группе входов коммутатора 18 сигналов о

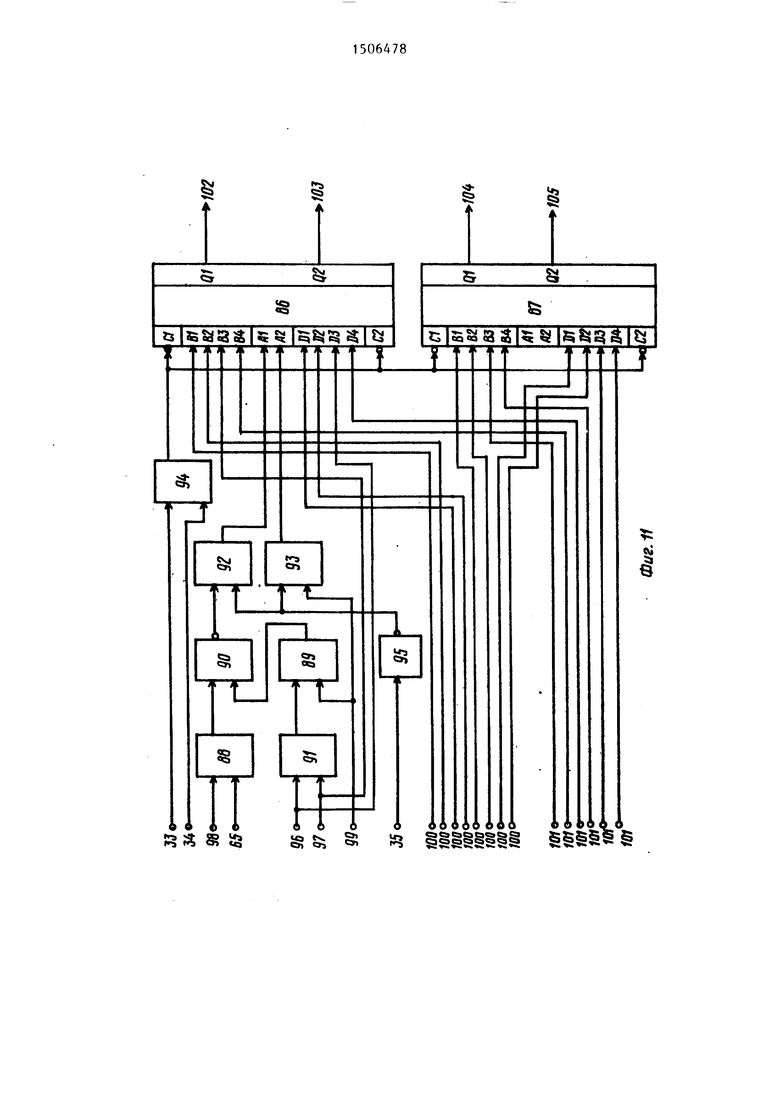

Коммутатор 18 сигналов содержит коммутаторы 86 и 87 и элементы И 88 и 89, ИЛИ-НЕ 90, ИПИ 91-94, и НЕ 95.

Второй вход 65 элемента И 88, первый вход 96 элемента ШШ 91 и второй вход 97 элемента ИЛИ 91 являются соответственно первым-третьим управляющими входами коммутатора 18 сигналов (управление разверткой символьной и графической информацией), Первый вход 33 и второй вход 34 элемента ИЛИ 94 являются четвертым и пятым управляющими входами коммутатора 18 (входы кадровой и строчной синхронизации) , а шестым его входом (сигнал разрешения вьюода на экран) является

вход 35 элемента НЕ 95. Группу управ- i тактовых импульсов (не показан). Выляющих входов коммутатора 18 образуют: первый вход 98 элемента И 88 и вторые входы элементов И 89 и JiriH 93, подключенные к шине 99. Первую группу 100 информационных входов коммутатора 18 сигналов образуют вьшоды: В1 коммутатора 87, D1 коммутатора 86, В1 коммутатора 86, D1 коммутатора 87, В2 коммутатора 87, D2 коммутатора 86, В2 коммутатора 86 и D2 коммутатора 87, подключенные соответственно к разрядам |АТО-АТ7. Вторую группу 101 информационных входов коммутатора 18 сигналов образуют вьшоды: В4 коммутатора 87, D4 коммутатора 86, В4 коммутатора 86, D4 коммутатора 87, D3 коммутатора 87 и ВЗ коммутатора 87, подключенные соответственно к разрядам 1-6 регистра 17 цвета. Выводы

20

ходы 56 элемента 124 задержки, 29 элемента 2И-2ИПИ-НЕ 107, 47 элемента И 114, 131 элемента НЕ 121 и 132 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 112 являются первым - пятым выходами формирователя. Выход 63 элемента 2И-2ИПИ-НЕ 108 и вьосод 64 элемента 119 образуют шестой выход формирователя. Выход 133 элемента ИСКПЮЧА1Ш1ЕЕ ИЛИ 110 25 является седьмым выходом формирователя.

Устройство работает следующим образом.

Устройство осуществляет прием информации по командам из процессора ЭВМ (не показан) и ее преобразование в видеосигнал изображения, а также форм1-фование сигналов синхронизации развертки, которые вместе г видео30

40

сигналом подаются в блок индикации

Q1 и Q2 коммутаторов 86 и 87, под-, 5 дJJд воспроизведения на экране ЭЛТ. ключенные к шинам 102-105 соответ- Изображение на экране может быть ственно, образуют группу выходов цветным или черно-белым, символьньи коммутатора 18 сигналов, подключен- или графическим. Символьное изобра- ную к информационным входам блока ин- жение выводится в двух форматах: дикации (не показан).

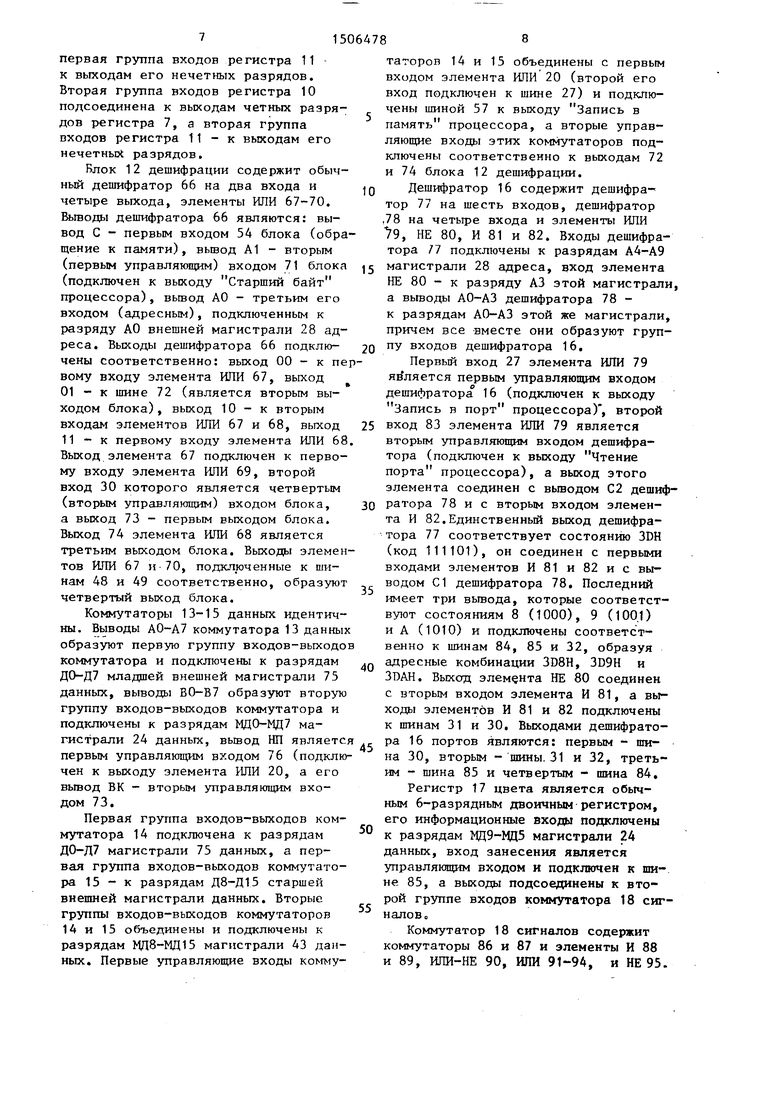

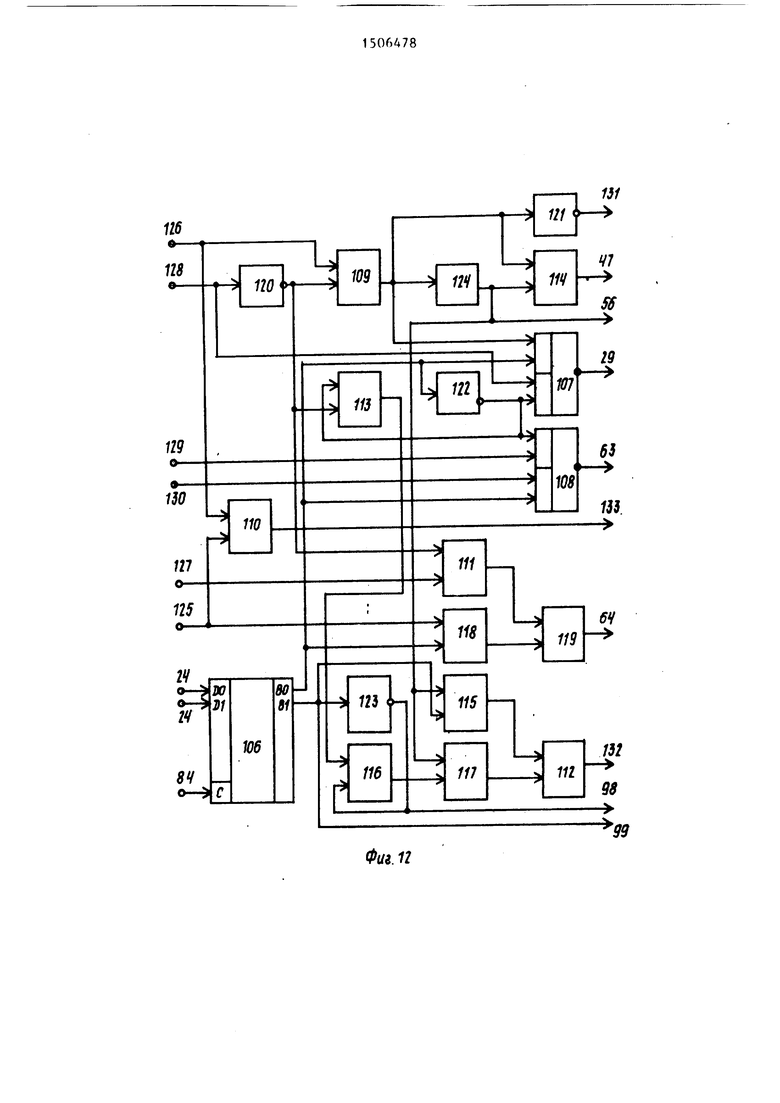

Формирователь 19 импульсов содержит регистр 106 режима на два разряда, элементы 2И-2ИЛИ-НЕ 107 и 108, ИСКЛЮЧАИЦЕЕ ИЛИ 109-112, И 113-117, ИЛИ 118 и 119, НЕ 120-123 и элемент 124 задержки. Вьшоды DO-D1 регистра 106 образуют группу информационных входов формирователя и подключены к разрядам ЩО-МД1 магистрали 24 данных, вьшод С является управляющим входом 84, вывод В1, подключенный к шине 99, и выход 98 элемента НЕ 123 образуют группу выходов фърмировате45

80 символов на 25 строк или 40 волов на 25 строк. Графическое изображение выводится в формате 320 точек на 200 строк.

Процессом преобразования информации в видеосигнал управляет контроллер 21, входящий в состав блока 1 Для этого он управляет регенерацией изображения путем перебора адресов , блока 2 оперативной памяти, изменяя кодовые комбинации на выводах МАО-МА12, подключенных к магистрали 25 адреса. Он также ведет пересчет строк растра внутри символьной строки (одна символьная строка содержит 8 строк растра) путем изменения кодовых комбинаций на выводах RAO-RA2, подключенных к магистрали 26. Контроллер 21 формирует сигналы к;1дровой син50

ля. Первые входы элементов ИСКЛЮЧАЮЩЕЕ ШШ 110 и ШШ 118 объединены р шину 125 и образуют тактовый вход Г2, а первый вход элемента ИСКЛЮЧА- ЩЕЕ ИЛИ 109 и второй вход элемента

647810

110, объединенные в шину 126, образуют тактовьш вход Т5, Первьш вход 127 элемента ИСКПЮЧАИДЕЕ ШШ 111 является тактовым входом Т7. Вход элемента НЕ 120 и третий вход элемента 2И-21-иш-НЕ 107 объединены в шину 128 и образуют тактовый вход Т8. Второй вход 129 элемента 2И-2RП i-HE Q 108 является тактовьт входом fj, а его третий вход 130 - тактовым входом f . Такты Т2, Т5, Т7, Т8 и импульсы с частотами f, , f (13 и 6,5 MrГц) вырабатываются блоком

0

ходы 56 элемента 124 задержки, 29 элемента 2И-2ИПИ-НЕ 107, 47 элемента И 114, 131 элемента НЕ 121 и 132 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 112 являются первым - пятым выходами формирователя. Выход 63 элемента 2И-2ИПИ-НЕ 108 и вьосод 64 элемента 119 образуют шестой выход формирователя. Выход 133 элемента ИСКПЮЧА1Ш1ЕЕ ИЛИ 110 5 является седьмым выходом формирователя.

Устройство работает следующим образом.

Устройство осуществляет прием информации по командам из процессора ЭВМ (не показан) и ее преобразование в видеосигнал изображения, а также форм1-фование сигналов синхронизации развертки, которые вместе г видео0

40

5 дJJд воспроизведения на экране ЭЛТ. Изображение на экране может быть цветным или черно-белым, символьньи или графическим. Символьное изобра- жение выводится в двух форматах:

45

80 символов на 25 строк или 40 волов на 25 строк. Графическое изображение выводится в формате 320 точек на 200 строк.

Процессом преобразования информации в видеосигнал управляет контроллер 21, входящий в состав блока 1 Для этого он управляет регенерацией изображения путем перебора адресов , блока 2 оперативной памяти, изменяя кодовые комбинации на выводах МАО-МА12 подключенных к магистрали 25 адреса. Он также ведет пересчет строк растра внутри символьной строки (одна символьная строка содержит 8 строк растра) путем изменения кодовых комбинаций на выводах RAO-RA2, подключенных к магистрали 26. Контроллер 21 формирует сигналы к;1дровой син50

II

хронизации на вьшоде VS, строчной синхрониэацтш на вьшоде HS и разрешния отображения на выводе DE. Послений определяет индицируемую часть строки и кадра.

При включении устройства или при смене режима (формата) вьтолняется программирование контроллера 21 по командам процессора ЭВМ, а также изменение содержимого регистра 106 режима и регистра 17 цвета. Для это процессор выставляет информацию на магистрали 75 данных, адрес на маги

страли 28 адреса и сигнал Запись

в порт на пгине 27, Последний инициирует работу дешифратора 16, который обеспечивает выделение адресных комбинаций: 3DOH-3D7H - обращение к контроллеру 21, 3D8H - обращение к регистру 106 режима, 3D9H - обращение к регистру 17 цвета, 3DAH - обращение к порту состояний БУ1 для БЫ- дачи состояния устройства.

Анализом состояния адресных разря дов А4-А9 магистрали 28 в дешифраторе 77 вьоделяется кодовая комбинация 3DH и вырабатывается соответствующий сигнал, который поступает на дешифратор 78 в качестве разрешающе- го сигнала, а также на элементы И 81 и 82.

На второй разрешающий вход дешифратора 78 с выхода элемента ИЛИ 79 поступает логическая сумма двух сиг

налов Запись в порт и Чтение порта, подаваемых на вход элемента 79 по Е инам 27 и 83. Эта логическая сумма поступает также на вход элемента И 82 о При наличии на входе дешифратора 78 двух разрешающих сигналов одновременно он открывается и анализом состояния адресных сигналов АО-АЗ вырабатывает один из сигналов обращения к регистрам режима 106, цвета 17 и порта состояний БУ1 соответственно на выходах 84, 85 и 32.

С помощью сигнала 3DH на элемента НЕ 80 и И 81 и 82 вырабатьшаются сигналы MCS и Е на шинах 31 и 30 для обслуживания контроллера 21, Первый из этих сигналов осуществляет выбор контроллера 21, а второй обозначает начало обмена контроллера 21 с процессором.

Для передачи данных в контроллер 21 служит коммутатор 13 данных. Сигнал Запись в порт по игине 27 через элемент ИЛИ 20 и шину 76 посту12

5

0

5 о

5

0

5

0

5

на вход НП коммутатора 13, обес- печ1шая направление передачи данных от магистрали 75 к магистрали 24, При наличии сигнала 3DH на выходе дешифратора 77 и сигнала на выходе элемента ИПИ 79 элемент И 82 вырабатывает сигнал на шине 30, который через элемент ИПИ 69 и шину 73 поступает на вход ВК коммутатора 13, обеспечивая выбор кристалла. В результате данные из процессора ЭВМ через магистрали 75 и 24 поступают на вьшоды МДО-МД7 контроллера 21, На вход 29 поступает тактовая частота из формирователя 19,

Сигнал Запись в порт, поступающий по шине 27 на вьшод R/W контроллера 21, определяет процесс записи при обмене. Адресный сигнал АО адресной магистрали 28 задает вид регистра контроллера 21, который должен участвсйзовать в обмене. При это будет адресный регистр,- при АО 1 - регистр данных, номер которого указан в адресном регистре. Контроллер 21 содержит 19 регистров данных.

Процесс занесения данных в каждый из этих регистров состоит из двух циклов обмена: в первом цикле в адресный регистр контроллера 21 заносится номер регистра данных, а во втором - заполняется регистр данных, номер которого содержится в регистре адреса контроллера 21, После заполнения всех регистров данных контроллера 21 процесс его программирован ия завершен.

Устройство обеспечивает обновление содержимого экрана одновременно с процессом регенерации изображения без его искажения. Это достигается тем, что запись в память новой информации осуществляется во время обратного хода луча по строке или по кадру. Сведения об обратном ходе луча поступают из блока 1 в процессор ЭВМ по магистрали 75 данных. Это дает возможность рассматривать процессы обращения к памяти и регенерации изображения независимо друг от друга.

Процесс загрузки блока 2 оперативной памяти вьтолняется под управлением арбитра 3 памяти. Процессор ЭВМ выставляет информацию на магистралях адреса 28 и данных 75, старшей внешней магистрали данных, а также сигналы Обращение к памяти и Запись в память на шинах 54 и 57.

Функция арбитра состоит в том, чтобы при обращении процессора к блоку оперативной памяти устройства выделить один полный период его работы для обмена с процессором и обеспечить в течение этого периода подключение к блоку 2 оперативной памяти внешней адресной магистрали через 4 адреса и сигнала Запис

коммутатор в память.

Периоды работы блока 2 оперативной памяти задает тактовый сигнал, поступаюгщй в блок 2 оперативной памяти из формирователя 19 по птне 47. Работа арбитра тактируется сигналами Т4 и Т9, поступающими по шинам 55 и 56, которые синхронны с сигналом на шине 47. Тргигер 50 срабатьшает по такту Т4 при наличии на его D-BXO де сигнала Обращение к памяти.

Выделенный на триггере 50 синхронный период обмена памяти с процессором в виде импульсного сигнала подается по шине 46 на коммутатор 4 адреса и обеспечивает подключение внещ ней адресной магистрали 28 к блоку 2 оперативной памяти через группы 59 и 60 элементов. Этот же сигнал подается на вход элемента И 52, обеспечивая прохождение сигнала Запись в память через элемент И 52 и по шине 45 на блок 2 оперативной памяти. Таким образом в течение выделенного синхронного периода осуществляется запись информации в блок 2 оперативной памяти по адресу, заданному процессором ЭВМ. Процессор работает с непрерьшным полем памяти и в нем область с адресами B8000H-BBFFFH соответствует блоку 2 опративной памяти, поэтому сигнал Обращение к памяти вырабатьтается процессором только тогда, когда адрес находится в указанной области.

Сигнал Обращение к памяти по шине 54 поступает в блок 12 на С-вход дешифратора 66. Пусть на адресные входы дешифратора 66 поступает сигнал Старший байт по шине 71, а содержимое нулевого разряда .адреса (АО) равно О. Тогда на выходе 10 дешифратора 66 образуется сигнал, в результате чего на шинах 73,48, 49 и 74 образуются сигналы. Сигналы по шинам 73 и 74 обеспечивают выбор кристалла комм:, таторов 13 и 15 данных

10

15

20

5

а сигналы по шннам 48 и 49 поступают в блок 2 оперативной памяти и через элементы 39-42 (при наличии сигнала на 1Ш1не 46) обеспеч}гвают выбор кристалла накопителей 36 и 37. Кроме тогг, сигпап Запись в память по шине 57 поступает в коммутатор 15 и через элемент 1ШИ 20 и шину 76 в комм татор 13, обеспечивая направление передачи данных из внешней магистрали к внутренней. В результате этого информация из процессора через обе внешние магистрали данных, коммутаторы 13 и 15, магистрали 24 и 43 данных поступают в накопители 36 и 37, на которые по шине 45 проходит сигнал записи из арбитра 3 памяти. Таким образом предлагаемое устройство обеспечивает обмен информацией между процессором ЭВМ и блоком 2 операт1твной памяти двумя байтами параллельно. Это используется для быстрой замены всего изображения, в целом или крупных фрагментов.

Пусть на адресные входы дешифратора 66 не поступает сигнал Старший байт по шине 71, а содержимое АО равно 1. Тогда на выходе-01 дешифратора 66 образуется сигнал, поступа- ющш на шину 72, в результате чегс сигнал появляется на шине 49. Сигнал на шине 72 обеспечивает выбор кристалла коммутатора 14 данных, а сигнал на шине 49 - выбор накопителя 37. Кроме того, в коммутатор 14 поступает сигнал Запись в память по шине 57J обеспечивая направление передачи из внешней магистрали данных к внутренней. В результате этого информация из процессора через внешнюю младшую магистраль 75 данных, коммутатор 14 и внутреннюю старшую магистраль 43 данных поступает в накопитель 37. Таким образом, обеспечивается однобайтовый обмен между процессором ЭВМ и блоком 2 оперативной памяти, причем младший байт наиболее Q удобный и быстрьй, с точки зрения

использования его в процессоре, засылается на место старшего байта в память устройства. Это позволяет изменять атрибут без изменения текста (в с1-гмвольном режиме в младшем байте содержится код символа, а в старшем - код атрибута, обеспечивающий задание параметров одного с гмвола, цвет, яркость и ТоД.).

0

5

0

5

5

I 15

Аналогично обеспечивается обмен младшего байта только по младшей магистрали данных и старшего байта только по старшей магистрали.

Процесс выгрузки блока 2 оперативной памяти выполняется по тем же правилам с той разницей, что отсутствует сигнал Запись в память на шине 57. При этом в арбитре 3 памяти отсутствует сигнал на выходе 45, в результате чего накопители 36 и 37 работают не в режиме записи, а в режиме считьшания. В коммутаторах отсутствует сигнал на входах НП, в результате чего информация передается из внутренней магистрали данных во внешнюю.

Для передачи состояния устройства из БУ1 в процессор ЭВМ процессор выставляет адрес ЗВАН на адресной магистрали 28 и сигналы Чтение порта на гаине 83. Дешифратор 16 срабатьгаает от этого сигнала аналогично описанному, причем на шинах 30 и 32 образуются сигналы. Первый из тгк. через элемент ИЛИ 69 и шину 73 выбирает кристалл коммутатора 13 данных. При отсутствии сигналов Запись в порт и Запись в память комму- татор 13 данных обеспечивает направление передачи данных от внутренней магистрали данных к внешней. Сигнал по шине 32 поступает на блок, где открьшает элементы И 22 и 23, в результате чего сигналы с вьтодов DE и VS через элементы И 22 и 23, магистраль 24, коммутатор 13 и магистраль 75 поступают в процессор ЭВМ. Последний путем анализа первого сиг- нала определяет наличие обратного хода по строке или по кадру, а путем анализа второго - только по кадру, что позволяет обеспечивать обновление информации в блоке 2 опера- тивной памяти во время обратного хода развертки.

Для подготовки процеса регенерации символьного черно-белого изображения в формате 80x25 процессор ЭВМ выставляет адрес 3D8H на адресной магистрали 28, код 01 на магистрали 75 данных и сигнал Запись в порт на шине 27. Дешифратор 16 сра- батьшает аналогично описанному и сигнал по шине 84 поступает на С-вхо регистра 106 режима (вход занесения) Код 01 через магистраль 75, коммутатор 13 дант,1ч и магистраль 24 заноси

д 5

0 5 О Q .

д

5

16

ся п регистр 106. Затем процессор выставляет адрес 3D9H на магистрали 28, код 011100 на магистрали 75 и сигнал Запись в порт на шине 27. АТЫЛОГИЧНЫМ образом формируется сигнал на 1101не 85 и код наносится в регистр 17 цвета.

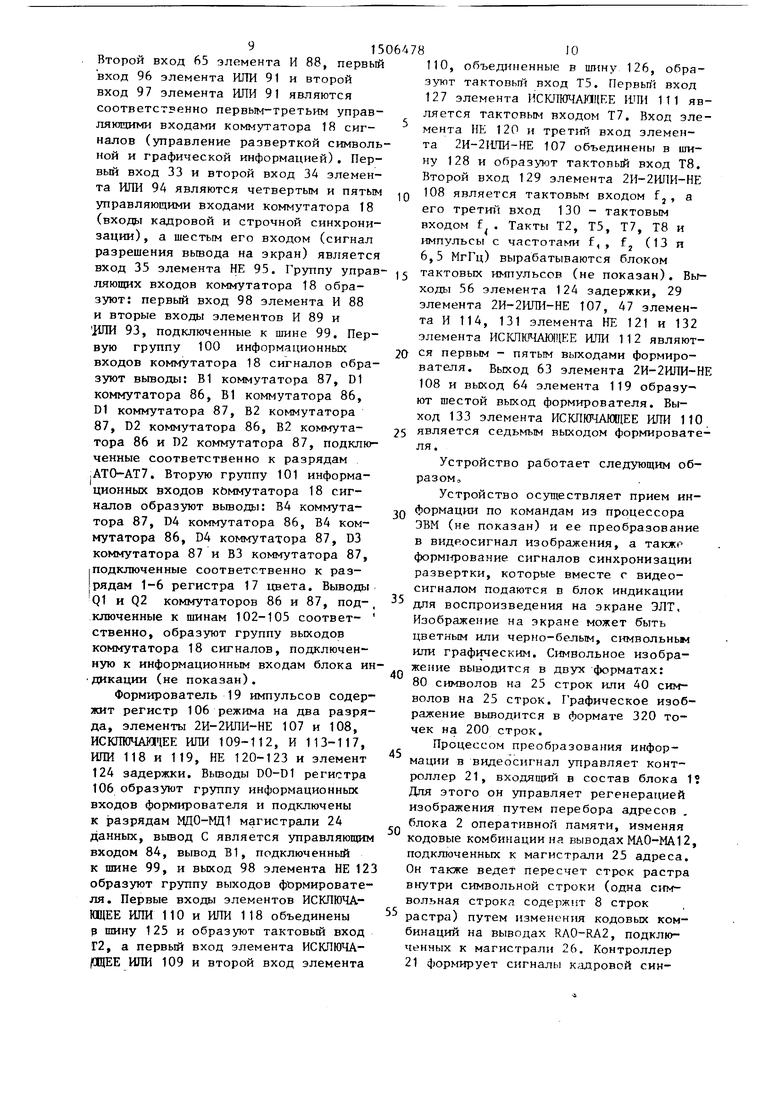

Заданное состояние регистра 106 в формттрователе 19 во взаимодействии с тактовыми сигналами S, на шине 129, fj на гшне 130, Т2 на шине 125, Т5 на шине 126, Т7 на шине 127 и Т8 на игине 1 28 определяют сигналы на выходах формирователя 19 (фиг. 13). С помощью комбинационной логики вырабатываются сигналы на следующих шинах: 131 - сигнал занесения в регистр 5 символа, формируемый элементами НЕ 120, ИСКЛЮЧАЮЩЕЕ ИЛИ 109, НЕ 121, 47 - сигнал синхронизации блока 2 оперативной памяти, формируемый элeмeн aми НЕ 120, ИСКЛЮЧАЮЩЕЕ ИЛИ 109, 124 задержки И 114; 29 - сигнал синхронизации работы котрол- лера 21, формируемьп элементами НЕ 120 ИСКЛЮЧАЕЦЕЕ ИЛИ 109, НЕ 122, 2И-2Ш1И-НЕ 107, 63 - сигнал сдвига регистров 9-11, формируемый элементами НЕ 122, 2И-2ИЛИ-НЕ 108, 133 - сигнал занесения в регистр 8 атрибутов, формируемый элементом ИСКЛЮЧА- КЩЕЕ ИЛИ 110, 64 - сигнал управления регистрами 9-11 сдвига, формируемый элементами НЕ 120, ИСКЛЮЧАЮЩЕЕ ИЛИ 111, ИЛИ 118 и 119, 132 - сигнал занесения в регистр 7 атрибутов, форми- руемьп элементами НЕ 120, ИСКЛЮЧАЮЩЕЕ ШШ 109, 124 задержки, И 115, НЕ 123, И 113, 116, 117 и ИСКЛЮЧАЮЩЕЕ 1-ШИ U2, 98 - сигнал управления комьгутатором 18.

В режиме регенерации контроллер 21 находится в процессе непрерывного перебора адресов, при выводе символов объем сканируемой памяти составляет 4К байт в графическом режиме 16К байт. Очередной адрес из контроллера 21 поступает на коммутатор 4 адреса по магистрали 25. В отсутствии сигнала Обращение к памяти на шине 54 триггер 50 нахо- в состоянии О и сигнал на тине 46 отсутствует, так что на выходе элемента НЕ 61 имеется сигнал, обеспечивающий прохождение адреса с магистрали 25 через группы 58 и 60 элементов и магистраль 44 в блок 2 оперативной памяти. Также отсутствует сигнал на шине 45 арбитра 3, в связи с чем накопители 36 и 37 находятся в режиме считьшания. В результате этого очередная пара байтов считывается из накопителей 36 и 37, причем младший байт по магистрали 24 заносится в регистр 5 символов, а старший байт по магистрали 43 заносится в регистр 8 атрибутов. При индикации каждый символ представляется матрицей строк и столбцов 8x8, Пусть атрибут данного символа 00010101. Из регистра 5 символа байт информации поступает на генератор 6 знаков, туда же из контроллера 21 по магистрали 26 поступают сигналы RAO-RA2. Генератор 6 знаков выдает в магистраль 62 байт информации, представляющий собой строку символа, номер у которой определяется комбинацией сигналов RAO-RA2. С магистрали 62 этот байт поступает на регистр 9 сдвига, который под управлением тактовых сигналов по шинам 63 и 64 осуществляет развертку байта в последовательный код, поступающий по шине 65 в коммутатор 18 сигналов.

Содержимое регистра 8 атрибутов передается в регистр 7 атрибутов и через группу 100 информационных- входов поступает в коммутатор 18 сигналов. Наличие дополнительного регистра 8 атрибутов связано с необходимостью временной задержки кода атрибута данного символа: во время вы- борки следующей пары байтов из па- мяти в регистре 9 сдвига хранится код строки данного символа, а его атрибут хранится в регистре 7.

Основой коммутатора 18 сигналов вляются два двухразрядных коммутаора 86 и 87, каждый разряд которых существляет подключение одного из етьфех входов на выход. Для адресаии входов используются входы А1 и 2, порядок выборки следующий: А2 0,А1 О - первый вход; А2 О, 1 1 - второй вход; А2 1, А1 0- трётий вход; А2 1,.А1 1 - четвертый вход.

В символьном режиме первый вход определяет цвет символа, второй вход - цвет фона и четвертый вход ,- цвет окантовки экрана. Выходы коммутатора 86 и 87 обеспечивают управление цветом по четырем каналам: шина 102 - красным цветом (R), 103

т

- 506478 8

зеленым (G), 104 - синим (В) и шина 105 - дополнительной яркостью (1).

Сигналы, подаваемые по группе 100 информационных входов, соответствуют 1ф (яркость фона), 1 (яркость ствола). В-.. В„ . G, G

to

( с ф с р ч Kj. , причем сигнал R. поступает на вывод В1 коммутатора 86. Сигналы, подаваемые по группе 101 информационных входов. Соответствуют Пал (палитра), Ф (цвет окантовки красный), Ф, Фр, Гр1 (яркость графического изображения), и Фл) (яркость окантовки),

(5 причем сигнал Ф.. поступает на вывод Д4 коммутатора 87.

Поскольку сигнал на шине 98 присутствует в ствольном режиме, управление входами А1 кo fмyтaтopoв 86 и 87

20 осуществляется сигналом на шине 65. Действительно, на входе 99 сигнал отсутствует, а на входе 35 присутствует при вьшоде символов (отсутствует при окантовке и при обратном ходе

25 луча). Управление входом А2 осущест- вляется сигналом на шине 35 через элементы НЕ 95 и ИЛИ 93 (сигнал на входах А2 коммутаторов 86 и 87 равен О во время вьгоода символов и 1 во время окантовки и обратного хода).

Таким образом, при заданных вьш1е кодах в регистрах 7 и 8 атрибутов сигналы на вькодах 102-ЮА (R,G,B; появятся за счет прохождения сигналов с группы 100 информационных входов только при индикации каждой точки символа. При индикации окантовки сигналы на выходах 102-104 появятся за счет прохождения сигналов с группы 101 входов. Во время обратного хода луча бланкирование коммутаторов 86 и 87 осуществляется по стробирующим входам С1, С2 С1|гнплами на шинах 33 (кадровая г шхронизация) и 34 (строчс ная синхронизация), поступающими из блока 1.

В результате в блок индикации по- даются сигналы всех трех основньпс цветов, что обеспечивает черно-белое позитивное изображение. Для получения негативного изображения следует

30

35

40

50

задать атрибуты символа равными О, а атрибуты фона равными 1. Исключить окантовку можно путем задания нулевых значенш во всех разрядах регистра 17 цвета. Для получения цветных изобра; Кен1п символов, фона и окантовки следует устанавливать в 1 соответствуюипте разряды регистров атрибута и цвета. Работа коммутатора 18 сигналов аналогична описанной.

Процесс регенерации символьного изображения в формате 40x25 отличается от предыдущего формата тем, что изменяются периоды ряда тактовых сигналов: по шинам 29, 64 и 132 (фиг, 13), Это обеспечивается тем, что в регистр 106 режима заносится код 00, вызывающий изменения в работе элементов 107, 108 и 122, В результате изображение каждого символа на экране увеличивается в два раза, В процессе регенерации графического изображения в регистр 106 режима заносится код 10, Работа формирователя 19 отличается от предыдущего режима тем, что появляется сигнал на шине 99, исчезает сигнал на шине 98 и изменяется временная диаграмма тактового сигнала на шине 132 (фиг, 13 В графическом режиме занесение пары байтов в регистр 5 символа и в регистры 7 и 8 атрибутов осуществляется по тем же правилам, что и в символьных режимах. Однако в информационном отношении оба байта равнозначны и используются дпя индикации восьми точек, причем дпя описания каждой точки требуется два бита,

В этом случае информация из регистра 5 символов и из регистра 7 атрибутов поступает в регистры 10 и 11 сдвига, В результате перед сдвигами в регистрах 10 и 11 содержится следующая информация (С - из регистра 5 символов, А - из регистра 7 атрибутов) : Рг10 С6-С4-С2-СО-А6-А4-А2-АО Рг11 С7-С5-СЗ-С1-А7-А5-АЗ-А1,

Вследствие этого при первом сдвиге регистров 10 и 11 в коммутатор 18 сигналов поступают разряды А1 и АО, описывающие одну графическую точку. При этом код 01 соответствует зеленому цвету, код 10 - красному, а код 11 - желтому. При наличии хотя бы одного из двух сигналов (по шинам 96 ипи 97) срабатьгаают элементы 91, 89, 90 и 92, обеспечивая отсутствие сигнала на входах А1 коммутаторов 86 и 87, Сигнал по шине 99 через элемент ИЛИ 93 поступает на входы А2, обеспечивая выборку третьих входов коммутаторов 86 и 87, Таким образом, наличие хотя бы одной 1 в коде обеспичивает изображение точки, код 00 соответствует фону.

Цвет фона, как и раньше, определяется содержимым регистра 17 цвета. Кроме того, второй и шестой разряды этого регистра участвуют в задании цвета графических точек следующим образом. При наличии сигнала Пал включается в работу канал синего цвета, изменяя цвет точек зеленый

на голубой, красный на фиолетовый

и желтый на белый. При наличии сигнала Гр1 изменяется яркость точек.

Таким образом, предпагаемое устройство обеспечивает повьш1ение быстродействия по сравнению с известным в два раза за счет обмена с процессором ЭВМ словом из двух байтов и за счет выборки слова из блока оперативной памяти при регенерации изображения (в известном устройстве работа только с байтом), Это дает возможность обеспечивать вывод на экран динамических процессов и объектов с вдвое большей скоростью перемещеНИИ и преобразований. Кроме того, устройство позволяет достичь тех же скоростей работы при использовании в блоке оперативной памяти накопите- лей с быстродействием в два раза

меньше, чем в известном устройстве,

Формула изобретения

35

40

1, Устройство дпя отображения информации, содержа1цее блок управления, блок оперативной памяти, арбитр памяти, коммутатор адреса, регистр символа, генератор знаков, перрый регистр атрибутов, три регистра сдвига, первый коммутатор данных, дешифратор, регистр цвета, коммутатор сигналов, формиро ватель импульсов и элемент ИЛИ, информационные входы первой группы коммутатора адреса и

с информационные входы дешифратора являются адресными входами устройства, информационные входы выходы первой группы первого коммутатора данных являются информационными входами-выQ ходами первой группы устройства, управляющий вход арбитра памяти является входом сигнала обращения к памяти устройства, вход управления записью арбитра памяти и первый вход элемента ИЛИ является входом сигнала записи в память устройства, второй вход элемента ИПИ, вход управления записью в порт дешифратора и вход, управления записью-чтением блока ytt5

21

равления япляются пходом сигнала записи в порт устройства, нход управле ния чтением порта дешифратора является входом сигнала чтения портов устройства, вход управления обращени ем блока управления подключен к одно му из адресных входов устройства, выход элемента ИЛИ подключен к первому управляющему входу первого коммутатора данных, выходы первой груп- блока управления соединены с информационными входами второй группы коммутатора адреса, выходы которого подключены к адресным входам блока оперативной памяти, информационные входы-выходы первой группы которого подключены к информационным входам- выходам второй группы первого коммутатора данных, соединенным с информационными входами-выходами блока управления, информационными входами формирователя импульсов и регистров цвета и символа, выходы регистра сим вола подключены к информационным вхо дам первых групп второго и третьего регистров сдвига-и адресным входам первой группы генератора знаков, адресные входы второй группы которого соединены с выходами второй группы блока управления, выходы генератора знаков подключены к информационным входам первого регистра сдвига, информационные входы вторых групп второго и третьего регистров сдвига соединены с выходами первого регистра, .атрибутов, подключенными к информа- ционным входам первой группы коммутатора сигналов, информационные входы второй группы которого соединены -с выходами регистра цвета, вход управления разверткой символьной инфор мации и первый и второй входы управления разверткой графической информации подключены соответственно к выходам первого, второго и третьего регистров сдвига, входы кадровой и строчной синхронизации - к первому и второму выходам блока управления соответственно, вход сигнала разрешения вьшода информации на экран - к третьему выходу блока управления, входы управления вьтодом информации с выходами группы формирователя импульсов, выходы коммутатора сигналов являются информационными выходами устройства, синхровыходами которого являются первьш и второй выходы блока упрагления, первьй и второй выхоS06478

ды дешифратора ссюдинеиы с - отиетственно со стробируюиппч входом и пходом управления выборкой блока утгравления, трет1ш и четвертый выходы дешифратора подключены к управляющшч входам соответственно регистра цвета и формирователя импульсов, nepBbrti, нторой и третт выходы которого соединены с Q тактовыми входами соответственно арбитра памяти, блока управления и блока oпepaт roнoй памяти, четвертый выход - с управляющим входом регистра символа, nnTbfi выход - с управля- )5 ющим входом первого регистра атрибутов, шестой выход - с управляюйц ми входами регистров сдвига, первый выход арбитра памяти соединен с управляющим входом коммутатора адреса, 20 а второй выход - с входом управления записью блока оперативной памяти, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок дешифра - 25 Ции, второй и третш коммутаторы данных и второй регистр атрибутов, управляющий вход которого соединен с седьмым вькодом формирователя им- пульсов, а выходы - с информацион- jg ными входами первого регистра атрибутов, первые управляющие входы второго и третьего коммутаторов данных соединены с входом сигнала записи в устройства, первый, второй и третий выходы блока дешифрации соединены с вторыми управляющими входами соответственно первого, второго-и третьего коммутаторов данных, информационные входы-выходы первой группы второго Q коммутатора данных соединены с информационными входами-выходами первой группы устройства, информационные входы-выходы nepfsofi группы третьего коммутатора данных являются информа- .. ционными входами-выходами второй группы устройства, информационные входы-выходы вторых групп второго и третьего коммутаторов данных подключены к информационным входам-вы- CQ ходам второй группы блока оперативной памяти(Соединенным с информационными входами второго регистра атрибутов, управляющий вход блока оперативной памяти соединен с первым выходом арбитра памяти, а вход управления выбором накопителя - с четвертым выходом блока дешифрац1ти, вход управления обращением к памяти которого соединен с входом сигнала обращения

35

55

к памяти устройства, первый управляющий вход является управляющим входом устройства, адресный вход соединен с одним из адресных входов устройства, а второй управляющий -вход соединен с первым выходом дешифратора.

3,Устройство по п. 1, отличающееся тем, что блок дешиф

рации содержит деш1«})ратор и четыре элемента ИЛИ, управляющий вход дешифратора является входом управления обращением к памяти блока, информационные входы дешифратора являются (Соответственно первым .управляющим и адресным входами блока, первый выход дешифратора подключен к первому входу первого элемента ИЛИ, второй вход которого и первый вход второго элемента ИЛИ подключены к третьему выходу дешифратора, четвертый выход которого подключен к второму входу

второго элемента ИЛИ, выход первого элемента ИЛИ подключен к первому входу третьего элемента ИЛИ, второй вход которого является вторым управляющим входом блока, первым, вторым

и третьим выходами блока являются

соответственно выход третьего элемента ИЛИ, второй выход дешифратора и выход второго элемента ИЛИ, входы четвертого элемента ИЛИ подключены

к второму выходу дешифратора и выходу второго элемента ИЛИ, выходы первого и четвертого элементов ИЛИ являются четвертым выходом блока.

aif Е

f

k5

//S Я4/

1

г

23

I

J5

/« J5

«г.5

гг.4Фы,г.5

ае.7

7S

ФирЗ

u|sg5g|ggigg g|

5

( I о

ер Ua о ча

6 о

§

I1

ts|5 ag|:5 1g gg|

%

.OOOOwOOOOOvO

Фиг. 12

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Адаптер цветного графического монитора персонального ; омпьютера IBM PC XT | |||

| - Techical Reference, IBM, Personal Computer XT, Hardware Reference Library., 1985. | |||

Авторы

Даты

1989-09-07—Публикация

1986-12-26—Подача