(21)4170474/24-24

(22)30.12,86

(46) 30.11.88. Бюл. № 44

(72) В.Я.Пыхтин, А.Н.Чистяков,

В.М.Григоренко и Е.Н.Воробей

(53)681.327.11(088.8)

(56) Патент Великобритании № 15631 65, кл. G 06 F 3/153, опубик. 1980.

Патент Великобритании № 2104356, кл. G 06 F 3/153, опублик. 1983.

(54)УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ

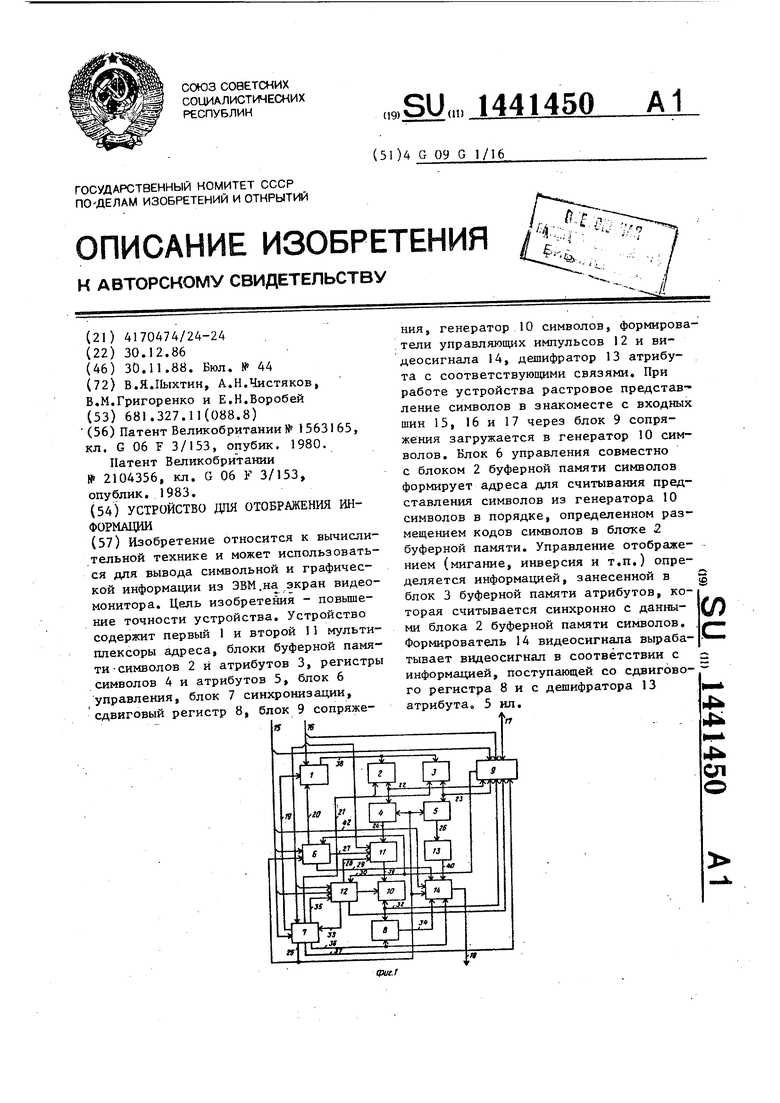

(57) Изобретение относится к вычислительной технике и может использоваться для вывода символьной и графической информации из ЭВМ.на экран видеомонитора. Цель изобретения - повьппе- ние точности устройства. Устройство содержит первый 1 и второй 11 мультиплексоры адреса, блоки буферной памяти -символов 2 и атрибутов 3, регистры символов 4 и атрибутов 5, блок 6 управления, блок 7 синхронизации, сдвиговый регистр 8, блок 9 сопряжения, генератор 10 символов, формирова- .тели управляющих импульсов 12 и видеосигнала 14, дешифратор 13 атрибута с соответствующими связями. При работе устройства растровое представление символов в знакоместе с входных шин 15, 16 и 17 через блок 9 сопряжения загружается в генератор 10 символов. БЛОК 6 управления совместно с блоком 2 буферной памяти символов формирует адреса для считывания представления символов из генератора 10 символов в порядке, определенном размещением кодов символов в блоке 2 буферной памяти. Управление отображе- - нием (мигание, инверсия и т.п.) определяется информацией, занесенной в § блок 3 буферной памяти атрибутов, ко- торая считывается синхронно с данны- f/J ми блока 2 буферной памяти символов. Формирователь 14 видеосигнала вырабатывает видеосигнал в соответствии с информацией, поступающей со сдвигово-. го регистра 8 и с дешифратора 13 атрибута 5 ил.J

ntia СП

Изобретение относится к вычислительной технике и может быть использовано для вывода символьной и графической информагши из ЭВМ на экран видеомонитора,

Цель изобретения - повышение точности устройства.

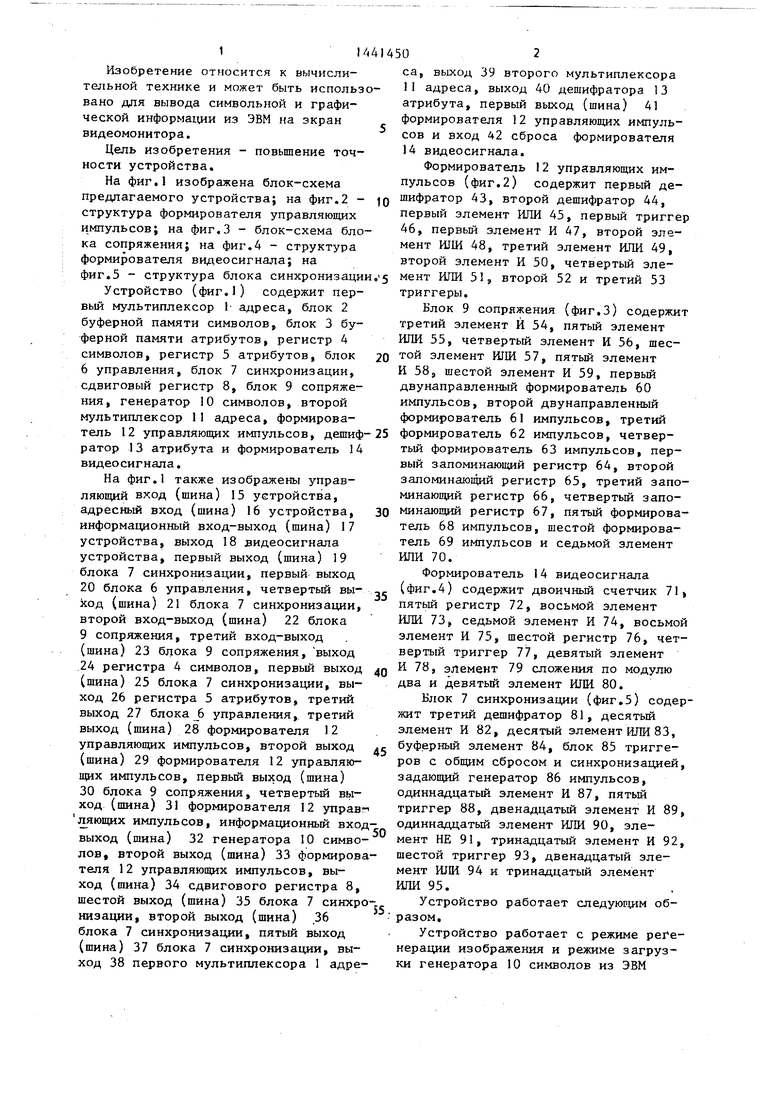

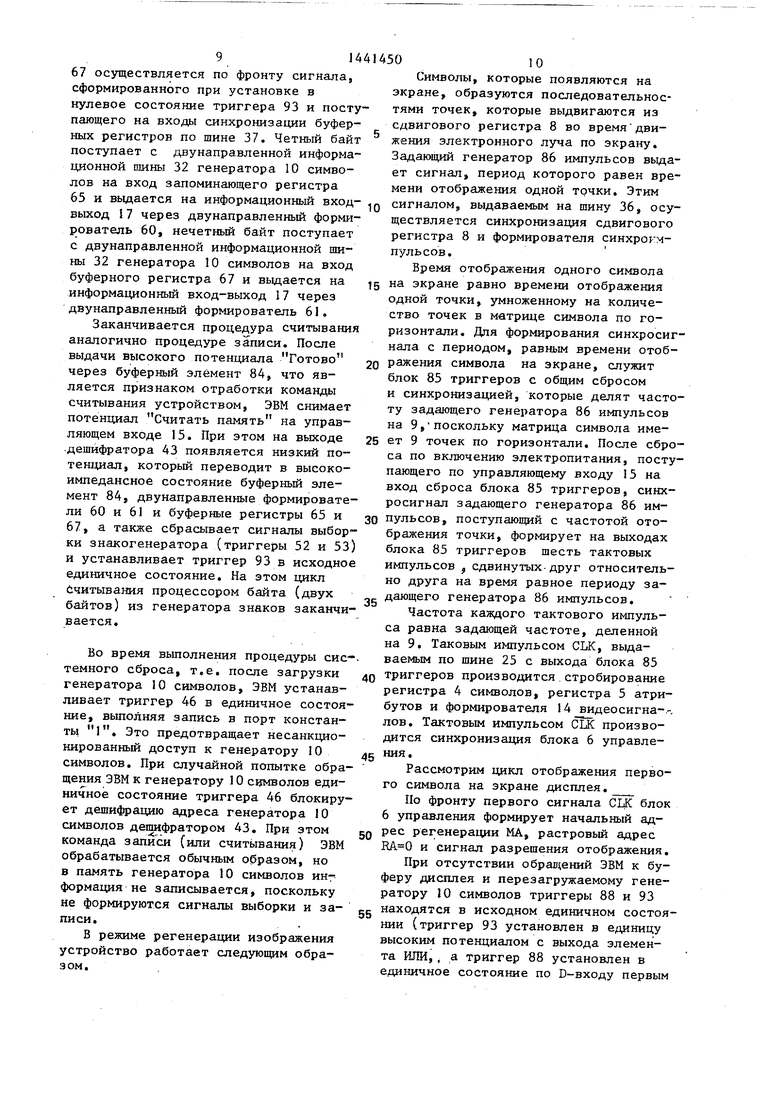

На фиг,1 изображена блок-схема предлагаемого устройства; на фиг.2 - структура формирователя управляющих и.мпульсов; на фиг.З - блок-схема блока сопряжения; на фиг.4 - структура формирователя видеосигнала; на фиг.5 - структура блока синхронизации

Устройство (фиг.1) содержит первый мультиплексор 1- адреса, блок 2 буферной памяти символов, блок 3 буферной памяти атрибутов, регистр 4 символов, регистр 5 атрибутов, блок 6 управления, блок 7 синхронизации, сдвиговый регистр 8, блок 9 сопряжения, генератор 10 символов, второй мультиплексор 1I адреса, формирователь 12 управляющих импульсов, дешифратор 13 атрибута и формирователь 14 видеосигнала.

На фиг.1 также изображены управляющий вход (щина) 15 устройства, адресный вход (шина) 16 устройства, информационный вход-выход (шина) 17 устройства, выход 18 видеосигнала устройства, первый выход (шина) 19 блока 7 синхронизации, первый выход 20 блока 6 управления, четвертый вы- ход (шина) 21 блока 7 синхронизации, второй вход-выход (шина) 22 блока 9 сопряжения, третий вход-выход (шина) 23 блока 9 сопряжения, выход .24 регистра 4 символов, первый выход (шина) 25 блока 7 синхронизации, выход 26 регистра 5 атрибутов, третий выход 27 блока 6 управления, третий выход (шина) 28 формирователя 12

управляющих импульсов, второй выход

(шина) 29 формирователя 12 управляющих импульсов, первый выход (шина) 30 блока 9 сопряжения, четвертый выход (шина) 31 формирователя 12 управ ляющих импульсов, информационный вхо выход (шина) 32 генератора 10 символов, второй выход (шина) 33 формировтеля 12 управляющих импульсов, выход (шина) 34 сдвигового регистра 8, шестой выход (шина) 35 блока 7 синхрнизации, второй выход (шина) 36 блока 7 синхронизации, пятый выход (шина) 37 блока 7 синхронизации, выход 38 первого мультиплексора 1 адре

0 5

0 с д

с

0

5

са, выход 39 второго мультиплексора II адреса, выход 40 дешифратора 13 атрибута, первый выход (шина) 41 формирователя 12 управляющих и fflyль- сов и вход 42 сброса формирователя 14 видеосигнала.

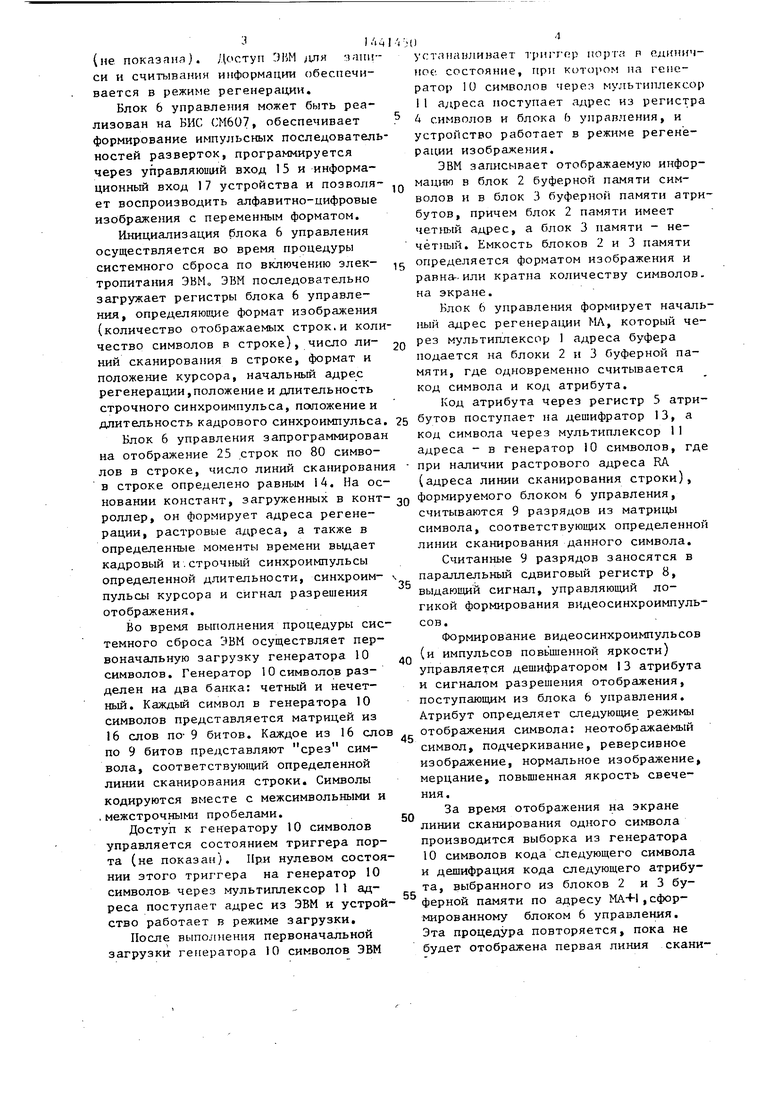

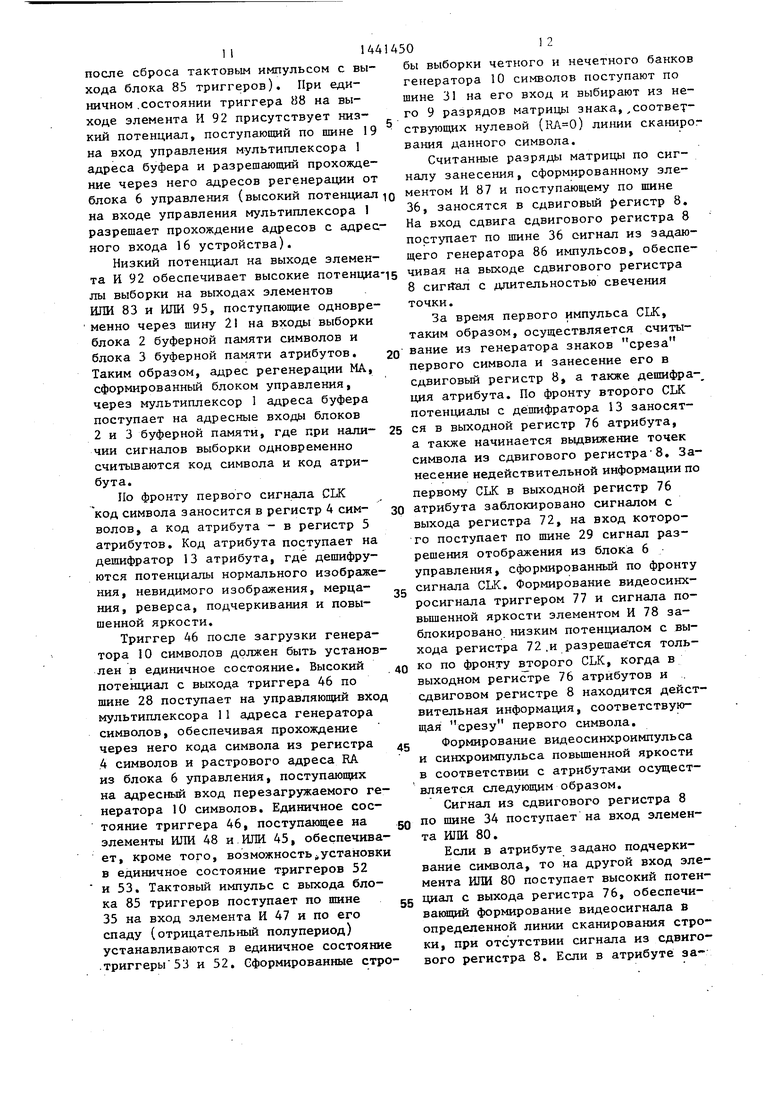

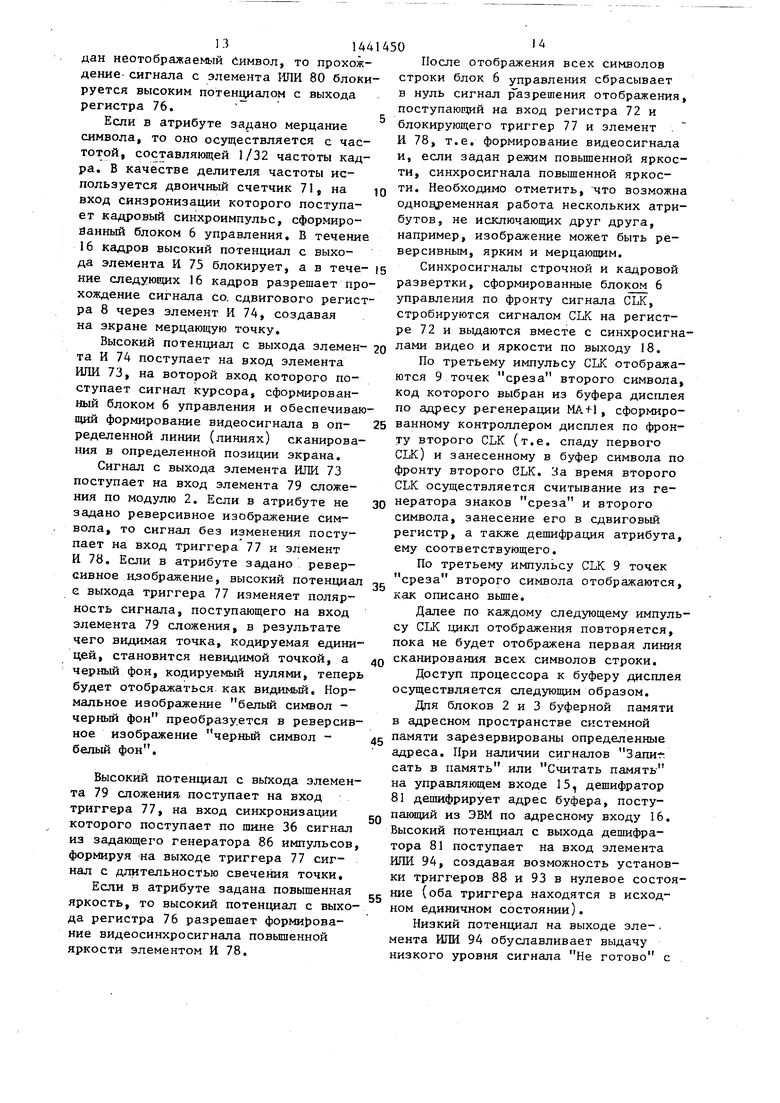

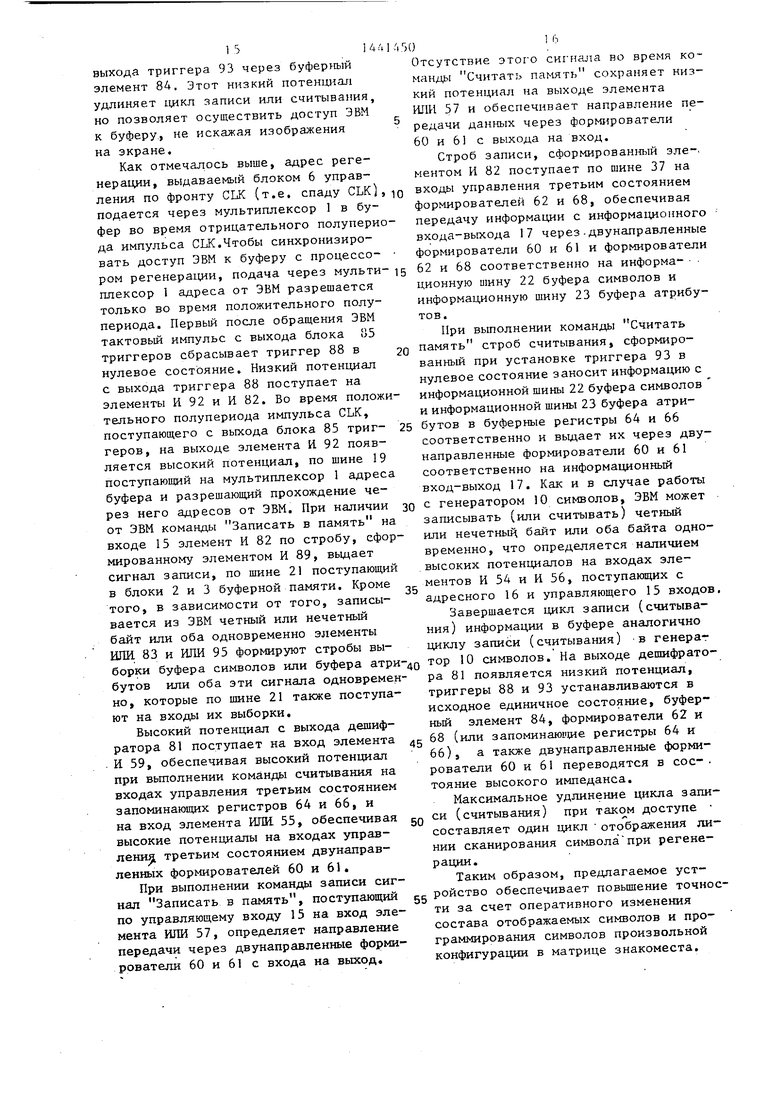

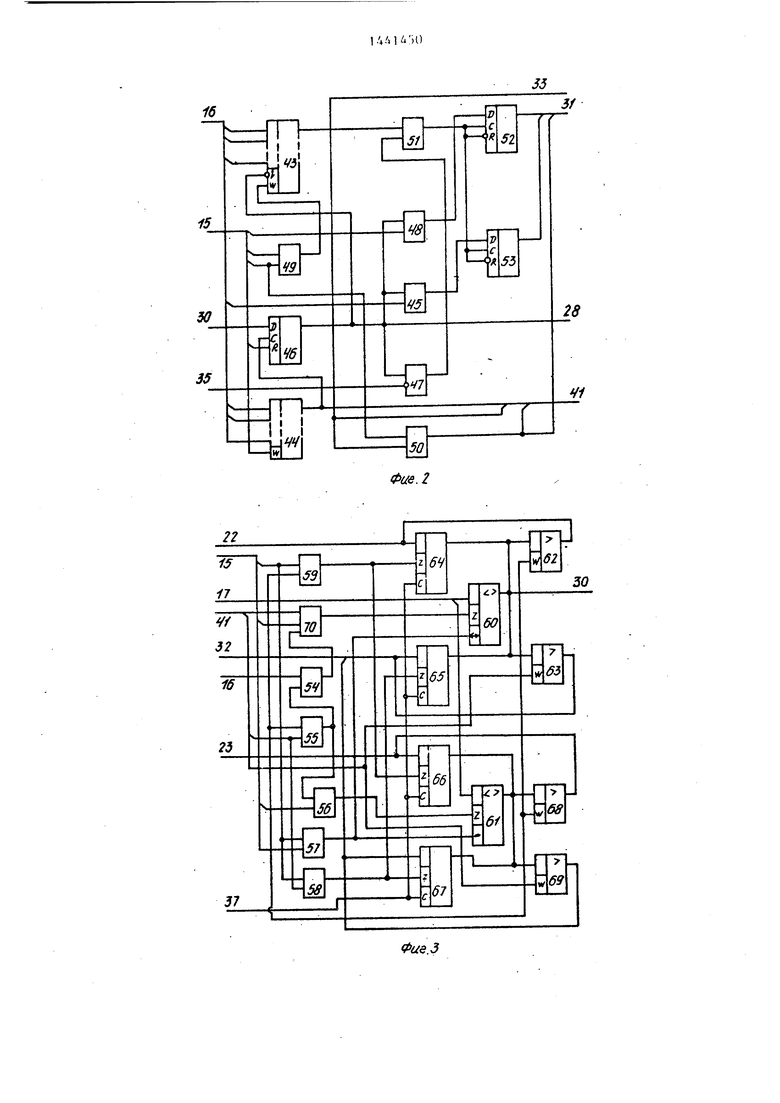

Формирователь 12 управляющих импульсов (фиг.2) содержит первый дешифратор 43, второй дешифратор 44, первый элемент ИЛИ 45, первьй триггер 46, первый элемент И 47, второй элемент ШШ 48, третий элемент ИЛИ 49, второй элемент И 50, четвертый элемент ШШ 51, второй 52 и третий 53 триггеры.

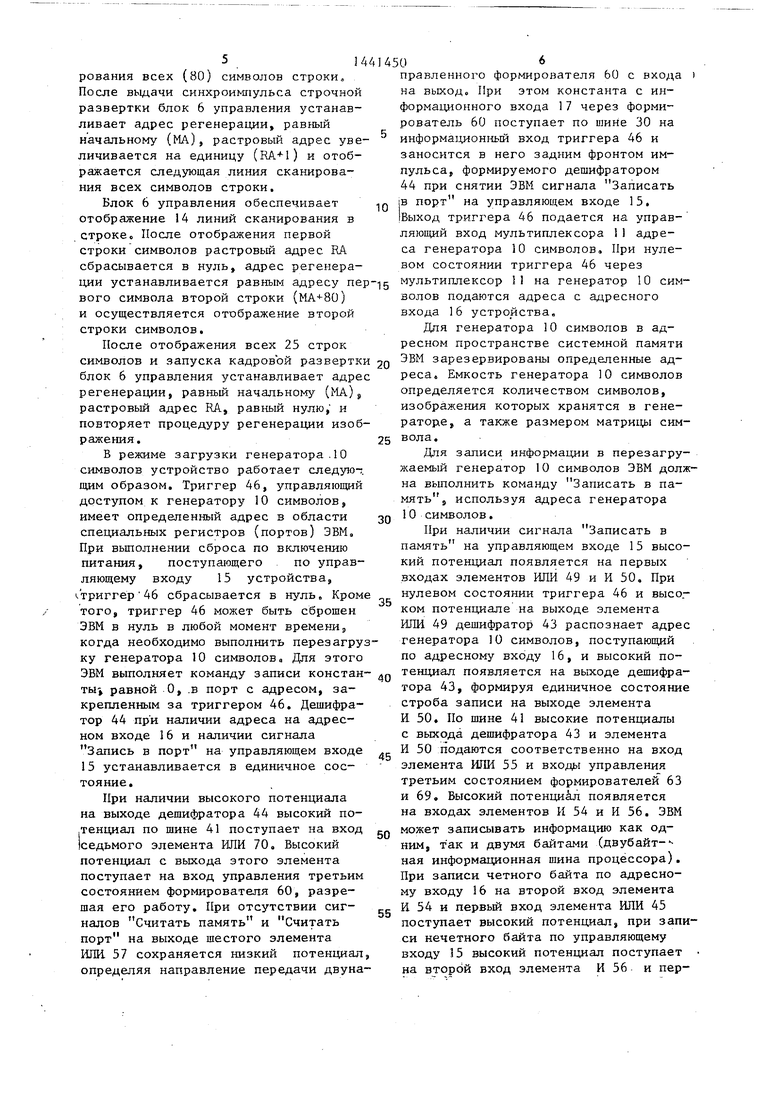

Блок 9 сопряжения (фиг.З) содержит третий элемент И 54, пятый элемент ИЛИ 55, четвертый элемент И 56, шестой элемент ШШ 57, пятый элемент И 58, шестой элемент И 59, первый двунаправленный формирователь 60 импульсов, второй двунаправленный формирователь 61 импульсов, третий формирователь 62 импульсов, четвертый формирователь 63 импульсов, первый запоминающий регистр 64, второй запоминающий регистр 65, третий запоминающий регистр 66, четвертьш запоминающий регистр 67, пятый формирователь 68 импульсов, шестой формирователь 69 импульсов и седьмой элемент ИЛИ 70.

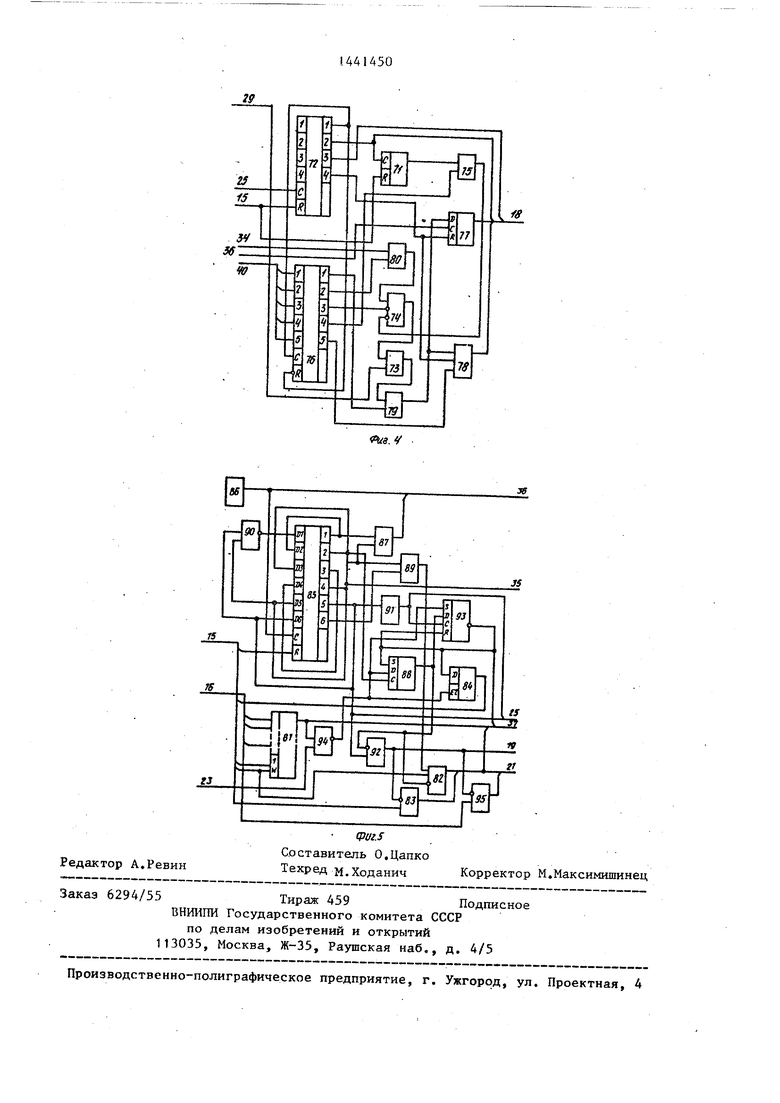

Формирователь 14 видеосигнала (фиг.4) содержит двоичный счетчик 71, пятый регистр 72, восьмой элемент ИЛИ 73, седьмой элемент И 74, восьмой элемент И 75, шестой регистр 76, четвертый триггер 77, девятый элемент И 78, элемент 79 сложения по модулю два и девятый элемент ИЛИ 80.

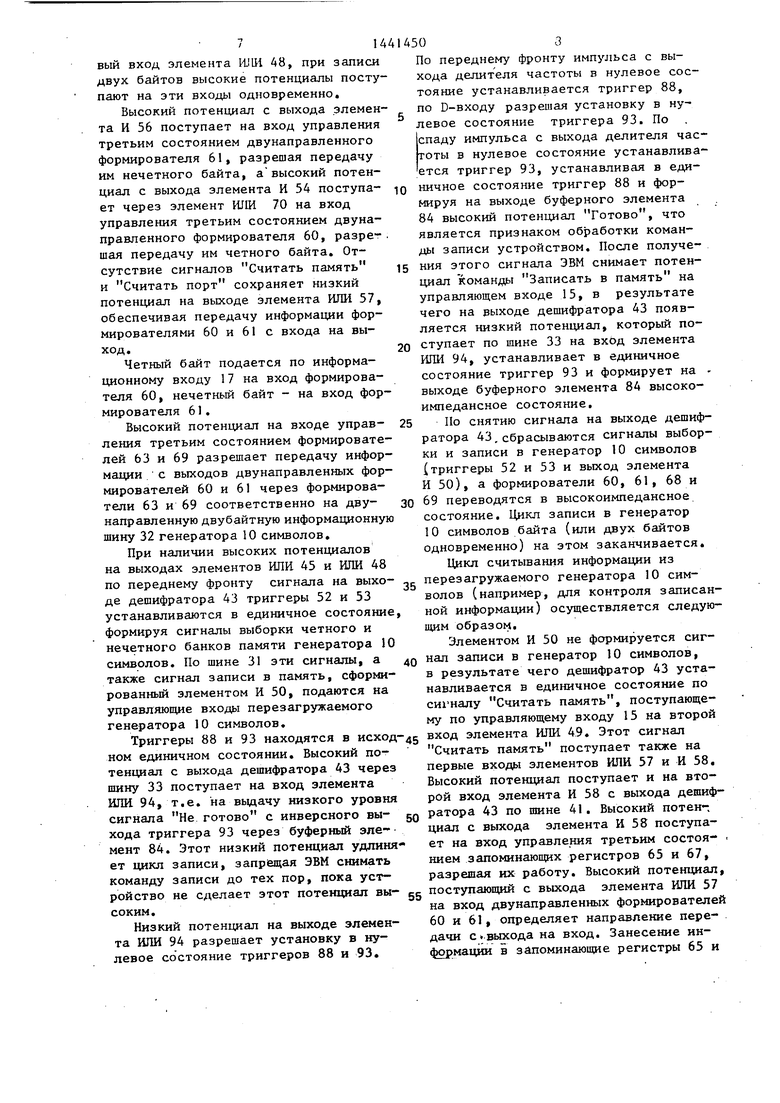

Блок 7 синхронизации (фиг.5) содержит третий дешифратор 81, десятый элемент И 82, десятый элемент ИЛИ 83, буферный элемент 84, блок 85 триггеров с общим сбросом и синхронизацией, задающий генератор 86 импульсов, одиннадцатый элемент И 87, пятый триггер 88, двенадцатый элемент И 89, одиннадцатый элемент ИЛИ 90, элемент НЕ 91, тринадцатый элемент И 92, шестой триггер 93, двенадцатый элемент ИЛИ 94 и тринадцатый элемент ИЛИ 95.

Устройство работает следуюрц м образом.

Устройство работает с режиме регенерации изображения и режиме загрузки генератора 10 символов из ЭВМ

l- .

(не показана). Доступ )ИМ для чаииси и считывании информации обеспечивается в режиме регенераиу и.

Блок 6 управления может быть реализован на БИС СМ607, обеспечивает формирование импульсных последовательностей разверток, программируется через управляющий вход 15 и информационный вход 17 устройства и позволя- ет воспроизводить алфавитно-цифровые изображения с переменным форматом.

Инициализация блока 6 управления осуществляется во время процедуры системного сброса по включению злек- тропитания ЭВМ ЭВМ последовательно загружает регистры блока 6 управления, определяющие формат изображения (количество отображаемых строк.и количество символов в строке), число ли- кий сканирования в строке, формат и положение курсора, начальный адрес регенерации,положение и дпительность строчного синхроимпульса, положение и длительность кадрового синхроимпульса

Блок 6 управления запрограммирован на отображение 25 строк по 80 символов в строке, число линий сканировани в строке определено равным 14. На основании констант, загруженных в конт- роллер, он формирует адреса регенерации, растровые адреса, а также в определенные моменты времени выдает кадровый и.строчный синхроимпульсы определенной длительности, синхроим- пульсы курсора и сИгнал разрешения отображения.

Во время выполнения процедуры системного сброса ЭВМ осуществляет первоначальную загрузку генератора 10 символов. Генератор 10 символов разделен на два банка: четный и нечетный. Каждый символ в генератора 10 символов представляется матрицей из 16 слов по- 9 битов. Каждое из 16 слов по 9 битов представляют срез символа, соответствуюнщй определенной линии сканирования строки. Символы кодируются вместе с межсимвольными и .межстрочными пробелами.

Доступ к генератору 10 символов управляется состоянием триггера порта (не показан). При нулевом состоянии этого триггера на генератор 10 СИМВОЛОВ- через мультиплексор 11 адреса поступает адрес из ЭВМ и устройство работает в режиме загрузки.

После выпо нения первоначальной загрузки reFieparopa 10 символов ЭВМ

,.

о 5

о

,.

5

5

Ч)

)наилинаег тригг пр порта Р единичное состояние, при котором на генератор 10 символов через мультиплексор 11 адреса поступает адрес из регистра 4 символов и блока Ь управления, и устройство работает в режиме регенерации изображения.

ЭВМ записывает отображаемую инфор- мащт в блок 2 буферной памяти символов и в блок 3 буферной памяти атрибутов, причем блок 2 памяти имеет четный адрес, а блок 3 памяти - нечетный. Емкость блоков 2 и 3 памяти определяется форматом изображения и равна-, или кратна количеству символов, на экране,

БЛОК 6 управления формирует начальный адрес peгeнepaц и МЛ, который через мультиплексор 1 адреса буфера подается на блоки 2 и 3 буферной памяти, где одновременно считывается код символа и код атрибута.

Код атрибута через регистр 5 атрибутов поступает на дешифратор 13, а код символа через мультиплексор 11 адреса - в генератор 10 символов, где при наличии растрового адреса RA (адреса линии сканирования строки), формируемого блоком 6 управления, считываются 9 разрядов из матрицы символа, соответствующих определенной линии сканирования данного символа.

Считанные 9 разрядов заносятся в параллельный сдвиговый регистр 8, выдающий сигнал, управляющий логикой формирования видеосинхроимпульсов.

Формирование видеосинхроимпульсов (и импульсов повьш1енной яркости) управляется дешифратором 13 атрибута и сигналом разрешения отображения, поступающим из блока 6 управления. Атрибут определяет следующие режимы отображения символа: неотображаёмый символ, подчеркивание, реверсивное изображение, нормальное изображение, мерцание, повьш1енная якрость свечения.

За время отображения на экране линии сканирования одного символа производится выборка из генератора 10 символов кода следующего символа и дешифрация кода следующего атрибута, выбранного из блоков 2 и 3 буферной памяти по адресу МА-4-1 , сформированному блоком 6 управления. Эта процедура повторяется, пока не будет отображена первая линия скани5 .144

рования всех (80) символов строки, После выдачи синхроимпульса строчной развертки блок 6 управления устанавливает адрес регенерации, равный

4506

правленно1 О формирователя 60 с входа на выход. При этом константа с информационного входа 17 через формирователь 60 поступает по шине 30 на

начальному (МА), растровый адрес уве- информаи юнный вход триггера 46 и

10

личивается на единицу () и отображается следующая линия сканирования всех символов строки.

Блок 6 управления обеспечивает отображение 14 линий сканирования в строке После отображения первой строки символов растровый адрес RA сбрасывается в нуль, адрес регенерации устанавливается равным адресу пер-|5 вого символа второй строки () и осуществляется отображение второй строки символов.

После отображения всех 25 строк

символов и запуска кадровой развертки 2о зарезервированы определенные ад- Емкость генератора 10 символов

заносится в него задним фронтом импульса, формируемого дешифратором 44 при снятии ЭВМ сигнала Записать в порт на управляющем входе 15, Выход триггера 46 подается на управляющий вход мультиплексора 11 адреса генератора 10 символов. При нулевом состоянии триггера 46 через мультиплексор 1 на генератор 10 сим волов подаются адреса с адресного входа 16 устройства.

Для генератора 10 символов в адресном пространстве системной памяти

25

30

35

блок 6 управления устанавливает адрес регенерации, равный начальному (МА) растровый адрес RA., равньй нулю, и повторяет процедуру регенерации изображения.

В режиме загрузки генератора. 10 символов устройство работает следую-:, щим образом. Триггер 46, управляющий доступом к генератору 10 символов, имеет определенный адрес в области специальных регистров (портов) ЭВМ, При выполнении сброса по включению питания, поступающего по управляющему входу 15 устройства, «-триггер 46 сбрасывается в нуль Кроме того, триггер 46 может быть сброшен ЭВМ в нуль в любой момент времени;, когда необходимо выполнить перезагрузку генератора 10 символов а Для этого ЭВМ выполняет команду записи констан- |Q ты% равной О, .в порт с адресом, закрепленным за триггером 46. Дешифратор 44 при наличии адреса на адресном входе 16 и наличии сигнала Запись в порт на управляющем входе 15 устанавливается в единичное состояние.

При наличии высокого потенциала на выходе дешифратора 44 высокий по- ,тенциал по шине 41 поступает на вход юедьмого элемента ИЛИ 70, Высокий потенциал с выхода этого элемента поступает на вход управления третьим состоянием формирователя 60, разрешая его работу. При отсутствии сигналов Считать память и Считать порт на выходе шестого элемента ИЛИ. 57 сохраняется низкий потенциал, определяя направление передачи двуна45

50

55

реса,

определяется количеством символов, изображения которых хранятся в генераторе, а также размером матрицы сим вола.

Для записи информации в перезагружаемый генератор 10 символов ЭВМ долж на выполнить команду Записать в память, используя адреса генератора 10 символов.

При наличии сигнала Записать в память на управляющем входе 15 высокий потенциал появляется на первых входах элементов ИЛИ 49 и И 50, При нулевом состоянии триггера 46 и высо.- ком потенциале на выходе элемента ИЛИ 49 дешифратор 43 распознает адре генератора 10 символов, поступающий по адресному входу 16, и высокий потенциал появляется на выходе дешифратора 43, формируя единичное состояние строба записи на выходе элемента И 50 По шине 41 высокие потенциалы с выхода дешифратора 43 и элемента И 50 подаются соответственно на вход элемента ИЛИ 55 и входы управления третьим состоянием формирователей 63 и 69. Высокий потенциал появляется на входах элементов И 54 и И 56. ЭВМ может записывать информацию как одним, т ак и двумя байтами (двубайт- - ная информационная шина процессора). При записи четного байта по адресному входу 16 на второй вход элемента И 54 и первьш вход элемента ИЛИ 45 поступает высокий потенциал, при запи си нечетного байта по управляющему входу 15 высокий потенциал поступает на второй вход элемента И 56 и пер4506

правленно1 О формирователя 60 с входа на выход. При этом константа с информационного входа 17 через формирователь 60 поступает по шине 30 на

информаи юнный вход триггера 46 и

0

|5

заносится в него задним фронтом импульса, формируемого дешифратором 44 при снятии ЭВМ сигнала Записать в порт на управляющем входе 15, Выход триггера 46 подается на управляющий вход мультиплексора 11 адреса генератора 10 символов. При нулевом состоянии триггера 46 через мультиплексор 1 на генератор 10 символов подаются адреса с адресного входа 16 устройства.

Для генератора 10 символов в адресном пространстве системной памяти

зарезервированы определенные ад- Емкость генератора 10 символов

реса,

определяется количеством символов, изображения которых хранятся в генераторе, а также размером матрицы символа.

Для записи информации в перезагружаемый генератор 10 символов ЭВМ должна выполнить команду Записать в память, используя адреса генератора 10 символов.

При наличии сигнала Записать в память на управляющем входе 15 высокий потенциал появляется на первых входах элементов ИЛИ 49 и И 50, При нулевом состоянии триггера 46 и высо.- ком потенциале на выходе элемента ИЛИ 49 дешифратор 43 распознает адрес генератора 10 символов, поступающий по адресному входу 16, и высокий потенциал появляется на выходе дешифратора 43, формируя единичное состояние строба записи на выходе элемента И 50 По шине 41 высокие потенциалы с выхода дешифратора 43 и элемента И 50 подаются соответственно на вход элемента ИЛИ 55 и входы управления третьим состоянием формирователей 63 и 69. Высокий потенциал появляется на входах элементов И 54 и И 56. ЭВМ может записывать информацию как одним, т ак и двумя байтами (двубайт- - ная информационная шина процессора). При записи четного байта по адресному входу 16 на второй вход элемента И 54 и первьш вход элемента ИЛИ 45 поступает высокий потенциал, при записи нечетного байта по управляющему входу 15 высокий потенциал поступает на второй вход элемента И 56 и первый вход элемента RlUi 48, при записи двух байтов высокие потенциалы поступают на эти входы одновременно.

Высокий потенциал с выхода элемента И 56 поступает на вход управления третьим состоянием двунаправленного формирователя 61, разрешая передачу им нечетного байта, а высокий потенциал с выхода элемента И 54 поступает через элемент ИЛИ 70 на вход управления третьим состоянием двунаправленного формирователя 60, разре- шая передачу им четного байта. Отсутствие сигналов Считать память и Считать порт сохраняет низкий потенциал на выходе элемента ИЛИ 57, обеспечивая передачу информации формирователями 60 и 61 с входа на выход.

Четный байт подается по информационному входу 17 на вход формирователя 60, нечетный байт - на вход формирователя 61.

Высокий потенциал на входе управления третьим состоянием формирователей 63 и 69 разрешает передачу информации с выходов двунаправленных формирователей 60 и 61 через формирователи 63 и 69 соответственно на двунаправленную двубайтную информационную шину 32 генератора 10 символов.

При наличии высоких потенциалов на выходах элементов ИЛИ 45 и ИЛИ 48 по переднему фронту сигнала на выходе дешифратора 43 триггеры 52 и 53 устанавливаются в единичное состояние формируя сигналы выборки четного и нечетного банков памяти генератора 10 символов. По шине 31 эти сигналы, а также сигнал записи в память, сформированный элементом И 50, подаются на управляющие входах перезагружаемого генератора 10 символов.

5

0

По переднему фронту импульса с выхода делителя частоты в нулевое состояние устанавливается триггер 88, по D-входу разрешая установку в нулевое состояние триггера 93. По спаду импульса с выхода делителя час- готы в нулевое состояние устанавливается триггер 93, устанавливая в единичное состояние триггер 88 и формируя на выходе буферного элемента 84 высокий потенциал Готово, что является признаком обработки команды записи устройством. После получения этого сигнала ЭВМ снимает потенциал команды Записать в память на управляющем входе 15, в результате чего на выходе дешифратора 43 появляется низкий потенциал, который поступает по шине 33 на вход элемента ИЛИ 94, устанавливает в единичное состояние триггер 93 и формирует на - выходе буферного элемента 84 высоко- импедансное состояние.

По снятию сигнала на выходе дешифратора 43,сбрасываются сигналы выборки и записи в генератор 10 символов (триггеры 52 и 53 и выход элемента И 50), а формирователи 60, 61, 68 и 0 69 переводятся в высокоимпедансное состояние. Цикл записи в генератор 10 символов байта (или двух байтов одновременно) на этом заканчивается.

Цикл считывания информации из перезагружаемого генератора 10 символов (например, для контроля записанной информации) осуществляется следующим образом.

Элементом И 50 не формируется сигнал записи в генератор 10 символов, в результате чего дешифратор 43 устанавливается в единичное состояние по сих налу Считать память, поступающему по управляющему входу 15 на второй

5

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1990 |

|

SU1795510A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство для сопряжения электронно-вычислительной машины с табло индикации | 1984 |

|

SU1211739A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Триггеры 88 и 93 находятся в исход- б вход элемента ИЛИ 49. Этот сигнал ном единичном состоянии. Высокий по- Считать память поступает также на

тенциал с выхода дешифратора 43 через шину 33 поступает на вход элемента ИЛИ 94, т.е. на выдачу низкого уровня сигнала Не готово с инверсного выхода триггера 93 через буферный эле- мент 84. Этот низкий потенциал удлиня ет цикл записи, запрещая ЭВМ снимать команду записи до тех пор, пока уст-

50

первые входы элементов ИЛИ 57 и И 58. Высокий потенциал поступает и на второй вход элемента И 58 с выхода дешифратора 43 по шине 41. Высокий потенциал с выхода элемента И 58 поступает на вход управления третьим состоя- . нием запоминающих регистров 65 и 67, разрешая их работу. Высокий потенциал,

ройство не сделает этот потенциал вы- gg поступающий с выхода элемента ИЛИ 57 соким.на вход двунаправленных формирователей

Низкий потенциал на выходе элемен- 60 и 61, определяет направление пере- та ИЛИ 94 разрешает установку в ну- дачи с выхода на вход. Занесение инлевое состояние триггеров 88 и 93.

первые входы элементов ИЛИ 57 и И 58. Высокий потенциал поступает и на второй вход элемента И 58 с выхода дешифратора 43 по шине 41. Высокий потенциал с выхода элемента И 58 поступает на вход управления третьим состоя- . нием запоминающих регистров 65 и 67, разрешая их работу. Высокий потенциал,

формации в запоминающие регистры 65 и

9144145010

67 осуществляется по фронту сигнала, Символы, которые появляются на сформированного при установке в экране, образуются последовательное- нулевое состояние триггера 93 и поступающего на входы синхронизации буфер10

тями точек, которые выдвигаются из сдвигового регистра 8 во время движения электронного луча по экрану, Задаквдий генератор 86 импульсов выдает сигнал, период которого равен времени отображения одной точки. Этим сигналом, выдаваемым на шину 36, осуществляется синхронизация сдвигового регистра 8 и формирователя синхроимпульсов .

Время отображения одного символа

5 на экране равно времени отображения одной точки, умноженному на количество точек в матрице символа по горизонтали. Для формирования синхросигнала с периодом, равным времени отоб20 ражения символа на экране, служит блок 85 триггеров с общим сбросом и синхронизацией, которые делят частоту задающего генератора 86 импульсов на 9,поскольку матрица символа име25 ет 9 точек по горизонтали. После сброса по включению электропитания, поступающего по управляющему входу 15 на вход сброса блока 85 триггеров, синхросигнал задающего генератора 86 им30 пульсов, поступающий с частотой отображения точки, формирует на выходах блока 85 триггеров шесть тактовых импульсов , сдвинутых-друг относительно друга на время равное периоду задающего генератора 86 импульсов.

Частота каждого тактового импульса равна задающей частоте, деленной на 9. Таковым импульсом CLK, выдаВо время выполнения процедуры сие-. ваемым по шине 25 с выхода блока 85 темного сброса, т.е. после загрузки о триггеров производится стробирование генератора 10 символов, ЭВМ устанав- регистра 4 символов, регистра 5 атрибутов и формирователя 14 видеосигна--. лов. Тактовым импульсом CLK произвоных регистров по шине 37. Четный байт поступает с двунаправленной информационной пшны 32 генератора 10 символов на вход запоминающего регистра 65 и выдается на информационный вход- выход 17 через двунаправленный формирователь 60, нечетный байт поступает с двунаправленной информационной шины 32 генератора 10 символов на вход буферного регистра 67 и выдается на информационный вход-выход 17 через двунаправленный формирователь 61.

Заканчивается процедура считывания аналогично процедуре записи. После выдачи высокого потенциала Готово через буферный элемент 84, что является признаком отработки команды считывания устройством, ЭВМ снимает потенциал Считать память на управляющем входе 15. При этом на выходе дешифратора 43 появляется низкий потенциал, которьш переводит в высоко- импедансное состояние буферный элемент 84, двунаправленные формирователи 60 и 61 и буферные регистры 65 и 67, а также сбрасывает сигналы выборки знакогенератора (триггеры 52 и 53) и устанавливает триггер 93 в исходное единичное состояние. На этом цикл Считывания процессором байта (двух байтов) из генератора знаков заканчивается.

35

ливает триггер 46 в единичное состояние, вьшолняя запись в порт константы 1. Это предотвращает несанкционированный доступ к генератору 10 символов. При случайной попытке обращения ЭВМ к генератору 10 символов единичное состояние триггера 46 блокирует дешифрацию адреса генератора 10 символов дешифратором 43. При этом команда записи (или считывания) ЭВМ обрабатывается обычным о0разом, но в память генератора 10 символов инт формация не записывается, поскольку не формируются сигналы выборки и записи.

В режиме регенерации изображения устройство работает следующим образом.

дится синхронизация блока 6 управле ияРассмотрим цикл отображения первого символа на экране дисплея.

По фронту первого сигнала CLK блок 6 управления формирует начальный адрес регенерации МА, растровый адрес RA.0 и сигнал разрешения отображения.

При отсутствии обрав ений ЭВМ к буферу дисплея и перезагружаемому генератору 10 символов триггеры 88 и 93 находятся в исходном единичном состоянии (триггер 93 установлен в единицу высоким потенциалом с выхода элемента ИЛИ,, а триггер 88 установлен в единичное состояние по D-входу первым

после сброса тактовь1м импульсом с выхода блока 85 триггеров). При единичном .состоянии триггера У8 на выходе элемента И 92 присутствует низкий потенциал, поступающий по шине 19 на вход управления мультиплексора 1 адреса буфера и разрешающий прохождение через него адресов регенерации от блока 6 управления (высокий потенциал на входе управления мультиплексора 1 разрешает прохождение адресов с адресного входа 16 устройства).

Низкий потенциал на выходе элемента И 92 обеспечивает высокие потенциа лы выборки на выходах элементов ИЛИ 83 и ИЛИ 95, поступающие одновре- менно через шину 21 на входы выборки блока 2 буферной памяти символов и блока 3 буферной памяти атрибутов. Таким образом, адрес регенерации МА, сформированный блоком управления, через мультиплексор 1 адреса буфера поступает на адресные входы блоков 2 и 3 буферной памяти, где при нали- чии сигналов выборки одновременно считываются код символа и код атрибута.

По фронту первого сигнала CLK код символа заносится в регистр 4 сим- волов, а код атрибута - в регистр 5 атрибутов. Код атрибута поступает на дешифратор 13 атрибута, где дешифруются потенциалы нормального изображения, невидимого изображения, мерцания, реверса, подчеркивания и повышенной яркости.

Триггер 46 после загрузки генератора 10 символов должен быть установлен в единичное состояние. Высокий потенциал с выхода триггера 46 по шине 28 поступает на управляющий вход мультиплексора 11 адреса генератора символов, обеспечивая прохождение через него кода символа из регистра А символов и растрового адреса RA из блока 6 управления, поступающих на адресный вход перезагружаемого генератора 10 символов. Единичное состояние триггера 46, поступающее на элементы ИЛИ 48 и ИЛИ 45, обеспечивает, кроме того, ВОЗМОЖНОСТЬ;,установки в единичное состояние триггеров 52 и 53. Тактовый импульс с выхода блока 85 триггеров поступает по шине 35 на вход элемента И 47 и по его спаду (отрицательный полупериод) устанавливаются в единичное состояние .триггеры 53 и 52. Сформированные стро

5 0 5

О

Q 5 Q g

5

бы выборки четного и нечетного банков генератора 10 символов поступают по шине 31 на его вход и выбирают из него 9 разрядов матрицы знака,соответствующих нулевой () линии сканирования данного символа.

Считанные разряд. матрицы по сигналу занесения, сформированному элементом И 87 и поступающему по шине 36, заносятся в сдвиговый { егистр 8. На вход сдвига сдвигового регистра 8 nocT TiaeT по шине 36 сигнал из задающего генератора 86 импульсов, обеспечивая на выходе сдвигового регистра 8 сигй ал с длительностью свечения точки.

За время первого импульса CLK, таким образом, осуществляется считывание из генератора знаков среза первого символа и занесение его в сдвиговый регистр 8, а также дешифра- ция атрибута. По фронту второго CLK потенциалы с дешифратора 13 заносятся в выходной регистр 76 атрибута, а также начинается выдвижение точек символа из сдвигового регистра 8. Занесение недействительной информации по первому CLK в выходной регистр 76 атрибута заблокировано сигналом с выхода регистра 72, на вход которого поступает по шине 29 сигнал разрешения отображения из блока 6 управления, сформированный по фронту сигнала CLK. Формирование видеосинхросигнала триггером 77 и сигнала повышенной яркости элементом И 78 заблокировано низким потенциалом с выхода регистра 72 .и разрешае тся только по фронту второго CLK, когда в выходном регистре 76 атрибутов и . сдвиговом регистре 8 находится действительная информация, соответствующая срезу первого символа.

Формирование видеосинхроимпульса и синхроимпульса повьшенной яркости в соответствии с атрибутами осуществляется следующим образом.

СигнсШ из сдвигового регистра 8 по шине 34 поступает на вход элемента ИЛИ 80.

Если в атрибуте задано подчеркивание символа, то на другой вход элемента ИЛИ 80 поступает высокий потенциал с выхода регистра 76, обеспечивающий формирование видеосигнала В определенной линии сканирования строки, при отсутствии сигнала из сдвигового регистра 8. Если в атрибуте за13144

дан неотображаемый Символ, то прохождение- сигнала с элемента ИЛИ 80 блокируется высоким потенциалом с выхода регистра 76.

Если в атрибуте задано мерцание символа, то оно осуществляется с частотой, составляющей 1/32 частоты кадра. В качестве делителя частоты используется двоичный счетчик 71, на вход синзронизации которого поступает кадровый синхроимпульс, сформированный блоком 6 управления, В течение 16 кадров высокий потенциал с выхода элемента И 75 блокирует, а в тече- ние следующих 16 кадров разрешает прохождение сигнала со. сдвигового регистра 8 через элемент И 74, создавая

Синхросигналы строчной и кадровой развертки, сформированные блоком 6 управления по фронту сигнала CLK, стробируются сигналом CLK на регистре 72 и выдаются вместе с синхросигнана экране мерцающую точку.

Высокий потенциал с выхода элемен- 20 видео и яркости по выходу 18. та И 74 поступает на вход элемента По третьему импульсу CLK отобража- ИЛИ 73, на воторой вход которого поступает сигнал курсора, сформированный блоком 6 управления и обеспечиваюются 9 точек среза второго символа, код которого выбран из буфера дисплея по адресу регенерации MAfl, сформирощий формирование видеосигнала в оп- 25 ванному контроллером дисплея по фрон- ределенной линии (линиях) сканирова- ТУ второго CLK (т.е. спаду первого НИН в определенной позиции экрана. CLK) и занесенному в буфер символа по

фронту второго CLK. На время второго CLK осуществляется считывание из ге30

Сигнал с выхода элемента ИЛИ 73 поступает на вход элемента 79 сложения по модулю 2. Если в атрибуте не задано реверсивное изображение символа, то сигнал без изменения поступает на вход триггера 77 и элемент И 78. Если в атрибуте задано реверсивное изображение, высокий потенциал с выхода триггера 77 изменяет полярность сигнала, поступающего на вход элемента 79 сложения, в результате чего видимая точка, кодируемая единицей, становится невидимой точкой, а черный фон, кодируемый нулями, теперь будет отображаться как видимый. Нормальное изображение белый символ - черный фон преобразуется в реверсивное изображение черный символ - белый фон.

Высокий потенциал с выхода элемента 79 сложения, поступает на вход триггера 77, на вход синхронизации которого поступает по шине 36 сигнал из задающего генератора 86 импульсов, формируя на выходе триггера 77 сигнал с длительностью свечения точки.

Если в атрибуте задана повышенная яркость, то высокий потенциал с выхода регистра 76 разрешает форми1)ова- ние видеосинхросигнала повышенной яркости элементом И 78.

35

нератора знаков среза и второго символа, занесение его в сдвиговый регистр, а также дешифрация атрибута, ему соответствующего.

По третьему импульсу CLK 9 точек среза второго символа отображаются.

40

как описано вьше.

Далее по каждому следующему импульсу CLK цикл отображения повторяется, пока не будет отображена первая линия сканирования всех символов строки.

Доступ процессора к буферу дисплея осуществляется следующим образом.

Дпя блоков 2 и 3 буферной памяти в адресном пространстве системной g памяти зарезервированы определенные адреса. При наличии сигналов Запи- -. сать в память или Считать память на управляющем входе 15, дешифратор 81 дешифрирует адрес буфера, поступающий из ЭВМ по адресному входу 16. Высокий потенциал с выхода дешифратора 81 поступает на вход элемента ИЛИ 94, создавая возможность установки триггеров 88 и 93 в нулевое состояние (оба триггера находятся в исходном единичном состоянии).

Низкий потенциал на выходе эле-, мента ИЛИ 94 обуславливает выдачу низкого уровня сигнала Не готово с

50

55

J4

После отображения всех символов строки блок 6 управления сбрасывает в нуль сигнал разрешения отображения, поступаюпдий на вход регистра 72 и блокирующего триггер 77 и элемент И 78, т.е. формирование видеосигнала и, если задан режим повьшенной яркости, синхросигнала повышенной яркости. Необходимо отметить, что возможна одновременная работа нескольких атрибутов, не исключающих друг друга, например, изображение может быть реверсивным, ярким и мерцающим.

Синхросигналы строчной и кадровой развертки, сформированные блоком 6 управления по фронту сигнала CLK, стробируются сигналом CLK на регистре 72 и выдаются вместе с синхросигна видео и яркости по выходу 18. По третьему импульсу CLK отобража-

ются 9 точек среза второго символа, код которого выбран из буфера дисплея по адресу регенерации MAfl, сформиро0

5

нератора знаков среза и второго символа, занесение его в сдвиговый регистр, а также дешифрация атрибута, ему соответствующего.

По третьему импульсу CLK 9 точек среза второго символа отображаются.

0

как описано вьше.

Далее по каждому следующему импульсу CLK цикл отображения повторяется, пока не будет отображена первая линия сканирования всех символов строки.

Доступ процессора к буферу дисплея осуществляется следующим образом.

Дпя блоков 2 и 3 буферной памяти в адресном пространстве системной g памяти зарезервированы определенные адреса. При наличии сигналов Запи- -. сать в память или Считать память на управляющем входе 15, дешифратор 81 дешифрирует адрес буфера, поступающий из ЭВМ по адресному входу 16. Высокий потенциал с выхода дешифратора 81 поступает на вход элемента ИЛИ 94, создавая возможность установки триггеров 88 и 93 в нулевое состояние (оба триггера находятся в исходном единичном состоянии).

Низкий потенциал на выходе эле-, мента ИЛИ 94 обуславливает выдачу низкого уровня сигнала Не готово с

0

5

выхода триггера 93 через буферный элемент 84, Этот низкий потенциал удлиняет цикл записи или считывания, но позволяет осуществить доступ ЭВМ к буферу, не искажая изображения на экране.

Как отмечалось выше, адрес регенерации, выдаваемый блоком 6 управления по фронту CLK (т.е. спаду CLK) подается через мультиплексор 1 в буфер во время отрицательного полуперио да импульса CLK.Чтобы синхронизировать доступ ЭВМ к буферу с процессором регенера1Ц1и, подача через мультиплексор 1 адреса от ЭВМ разрешается только во время положительного полупериода. Первый после обращения ЭВМ тактовый импульс с выхода блока 85 триггеров сбрасывает триггер 88 в нулевое состояние. Низкий потенциал с выхода триггера 88 поступает на элементы И 92 и И 82. Во время положи тельного полупериода импульса CLK, поступающего с выхода блока 85 триггеров, на выходе элемента И 92 появляется высокий потенциал, по шине 19 поступающий на мультиплексор 1 адреса буфера и разрешающий прохождение через него адресов от ЭВМ. При наличии от ЭВМ команды Записать в память на входе 15 элемент И 82 по стробу, сформированному элементом И 89, выдает сигнал записи, по шине 21 поступаюш 1й в блоки 2 и 3 буферной памяти. Кроме того, в зависимости от того, записывается из ЭВМ четный или нечетньй байт или оба одновременно элементы ИЛИ 83 и ИЛИ 95 формируют стробы выборки буфера символов или буфера атрибутов или оба эти сигнала одновременно, которые по шине 21 также поступают на входы их выборки.

Высокий потенциал с выхода дешифратора 81 поступает на вход элемента И 59, обеспечивая высокий потенциал при вьтолнении команды считывания на входах управления третьим состоянием запоминаюшлх регистров 64 и 66, и на вход элемента ИЛИ 55, обеспечивая высокие потенциалы на входах управления третьим состоянием двунаправленных формирователей 60 и 61.

При выполнении команды записи сигнал Записать в память, поступающий по управляющему входу 15 на вход элемента ШШ 57, определяет направление передачи через двунаправленные формирователи 60 и 61 с входа на выход.

Отсутствие этого сигнала но время команды Считать память сохраняет низкий потенциал на выходе элемента И11И 57 и обеспечивает направление передачи данных через формирователи 60 и 61 с выхода на вход.

Строб записи, сформированный эле. ментом И 82 поступает по шине 37 на

Q входы управления третьим состоянием формирователей 62 и 68, обеспечивая передачу информации с информагщонного входа-выхода 17 через.двунаправленные формирователи 60 и 61 и формирователи

5 62 и 68 соответственно на информа- ционную шину 22 буфера символов и информационную шину 23 буфера атрибутов.

При выполнении команды Считать

Q память строб считывания, сформированный при установке триггера 93 в нулевое состояние заносит информацию с информационной шины 22 буфера символов и информационной шины 23 буфера атри5 бутов в буферные регистры 64 и 66

соответственно и выдает их через двунаправленные формирователи 60 и 61 соответственно на информационный вход-выход 17. Как и в случае работы

0 с генератором 10 символов, ЭВМ может записывать (или считывать) четный или нечетный байт или оба байта одновременно, что определяется наличием высоких потенциалов на входах элементов И 54 и И 56, поступающих с адресного 16 и управляющего 15 входов,

Завершается цикл записи (считывания) информации в буфере аналогично циклу записи (считывания) -в генераг

0 Р О символов. На выходе дешифратора 81 появляется низкий потенциал, триггеры 88 и 93 устанавливаются в исходное единичное состояние, буферный элемент 84, формирователи 62 и

g 68 (или запоминаюрще регистры 64 и 66), а также двунаправленные формирователи 60 и 61 переводятся в сое- тояние высокого импеданса.

Максимальное удлинение цикла запиQ си (считывания) при таком доступе - составляет один цикл отображения линии сканирования символа при регенерации.

Таким образом, предлагаемое устg ройство обеспечивает повыщение точности за счет оперативного изменения состава отображаемых символов и программирования символов произвольной конфигурации в матрице знакоместа.

5

1714

Формула изобретения Устройство для отображения информации, содержащее первый мультиплексор адреса, блок буферной памяти сим- волов, генератор символов, блок буферной памяти атрибутов, регистр символов, формирователь видеосигнала, регистр атрибутов, блок управления, блок синхронизации, сдвиговый регистр блок сопряжения, первый выход которого соединен с информационным входом блока управления, вход синхронизации которого и входы синхронизации регистров символов и атрибутов подключе- ны к первому выходу блока синхронизации, второй выход которого соединен с входом синхронизации сдвигового регистра, третий выход блока синхро- низаоди подключен к управляющему входу первого мультиплексора адреса, выход которого соединен с адресными входами блоков буферной памяти символов и атрибутов, входы выборки которых подключены к четвертому выходу блока синхронизации, управляющий вход которого и управляющие входы блока управления и блока сопряжения являются управляющим входом устройства, адресным входом которого являются первый информационный вход первого мультиплексора адреса, адресный вход блока синхронизации и адресный вход . блока сопряжения, синхровход которого соединен с пятым выходом блока синх- ронизации, первый вход-выход блока сопряжения является информационным входом-выходом устройства, информационный вход регистра символов и информационный вход-выход блока буфер- ной памяти символов подключены к второму входу-выходу блока сопряжения, третий вход-выход которого соединен с информационным входом-выходом блока буферной памяти атрибутов и с информационным входом регистра атрибутов, второй информационный вход первого мультиплексора адреса подключен к первому выходу блока управления отличающееся тем, что, с целью повышения точности устрой301Я

ства, оно содержит второй мультиплексор адреса, формирователь управляющих импульсов, дешифратор атрибута, выход которого подключен к управляющему входу формирователя видеосигнала, первь1й информационный вход которого подключен к второму выходу блока управления, третий выход которого соединен с первым информационным входом второго мультиплексора адреса, второй информационный вход которого и адресный вход формирователя управляющих импульсов соединены с адресным входом устройства, информационный вход сдвигового регистра и информа-. ционный вход-выход генератора символов подключены к четвертому входу- выходу блока сопряжения, тактовый вход которого соединен с первым выходом формирователя управляющих импульсов, второй выход которого подключен к тактовому входу блока синхронизации, шестой выход которого соединен с входом синхронизации формирователя управляющих импульсов, управляющий вход которого и вход сброса формирователя видеосигналов соединены с управляющим входом устройства, третий выход формирователя управляющих импульсов подключен к управляющему входу второго мультиплексора- адреса, выход которого подключен к адресному входу генератора символов, управляющий вход которого соединен с четвертым выходом формирова - теля управляющих импульсов, информационный вход которого подключен к первому выходу блока сопряжения, выход регистра символов соединен с третьим информационным входом второго мультиплексора адреса, выход регистра атрибутов подключен к входу дешифратора атрибута, выход сдвигового регистра соединен с вторым информационным входом формирователя видеосигнала, синхровходы которого подключены к первому и второму выходу блока синхронизации, выход формирователя видеосигнала является выходом видеосигнала устройства.

Авторы

Даты

1988-11-30—Публикация

1986-12-30—Подача