11292183

Изобретение относится к радиоизШ

20

25

мерительной технике и может быть использовано для стробоскопического преобразования сигналов в масштабно- временных преобразователях и автоматизированных измерителях параметров сигналов.

Цель изобретения - повышение быстродействия и упрощение устройства.

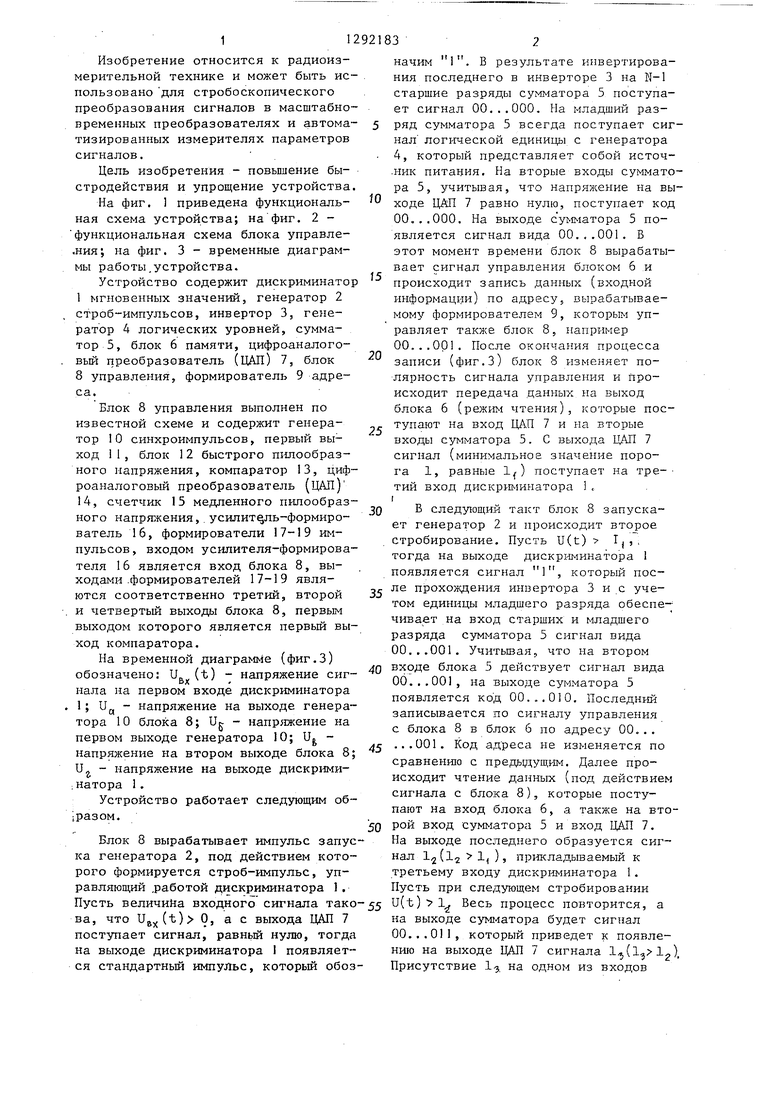

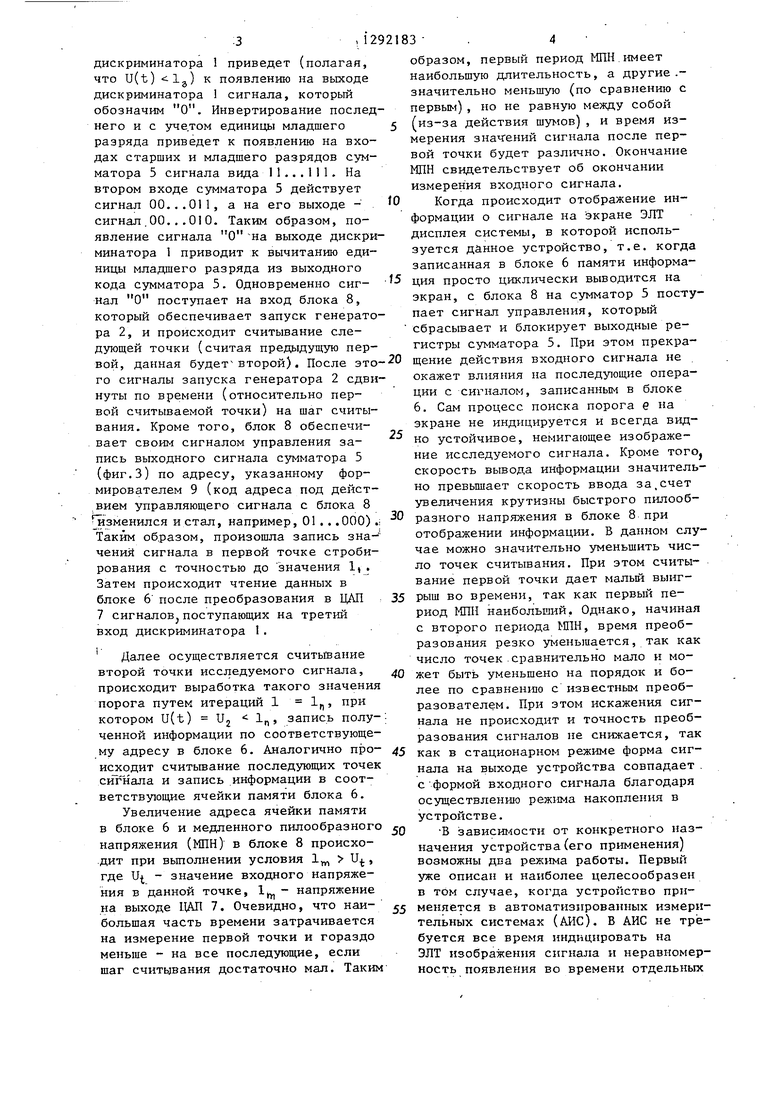

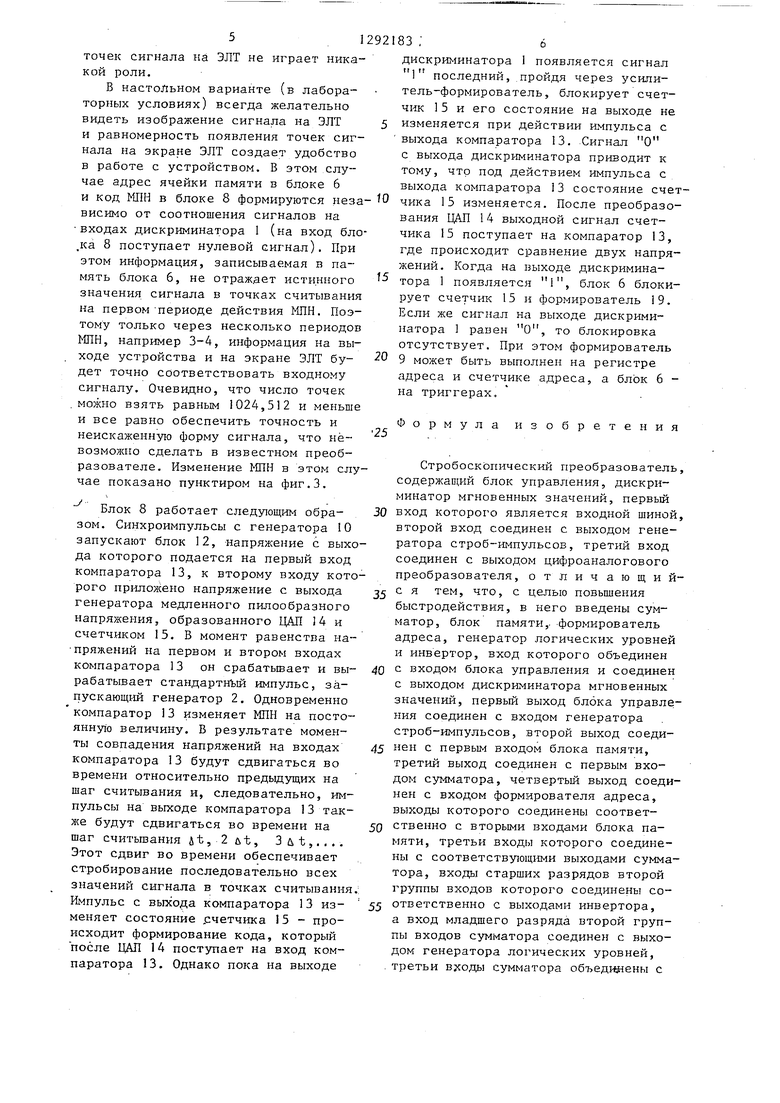

На фиг. приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока управле- .ния; на фиг. 3 - временные диаграммы работы,устройства.

Устройство содержит дискриминатор 1 мгновенных значений, генератор 2 строб-импульсов, инвертор 3, генератор 4 логических уровней, сумматор 5, блок 6 памяти, цифроаналого- вый преобразователь (ЦАП) 7, блок 8 управления, формирователь 9 адреса.

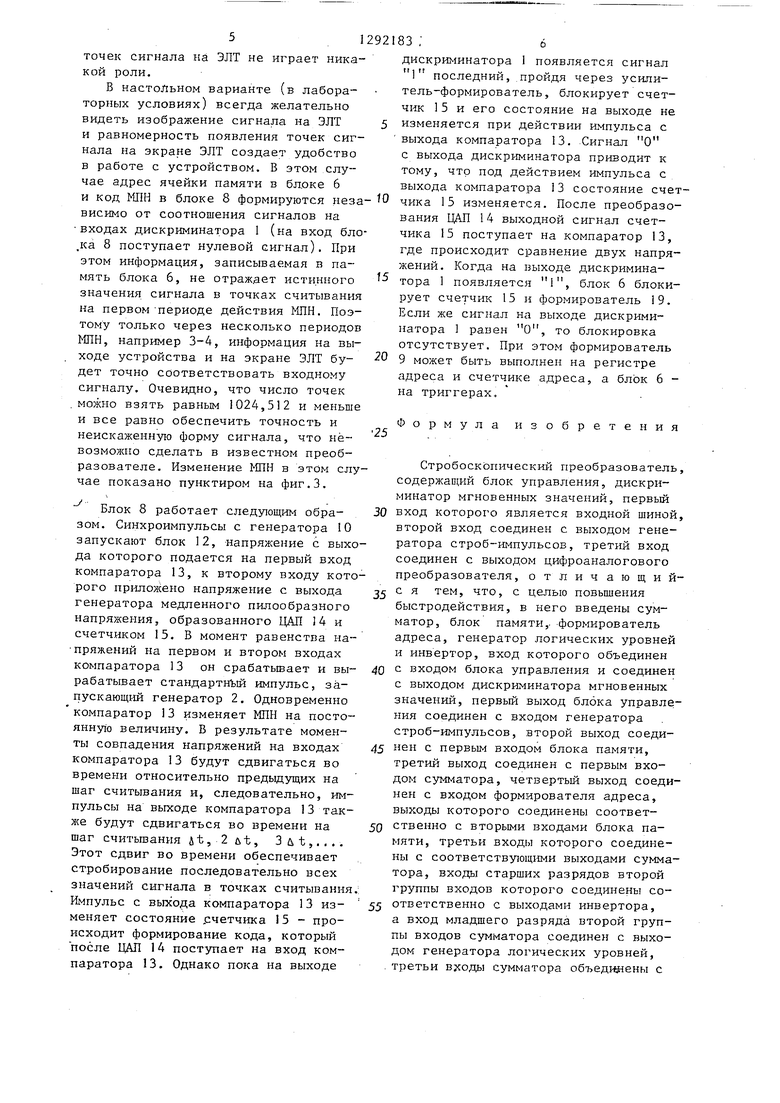

Блок 8 управления выполнен по известной схеме и содержит генератор 10 синхроимпульсов, первый выход 11, блок 12 быстрого пилообразного напряжения, компаратор 13, циф- роаналоговый преобразователь (ЦАП) 14, счетчик 15 медленного пилообразного напряжения, усилит ль-формиро- ватель 16, формирователи 17-19 импульсов, входом усилителя-формирователя 16 является вход блока 8, выходами -формирователей 17-19 являются соответственно третий, второй и четвертый выходы блока 8, первым выходом которого является первый выход компаратора.

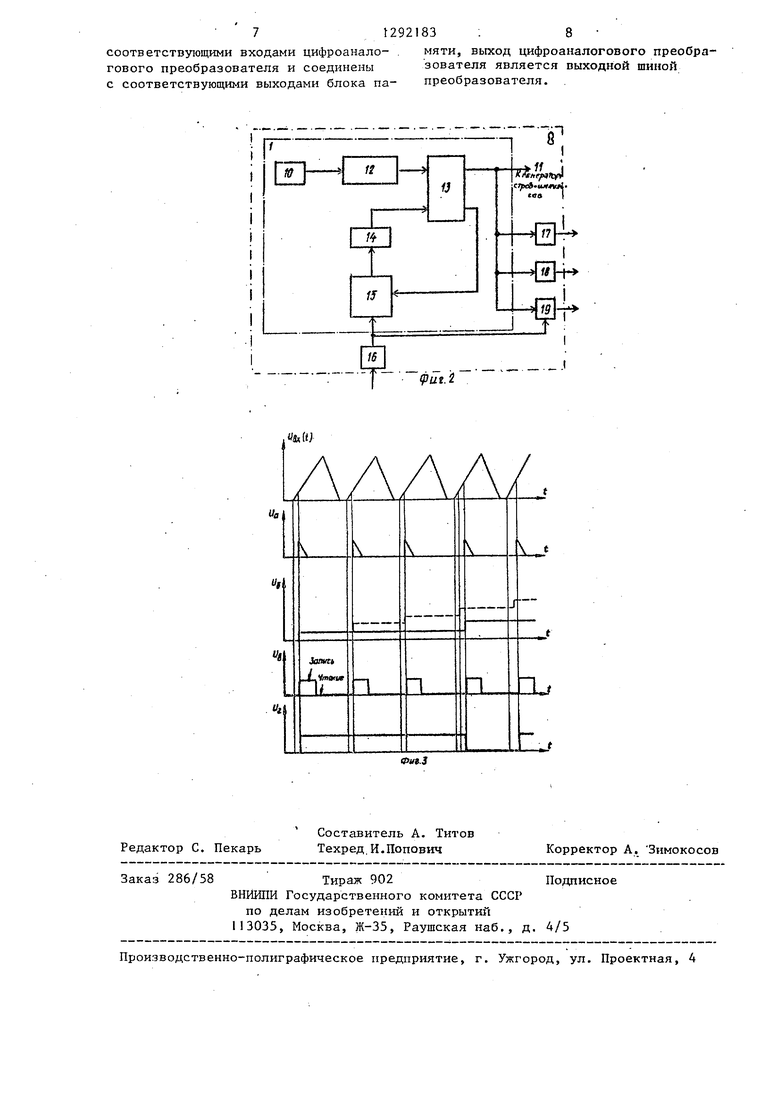

На времениой диаграмь1е (фиг.З) обозначено: U (t) - напряжение сигнала на первом входе дискриминатора 1; Ug - напряжение на выходе генератора 10 блока 8; и - напряжение на первом выходе генератора 10; U - напряжение на втором выходе блока 8; и - напряжение на выходе дискрими- ;Натора 1.

Устройство работает следующим об- iразом.

30

35

40

Блок 8 вырабатывает импульс запуска генератора 2, под действием которого формируется строб-импульс, управляющий .работой дискриминатора 1 .

50

Б следующий такт блок 8 запускает генератор 2 и происходит второе стробирование. Пусть U(t) тогда на выходе дискриминатора 1 появляется сигнал 1, который после прохождения инвертора 3 и с учетом единицы младшего разряда обеспе- чивает на вход старших и младшего разряда сумматора 5 сигнал вида 00...001. Учитьшая, что на втором входе блока 5 действует сигнал вида 00...001, на выходе сумматора 5 появляется ко д 00... 010. Последний записывается по сигналу управления с блока 8 в блок б по адресу 00... ...001. Код адреса не изменяется по сравнению с предыдуш,им. Далее происходит чтение данных (под действием сигнала с блока 8), которые поступают на вход блока б, а также на второй вход сумматора 5 и вход ЦАП 7. На выходе последнего образуется сигнал Ijdi l )s прикладываемый к третьему входу дискриминатора 1. Пусть при следующем стробировании

ва, что Ug(t) О, а с выхода ЦАП 7

Пусть величийа входного сигнала тако-55 U(t)l Весь процесс повторится, а

на выходе сум1 1атора будет сигнал 00...01I, который приведет к появлению на выходе ЦАП 7 сигнала I.(l 1 Присутствие 1 на одном из входов

поступает сигнал, равньй нулю, тогда на выходе дискриминатора 1 появляется стандартный импульс, который обоз

0

5

начим 1 . В результате инвертирования последнего в инверторе 3 на N-1 старшие разряды сумматора 5 поступает сигнал 00... 000. На младший разряд сумматора 5 всегда поступает сигнал лоп-гческой единицы с генератора 4, который представляет собой источник питания. На вторые входы сумматора 5, учитывая, что напряжение на выходе ЦАП 7 равно нулю, поступает код 00...000. На выходе с умматора 5 появляется сигнал вида 00...001. В этот момент времени блок 8 вырабатывает сигнал управления блоком б и происходит запись данных (входной информации) по адресу, вырабатываемому формирователем 9, которым управляет также блок 8, например 00...001. После окончания процесса записи (фиг.З) блок 8 изменяет полярность сигнала управления и Происходит передача данных на выход блока 6 (режим чтения), которые поступают на вход ПДП 7 и на вторые входы сумматора 5. С выхода ДАН 7 сигнал (минимальное значение порога 1, равные If) поступает на тре- тий вход дискриминатора 1,

0

5

0

0

Б следующий такт блок 8 запускает генератор 2 и происходит второе стробирование. Пусть U(t) тогда на выходе дискриминатора 1 появляется сигнал 1, который после прохождения инвертора 3 и с учетом единицы младшего разряда обеспе- чивает на вход старших и младшего разряда сумматора 5 сигнал вида 00...001. Учитьшая, что на втором входе блока 5 действует сигнал вида 00...001, на выходе сумматора 5 появляется ко д 00... 010. Последний записывается по сигналу управления с блока 8 в блок б по адресу 00... ...001. Код адреса не изменяется по сравнению с предыдуш,им. Далее происходит чтение данных (под действием сигнала с блока 8), которые поступают на вход блока б, а также на второй вход сумматора 5 и вход ЦАП 7. На выходе последнего образуется сигнал Ijdi l )s прикладываемый к третьему входу дискриминатора 1. Пусть при следующем стробировании

:3

дискриминатора 1 приведет (полагая, что U(t) lj) к появлению на выходе дискриминатора 1 сигнала, который обозначим О. Инвертирование последнего и с уче.том единицы младшего разряда приведет к появлению на входах старших и младшего разрядов сумматора 5 сигнала вида 11... 111. На втором входе сумматора 5 действует сигнал 00.,.011, а на его выходе - сигнал.00...010. Таким образом, появление сигнала О -на выходе дискриминатора 1 приводит к вычитанию единицы младшего разряда из выходного

образом, первый период МЛН liMeeT наибольшую длительность, а другие .- значительно меньшую (по сравнению с первьм), но не равную между собой 5 (из-за действия шумов), и время измерения знач ений сигнала после первой точки будет различно. Окончание №Н свидетельствует об окончании измерения входного сигнала, 10 Когда происходит отображение информации о сигнале на экране ЭЛТ дисплея системы, в которой используется данное устройство, т.е. когд записанная в блоке 6 памяти информа

экран, с блока 8 на сумматор 5 пост пает сигнал управления, который сбрасывает и блокирует выходные регистры сумматора 5. При этом прекра

25

кода сумматора 5. Одновременно сиг- дия просто циклически выводится на нал О поступает на вход блока 8, который обеспечивает запуск генератора 2, и происходит считывание следующей точки (считая предыдущую первой, данная будет второй). После это--20 щение действия входного сигнала не го сигналы запуска генератора 2 сдвинуты по времени (относительно первой считываемой точки) на шаг считывания. Кроме того, блок 8 обеспечивает своим сигналом управления запись выходного сигнала сумматора 5 (фиг.З) по адресу, указанному формирователем 9 (код адреса под дейст- ,вием управляющего сигнала с блока 8 изменился и стал, например, 01 .. .000) .. Таким образом, произошла запись зна- чения сигнала в первой точке строби- рования с точностью до значения 1. Затем происходит чтение данных в блоке 6 после преобразования в ЦАП 7 сигналов поступающих на третий вход дискриминатора 1,

35

окажет влияния на последующие опера ции с сигналом, записанным в блоке 6, Сам процесс поиска порога е на экране не индицируется и всегда вид но устойчивое, немигающее изображение исследуемого сигнала. Кроме Tor скорость вывода информации значител но превьш1ает скорость ввода за,счет увеличения крутизны быстрого пилооб разного напряжения в блоке 8 при отображении информации. В данном сл чае можно значительно уменьшить чис ло точек считывания. При этом считы вание первой точки дает малый выигрыш во времени, так как первый период МПП наибольший. Однако, начина с второго периода МШ, время преобразования резко уь{еньшается, так ка число точек.сравнительно мало и может быть уменьшено на порядок и более по сравнению с известным преобразователем. При этом искажения сиг нала не происходит и точность преоб разования сигналов не снижается, та как в стационарном режиме форма сиг нала на выходе устройства совпадает с формой входного сигнала благодаря осуществлению режима накопления в устройстве,

Далее осуществляется считьгвание второй точки исследуемого сигнала, происходит выработка такого значения порога путем итераций 1 1, при котором U(t) Uj IH 9 запись полученной информации по соответствующему адресу в блоке 6. Аналогично про- ис содит считывание последующих точек сигнала и запись информации в соответствующие ячейки памяти блока 6. Увеличение адреса ячейки памяти в блоке 6 и медленного пилообразного напряжения (МПН) в блоке 8 происходит при выполнении условия 1 U, где и - значение входного напряжения в данной точке, 1 - напряжение на выходе ЦАП 7. Очевидно, что наибольшая часть времени затрачивается на измерение первой точки и гораздо меньше - на все последующие, если шаг считывания достаточно мал. Таким

2183- . 4

образом, первый период МЛН liMeeT наибольшую длительность, а другие .- значительно меньшую (по сравнению с первьм), но не равную между собой 5 (из-за действия шумов), и время измерения знач ений сигнала после первой точки будет различно. Окончание №Н свидетельствует об окончании измерения входного сигнала, 10 Когда происходит отображение информации о сигнале на экране ЭЛТ дисплея системы, в которой используется данное устройство, т.е. когда записанная в блоке 6 памяти информаэкран, с блока 8 на сумматор 5 поступает сигнал управления, который сбрасывает и блокирует выходные регистры сумматора 5. При этом прекрадия просто циклически выводится на щение действия входного сигнала не

дия просто циклически выводится на щение действия входного сигнала не

окажет влияния на последующие операции с сигналом, записанным в блоке 6, Сам процесс поиска порога е на экране не индицируется и всегда видно устойчивое, немигающее изображение исследуемого сигнала. Кроме TorOj скорость вывода информации значительно превьш1ает скорость ввода за,счет увеличения крутизны быстрого пилообразного напряжения в блоке 8 при отображении информации. В данном случае можно значительно уменьшить число точек считывания. При этом считывание первой точки дает малый выигрыш во времени, так как первый период МПП наибольший. Однако, начиная с второго периода МШ, время преобразования резко уь{еньшается, так как число точек.сравнительно мало и может быть уменьшено на порядок и более по сравнению с известным преобразователем. При этом искажения сигнала не происходит и точность преобразования сигналов не снижается, так как в стационарном режиме форма сигнала на выходе устройства совпадает . с формой входного сигнала благодаря осуществлению режима накопления в устройстве,

В зависимости от конкретного назначения устройства (его применения) возможны два режима работы. Первый уже описан и наиболее целесообразен в том случае, когда устройство применяется в автоматизированных измерительных системах (АИС). В АИС не требуется все время индицировать на ЭЛТ изображения сигнала и неравномерность появления во времени отдельных

512921

точек сигнала на ЭЛТ не играет никакой роли.

В настольном варианте (в лабораторных условиях) всегда желательно видеть изображение сигнала на ЭЛТ 5 и равномерность появления точек сигнала на экране ЭЛТ создает удобство в работе с устройством. В этом случае адрес ячейки памяти в блоке 6 и код ffilH в блоке 8 формируются неза- О висимо от соотношения сигналов на входах дискриминатора 1 (на вход бло- ка 8 поступает нулевой сигнал). При этом информация, записываемая в память блока 6, не отражает истинного значения сигнала в точках считывания на первом периоде действия МПН. Поэтому только через несколько периодов МПН, например 3-4, информация на выходе устройства и на экране ЭЛТ бу- дет точно соответствовать входному сигналу. Очевидно, что число точек можно взять равным 1024,512 и меньше и все равно обеспечить точность и неискаженную форму сигнала, что невозможно сделать в известном преобразователе. Изменение МПН в этом случае показано пунктиром на фиг.З.

Блок 8 работает следующим обра- 30 зом. Синхроимпульсы с генератора 10 запускают блок 12, напряжение с выхода которого подается на первый вход компаратора 13, к второму входу которого приложено напряжение с выхода 35 генератора медленного пилообразного напряжения, образованного ЦАП 14 и счетчиком 15. В момент равенства на- пряжений на первом и втором входах компаратора 13 он срабатьшает и вы- 40 рабатывает стандартный импульс, запускающий генератор 2. Одновременно компаратор 13 изменяет МПН на посто- ЯНН5ПО величину. В результате моменты совпадения напряжений на входах 45 компаратора 13 будут сдвигаться во времени относительно предыдущих на шаг считывания и, следовательно, импульсы на выходе компаратора 13 таке будут сдвигаться во времени на 50 шаг считьшания it, 2 at, 3ut,.,.. Этот сдвиг во времени обеспечивает стробирование последовательно всех значений сигнала в точках считывания.; Импульс с Bbixof a компаратора 13 из- 55 еняет состояние .счетчика 15 - происходит формирование кода, который после ЦАП 1А поступает на вход компаратора 13. Однако пока на выходе

83: 6

дискриминатора 1 появляется сигнал 1 последний, .пройдя через усилитель-формирователь, блокирует счетчик 15 и его состояние на выходе не изменяется при действии импульса с выхода компаратора 13. Сигнал О с выхода дискриминатора приводит к тому, что под действием импульса с выхода компаратора 13 состояние счетчика 15 изменяется. После преобразования ЦДЛ 14 выходной сигнал счетчика 15 поступает на компаратор 13, где происходит сравнение двух напряжений. Когда на выходе дискриминатора 1 появляется 1, блок 6 блокирует счетчик 15 и формирователь 19. Если же сигнал на выходе дискриминатора 1 равен О, то блокировка отсутствует. При этом формирователь 9 может быть выполнен на регистре адреса и счетчике адреса, а блок 6 - на триггерах,,

Формула изобретения

Стробоскопический преобразователь содержащий блок управления, дискриминатор мгновенных значений, первый вход которого является входной шиной второй вход соединен с выходом генератора строб-импульсов, третий вход соединен с выходом цифроаналогового преобразователя, отличающий с я тем, что, с целью повьш1ения быстродействия, в него введены сумматор, блок памяти,, формирователь адреса, генератор логических уровней и инвертор, вход которого объединен с входом блока управления и соединен с выходом дискриминатора мгновенных значений, первый выход блока управления соединен с входом генератора строб-импульсов, второй выход соединен с первым входом блока памяти, третий выход соединен с первым входом сумматора, четвертый выход соединен с входом формирователя адреса, выходы которого соединены соответственно с вторыми входами блока памяти, третьи входы которого соединены с соответствующими выходами сумматора, входы старших разрядов второй группы входов которого соединены соответственно с выходами инвертора, а вход младшего разряда второй группы входов сумматора соединен с выходом генератора логических уровней, . третьи входы сумматора об7эедилены с

соответствующими входами цифроанало- . мяти, выход цифроаналогового преобра- гового преобразователя и соединены зователя является выходной шиной с соответствующими выходами блока па- преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения динамических характеристик быстродействующих цифроаналоговых преобразователей | 1990 |

|

SU1765890A1 |

| Стробоскопический цифровой преобразователь | 1987 |

|

SU1503017A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для считывания графической информации | 1989 |

|

SU1635203A1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| Устройство для считывания изображений | 1987 |

|

SU1481816A2 |

| Цифровой формирователь трехфазных синусоидальных сигналов | 1990 |

|

SU1732418A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1506460A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

Изобретение относится к радиоизмерительной технике и может быть использовано для стробоскопического преобразования сигналов в масштабно- временных преобразователях и автоматизированных измерителях парамет- ров сигнала. Изобретение позволяет повысить быстродействие и упростить преобразователь. Это достигается тем, что в преобразователь, содержащий дискриминатор 1 мгновенных значений, генератор 2 строб-ш-шуль- сов, цифроаналоговый преобразоЬатель 7, блок 8 управления, введены инвертор 3, генератор 4 логических уровней, сумматор 5, блок 6 памяти, формирователь 9 адреса. 3 ил. Вмд (Л с 0i/a/

/

1

Jtinutt

It

Редактор С. Пекарь

Составитель А. Титов Техред И.Попович

Заказ 286/58

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

t

L

L

ГЬ

Корректор А. Зимокосов

| Херманис Э.Х., Кагрклиньш Б.Г | |||

| Дискретные стробоскопические преобразователи.- Рига: Зинатне, 1977, | |||

| с | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Цифровой стробоскопический преобразователь | 1975 |

|

SU565391A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1985-01-02—Подача