каналов. Триггеры 13 - 18 предназначены для блокировки элементов 2-2И-2ИЛИ-НЕ 19 - 21 по соответствующим входам с целью предотвращения разрушения сигнала переполнения счетчика импульсами той же частоты, которые вызывали переполнение, В предлагаемом устройстве, независимо от соотношения сравниваемых частот, емкость счетчиков 22 - 24 остается

1

Изобретение относится к электро- и радиоизмерительной технике и может быть использовано для управления процессом выбора сигнала средней частоты из трех входных, поступающих от датчиков с частотно-зависимой характеристикой.

Цель изобретения - повьшение точности дискриминирования средней частоты.

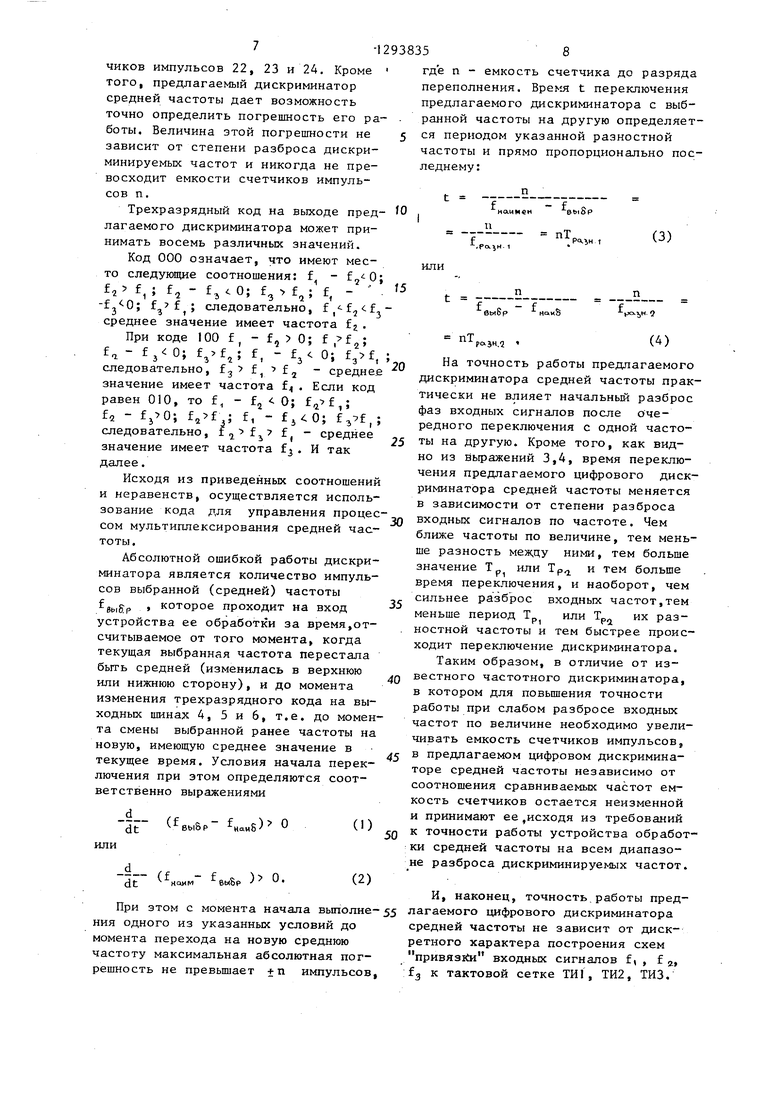

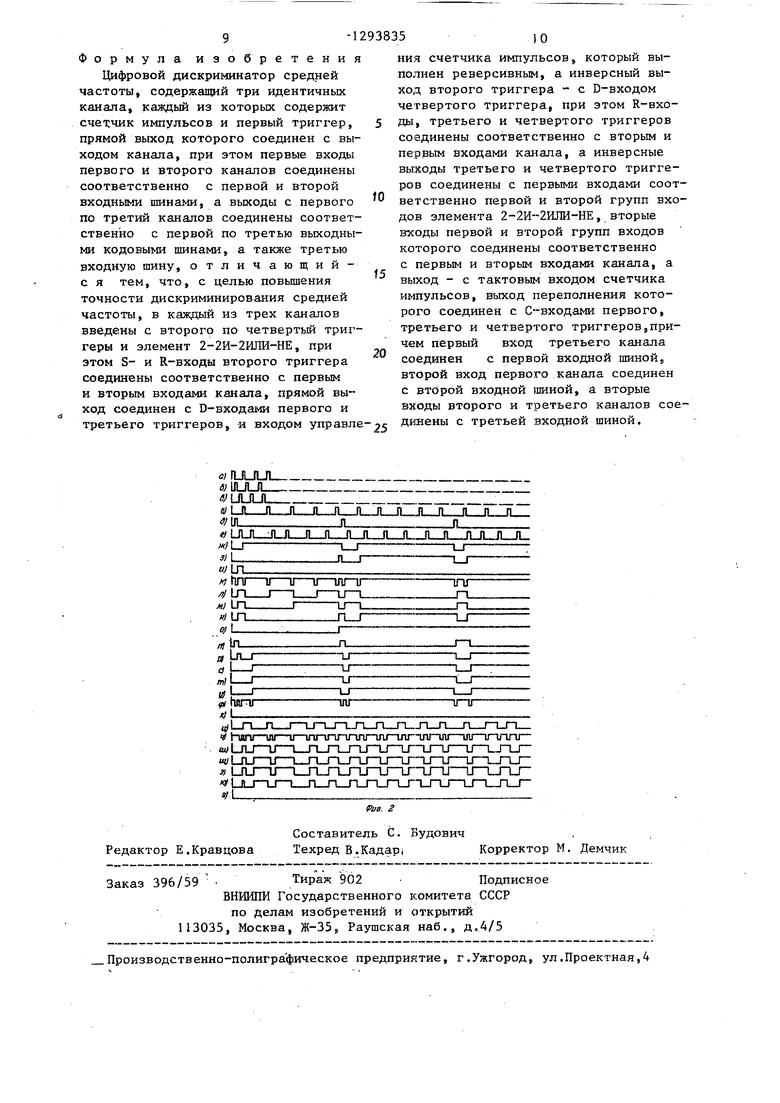

На фиг.1 показана структурная электрическая схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства с двухразрядными счетчиками импульсов.

Устройство содержит первые триггеры 1,2 и 3, выходы которых являю.- ся вьгходами, соответственно, первого, второго и третьего каналов, при этом выходы первого, второго и третьего каналов соединены соответственно , с первой, второй и третьей выходными кодовыми шинами 4,5 и 6. Входы первых триггеров 1, 2 и 3 соединены с прямыми выходами, соответственно, вторых триггеров 7, 8 и 9, S- и R-входы которых являются, соответственно, первым и вторым входами соответствующего канала, при этом первые входы первого и третьего каналов соединены с первой входной шиной 10, второй вход первого канала и первый вход второго канала соединены с второй входной шиной 11, вторые входы второго и третьего каналов соединены с третьей входной шиной 12. Прямые выхода вторых триггеров 7,8 и 9 соединены с D-входами, соответственно, третьих триггеров 13,14 и 15, а инверсные выходы вторьп триггеров

неизменной и принимать ее следует, исходя из требований к точности работы устройства обработки средней частоты на всем диапазоне разброса дискриминируемых частот. Точность работы устройства не зависит от дискретного характера построения схем привязки входных сигналов к тактовой сетке. 2 ил.

7,, 8 и 9 соединены с D-входами, соот- в ;тственно, четвертых триггеров 16, 17 и 18. Инверсные выходы третьих триггеров 13, 14 и 15 соединены с

первыми входами первых групп входов, соответственно, элементов 19, 20 и 21 2-2И-2ИЛИ-НЕ, выходы которых соединены, соответственно, с тактовыми входакж реверсивных счетчиков 22,

23 и 24 импульсов. Прямые выходы

триггеров 7, 8 и 9 соединены с входами управления, соответственно счетчиков 22, 23 и 24. Инверсные вьгходы триггеров 16,17 и 18 соединены с первыми входами вторьпс групп входов, соответственно, элементов 19, 20 и 21 2-2И-2ШШ-НЕ, вторые входы первой группы входов которых соединены с первым входом, соответственно, первого, второго и третьего каналов, а вторые входы второй группы входов элементов 19, 20 и 21 - соответственно, с вторыми входами первого, второго И третьего каналов. Выходы переполнения счетчиков 22, 23 и 24 сое- дкщены с С-входами, соответственно, триггеров 1,2 и 3, с С-входами, соответственно, триггеров 13, 14 и 15, а также с С-входами, соответственно триггеров 16, 17 и 18. R-входы триггеров 16,17 и 18 соединены с первыми входами соответственно, пер- BOiro, второго и третьего каналов, а R-входы триггеров 13, 14 и 15 соеди:нены с вторыми входами, соответственно, первого, второго и третьего каналов.

20

40 Устройство работает следующим образом.

При включении цифрового дискримнатора средней частоты все счетчики 22, 23 и 24 импульсов и триггеры 1-3,7-9 и 13-18 устанавливаются в нулевое состояние. Цепи установки на фиг.1 не показаны. На входны шины 10, П и 12 дискриминатора потупают импульсы сигналов сравнивае мьк частот f, f , f (фиг.2 г, д, е), предварительно засинхронизиро- ванные (привязанные) импульсами многофазной тактовой сетки ТИ, ТИ2,ТИЗ (фиг.2 а, 6, в). Каждый входной импульс частоты f своим предним фронтом устанавливает триггеры 7 и 9 первого и третьего каналов в единичное состояние (фиг. 2 ж, ц) и через элементы 19 и 21 2-2И-2ИЛИ-НЕ (фиг.2 к, ч), соответственно, первого и третьего канлов проходит на счетные входы ревесивных счетчиков 22 и 24 импульсов Реверсивные счетчики 22, 23 и 24 ипульсов всех каналов по счетным вхдам переключаются задними фронтами входных импульсов. Входные импульс частоты f,j своими передними фронтами устанавливают триггер 7 первого канала в нулевое состояние (фиг.2 а триггер 8 - в единичное (фиг.2 п и через элементы 19 и 20 2-2И-2ИЛИ НЕ (фиг.2 к, ф) первого и второго каналов проходят на счетные входы счетчиков 22 и 23 импульсов. Входные сигналы частоты f своими пере ними фронтами устанавливают тригге 8 и 9 второго и третьего каналов в нулевое состояние (фиг.2 п, ц), и рез элементы 20 и 21 2-2И-2ИЛИ-НЕ проходят на счетные входы реверсив ньЕ/ счетчиков 23 и 24 импульсов. Ипульсы сравниваемых частот f, fj.

f3 проходят через элементы 19, 20

и 21 2-2И-2ИЛИ-НЕ на счетные входы

реверсивных счетчиков 22, 23 и 24

пульсов до тех пор, пока соответствующие третьи и четвертые триггеры каналов находятся в нулевом состоянии.

Триггеры 7, 8 и 9 каналов на своих прямых выходах формируют сигнал управления режимом работы, соответственно, счетчиков 22, 23 и 24 импульсов своих каналов (сложение или вычитание). Так, при действии на входной шине 10 входного импульса f триггеры 7 и 9 первого и третьего каналов устанавливаются в единич

ное состояние, обеспечивая счетчикам 22 и 24 зтих каналов режим сложения по заднему фронту импульса f. Когда на входной шине 11 присутствует импульс частоты f, триггер 7 первого канала обеспечивает счетчику 22 режим вычит ания, а триггер 8 второго канала обеспечивает счетчику 23 импульсов режим сложения по заднему фронту импульса f. Импульс fg на входной Е1ине 12 устанавливает триггеры 8 и 9 второго и третьего каналов в нулевое состояние, обеспечивая тем самым Счетчикам 23 и 24 этих каналов режим вычитания по своему заднему фронту.

5

0

5

0

0

„нпульса частоты

Следовательно, в момент включения цифрового дискриминатора средней частоты все триггеры дискриминатора устанавливаются в нулевое состояние. На выходных ишнах 4, 5 и 6 (фиг.2 о, X, я) дискриминатора присутств ует код 000. Этот код используется для управления процессом мультиплексирования средней частоты на вход устройства ее дальнейшей обработки. I

Если первым на входных шинах

10, 11 и 12 после включения дискриминатора появляется, например, входной импульс частоты f (на входной шине 11), то он подтверждает нулевое состояние триггера 7 первого канала и триггера 17 второго канала (фиг.2 у), переводит в единичное состояние триггер 8 второго канала и через открытые элементы 19 и 20 2-2И-2ИЛИ-НЕ первого и второго каналов проходит на счетные элементы 19 и 20 2-2И-2ИЛИ-НЕ первого и второго каналов, проходит на счетные входы счетчиков 22 и 23 импульсов этих каналов. К моменту окончания

„нпульса частоты

f,j счетчик 22 им

пульсов первого канала (фиг.2 л, м, и) находится в режиме вычитания, поскольку на его управляющем входе присутствует низкий потенциал с выхода триггера 7, а счетчик 23 импульсов второго канала имеет режим сложения за счет высокого потенциала на выходе триггера 8 своего канала. Поскольку в момент включения дискриминато- ра все его счетчики импульсов установлены в нулевое состояние, то по заднему фронту импульса f на выходе счетчика 22 импульсов первого канала возникает сигнсш переполнения за

счет вычитания единицы из нуля. Этот сигнал поступает на G-входы триггеро 1, 13 и 16 первого канала. Поскольку на D-входах триггеров 1 и 13 присутствует нулевой уровень с прямого выхода триггера 7, то этот сигнал переполнения подтверждает их нулевое состояние (фиг.2 з, о) и переводит в единичное состояние триггер 6 первого канала (фиг,2 и), так как на его D-входе в этот момент присутствует единичный уровень с инверсного выхода триггера 7, Низкий потенциал инверсного выхода триггера 16 первого канала блокирует прохождение на счетный вход счетчика 22 импульсов последующих входных импульсов частоты f j, поступающих на входную шину I1 дискриминатора.

Этот же импульс частоты f по своему заднему фронту добавляет единицу в счетчик 23 импульсов второго канала (фиг.2 р, с, т),

Если после этого на входной шине 10 появляется импульс частоты f , то он переводит в единичное состояние триггеры 7 и 9 первого и третьего каналов, возвращает р нулевое состояние триггер 6 первого канала и подтверждает нулевое состояние триггера 18 третьего канала (фиг,2ю). Кроме того, пройдя через открытьш элементы 19 и 21 2-2И-2ИЖ-НЕ первого и третьего каналов, этот импульс своим задним фронтом возвращает в О счетчик 22 импульсов первого канала, поскольку после вычитания из О единицы импульсом f 2, все разряда этого счетчика находятся в единичном состоянии, и прибавляет единицу в счетчик 24 импульсов третьего канала. И так далее.

Таким образом, на счетчике 22 импульсов первого канала осуществляется сложение импульсов частоты f, и вычитание импульсов частоты f,j « На счетчике 23 импульсов второго канала осуществляется сложение импульсов

12938356

(в рсгжиме сложения или в режиме вычитания), т.е. фактически определяют

f. - f

2

JT

f 10

J5

20

25

30

40

знак разности частот

ЧТриггеры I5 2 и 3 каналов предназначены для запоминания этого знака и его хранения до изменения знака разности, I

Триггеры 13, 14, 15 и 16, 17, 18

каналов предназначены для блокировки элементов 19, 20, 21 2-2И-2ИЛИ- НЕ по соответствующим входам с целью щ едотвращения разрушения сигнала переполнения счетчика импульсами той же частоты, которые вызвали переполнение. Так, если, например, при действии на входной шине 10 импульса частоты ft по его заднему фронту возникает сигнал переполнения на выходе счетчика 24, то этот сигнал устанавливает в единичное состояние триггер 3 и триггер 15 в третьем канале. Начиная с этого момента ни один из последующих импульсов частоты f, не проходит через заблокированный по первому входу элемент 21 2-2И-2Шта-НЕ на счетный вкод счетчика 24 импульсов до тех пор, пока на входную шину 12 дискриминатора не поступит очередной импульс частоты fj, который возвращает-триггер 15 в нулевое состояние и снимает упомянутую блокировку элемента 21 35 2-2И-2ИЛИ-НЕ для импульсов частоты f . Однако своим задним фронтом этот импульс частоты f уменьшает код в

счетчике 24 импульсов на единицу, поэтому следующий импульс частоты

f, проходя на счетный вход счетчика 24 импульсов, дббавляет эту единицу к содержимому счетчика, не вызывая изменения состояния на выходе переполнения (на выходе старшего 45 разряда) счетчика. Таким образом, трехразрядный код, формируемый на выходных шинах 4, 5 и 6 дискриминатора и используемый для управления процессом выделения (мультиплексирочастоты fj и вычитание импульсов час- 50 вания) средней частоты из трех

тоты fi и, наконец, на счетчике 24 импульсов происходит сложение импульсов частоты f и вычитание импульсов частоты f (фиг.2 ш, щ, э). Емкость счетчиков 22, 23 и 24 импульсов одинакова и для каждого канала равна п. Триггеры 7,8 и 9 каналов определяют знак сигнала переполнения соответствующего счетчика импульсов

входных, изменяет свое значение не под воздействием изменения величины этих частот, как это имеет место в известном дискриминаторе, а под дей- 55 ствием изменения разностей дискри- минируе№)гх частот, благодаря чему значительно возрастают устойчивость и точность работы дискриминатора при значительно меньшей емкости п счет- .

f. - f

2

JT

f

0

5

0

знак разности частот

ЧТриггеры I5 2 и 3 каналов предназначены для запоминания этого знака и его хранения до изменения знака разности, I

Триггеры 13, 14, 15 и 16, 17, 18

каналов предназначены для блокировки элементов 19, 20, 21 2-2И-2ИЛИ- НЕ по соответствующим входам с целью щ едотвращения разрушения сигнала переполнения счетчика импульсами той же частоты, которые вызвали переполнение. Так, если, например, при действии на входной шине 10 импульса частоты ft по его заднему фронту возникает сигнал переполнения на выходе счетчика 24, то этот сигнал устанавливает в единичное состояние триггер 3 и триггер 15 в третьем канале. Начиная с этого момента ни один из последующих импульсов частоты f, не проходит через заблокированный по первому входу элемент 21 2-2И-2Шта-НЕ на счетный вкод счетчика 24 импульсов до тех пор, пока на входную шину 12 дискриминатора не поступит очередной импульс частоты fj, который возвращает-триггер 15 в нулевое состояние и снимает упомянутую блокировку элемента 21 5 2-2И-2ИЛИ-НЕ для импульсов частоты f . Однако своим задним фронтом этот импульс частоты f уменьшает код в

счетчике 24 импульсов на единицу, поэтому следующий импульс частоты

f, проходя на счетный вход счетчика 24 импульсов, дббавляет эту единицу к содержимому счетчика, не вызывая изменения состояния на выходе переполнения (на выходе старшего разряда) счетчика. Таким образом, трехразрядный код, формируемый на выходных шинах 4, 5 и 6 дискриминатора и используемый для управления процессом выделения (мультиплексировходных, изменяет свое значение не под воздействием изменения величины этих частот, как это имеет место в известном дискриминаторе, а под дей- 55 ствием изменения разностей дискри- минируе№)гх частот, благодаря чему значительно возрастают устойчивость и точность работы дискриминатора при значительно меньшей емкости п счет- .

7чиков импульсов 22, 23 и 24. Кроме того, предлагаемый дискриминатор средней частоты дает возможность точно определить погрешность его ра боты. Величина этой погрешности не зависит от степени разброса дискриминируемых частот и никогда не превосходит емкости счетчиков импульсов п.

Трехразрядный код на выходе пред лагаемого дискриминатора может принимать восемь различных значений.

Код 000 означает, что имеют мес

то f,

-f

f. следующие

f

среднее

При коде

соотношения: f .;

следовательно,

f/0

f, 0;

з .

значение имеет

fa 100 f,

fs f.; 3

- fo

f. - з

f, f.

fVf.fjfzчастота

0; f, f 0;

- среднее

частота f . Если код О;

2

f3 f,

f(i f,;

f,f ; f, - f,0; f,7f f o f, f, ч i частота

среднее И так

следовательно, значение имеет равен 010, то f - f, fa -

следовательно, f о f значение имеет далее.

Исходя из приведенных соотношений и неравенств, осуществляется использование кода для управления процессом мультиплексирования средней частоты.

Абсолютной ошибкой работы дискриминатора является количество импульсов выбранной (средней) частоты выВ.р которое проходит на вход устройства ее обработки за время,отсчитываемое от того момента, когда текущая выбранная частота перестала быть средней (изменилась в верхнюю или нижнюю сторону), и до момента изменения трехразрядного кода на выходных шинах 4, 5 и 6, т.е. до момента смены выбранной ранее частоты на новую, имеющую среднее значение в текущее время. Условия начала переключения при этом определяются соответственно выражениями

АГ CfsbiSp HaMs) О

или

d (f . (jt поим емйр

) 0.

При этом с момента начала выполие-55 лагаемого цифрового дискриминатора

средней частоты не зависит от дискретного характера построения схем привяз14и входных сигналов f, , f 2 :f, к тактовой сетке ТИ1 , ТИ2, ТИЗ.

ния одного из указанных условии до момента перехода на новую среднюю частоту максимальная абсолютная погрешность не превьш ает +п импульсов,

где п - емкость счетчика до разряда переполнения. Время t переключения предлагаемого дискриминатора с выбранной частоты на другую определяется периодом указанной разностной частоты и прямо пропорционально последнему:

t

- f.

BbiSp

пТ

.PttJM-1

Ра.н t

(3)

15

или

t

пТ

-выбр

- f

riawS

ро-ЗН.Э

5

(4)

На точность работы предлагаемого дискриминатора средней частоты практически не влияет начальный разброс фаз входных сигналов после очередного переключения с одной частоты на другую. Кроме того, как видно из выражений 3,4, время переключения предлагаемого цифрового дискриминатора средней частоты меняется в зависимости от степени разброса входньк сигналов по частоте. Чем ближе частоты по величине, тем мень35

40

45

50

ними, и тем

тем больше больше

ше разность меж,цу

значение Т или Тр

время переключения, и наоборот, чем

сильнее разброс входных частот,тем

Ра

их разменьше период Тр или Т| ностной частоты и тем быстрее происходит переключение дискриминатора. Таким образом, в отличие от известного частотного дискриминатора, в котором для повьшгения точности работы при слабом разбросе входных частот по величине необходимо увеличивать емкость счетчиков импульсов, в предлагаемом цифровом дискриминаторе средней частоты независимо от соотношения сравниваемых частот емкость счетчиков остается неизменной и принимают ее ,исходя из требований к точности работы устройства обработки средней частоты на всем диапазоне разброса дискриминируемых частот.

И, наконец, точность,работы пред

Формула изобретения

Цифровой дискриминатор средней частоты, содержащий три идентичньк каиала, каждый из которых содержит счетчик импульсов и первый триггер, прямой выход которого соединен с выходом канала, при этом первые входа первого и второго каналов соединены соответственно с первой и второй входными шинами, а выходы с первого по третий каналов соединены соответственно с первой по третью выходными кодовыми шинами, а также третью входную шину, отличающий- с я тем, что, с целью повышения точности дискриминирования средней частоты, в каждый из трех каналов введены с второго по четвертьй триггеры и элемент 2-2И-2Ш1И-НЕ, при этом S- и R-входы второго триггера соединены соответственно с первым и вторым входами канала, прямой выход соединен с D-вкодами первого и третьего триггеров, и входом управле

а) lULJUl

S liULJl

гуцил

в;

у|п

# haru-шг-и-итпппппппг-шпппл -uu-irinni-

ния счетчика импульсов, который выполнен реверсивным, а инверсный выход второго триггера - с D-входом четвертого триггера, при этом R-входы, третьего и четвертого триггеров соединены соответственно с вторым и первым входа1«ш канала, а инверсные выходы третьего и четвертого триггеров соединены с первыми входами соответственно первой и второй групп входов элемента 2-2И-2ИЛИ-НЕ, вторые входы первой и второй групп входов которого соединены соответственно с первым и вторьм входами канала, а выход - с тактовым входом счетчика импульсов, выход переполнения которого соединен с С-входами первого, третьего и четвертого триггеров,причем первый вход третьего канала соединен с первой входной шиной., второй вход первого канала соединен с второй входной тиной, а вторые входы второго и третьего каналов соединены с третьей входной шиной.

Составитель С. Вудович Редактор Е.Кравцова Техред В.Кадар, Корректор М. Демчик

Заказ 396/59 Тираж 902 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д,4/5

11роизводственно-полигра фическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотный дискриминатор | 1983 |

|

SU1119162A1 |

| Цифровой дискриминатор частоты импульсов | 1988 |

|

SU1582344A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1083356A1 |

| Устройство управления следящим приводом | 1986 |

|

SU1383288A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1984 |

|

SU1239622A1 |

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

| Кодовый датчик давления | 1986 |

|

SU1397758A1 |

| Устройство автоподстройки частоты | 1987 |

|

SU1467751A1 |

Изобретение может быть использовано для управления процессом выбора сигнала средней частоты из трех входных, поступающих от датчиков с частотно-зависимой характеристикой. Цель изобретения - повышение точности дискриминирования средней частоты. Цифровой дискриминатор состоит из трех каналов, каждый из которых включает реверсивные счетчики 22,23 и 24 и выходные триггеры 1, 2 и 3. В каждый канал цифрового дискриминатора введены триггеры 7-9, 13 - 15 и 16 - 18 и элементы 2-2И-2ИЛИ-НЕ 19 - 21. Триггеры 13-18 каналов на своих прямых выходах формируют сигнал управления режимом работы счетчиков 22 - 24 импульсов своих (Л ОФ сд

| Цифровой частотный дискриминатор | 1982 |

|

SU1083356A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-28—Публикация

1985-10-02—Подача