31582344

Изобретение.относится к импульс-( | ной технике и может быть использовано для оыбора заданной частоты, как средней, так и минимальной или макси- , мальной, при работе с частотно-импульсными датчиками.

Цель изобретения - повышение точности выбора частоты за счет уменьшения количества импульсов входной Q частоты, которое проходит за время, отсчитываемое от того момента, когда текущая выбранная частота изменила свое значение, до момента изменения кода на выходе устройства. 15

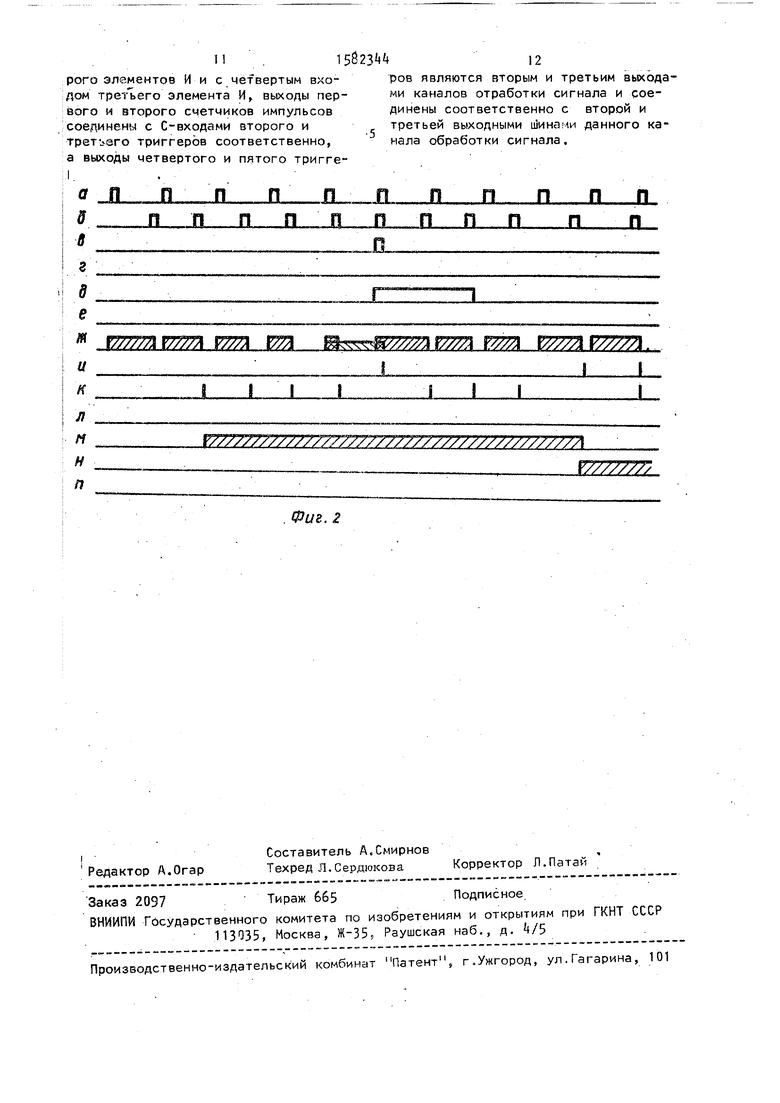

На фиг. 1 приведена структурная схема цифрового дискриминатора частоты импульсов; на фиг. 2 -,диаграммы его работы для одного канала обработки сигнала.20

На фиг. 2 приняты следующие обозначения: а - первый вход; б - второй вход , в - первый выход блока выделения разностной частоты г - второй выход блока выделения разностной 25 частоты; д - выход второго триггера; е - выход третьего триггера; ж величина сдвига; и - выход А В элемента сравненияj к - выход А 3

-выход А В

-первый выход второй выход третий выход

30

35

элемента сравнения; л элемента сравнения, м канала (f f6); н - канала (fА fe) ; п - канала (fА f6).

Цифровой дискриминатор частоты импульсов содержит идентичные первый второй и третий каналы 1-3 обработки сигнала, каждый из которых содержит первый и второй счетчики 4 и 5 импульсов, с первого по пятый триг- 4о геры 6-10, блок 11 выделения разностной частоты, первый, второй и третий формирователи 12-14 импульсов, первый и второй блоки 15 и 16 задержки, первый и второй регистры 17 и 18, 45 элемент 19 сравнения, первый, второй и третий элементы И 20 - 22, с первого по пятый элементы ИЛИ , а также первую, вторую и третью входные шины 28 - 30, первую, вторую и третью 5Q выходные шины 31 33 первого канала 1 обработки сигнала, первую, вторую и тоетью выходные шины 34 36 второго канала 2 обработки сигнала, первую, вторую и третью выходные шины 37 - 39 третьего канала 3 обработки сигнала.

Первая, вторая и третья входные шины 28 - 30 соединены соответствен55

Q 5

0

5

0

5

о 5 Q

5

но с первыми входами блоков 11 первого, второго и третьего каналов 1-3, кроме того, (первая входная шина 28 подключена к второму входу блока 11 второго канала 2, вторая входная шина 29 подключена к второму входу блока 11 третьего канала 3, а третья входная шина 30 - к второму входу блока 11 первого канала 1. В каждом канале первый вход блока 11 для выделения разностной частоты соединен со счетным входом первого счетчика 4 и входом первого формирователя 12. Второй вход блока 11 подключен к счетному входу второго счетчика 5 и к входам второго и третьего формирователей 13 и 14. Первый выход блока 11 соединен с S-входом второго триггера 7 и первым входом первого элемента ИЛИ 23, выход которого подключен к S-входу первого триггера 6 и к первым входам второго и третьего элементов ИЛИ 2k и 25. Второй выход блока 11 соединен с S-входом третьего триггера 8 и первым входом четвертого элемента ИЛИ 26, выход последнего подключен к S-входу четвертого триггера 9 к второму входу третьего элемента ИЛИ 25 и первому входу пятого элемента ИЛИ 27. Вторые входы четвертого и первого элементов ИЛИ 26 и 23 соединены соответственно с выходами первого и второго элементов И 20 и 21, первые входы которых подключены к выходам второго и третьего триггеров 7 и 8 и к R-входам первого и второго счетчиков 4 и 5 соответственно, а также к первому и второму входам третьего элемента И 22, выход которого соединен с S-входом пятого триггера 10 и с вторыми входами второго и пятого элементов ИЛИ 2k и 27. Выход первого формирователя 12 подключен к входу первого блока 15, выходы которого поразрядно соединены с D-входами первого регистра 17( выходы которого поразрядно подключены к D-входам второго регистра 18 и к первой группе входов элемента 19, вторая группа входов которого поразрядно подключена к выходам второго регистра 18. Выход А В элемента 19 соединен с вторым входом первого элемента И 20, выход А В - с вторым входом второго элемента И 21. а выход А В - с третьим входом третьего элемента И 22, выход третьего формирователя 14 подключен к С-входам

второго регистра 18. Выход второго блока 16 соединен с третьими входами первого и второго элементов И 20 и 21 и с четвертым входом третьего элемента И 22. Выходы первого и второго счетчиков k и 5 соединены с С-входами второго и третьего триггеров 7 и 8 соответственно. Выходы пер- вого, четвертого и пятого1 триггеров 6, 9 и 10 первого канала 1 соединены с первой, второй, третьей выходными шинами соответственно, аналогично выходы второго канала 2 соединены с шинами 3 - 36, а выходы третьего канала 3 - с шинами . Выходные шины 31-39 являются выходами цифрового дискриминатора частоты.

Величина задержки первого блока 15 должна быть не меньше периода следования входных импульсов. Количество выходов может быть любым, с их увеличением повышается точность сравнения частот. Величина задержки второго блока 16 должна превышать суммарную величину задержки, вносимую первым и вторым- регистрами 17 и 18 и элементом 19, но быть меньше длительности паузы между импульсами входной частоты. Блоки 15 и 16 задержки могут быть реализованы любым способом, например на линиях задержки.

Блок 11 для формирования импульсов разностной частоты должен выдавать импульс на свой первый выход, если частота на первом его входе ниже частоты на его втором входе, если на первом входе частота выше, то импульс должен выдаваться на второй выход. В качестве такого блока можно использовать известное устройство.

Цифровой дискриминатор работает следующим образом.

Перед началом работы схема устанавливается в исходное состояние, обнуляется. На фиг 1 цепи сброса условно не показаны. Второй и третий триггеры 7 и 8 обнуляются подачей сигнала на R-вход, и своим высоким потенциалом с инверсного выхода они обнуляют первый и второй счетчики k и 5. Для обнуления первого, четвертого и пятого триггеров 6, 9 и 10 можно использовать С-вход или пода- вать сигналы на R-входы через элементы ИЛИ. После подачи сигнала Сброс на всех выходных шинах уст5823 й

0

5

0

5

0

5

5

0

5

ройства устанавливается низкий (ну- левой) потенциал.

Так как устройство каналов одинаково, рассмотрим работу одного кана- ла, например первого канала 1.

Входные импульсы с входных шин 28 и 30 поступают на вход блока 11 (фиг. 2а, б). Допустим, на входную шину 30 поступило два импульса, а на входную шину 28 - один, тогда на первом выходе блока 11 (фиг. 2в) формируется импульс, который через первый элемент ИЛИ 23 поступает на S-вход первого триггера 6 и устанавливает его в единичное состояние (фиг. 2м), т.е. на первой выходной шине 31 первого канала 1 формируется сигнал о том, что частота на входной шине 30 превышает частоту на входной шине 28, Кроме того, импульс с первого выхода блока 11 устанавливает в единичное состояние второй триггер 7 (фиг. 2д), который низким потенциалом со своего инверсного выхода закрывает связанные с ним первый и третий элементы И 20 и 22, а также снимает сброс с первого счетчика k. В случае дальнейшего поступления импульсов только на входную шину 3 состояние указанных элементов не изменяется. Если импульсы на входные шины 28 и 30 поступают поочередно, то блок 11 перестает формировать на своем выходе импульсы, первый счетчик k по второму импульсу, пришедшему на входную шину 28 после снятия с него сброса, устанавливает в нулевое состояние второй триггер 7 (фиг. 2д). Так как импульс с выхода счетчика поступает на С-вход, то триггер 7 обнуляется по его окончании. После установки первого триггера 7 в исходное состояние открываются по первым входам первый и третий элементы И 20 и 22.

Рассмотрим, как работает дискриминатор при поочередном поступлении входных импульсов.

С первой входной шины 28 импульс через первый формирователь 12 поступает на вход первого блока 15 и начинает продвигаться по нему. Так как величина задержки первого блока 15 не меньше времени между входными импульсами, то импульс,сформированный вторым формирователем 13 по заднему фронту импульса с третьей входной шины 30, поступает на С-входы первого регистpa 1; в TdKoe время, когда на каком то из выходов первого блока 15 при- сугстпует сигнал, т,е, взаимный сдаиг импульсов на первой и третьей „ входных шинах (фиг. 2ж) отражается кодом, записанным в первый регистр 17. В первый регистр 17 каждый период по заднему фронту импульса с третьей входной шины 30 записывается JQ код фазового сдвига сравниваемых

частот. По переднему фронту импульса третьей входной шины 30, сформиро- ванному третьим формирователем Ik,

указанный код переписывается во вто- 55 рой регистр 18, Таким образом, во втором регистре 18 хранится код фа

Зового сдвига сравниваемых частот предыдущего периода, а в первом ре- гистре 17 текущего периода. Элемент 2Q

19 сравнивает коды на выходах перво- го и второго регистров 17 и 18 и формирует один из трех сигналов (фиг. 2и, к, л).

Сигнал А В формируется, если 25 значение кода в первом регистре 17 превышает значение кода во втором регистре 18 (фиг. 2л), сигнал - если код второго регистра 18 больне (фиг, 2м), и сигнал Аь В - при рз- 30 венстве кодов (фиг, 2н), Сигналы с выходов элемента 19 (фиг. 2и к, л) поступают на элементы И 20 - 22, которые также связаны с выходами второго 7 и третьего 8 триггеров м выходом второго блока 16 задержки Первый, второй и третий элементы И 20 - 22 открыты по входам, соеди - ненным с выходами второго и третьего триггеров 7 и 8.Ф

Так как величина задержки на втором блоке 16 превышает суммарное аремя задержки на первом и втором регистрах 17 и 18 и элементе 19 то импульс, сформированный вторым форми- дз рователем 13 и задержанный вторым блоком 16, поступает на первый, второй и третий элементы И 20 - 22 после того, как элемент 19 сформирует сигнал, соответствующий соотношению кодов. Если частота на первой входной шине 28 выше5 чем частота на третьей входной шине 30 (фиг. 2a,6)s то фазовый сдвиг между входнымм импульсами увеличивается, значение ко- да в каждом последующем периоде становится меньше и элемент 19 формирует сигнал на выходе A f В (фиг. 2;) . В этом случае импульс с

35

Q

5 0

з

5

выхода второго блока 16 устройства задержки через первый элемент И 20 и четвертый элемент ИЛИ 26 устанавливает в единичное состояние третий триггер 9 и на втором выходе 32 появ- пяется сигнал (фиг. 2н). Если частота на первой входной шине 28 (фиг.2а) ниже частоты на третьей входной шине 30 (фиг. 26), то элемент 19 формиру- ет сигнал на выходе А В (фиг.2к) и задержанный вторым блоком 16 импульс через второй элемент И 21 и первый1 элемент ИЛИ 23 устанавливает в единичное состояние первый триггер 6 и через элемент ИЛИ 24 обнуляет третий триггер 9. На первом выходе 31 появляется сигнал (фиг. 2м) а на втором выходе 32 сигнал пропадает (фиг. 2н). Если частоты на первой и третьей входных шинах 28 и 30 равны, тс элемент 19 формирует сигнал на выходе А - В, а импульс с выхода второго блока 16 устанавливает в единичное состояние пятый триггер 10 и через второй и пятый элементы И 2 и 27 обруляет первый и четвертый триггеры 6 и 9.

Таким образом, при значительном рассогласовании входных частот их сравнение осуществляет блок 11 выделения разности частот, при этом импульсом с соответствующего выхода блока 11 устанавливаются в единичное состояние первый и второй триггеры 6 и 7 или четвертый и третий триггеры 9 и 8. Срабатывание второго 7 или третьего 8 триггеров блокирует прохождение импульса с выхода второго блока 16, исключая работу элемента 19 (фиг, 2д, и, н). При малой разности частот их сравнение осуществляет элемент 19.

Остальные канапы устройства работают аналогично описанному, Комбинация сигналов на выходах трех каналов позволяет определить соотношение входных частот. Из описания работы устройства следует, что на первых выходных шинах 31, 3 и 37 первого, второго и третьего каналов 1 - 3 фоомируется сигнал, если частота на первом входе канала ниже частоты на втором входе канала, на вторых выходных шинах 32, 35 и 38 первого, второго и третьего каналов 1 - 3 формируется сигнал, если частота на первом входе канала выше частоты на втором входе канала, на третьих выходных шинах 33, 36 и 39 первого, второго и третьего каналов 1 - 3 формируется сигнал при равенстве частот на входах канала.

Избыточность выходов позволяет осуществлять дискриминирование входных частот с повышенной надежностью, т.е. отказ любого элемента устройства не влияет на конечный результат.

Так как выходные сигналы формируют по результатам обработки текущего и предыдущего периодов, то сигналы на выходах дискриминатора изменяются сразу после изменения разности входных частот. Благодаря этому повышается точность выбора частоты в условиях изменения входных частот.

Формула изобретения 20

Цифровой дискриминатор частоты импульсов, содержащий идентичные первый, второй и третий каналы обработки сигнала, каждый из которых содержит первый счетчик импульсов, с первого по четвертый триггеры, при этом выход первого триггера подключен к первому выходу данного канала обработки сигнала, первые входы первого, второго и третьего каналов обработки сигнала соединены соответственно с первой, второй и третьей входными шинами, первые выходы первого, второго и третьего каналов обработки сигнала соединены с первой группой выходных шин этих каналов, первый вход первого канала обработки сигнала подключен к второму входу второго канала обработки сигнала, первый вход второго канала обработки сигнала - к второму входу третьего канала обработки сигнала, первый вход третьего канала обработки сигнала - к второму входу первого канала обработки сигнала, отличающийся тем, что, с целью повышения .точности выбора, частоты, в каждый из каналов обработки сигнала введены блок выделения разностной частоты, первый, второй и третий формирователи импульсов, второй счетчик импульсов, пятый триггер, первый и второй блоки задержки, первый и второй регистры, элемент сравнения, первый, второй и третий элементы И, с первого по пятый элементы ИЛИ, при этом первый вход каждого канала обра ботки сигнала соединен с первым вхо10

25

20

дом блока выделения разностной частоты, со счетным входом первого счетчи ка импульсов и входом первого формирователя импульсов, второй вход каждого канала обработки сигнала подключен к второму входу блока выделения разностной частоты, к счетному входу счетчика импульсов и к входам второго и третьего формирователей импульсов, первый выход блока выделения разностной .частоты соединен с S-входом второго триггера и первым входом первого элемента ИЛИ, выход которого подключен к S-входу первого триггера и к первым входам второго и третьего элементов ИЛИ, второй выход блока выделения разностной частоты соединен с S-входом третьего триггера и первым входом четвертого элемента ИЛИ, выход которого подключен к S-входу четвертого триггера, к второму входу третьего элемента ИЛИ и к первому входу пятого элемента ИЛИ, при этом вторые входы четвертого и первого элементов ИЛИ соединены соответственно с выходами первого и второго элементов И, первые входы которых подключены к выходам второго и третьего триггеров соответственно, к R-входам первого и второго счетчиков соответственно, а также к перво-; му и второму входам третьего элемента И соответственно, выход котооого соединен с S-входом пятого триггера и с вторыми входами второго и пятого элементов ИЛИ, а выход пеового формирователя импульсов подключен к входу первого блока задержки, выходы которого соединены поразрядно с D-входа- ми первого регистра, выход второго формирователя импульсов подключен к входу второго блока задержки и к С-входам первого регистра, выходы которого поразрядно соединены с D-входами второго регистра и с первой группой входов элемента сравнения, вторая группа входов которого подключена поразрядно к выходам второго регистра, при этом выход А : В элемента сравнения соединен с вторым входомпервого элемента И, выход А В с вторым входом первого элемента И, а выход А Б - с третьим входом третьего элемента И, выход третьего формирователя импульсов подключен к С-входам второго регистра, выход второго блока задержки соединен с третьими входами первого и вто30

35

40

45

50

55

11

рого элементов И и с четвертым входом третьего элемента И, выходы первого и второго счетчиков импульсов соединены с С-входами второго и третьего триггеров соответственно, а выходы четвертого и пятого тригге- I

15823М12

ров являются вторым и третьим выходами каналов отработки сигнала и соединены соответственно с второй и третьей выходными шинами данного канала обработки сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2019 |

|

RU2713624C1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2020 |

|

RU2759511C1 |

Изобретение относится к импульсной технике и может быть использовано для выбора минимальной, средней или максимальной из трех частот. Целью изобретения является повышение точности выбора путем уменьшения задержки изменения кода на выходных шинах при изменении входных частот. Для достижения цели в устройстве, содержащем каналы 1 - 3, в каждый из которых входят счетчик 4, триггеры 6 - 9, введены в каждый канал счетчик 5, триггер 10, блок 11 выделения разностной частоты, формирователи 12 - 14 импульсов, блоки 15, 16 задержки, регистры 17, 18, элемент 19 сравнения, элементы И 20 - 22, элементы ИЛИ 23 - 27. Каждый канал 1 - 3 сравнивает две из трех входных частот. В случае, когда между двумя импульсами одной из входных частот приходят два импульса другой входной частоты, появляется импульс на одном из выходов блока 11 и устанавливается триггер 6 или триггер 9. Если импульсы на входах чередуются, с помощью блока 15 задержки, регистров 17 и 18 и элемента 19 сравнения анализируется изменение фазового сдвига этих импульсов, знак приращения которого зависит от знака разности частот. При этом также устанавливается один из триггеров 6, 9, 10. 2 ил.

Фиг. 2

| Цифровой частотный дискриминатор | 1980 |

|

SU907793A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой дискриминатор средней частоты | 1985 |

|

SU1293835A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-30—Публикация

1988-10-24—Подача