Изобретение относится к области автоматики и предназначено для использования в системах числового программного управления (СЧПУ) стан- «ами.

Цель изобретения - расширение области применения.

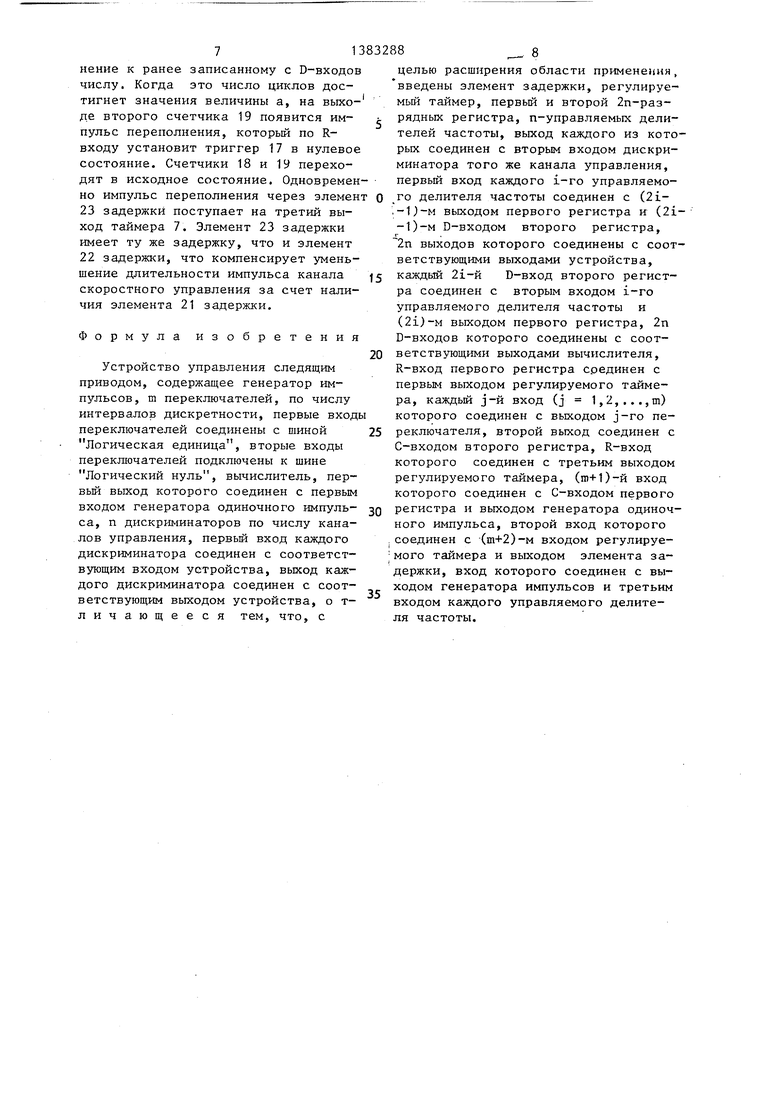

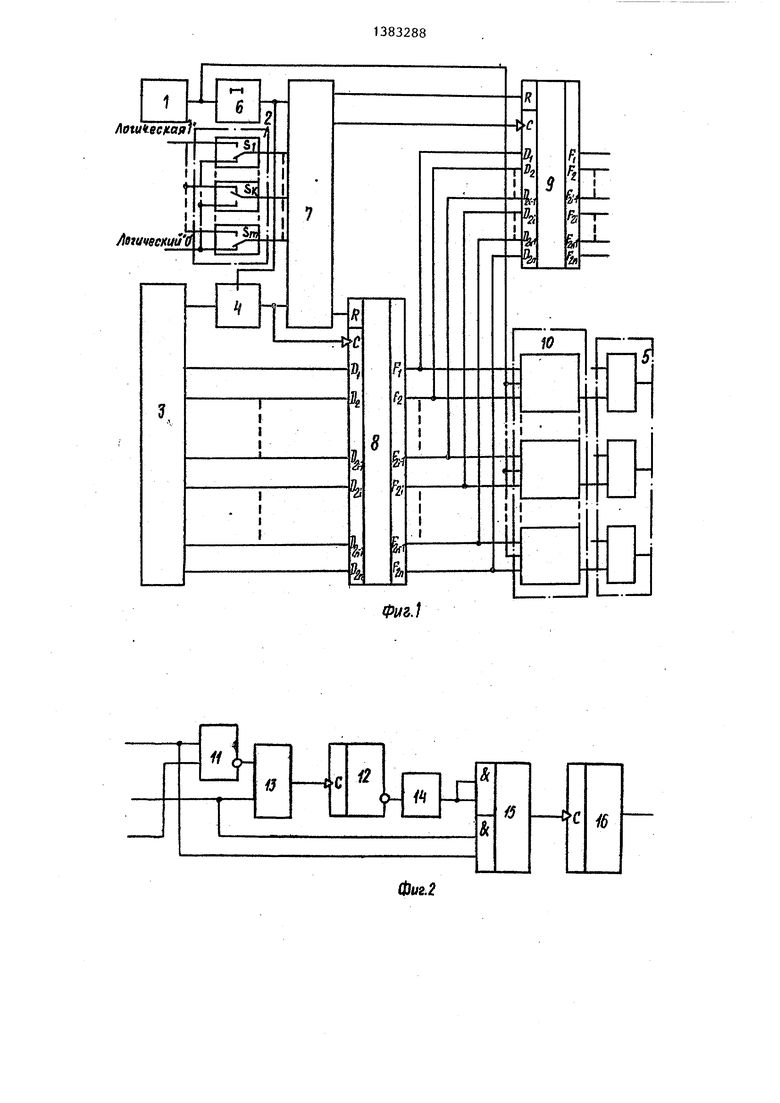

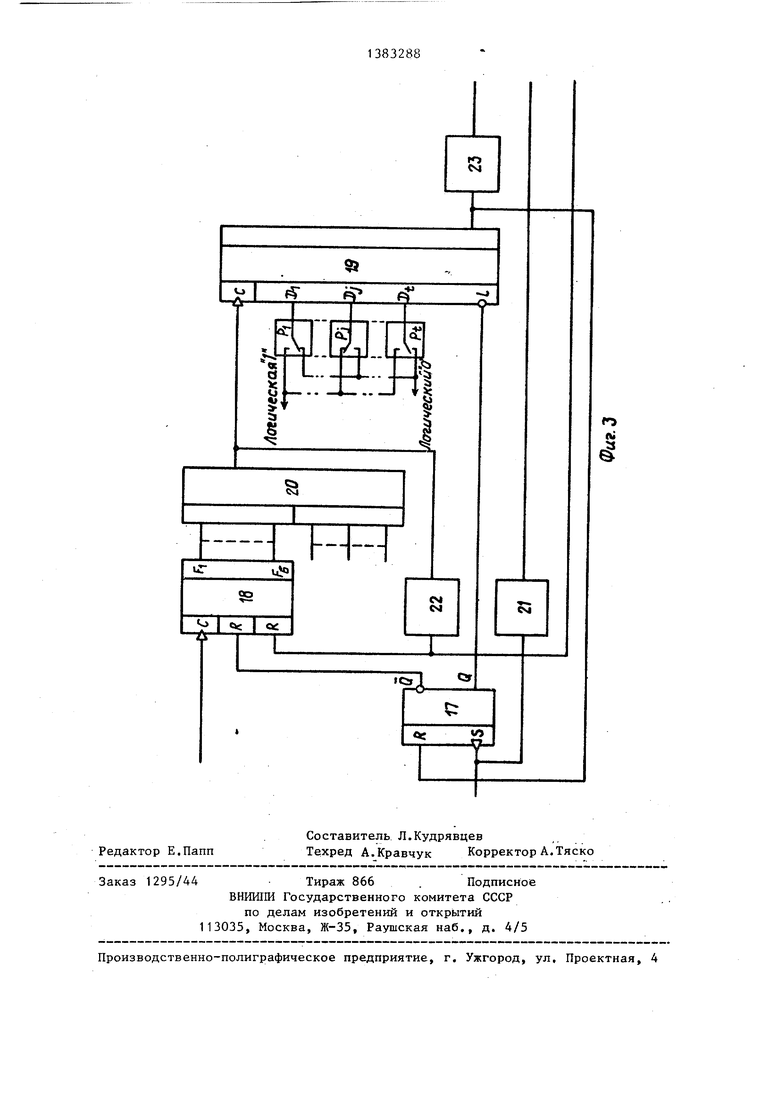

На фиг. 1 приведена функциональна схема устройства управления следящим приводом, на фиг. 2 - схема управляемого делителя частоты, на фиг.З - схема блока таймера.

Устройство содержит генератор 1 импулЬсов, m переключателей 2, вычислитель 3, генератор А одиночного импульса, п дискриминаторов 5, элемент 6 задержки, регулируемый таймер 7j первый и второй 2п-разрядных регистра 8 и 9 и п управляемых делителей 10 частоты.

Управляемый делитель 10 частоты содержит элемент 2ИЛИ-НЕ 11, триггер 12, элемент 2И 13, формирователь 14 импульсов, элемент 2-2И-2ИЛИ 15 и делитель 16-частоты.

Регулируемый таймер 7 содержит триггер 17, первый 18 и второй 19 счетчики, мультиплексор 20, второй 21, третий 22 и четвертый 23 элемен- ть1 задержки.

Устройство работает следующим образом.

После включения, а также в исходном состоянии импульсы на выходах вычислителя 3 отсутствуют. Поэтому на выходе генератора 4 одиночного импульса импульсов тоже нет. В результате состояние блока 7 таймера остается неизменным, на его выходах импульсов нет, а регистры 8 и 9 сохраняют свое нулевое состояние. Отсут ствие на первом и втором входах управляемых делителей 10 частоты управ ляющих сигналов с выходов регистра 8 устанавливает для указанньпс делителей обычный режим деления тактовой последовательности импульсов с выхода генератора 1 импульсов с периодом следования, равным Т. С выхода уп- равляемых делителей 10 частоты импульсы, имеющие постоянное временное положение (фазу), поступают на вторые входы дискриминаторов 5 соответственно. На первые входы дискрими- наторов с той же частотой поступают импульсы (сигнал обратной сврзи) из группы п входов устройства и на выходе дискриминаторов формируются

0

5

5 0 5 Q 5

0

управляющие сигналы, составляющие, первую группу из п выходов устройства.

Таким образом, в исходном состоянии, а при включении уже после отработки возможного рассогласования, на выходе каждого дискриминатора рассогласования нет, а импульсы на первом их входе имеют сдвиг по фазе в 180 относительно импульсов на втором входе.

С началом работы вычислителя 3 на jero группе выходов начинают появлятьг ся импульсы, количество которЬгх по- каждому выходу определяет величину перемещения. Эти импульсы синхронизированы в вьиислителе 3 импульсами, которые поступают -с выхода вычислителя 3 на первый вход генератора 4 одиночного импульса. Частота их следования намного меньше частоты следования выходных импульсов генератора 1 импульсов.

С поступлением импульса на первьш вход генератора 4 одиночного импульса на его выходе формируется импульс, синхронизированньй очередным импульсом генератора 1 импульсов, который через элемент 6 задержки поступает на второй вход генератора 4, одиночного импульса. Передним фронтом сформированного импульса через С-вход первого регистра 8 производится запись в него с D-входов единицы или нуля, соответствующих наличию или отсутствию импульса в группе выходов вычислителя 3, Эта информация через выходы первого регистра 8 подается на одноименные разряды D-входов второго регистра 9 и на соответствующие первые или вторые входы управляемых делителей частоты каждого из п каналов управления. Кроме того, выходной импульс генератора 4 одиночного импульса поступает на первьм вход таймера 7. На выходах таймера 7 появляются импульсы с задержкой относительно импульсов на его первом входе, а именно на втором выходе на величину t, , на первом выходе , на третьем выходе , причем t, : ЕГ з ,

Ввиду идентичности и независимости каналов управления дальнейшую работу устройства рассмотрим по i-му -яналу управления.

При работе вычислителя 3 возможны следующие случаи.

Случай 1, Импульсы из вычислителя 3 на D,;,) - и -входы первого регистра 8 не поступают. Поэтому по импульсу на С-входе первого регистра 8 на его F..,- и -выходах сохраняется нулевое состояние и оно не изменится после поступления импульса на R-вход первого регистра 8, Аналогично не изменится нулевое состояние и -выходов второго регистра 9 после поступления импульсов на его С- и R-входы. Отсутствие управляющих сигналов на первом и втором входах управляемого делителя 10 час- тоты обеспечивает неизменность фазы его выходных импульсов. Поэтому на выходе дискриминатора 5 сигналы аналогичны сигналам в исходном состояни

Случай 2. Из вычислителя 3 на В,,-вход первого регистра 8 поступа ет импульс для положительного переме щения. Одновременно на выходе вычислителя 3 появляется импульс, которьй через генератор 4 одиночного импуль- са осуществляет запись в первьй регистр 8, так что на Fjj.,-выходе последнего появляется управляющий сигнал. Этот сигнал по первому входу управляемого делителя 10 частоты уменьшает коэффициент деления последнего в два раза. В зависимости от того, через какое число К периодов (К 1,2,...) тактовой последовательности импульсов с выхода генератора 1 импульсов на R-вход первого регистра 8 придет импульс сброса, указанная выше операция будет эквивалентна добавлению К импульсов в тактовую последовательность импульсов на третьем входе управляемого делителя 10 частоты. В результате на его выходе фаза импульсной последовательности сдвинется на К шагов в положительном направлении.

Случай 3. Из вычислителя 3 на вход первого регистра 8 поступает импульс для отрицательного перемещения. Здесь имеет место изложенное в случае 2 с тем отличием, что сигнал F,; -выхода первого регистра 8, поступая на второй вход управляемого делителя 10 частоты, запретит прохождение импульсов тактовой последовательности через указанный делитель Такая операция эквивалентна вычита нию К импульсов.

Изменение фазы импульсной последовательности на втором входе дискри

юJ5

20 25 0

35

40

45

.50

55

минатора 5 на К шагов в положитель- ном или в отрицательном направлении вызьюает на его выходе рассогласование.

В рассмотренных выше случаях 2 и 3 управляющий сигнал с выходов первого регистра 8 подавался, кроме того, на соответствующие входы второго регистра 9. Импульсом по С-входу в него производилась запись, а следующим затем импульсом осуществлялся сброс по R-входу. В результате при импульсе положительного перемещения .на Fjj-., -выходе второго регистра 9, а при импульсе отрицательного перемещения на Fjj -выходе, формируется импульс канала скоростного управления, который является дополнительным выходным воздействием к сигналу рассогласования на выходе дискриминатора 5, что повьнпает динамические свойства устройства управления.

Длительность импульса канала скоростного управления, равная Г -a c , где а 1,2,..., в зависимости от требуемых динамических характеристик устройства может быть изменена в широком диапазоне путем соответствующей установки таймера 7. которая определяет величину числа а.

С другой стороны, масштабное преобразование на К шагов перемещений, определяемых вычислителем 3, устанавливается с помощью подключения переключателя 2 S к логической 1, а остальных - к логическому О. Поэтому импульс на первом выходе таймера 7 появляется с задержкой на величину 2 i kT.

Таким образом, с помощью таймера 7 -длительность импульса канала скоростного управления, равная 2Г, a k T, может быть изменена изменением величины коэффициента а с учетом требований к динамическим характеристикам устройства, в то же время величина Tj остается пропорциональной величине заданной на m переключателях дискретности, что обеспечивает постоянство динамических характеристик во всем допустимом диапазоне значений дискретностей.

Для обеспечения работоспособности устройства величина должны быть меньше наименьшего периода следования импульсов с выхода вычислителя 3.

Пример реализации управляемого делителя частоты приведен на

фиг,, 2, Делитель работает следующим образом. При отсутствии сигналов на перпом и втором входах управляемого делителя частоты сигнал с выхода элемента 2ИЛИ-НЕ 11 разрешает прохождение тактовой последовательности на вход триггера 12 через элемент 2И 13.С инверсного выхода триггера 12 через формирователь 14 импульсов и элемент 2-2И-25ШИ 15 импульсы поступают на вход делителя 16 частоты. Коэффициент деления импульсов тактовой последовательности в этом случае равен номинальному значению. При поступлении сигнала на первьй вход элемента 2ИЛИ-НЕ 11 блокируется прохождение импульсов тактовой последовательности на вход триггера 12 и разрешается их прохождение через элемент 2-2И-2ШШ 15 сразу на вход делителя 16 частоты. При этом коэффи- цинт деления управляемого делителя частоты уменьшается в два раза, что эквивалентно поступлению в управляе- мьй делитель частоты дополнительного числа импульсов. Их количество равно числу периодов импульсов тактовой последовательности, в течение которы присутствует сигнал на первом входе элемента 11.

Поступление сигнала на второй вхо делителя частоты с переменным коэффициентом деления блокирует через элементы 2ИЛИ-НЕ 11 и 2И 13 прохождение импульсов тактовой последовательности, что эквивалентно вычитанию из управляемого делителя частоты определенного числа импульсов. Их количество равно числу периодов импульсов тактовой последовательности, в течение которых присутствует сигнал на втором входе управляемого делите- ля частоты,

Пример реализации таймера 7 приведен на фиг. 3. В исходном состоянии триггер 17 находится в нулевом состоянии и импульсы с первого входа блока на его динамический S-вход установки в единицу не поступают. В результате с Q-выхода триггера 17 на первый R-вход сброса первого счет чш-са 18 подается логическая 1 и первый счетчик 18 находиися в нулевом состоянии. Поэтому подсчет входных импульсов тактовой последовательности, поступающих через второй вх(д таймера 7 им не производится. Уровнем логического О с Q-выхода

триггера 17 через L-вход разрешения записи во втором счетчике 19 фикси- руется состояние его D-входов. На

этих входах с помощью переклк чателей Р,, ..., Р:,..., Р таймера 7 устанавливается число, дополняющее число а до числа переполнения второго счетчика 19.

Через группу входов таймера 7 на один иё логических входов мультиплексора 20 подается логическая 1, а на остальные - логический О, По- рядковьй номер логического входа

единицы соответствует числу k+1, так как счет логических входов ведется от нуля. Каждое состояние выходов первого счетчика 18 через группу входов управления мультиплексора 20 подключает к выходу последнего соответствующий логический вход. Поскольку число k не равно нулю, то при нулевом состоянии выходов первого счетчика 18 в режиме сброса на выходе мультиплексора 20 сигнала нет.

С приходом импульса на первьй вход таймера 7 он через элемент 21 задержки поступает на второй выход блока. Величина времени задержки масла

и определяется временем записи информации в первый регистр 8. Кроме того, по заднему фронту поступившего импульса триггер 17 устанавливается в единицу, в результате чего логическая 1 по первому R-вХоду сброса первого счетчика 18 снимается. По переднему фронту очередного импульса, на счетном входе первьй счетчик 18 начинает работать в режиме счета, при этом состояние его выходов меняется, последовательно подключая логические входы к выходу мультиплексора 20. При подсчете k-ro импульса к его выходу будет подключен логический вход, имеющий значение единицы. Импульс с выхода мультиплексора 20 через элемент 22 задержки поступает на первый выход блока, а также на вто- v рой R-вход для сброса первого счетчика 18 в нуль, после чего цикл счета возобновится от нуля. Время задержки элемента 22 задержки мало и определяется необходимостью надежно- - го сброса первого счетчика 18.

При установке триггера 17 в единицу с его р-вькода снимается значение логического О, с L-входа при этом счетчик 19 начинает считать число циклов работы счетчика 18 в допол-

нение к ранее записанному с D-входов числу. Когда это число циклов достигнет значения величины а, на выхо- де второго счетчика 19 появится импульс переполнения, который по R- входу установит триггер 17 в нулевое состояние. Счетчики 18 и 19 переходят в исходное состояние. Одновременно импульс переполнения через элемент 23 задержки поступает на третий выход таймера 7. Элемент 23 задержки имеет ту же задержку, что и элемент 22 задержки, что компенсирует уменьшение длительности импульса канала скоростного управления за счет наличия элемента 21 задержки.

Формула изобретения

Устройство управления следящим приводом, содержащее генератор импульсов, ш переключателей, по числу интервалов дискретности, первые входы

переключателей соединены с шиной Логическая единица, вторые входы переключателей подключены к шине Логический нуль, вычислитель, пер- вьй выход которого соединен с первым входом генератора одиночного импульса, п дискриминаторов по числу каналов управления, первьй вход каждого дискриминатора соединен с соответствующим входом устройства, выход каждого дискриминатора соединен с соответствующим выходом устройства, о т- личающееся тем, что, с

т

О

15

83288 8

целью расширения области применения, введены элемент задержки, регулируемый таймер, первый и второй 2п-раз- рядных регистра, п-управляемых делителей частоты, выход каждого из которых соединен с вторым входом дискриминатора того же канала управления, первый вход каждого i-ro управляемого делителя частоты соединен с (2i- .-1)-м выходом первого регистра и (21- -1)-м D-входом второго регистра, 2п выходов которого соединены с соответствующими выходами устройства, каждБЙ 21-й D-вход второго регистра соединен с вторым входом i-ro управляемого делителя частоты и (2i)-M выходом первого регистра, 2п D-входов которого соединены с соответствующими выходами вычислителя, R-вход первого регистра срединен с первым выходом регулируемого таймера, каждьй j-й вход (j 1,2,,,,,m) которого соединен с выходом j-ro переключателя, второй выход соединен с С-входом второго регистра, R-вход которого соединен с третьим выходом регулируемого таймера, (п)+1)-й вход которого соединен с С-входом первого регистра и выходом генератора одиночного импульса, второй вход которого соединен с (т+2)-м входом регулируемого таймера и выходом элемента задержки, вход которого соединен с выходом генератора импульсов и третьим входом каждого управляемого делителя частоты.

20

25

30

35

n

At

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления следящим приводом | 1986 |

|

SU1416939A1 |

| Электронные часы со звуковой сигнализацией | 1986 |

|

SU1377817A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Устройство для управления следящим приводом | 1985 |

|

SU1278810A1 |

| ДИСКРИМИНАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2002 |

|

RU2234729C2 |

| Устройство для управления следящим приводом | 1985 |

|

SU1308988A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство контроля состояния объектов | 1985 |

|

SU1366993A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

Изобретение относится к автоматике и предназначено для использова-- ния в системах числовогЪ программно го управления станками. Целью изобретения является расширение области применения устройства управления следящим приводом. Поставленная цель достигается тем, что в устройство, которое содержит генератор импульсов с периодом следования Т, m переклюкий О, где га 1, 2, вычислитель, выход которого соединен с первым входом генератора одиночного импульса, п каналов управления, каждый- из которых содержит дискриминатор, введены элемент задержки, блок таймера, первьй и второй 2п-разрядные регистры, а в каждый канал управления - управляемьй делитель частоты. Б каждом канале управления дискриминатор, работающий в фазовом режиме, сравнивает фазу импульсов обратной связи группы входов устройства с фазой импульсов на выходе управляемого делителя частоты. При разности фаз, отличной от 180 , на выходе дискри- минатора формируется сигнал рассогласования, поступающий на первую группу выходов устройства. При расчете траектории вычислитель формирует импульсы положительного или отрицательного перемещения по каждому каналу управления. Эти импульсы записьюаются в первьй регистр, а с его выхода - во второй регистр. На выходах второго регистра формируются импульсы канала скоростного управления, поступающие на выход устройства. 3 ил. S (Л С со 00 со ts5 сх 00

h-l-l

QO

о I QcTog

CM CM

ем

| Устройство для управления следящим приводом | 1977 |

|

SU682870A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-23—Подача