Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки информации.

Цель изобретения - повышение быстродействия устройства.

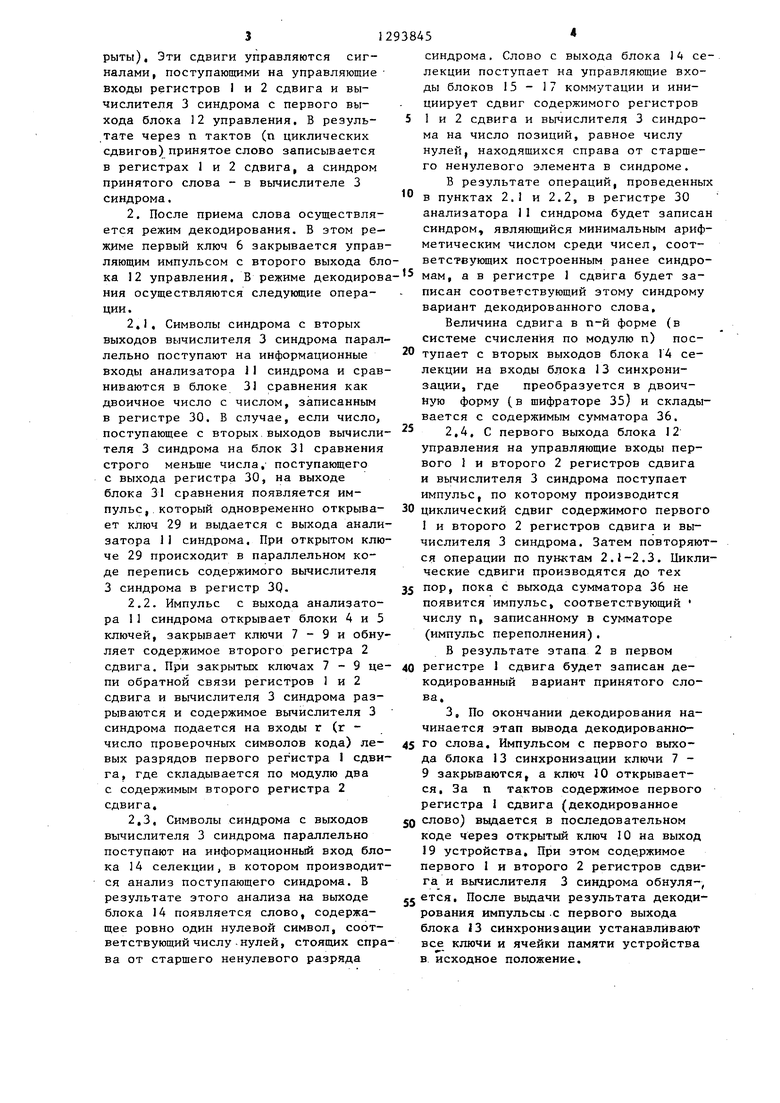

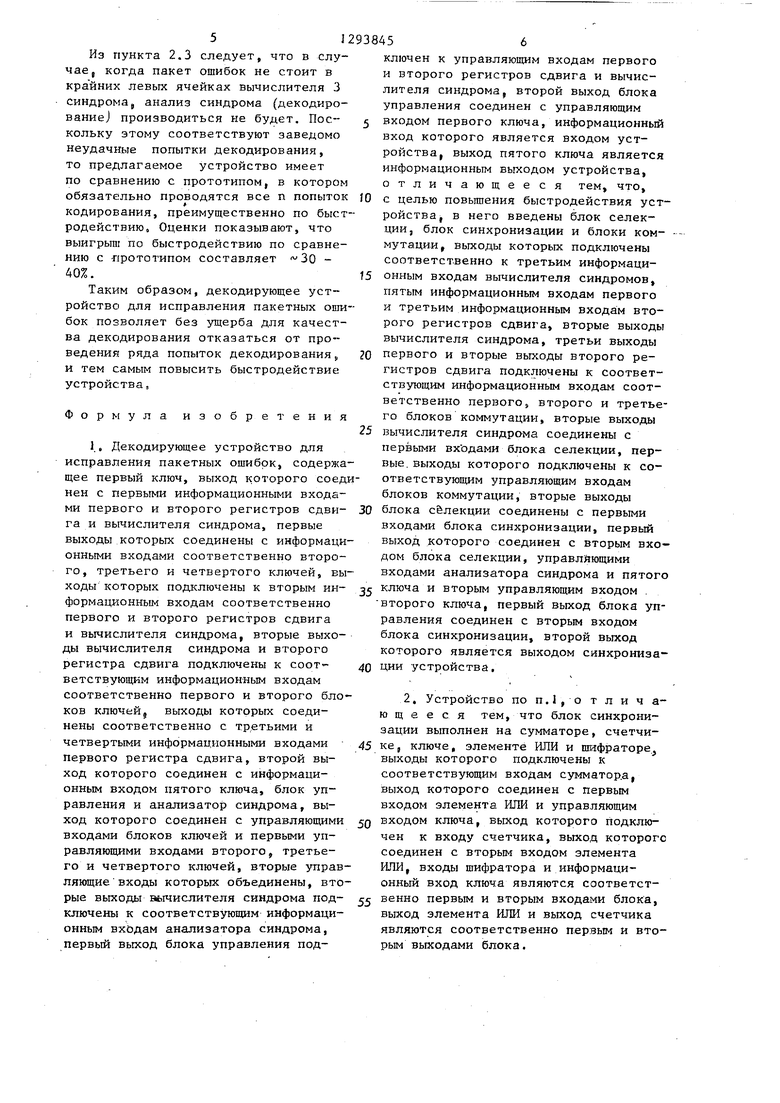

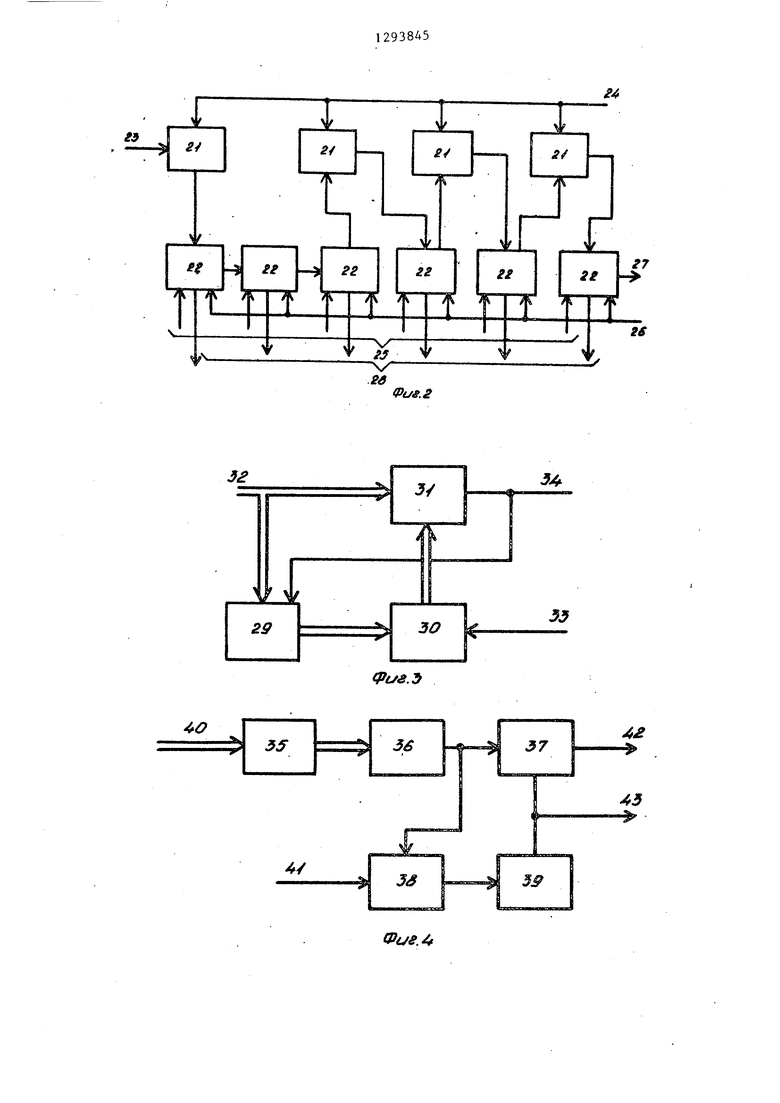

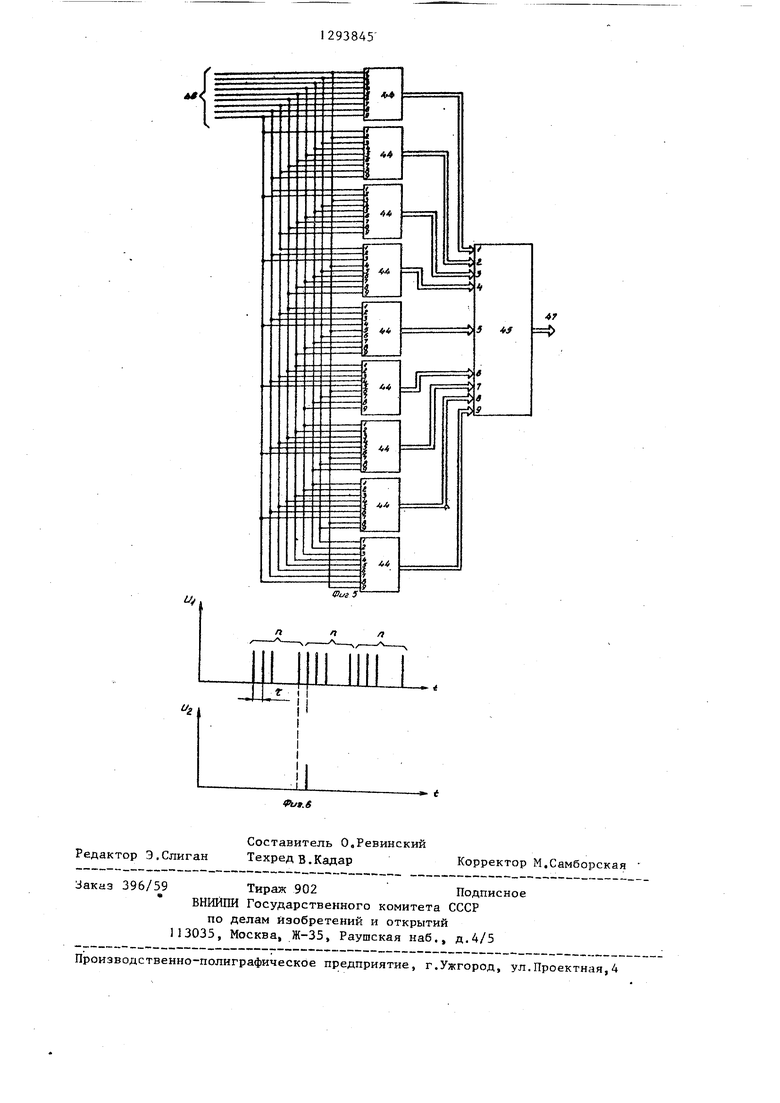

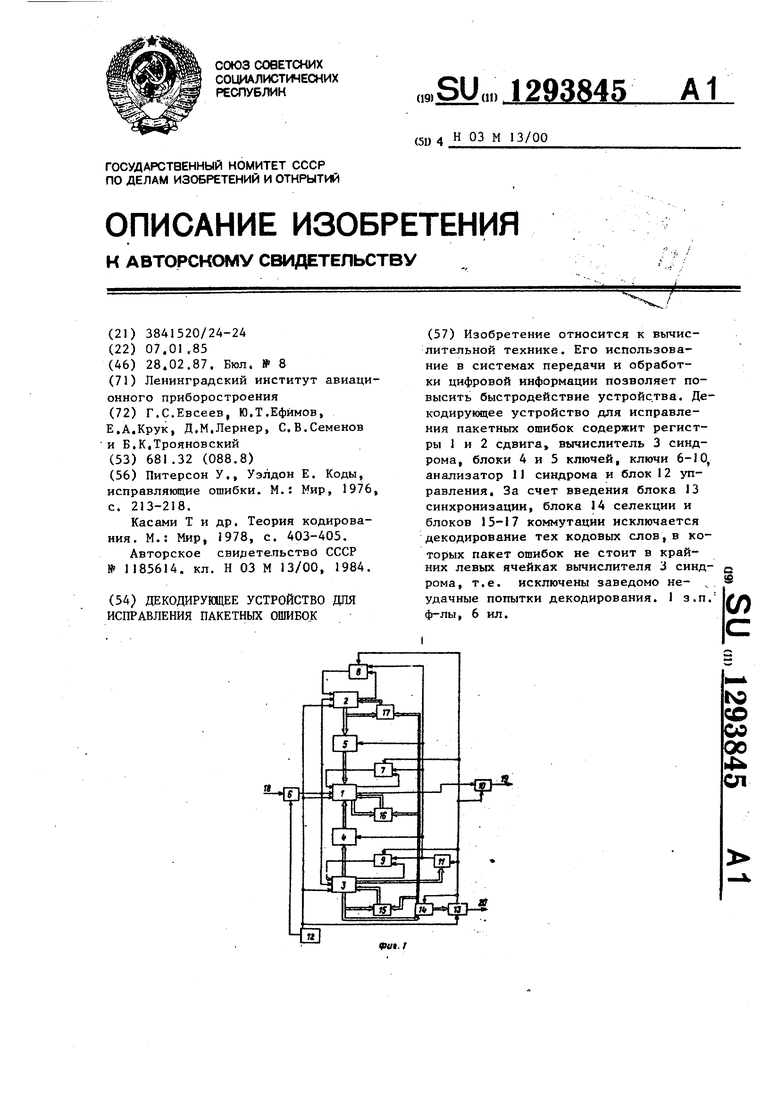

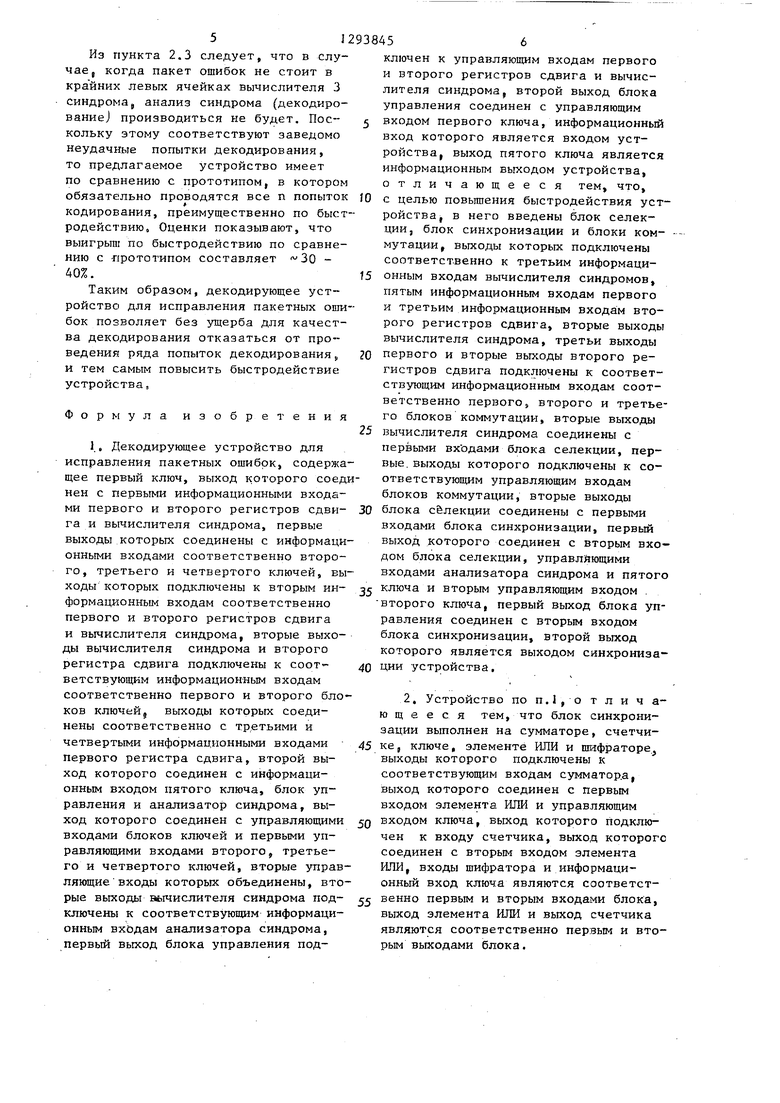

На фиг,1 приведена блок-схема декодирующего устройства для исправления пакетных ошибокj на фиг.2 - .функциональная схема конкретного выполнения вычислителя синдрома; на фиг.З - схема анализатора синдромаJ на фи1 ,4 - схема блока синхронизации, на фиг ,5 - возможная реализация функциональной схемы блока коммутации; на фиг.6 - временные диаграммы работы блока управления,

Декодирующее устройство для исправления пакетных ошибок содержит первый 1 и второй 2 регистры сдвига, вычислитель 3 синдрома, первьш 4 и второй 5 блоки ключей, первый - пятый ключи 6 - 10, анализатор П синдрома, блок 12 управления, блок 13 синхронизации, блок 14 селекции, первый 15, второй 16 и третий J7 блоки коммутации. На фиг,1 обозначены вход 18,информационный выход 9 и выход 20 синхронизации. Вычислитель 3 . синдрома представляет собой кодовый фильтр и для линейного циклического (15,9)-кода с порождающим многочленом g(x) х + х + х + X + 1

в числе, подаваемом на первые входы блока. Он может быть реализован в виде логической схемы, каждый выход у . который связан с входами х зависимостью

У

X

.X.

10

15

40

выполнен (фиг.2) на полусумматорах 21 и триггерах 22. На фиг.2 обозначены первый 23, второй 24 и третий 25 информационные входы, управляющий вход 26, первьш 27 и вторые 28 выходы. На фиг,1 вторые выходы вычислителя 3 синдрома для удобства изображения показаны в виде трех отдельных групп. Анализатор 11 синдрома (фиг.З) выполнен на блоке 29 ключей, буферном регистре 30 и блоке 31 сравнения. На .З обозначены первые 32 и 45 вторые 33 входы и выход 34, Блок 13 синхронизации (фиг.4) выполнен на шифраторе 35, сумматоре 36, элементе ИЛИ 37, ключе 38 и счетчике 39, На фиг,4 обозначены первые 40 50 и второй 41 входы, первый 42 и второй 43 выходы. Блок 14 селекции представляет собой селектор, выходы : которого соединены с информационны,-, г

Блоки 15 - 17 коммутации имеют

одинаковое выполнение, например, как на фиг.5, где показаны группы 44 ключей, буферный регистр 45, информационные входы 46 и выходы 47. Управляющие входы ключей в каждой группе 44 (не показаны объединены. Совокупность управляющих входов всех групп 44 является управляющими входами блока. Выходы всех групп 44 на входе регистра 45 объединяются на элементах ИЛИ, Блоки 16 и 17 содержат по п групп 44 ключей, где п - разрядность входного кодового слова., Блок 15 содержит г групп 44, где г - число проверочных символов кода. Блоки 15 - 17 коммутации осуществляют циклическую перестановку подаваемых на их входы слов X , У ,...х на ii п-1 разрядов. Блоки 15-17 могут быть реализованы также с помощью оперативных запоминающих устройств

(ОЗУ), Блок 12 управления представляет собой генератор тактовых импульсов, выход которого соединен с входом счетчика, выходы которого подключены к входам дешифратора.

35 Выходы последнего являются выходами блока 12 управления. Сигналы на первом и втором входах блока 12 управления приведены на фиг.6.

Декодирующее устройство для исправления пакетных ошибок работает

20

25

следующим образом.

В исходном положении открыты первый 6, второй 7, третий 8 и четвертый 9 ключи, ключ 10 и блок 4 и 5 закрыты, первый 1 и второй 2 регистры сдвига и вычислитель 3 синдрома находятся в нулевом, а регистр 30 в анализаторе 1Г синдрома - в единичном состоянии, блок 13 синхронизации находится в нулевом состоянии.

1. В режиме приема переданного слова с входа 18 п символом (п - длина используемого кода) последовательно, поступают через открытый

ми входами группы ключей, управляющие 55 ключ 6 на первые информационные вхо- входы которых объединены и являются ДЫ первого 1 и второго 2 регистров вторым входом блока 14. Селектор сдвига и вычислителя 3 синдрома, в служит для определения числа нулей которых одновременно осуществляются справа от старшей значащей цифры циклические сдвиги (ключи 7-9 откв числе, подаваемом на первые входы блока. Он может быть реализован в виде логической схемы, каждый выход у . который связан с входами х зависимостью

У

X

.X.

,-, г

Блоки 15 - 17 коммутации имеют

одинаковое выполнение, например, как на фиг.5, где показаны группы 44 ключей, буферный регистр 45, информационные входы 46 и выходы 47. Управляющие входы ключей в каждой группе 44 (не показаны объединены. Совокупность управляющих входов всех групп 44 является управляющими входами блока. Выходы всех групп 44 на входе регистра 45 объединяются на элементах ИЛИ, Блоки 16 и 17 содержат по п групп 44 ключей, где п - разрядность входного кодового слова., Блок 15 содержит г групп 44, где г - число проверочных символов кода. Блоки 15 - 17 коммутации осуществляют циклическую перестановку подаваемых на их входы слов X , У ,...х на ii п-1 разрядов. Блоки 15-17 могут быть реализованы также с помощью оперативных запоминающих устройств

(ОЗУ), Блок 12 управления представляет собой генератор тактовых импульсов, выход которого соединен с входом счетчика, выходы которого подключены к входам дешифратора.

Выходы последнего являются выходами блока 12 управления. Сигналы на первом и втором входах блока 12 управления приведены на фиг.6.

Декодирующее устройство для исправления пакетных ошибок работает

следующим образом.

В исходном положении открыты первый 6, второй 7, третий 8 и четвертый 9 ключи, ключ 10 и блок 4 и 5 закрыты, первый 1 и второй 2 регистры сдвига и вычислитель 3 синдрома находятся в нулевом, а регистр 30 в анализаторе 1Г синдрома - в единичном состоянии, блок 13 синхронизации находится в нулевом состоянии.

1. В режиме приема переданного слова с входа 18 п символом (п - длина используемого кода) последовательно, поступают через открытый

рыты). Эти сдвиги управляются сигналами, поступающими на управляющие входы регистров I и 2 сдвига и вычислителя 3 синдрома с первого выхода блока 12 управления, В результате через п тактов (п циклических сдвигов) принятое слово записывается в регистрах 1 и 2 сдвига, а синдром принятого слова - в вычислителе 3 синдрома.

2. После приема слова осуществляется режим декодирования. В этом режиме первый ключ 6 закрывается управляющим импульсом с второго выхода бло10

синдрома, Слово с выхода блока I селекции поступает на управляющие входы блоков 15 - 17 коммутации и инициирует сдвиг содержимого регистров 1 и 2 сдвига и вычислителя 3 синдрома на число позиций, равное числу нулей, находящихся справа от старшего ненулевого элемента в синдроме.

В результате операций, проведенных в пунктах 2.1 и 2.2, в регистре 30 анализатора 11 синдрома будет записан синдром, являющийся минимальным арифметическим числом среди чисел, соответствующих построенным ранее синдрока 12 управления, В режиме декодирова- мам, а в регистре 1 сдвига будет зания осуществляются следующие операции.

2.1,Символы синдрома с вторых выходов вычислителя 3 синдрома параллельно поступают на информационные входы анализатора J1 синдрома и сравниваются в блоке 3 сравнения как двоичное число с числом, записанным

в регистре 30. Б случае, если число, поступающее с вторых,выходов вычислителя 3 синдрома на блок 31 сравнения строго меньше числа,- поступающего с выхода регистра 30, на выходе блока 31 сравнения появляется импульс, который одновременно открывает ключ 29 и выдается с выхода анализатора 11 синдрома. При открытом ключе 29 происходит в параллельном коде перепись содержимого вычислителя 3 синдрома в регистр 3Q.

2.2.Импульс с выхода анализатора 11 синдрома открывает блоки 4 и 5 ключей, закрывает ключи 7 - 9 и обнуляет содержимое второго регистра 2

сдвига. При закрытых ключах 7-9 це- 40 регистре сдвига будет записан депи обратной связи регистров 1 и 2 сдвига и вычислителя 3 синдрома разрываются и содержимое вычислителя 3 синдрома подается на входы г (г - число проверочных символов кода) левых разрядов первого регистра 1 сдвига, где складывается по модулю два с содержимым второго регистра 2 сдвига.

2,3, Символы синдрома с выходов вычислителя 3 синдрома параллельно поступают на информационный вход блока 14 селекции, в котором производится анализ поступающего синдрома. В результате этого анализа на выходе блока 14 появляется слово, содержащее ровно один нулевой символ, соответствующий числу -нулей, стоящих справа от старщего ненулевого разряда

синдрома, Слово с выхода блока I селекции поступает на управляющие входы блоков 15 - 17 коммутации и инициирует сдвиг содержимого регистров 1 и 2 сдвига и вычислителя 3 синдрома на число позиций, равное числу нулей, находящихся справа от старшего ненулевого элемента в синдроме.

В результате операций, проведенных в пунктах 2.1 и 2.2, в регистре 30 анализатора 11 синдрома будет записан синдром, являющийся минимальным арифметическим числом среди чисел, соответствующих построенным ранее синдро

писан соответствующий этому синдрому вариант декодированного слова.

Величина сдвига в п-й форме (в системе счисления по модулю п) поступает с вторых выходов блока 14 селекции на входы блока 13 синхронизации, где преобразуется в двоичную форму (в щифраторе 35) и складывается с содержимым сумматора 36. 2,4, С первого выхода блока 12 управления на управляющие входы первого 1 и второго 2 регистров сдвига и вычислителя 3 синдрома поступает импульс, по которому производится

циклический сдвиг содержимого первого I и второго 2 регистров сдвига и вычислителя 3 синдрома. Затем повторяются операции по пунктам 2.J-2.3. Циклические сдвиги производятся до тех

пор, пока с выхода сумматора 36 не появится импульс, соответствующий числу п, записанному в сумматоре (импульс переполнения).

В результате этапа 2 в первом

кодированный вариант принятого слова,

3, По окончании декодирования начинается этап вывода декодированно45 го слова. Импульсом с первого выхода блока 13 синхронизации ключи 7 - 9 закрываютсяJ а ключ 10 открывается. За п тактов содержимое первого регистра 1 сдвига (декодированное

50 слово) выдается в последовательном коде через открытый ключ 10 на выход 19 устройства. При этом соде.ржимое первого 1 и второго 2 регистров сдвига и вычислителя 3 синдрома обнуля-,

J5 ется. После выдачи результата декодирования импульсы .с первого выхода блока 13 синхронизации устанавливают все ключи и ячейки памяти устройства в исходное положение.

Из пункта 2.3 следует, что в случае, когда пакет ошибок не стоит в крайних левых ячейках вычислителя 3 синдрома, анализ синдрома (декодирование J производиться не будет. Поскольку этому соответствуют заведомо неудачные попытки декодирования, то предлагаемое устройство имеет по сравнению с прототипом, в котором обязательно проводятся все п попыток кодирования, преимущественно по быстродействию. Оценки показывают, что выигрьга по быстродействию по сравнению с прототипом составляет (ЗО - 40%.

Таким образом, декодирующее устройство для исправления пакетных ошибок позволяет без ущерба для качества декодирования отказаться от проведения ряда попыток декодирования и тем самым повысить быстродействие устройства,

Формула изобретения

ключен к управляющим входам первого и второго регистров сдвига и вычислителя синдрома, второй выход блока управления соединен с управляющим

5 входом первого ключа, информационный вход которого является входом устройства, выход пятого ключа является информационным выходом устройства, отличающееся тем, что,

Ш с целью повьштения быстродействия устройства в него введены блок селекции, блок синхронизации и блоки ком- - мутации, выходы которых подключены соответственно к третьим информаци15 онным входам вычислителя синдромов, пятым информационным входам первого и третьим информационным входа:м второго регистров сдвига, вторые выходы вычислителя синдрома, третьи выходы

20 первого и вторые выходы второго регистров сдвига подключены к соответствующим информационным входам соответственно первогоS второго и третьего блоков коммутации, вторые выходы

25 вычислителя синдрома соединены с

первыми вхЪдами блока селекции, пер- Bbie. которого подключены к соответствующим управляющим входам блоков коммутации, вторые выходы

второго регистров сдви- 30 блока селекции соединены с первыми

входами блока синхронизации, первый выход которого соединен с вторым входом блока селекции, управляющими входами анализатора синдрома и пятого

2 ключа и вторым управляющим входом . второго ключа, первый выход блока управления соединен с вторым входом блока синхронизации, второй выход которого является выходом синхрониза40 ции устройства.

1., Декодирующее устройство для исправления пакетных ошибок, содержащее первый ключ, выход которого соединен с первыми информационными входами первого и

га и вычислителя синдрома, первые выходы которых соединены с информационными входами соответственно второго, третьего и четвертого ключей, выходы которых подключены к вторым информационным входам соответственно первого и второго регистров сдвига и вычислителя синдрома, вторые выходы вычислителя синдрома и второго регистра сдвига подключены к соответствующим информационным входам соответственно первого и второго блоков ключейJ выходы которых соединены соответственно с тр,етьими и четвертыми информационными входами первого регистра сдвига, второй выход которого соединен с информационным входом пятого ключа, блок управления и анализатор синдрома, выход которого соединен с управляющими входами блоков ключей и первыми управляющими входами второго, третьего и четвертого ключей, вторые управляющие входы которых объединены, вторые выходы вычислителя синдрома подключены к соответствующим информационным входам анализатора синдрома, первый выход блока управления под45

2, Устройство по П.1, о т л и ч а- ю щ е е с я тем, что блок синхронизации выполнен на сумматоре, счетчике, ключе, элементе ИЛИ и ппяфраторе.

выходы которого подключены к соответствующим входам сумматор.а, выход которого соединен с первым входом элемента ИЛИ и управляющим

5Q входом ключа, выход которого подключен к входу счетчика, выход которого соединен с вторым входом элемента ИЛИ, входы шифратора и информационный вход ключа являются соответст венно первьм и вторым входами блока, выход элемента ИЛИ и выход счетчика являются соответственно первым и вторым выходами блока.

45

2, Устройство по П.1, о т л и ч а- ю щ е е с я тем, что блок синхронизации выполнен на сумматоре, счетчике, ключе, элементе ИЛИ и ппяфраторе.

выходы которого подключены к соответствующим входам сумматор.а, выход которого соединен с первым входом элемента ИЛИ и управляющим

5Q входом ключа, выход которого подключен к входу счетчика, выход которого соединен с вторым входом элемента ИЛИ, входы шифратора и информационный вход ключа являются соответст венно первьм и вторым входами блока, выход элемента ИЛИ и выход счетчика являются соответственно первым и вторым выходами блока.

9

г/

-iL

s

г/

f

f

f

f

ff

гг

I

ff /R /fk гл Ж m Ж Ж Ж Ж

Л

1

29

40

55

22

If

21

17

26

V

v/

гл

tPuf.S

J/

S

ЭО

JJ

tpus.

3

S7

4

4S

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство для исправления пакетных ошибок | 1985 |

|

SU1300645A1 |

| Устройство для декодирования пакетных ошибок | 1984 |

|

SU1185614A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Мажоритарное декодирующее устройство | 1981 |

|

SU1005059A1 |

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU265186A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

Изобретение относится к вычис- -лительной технике. Его использование в системах передачи и обработки цифровой информации позволяет повысить быстродействие устройс.тва. Декодирующее устройство для исправления пакетных ошибок содержит регистры 1 и 2 сдвига вычислитель 3 синдрома, блоки 4 и 5 ключей, ключи 6-30, анализатор i 1 синдрома и блок 12 управления. За счет введения блока 13 синхронизации, блока 14 селекции и блоков 15-17 ко в1утации исключается декодирование тех кодовых слов,в которых пакет ошибок не стоит в крайних левых ячейках вычислителя 3 синд- Q рома, т.е. исключены заведомо неудачные попытки декодирования, ф-лы, 6 ил. 1 3 .п. (Л tc со со 00 1 ел 941%. I

/

5S

fPtjS.

у

Фиг S

-ч,

Ш11

|

Редактор Э.Слиган

Составитель О.Ревинский Техред В.Кадар

Заказ 396/59 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

t

Корректор М.Самборская

| Питерсон У., Уэлдон Е | |||

| Коды, исправлякнцие ошибки | |||

| М.: Мир, 1976, с | |||

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

| и др | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Способ включения усилителя в трансляцию | 1923 |

|

SU403A1 |

| свидетельстве} СССР Касами Т ния | |||

| М.: Мир, Авторское № 1185614 | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-28—Публикация

1985-01-07—Подача