(5) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИТЕЛЬНОСТИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство для нормализации кодов Фибоначчи | 1980 |

|

SU951291A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| ПОДСИСТЕМА ПРЕДСТАВЛЕНИЯ ИНФОРМАЦИИ О ХАРАКТЕРИСТИКАХ РАДИОТЕХНИЧЕСКОЙ СИСТЕМЫ, ЗАВИСЯЩИХ ОТ СВОЙСТВ РЕЛЬЕФА МЕСТНОСТИ | 1994 |

|

RU2087001C1 |

| Устройство для сжатия последователь-НОСТи СигНАлОВ | 1979 |

|

SU842911A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1446693A1 |

| Устройство для определения гистограммы | 1981 |

|

SU1020836A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

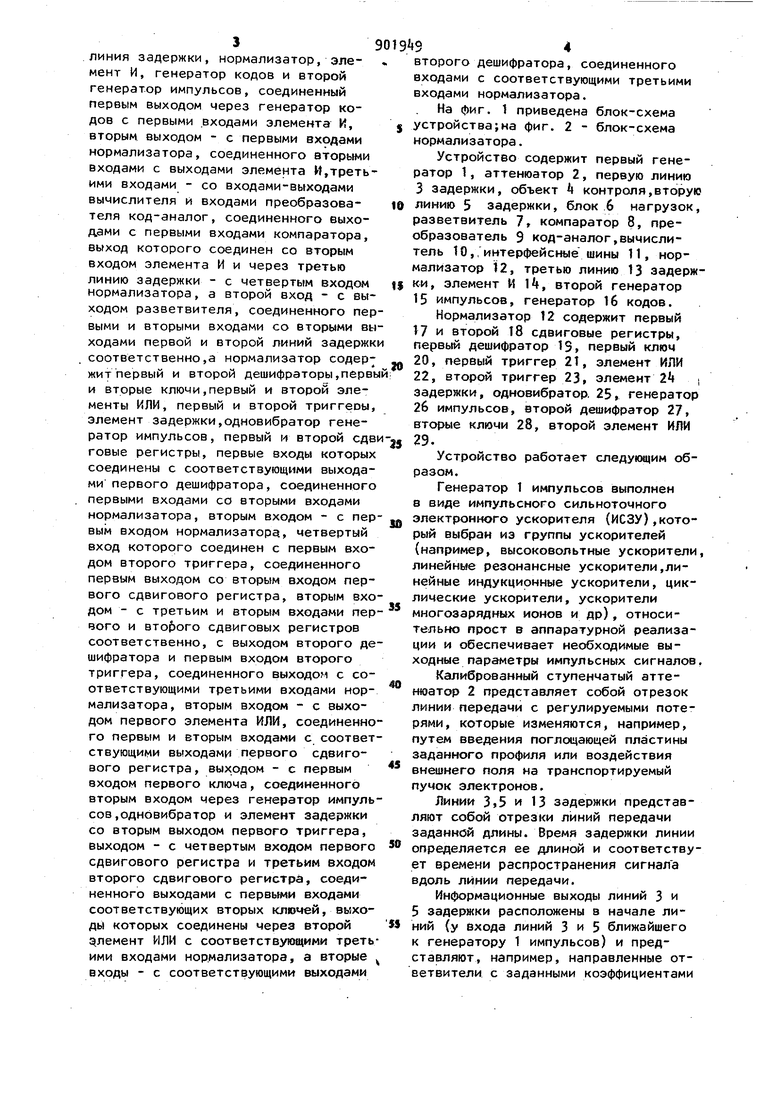

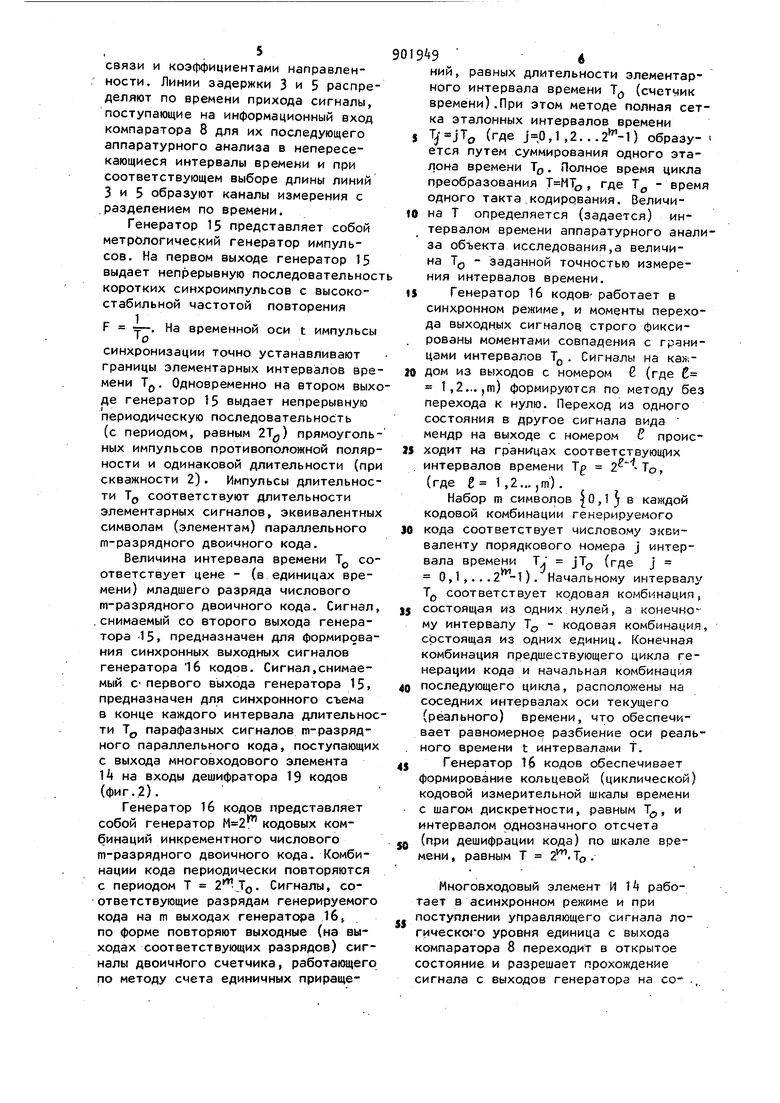

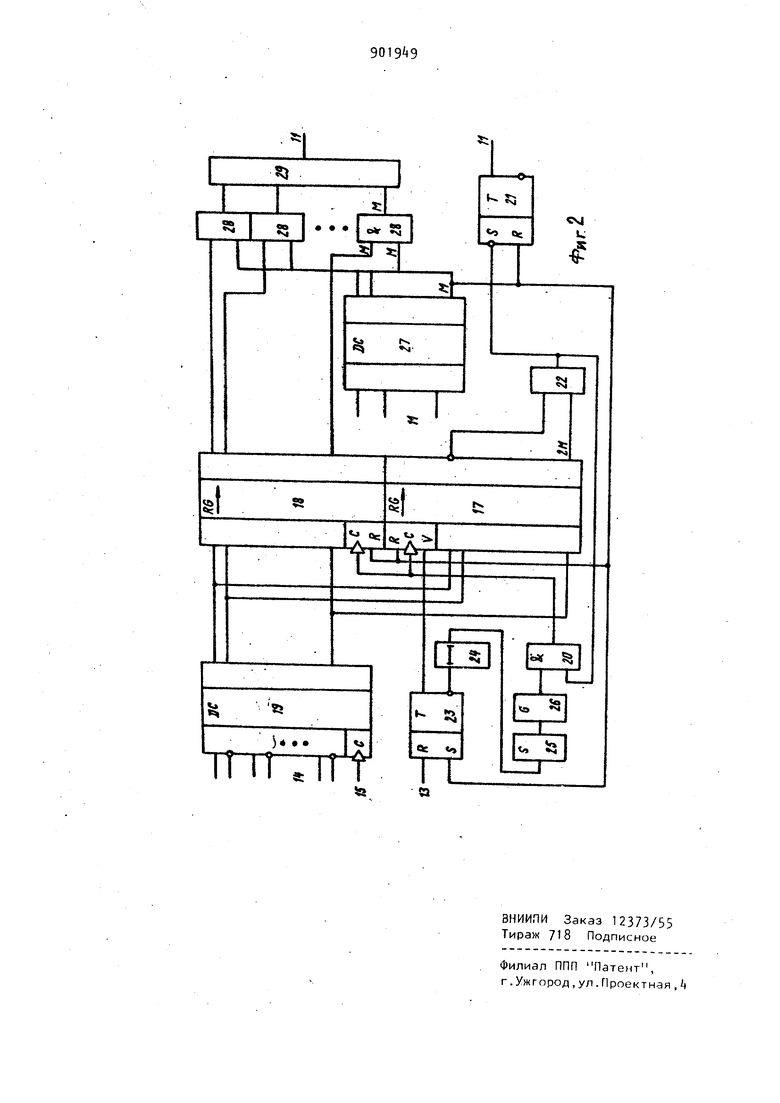

Изобретение относится к контрольно-измерительной технике и может быт использовано для контроля длительности импульсов. Известно устройство для измерения длительности импульсов, содержащее генератор импульсов, стробоскопический блок, фильтр нижних частот, нагрузку, вычислитель, блок ввода-вы вода 1 . Недостатком известного устройства является низкое быстродействие,обусловленное тем, что измерение длитель ности проводится не в реальном маештабе времени, а с использованием стробического способа. Наиболее близким к предлагаемому по технической сущности является уст ройство для измерения длительности импульсов, содержащее генератор импульсов, первую и вторую линии задержки, блок нагрузок и стробирующий блок 2. Недостаток известного устройства также состоит в низком быстродействии, обусловленном тем, что измерение длительности проводится не в реальном мг сштабе времени, а с использованием г.тробоскопического способа, требующе|-о многократного повторения измерения одного и того же импульса в различные моменты времени. Цель изобретения - повышение быстроде1Тствия устройства. Поставленная цель достигается ; тем, что в устройство для измерения длительности импульсов, содержащее вычислитель, первый генератор импульсов, соединенный выходом через аттенюатор со входом первой линии задержки, первый выход которой соединен со входом объекта контроля, соединенного выходом со входом второй линии задержки, соединенной первым выходом со входом блока нагрузок, введены разветвитель, компаратор, преобразователь код-аналог,третья линия задержки, нормализатор, элемент И, генератор кодов и второй генератор импульсов, соединенный первым выходом через генератор кодов с первыми входами элемента И, вторым выходом - с первыми входами нормализатора, соединенного вторыми входами с выходами элемента И,третьими входами - со входами-выходами вычислителя и входами преобразователя код-аналог, соединенного выходами с первыми входами компаратора, выход которого соединен со вторым входом элемента И и через третью линию задержки - с четвертым входом нормализатора, а второй вход - с выходом разветвителя, соединенного пер выми и вторыми входами со вторыми вы ходами первой и второй линий задержк соответственно,а нормализатор содержит первый и второй дешифраторы,первы и вторые ключи,первый и второй элементы ИЛИ, первый и второй триггеоы, элемент задержки,одновибратор генератор импульсов, первый и второй сда говые регистры, первые входы которых соединены с соответствующими выходами первого дешифратора, соединенного первыми входами со вторыми входами нормализатора, вторым входом - с пер вым входом нормализатору, четвертый вход которого соединен с первым входом второго триггера, соединенного первым выходом со вторым входом первого сдвигового регистра, вторым вхо дом - с третьим и вторым входами пер чого и второго сдвиговых регистров соответственно, с выходом второго де шифратора и первым входом второго триггера, соединенного выходом с соответствующими третьими входами нормализатора, вторым входом - с выходом первого элемента ИЛИ, соединенно го первым и вторым входами с соответ ствующими выходами первого сдвигового регистра, выходом - с первым входом первого ключа, соединенного вторым входом через генератор импуль сов, одновибратор и элемент задержки со вторым выходом первого триггера, выходом - с четвертым входом первого сдвигового регистра и третьим входом второго сдвигового регистра, соединенного выходами с первыми входами соответствующих вторых ключей, выходы которых соединены через второй элемент ИЛИ с соответствуюа ими треть ими входами нормализатора, а вторые входы - с соответствующими выходами S S4 второго дешифратора, соединенного входами с соответствующими третьими входами нормализатора. На фиг. 1 приведена блок-схема устройства;на фиг, 2 - блок-схема нормализатора. Устройство содержит первый генератор 1, аттенюатор 2, первую линию 3 задержки, объект контроля,вторую линию 5 задержки, блок 6 нагрузок, разветвитель 7 компаратор 8, преобразователь 9 код-аналог,вычислитель 10,, интерфейсные шины 11, нормализатор 12, третью линию 13 задержки, элемент И 1, второй генератор 15 импульсов, генератор 16 кодов. Нормализатор 12 содержит первый 17 и второй 18 сдвиговые регистры, первый дешифратор 13 первый ключ 20, первый триггер 21, элемент ИЛИ 22, второй триггер 23, элемент 2 j задержки, одновибратор. 25, генератор 2б импульсов, второй дешифратор 27, вторые ключи 28, второй элемент ИЛИ 29. Устройство работает следующим образом. Генератор 1 импульсов выполнен в виде импульсного сильноточного электронного ускорителя (ИСЗУ),который выбран из группы ускорителей (например, высоковольтные ускорители, линейные резонансные ускорители,линейные индукционные ускорители, циклические ускорители, ускорители многозарядных ионов и др), относительно прост в аппаратурной реализации и обеспечивает необходимые выходные параметры импульсных сигналов. Калиброванный ступенчатый аттенюатор 2 представляет собой отрезок линии передачи с регулируемыми потерями, которые изменяются, например, путем введения поглощающей пластины заданного профиля или воздействия внешнего поля на транспортируемый пучок электронов. Линии 3,5 и 13 задержки представляют собой отрезки линий передачи заданной длины. Время задержки линии определяется ее длиной и соответствует времени распространения сигнала вдоль линии передачи. Информационные выходы линий 3 и 5 задержки расположены в начале линий (у входа линий 3 и 5 ближайшего к генератору 1 импульсов) и представляют, например, направленные ответвители с заданными коэффициентами связи и коэффициентами направленности. Линии задержки 3 и 5 распределяют по времени прихода сигналы, поступающие на информационный вход компаратора 8 для их последующего аппаратурного анализа в непересекающиеся интервалы времени и при соответствующем выборе длины линий 3 и 5 образуют каналы измерения с .разделением по времени. Генератор 15 представляет собой метрологический генератор импульсов. На первом выходе генератор 15 выдает непрерывную последовательнос коротких синхроимпульсов с высокостабильной частотой повторения F.1-. На временной оси t импульсы о синхронизации точно устанавливают границы элементарных интервалов вре мени TQ, Одновременно на втором вых де генератор 15 выдает непрерывную периодическую последовательноЬть (с периодом, равным 2Т) прямоуголь ных импульсов противоположной поляр ности и одинаковой длительности (пр скважности 2). Импульсы длительнос ти Тд соответствуют длительности элементарных сигналов, эквивалентны символам (элементам) параллельного т-разрядного двоичного кода. Величина интервала времени Т со ответствует цене - (в единицах времени) младшего разряда числового т-разрядного двоичного кода. Сигнал .снимаемый со второго выхода генератора -15. предназначен для формирова ния синхронных выходных сигналов генератора 16 кодов. Сигнал,снимаемый Спервого выхода генератора 15, предназначен для синхронного съема в конце каждого интервала длительно ти Тр парафазных сигналов т-разрядного параллельного кода, поступающи с выхода многовходового элемента 14 на входы дешифратора 19 кодов (фиг.2). Генератор 16 кодов представляет собой генератор кодовых комбинаций инкрементного числового т-разрядного двоичного кода. Комбинации кода периодически повторяются с периодом Т , Сигналы, соответствующие разрядам генерируемого кода на m выходах генератс а 16, по форме повторяют выходные (на выходах соответствующих разрядов) сиг налы двоичного счетчика, работающего по методу счета единичных прираще 9 « НИИ, равных длительности элементарного интервала времени Т (счетчик времени).При этом методе полная сетка эталонных интервалов времени (ffls ,1,2...) образуется путем суммирования одного эталона времени Т,. Полное время цикла преобразования , где Т - время одного такта .кодирования. Величина Т определяется (задается) интервалом времени аппаратурного анализа объекта исследования,а величина TQ - заданной точностью измерения интервалов времени. Генератор 16 кодов- работает в синхронном режиме, и моменты перехода выходных сигналов строго фиксированы моментами совпадения с границами интервалов Т. Сигналы на каждом из выходов с номером (где 6 1,2...,т) формируются по методу без перехода к нулю. Переход из одного состояния в другое сигнала вида мендр на выходе с номером С происходит на гран1 цах соответствующих интервалов времени Тр , (где g 1,2.„ ,т). Набор m символов 0,1 j в каждой кодовой комбинации генерируемого кода соответствует числовому эквиваленту порядкового номера j интервала времени Т; jT (где j 0,1,...2 -1). Начальному интервалу Тд соответствует кодовая комбинация, состоящая из одних нулей, а конечному интервалу Т - кодовая комбинация, состоящая из одних единиц. Конечная комбинация предшествующего цикла генерации кода и начальная комбинация последующего цикла, расположены на соседних интервалах оси текущего (реального) времени, что обеспечивает равномерное разбиение оси реального времени t интервалами Т. Генератор 1б кодов обеспечивает формирование кольцевой (циклической) кодовой измерительной шкалы времени с шагом дискретности, равным Т,,, и интервалом однозначного отсчета (при дешифрации кода) по шкале sWl т мени, равным Т . TO Многоаходовый элемент И 1 рабоает в асинхронном режиме и при оступлении управляющего сигнала лоическо о уровня единица с выхода омпаратора 8 переходит в открытое остояние и разрешает прохождение игнала с выходов генератора на со .,.

. 90 ответствующие входы дешифратора 19 кодов нормализатора 12 памяти (фиг.2)

Двухканальный преобразователь 9 код-аналог содержит первый и второй буферные регистры кодов уровней сравнения и первый и второй преобразователи код-аналог. Входы буферных регистров являются соответствующими входами преобразователя 9, а выходы через соответствующие преобразователи код-аналог подключены к первому и-второму выходам преобразователя 9.

В соответствии с заданным режимом работы одиночный короткий импульсный сигнал с выхода генератора 1 импульсов проходит последовательно через аттенюатор 2, линию 3 задержки, объект k контроля, линию 5 задержки и поступает на вход блока 6 нагрузок.

Блок 6 нагрузок может работать в одном из следующих режимов: холостого хода, короткого замыкания,согласованном с заданным входным импедансом. Например, при анализе элементов матрицы передачи четырехполюсника блок 6 обеспечивает режим работы,при котором падающий сигнал отражается от его входа и проходит весь путь в обратном направлении.

Анализируемый сигнал при распространении как в прямом, так и в обратном направлении отйетвляется информационными выходами линий 3 и 5 и через разветвитель 7 последовательно .во времени поступает на информационный вход двухпорогового компаратора 8. Двухканальный преобразователь 9 код-аналог программно по командам от вычислителя 10 устанавливает первый (нижний) и второй (верхний) пороговые уровни, которые фиксируются до тех пор, пока в соответствии с рабочей программой не поступят команды на установку новых значений пороговы уровней. Пороговые уровни задают начало и конец отсчета длительности импульса. Компаратор 8 может быть использован в однопоррговом режиме анализа, который задается установкой только нижнего или только верхнего порогового уровня.

Режиму нижнего порогового уровня соответствует логика сравнения, задаваемая строгим неравенством;анализируемый сигнал равен или больше заданного нижнего порогового уровня.

Режиму верхнего порогового уровня соответствует логика сравнения, за.9. 8

даваемая строгим неравенством: анализируемый сигнал равен или меньше заданного верхнего порогового уровня. Режиму двухпорогового сравнения

) соответствует логика сравнения, задаваемая одновременным выполнением двух строгих неравенств: анализируемый сигнал равен или больше нижнего порогового уровня или меньше верхнеO го порогового уровня.

В каждом цикле измерения, соответствующем запуску генератора 1 импульсов, на выходе компаратора 8 вырабатывается сигнал логического уров$ ня единица, который одновременно поступает на управляющий вход многовходового элемента И 1 и на вход линии 13 задержки. Сигнал логическая единица открывает элемент 14

о и пропускает через него сигналы

параллельного т-разрядного двоичного кода, поступающие на разрядные входы элемента 1 с соответствующих выходов генератора 16 кодов. Управляемый выходным сигналом компаратора 8 элемент 14 выполняет функцию устройства считывания и обеспечивает выборку (считывание) на заданного упорядоченного набора всех возможных числовых эквивалентов параллельного т-разрядного двоичного кода тех и только тех числовых эквиваленJOB, позиции которых на элементарных интервалах Т совпадают по времени

. с единичными состояниями сигнала,поступающего с выхода компаратора 8 на управляющий вход элемента 14.Сигналы считанных комбинаций кода с разрядных выходов элемента 14 поступают

0 на парафазные входы дешифратора 19 (фиг.2) нормализатора 12.

Дешифратор 19 однозначно преобразует входные кодовые комбинации п раллельного т-разрядного кода в еыj ходные сигналы позиционного единичного унитарного) кода. В конце каждого интервала вход (С) дешифратора 19 поступает стробирующий синхросигнал с первого выхода генератора 15. Накопленные по каждому разрядному входу сигналы, соответствующие символам J0,1 m-разрядного кода, поступают на комбинационную схему дешифратора, и на соответствующем выходе вырабатывается сигнал логического уровня - единица. Сигнал 1 с выхода дешифратора 19 параллельно поступает на соответствующий порядковому номеру числового эквивалента кода разрядный вход регистра 18 сдвига и регистра 17 сдвига.

Входы регистра 18 открыты в течение всего интервала времени измерения Т. Входы регистра 17 управляются сигналом на входе (V) и открыты в течение интервала времени задержки линии 13 задержки, который соответствует началу измерения, В каждом цикле измерения линия 13 задержки обеспечивает выделение начала отсчет времени, фиксируя интервал времени задержки, достаточной для. записи в регистр 17 нескольких символов Jl унитарного кода, совпадающих по времени с начальным интервалом сигнала релейной функции, поступающей на вход линии 13 задержки с выхода компаратора 8, Зарегистрированная регистром 17 последовательность символов однозначно устанавливает начало М-разрядного;унитарного кода, зарегистрированного в одноименном цикле измерения регистром 18. В каждом цикле измерения содержимое регистров 17 и 18 однозначно фиксирует результат измерения, проведенного в реальном масштабе времени. Символ J1 в соответствующем разряде регистров 17 и 18 эквивалентен элементарному интервалу TQ в заданных единицах измерения времени, например,в пикосекундах;

Генератор 1 импульсов работает в режиме однократных или редко повто,ряющихся импульсов, которые асинхронны по отношению к моменту начала каждого,цикла генерации кода генератора 16 кодов. Это положительно отражается на точности процесса измерения, однако приводит к тому,что в каждом новом цикле измерения начало интервала измерения, отсчитываемое по переднему фронту сигнала, поступающего на информационный вход компаратора 8, сдвигается по случайному закону, вследствие чего необходимой оказывается нормализация результата измерения. В каждом последовательном цикле измерения результаты измерения, зафиксированные и регистре 18, размещаются в. разрядах регистра так, что заполненные разряды оказываются сдвинуты относительно разряда с первым порядковым номером на некоторое случайное число разрядо Это число .равно порядковому номеру младшего разряда, содержащего текущу запись символов l.e регистре 17, и

на единицу меньше количества шагов (тактов) , на которое необходимо циклически сдвинуть (нормализовать) в сторону младших разрядов информацию, записанную в регистрах 17 и 18,чтобы совместить начало цикла генерации (нулевая кодовая информация) генератора 1б с первым (начальным) разрядом регистров 17 и 18, Компенсация

начального сдвига (нормализация) производится по управляющему сигналу, поступающему с выхода линии 13 задержки на вход R-триггера 23 управления в соответствии с информацией,

записанной в регистре 17. Сигнал 1 со входа от линии 13 устанавливает в нуль триггер 23, При этом сигнал О с прямого выхода триггера 23 поступает на вход (V) регистра 17

и запрещает запись последующих данных измерения, а сигнал 1 с инверсного выхода через время Т задержки элемента 2 задержки поступает на вход одновибратора 25 и запускает

его. Для этого задержка сдвига регистра 17 на величину Т необходима для возможности осуществления полного цикла записи величины измеряемого интервала времени в регистр 18

в унитарном коде, например 000011,,,, после чего возможна нормализация за счет сдвига этого кода. Одновибратор 25 вырабатывает запускающий импульс, длительность которого соответствует

периоду цикличности регистров 17 и 18, Импульс с выхода одновибратора 25 поступает на вход тактового генератора 26 и разрешает его работу в течение длительности импульса, обес-,

печивая поиск начала интервала измерения в пределах всех разрядов регистра 17. Тактирующие импульсы с выхода генератора 2б через открытый в исходном состоянии ключ 20 поступают на

входы (с) регистров 17 и 18 кольцевого (циклического) сдвига и сдвигаХ т содержимое регистров 17 и 18 в сторону младших разрядов до тех пор, пока младший разряд регистра.17, содержащий

запись единицы, не совпадает с его первым (начальным) разрядом. Совместная работа инверсного первого выхода и прямого последнего выхода регистра 17 и логического элемента ИЛИ 22,вы- .

полняющих логическую функцию импликация, контролирует момент совпадения начала измерения интервала Т с включением первого разряда регистра 17. В момент поступления на очередном 19 такте сдвига единицы, соответствующе началу интервала измерения, в первый разряд регистра 17 на выходе элеменta ИЛИ 22 вырабатывается сигнал О, который поступает на управляющий вхо ключа 20 и останавливает сдвиг инфор мации в регистрах 17 и 18 и одновременно поступает на инверсный вход триггера 21 готовности и устанавлива ет его в состояние единица, в кото ром на прямом выходе триггера 21 вырабатывается сигнал логического уров ня единица (флаг готовности), сигнализирующий в вычислитель 10 о заве шении в очередном цикле измерения но мализации, при котором выходные разряды регистра 18 однозначно соответствуют интервалам Тр равномерного ра биения шкалы времени Т на элементарных интервалов, и номер вы одного разряда соответствует порядковому номеру j интервала Т JJ (j 1 ,2,... ,) на равномерной шкале времени Т, Измерительная информация, накопле ная в очередном цикле измерения в регистре 18, при необходимости может быть выведена из регистра 18 через ключи 28 в параллельном или последовательном коде по сигналам, заданным от вычислителя 10 через дешифр тор 27. Таким образом, введение блоков 7-16 и выполнение нормализатора в ви элементов.17-29 позволяет производит . контроль длительности импульсов в ре альном широком масштабе времени при сохранении высокой точности, что существенно повышает быстродействие устройства. Формула изобретения 1. Устройств.о для измерения длительности импульсов, содержащее вычислитель, первый генератор импульсов, соединенный выходом через аттенюатор со входом первой Л1нии задерн ки, первый выход которой соединен со входом объекта контроля,соединенного выходом со входом второй линии задержки, соединенной первым выходом со входом блока нагрузок, о тличающееся тем, что, с целью повышения быстродействия устройства, в него введены разветвитель компаратор,преобразователь код-ана.лог, третья линия задержки, норма912лизатор, элемент И, генератор кодов и второй генератор импульсов, соединенный первым выходом через генератор кодов с первыми входами элемента И, вторым выходом - с первыми выходами нормализатора, соединенного вторыми входами с выходами элемента И, третьими входами - со входамивыходами вычислителя и входами преобразователя код-аналог, соединенного выходами с первыми входами компаратора, выход которого соединен со вторым входом, элемента И и через третью линию задержки - с четвертым входом нормализатора, а второй вход с выходом разветвителя, соединенного первыми и вторыми входами со вторыми выходами первой и второй линий задержки соответственно. 2. Устройство по п.1, о т л ичающееся тем, что нормализатор содержит первый, и второй дешифраторы, первый и вторые ключи,, первый и второй элементы ИЛИ, первый и второй триггеры, элемент задержки, одновибратор, генератор, импульсов, первый и второй сдвиговые регистры, первые входы которых соединены с соответствующими выходами первого дешифратора, соединенного первыми входами со вторыми входами нормализатора, вторым входом - с первым входом нормализатора, четвертый вход которого соединен с первым входом второго триггера, соединенного первым выходом со вторым входсЗм первого сдвигового регистра, вторым входом - с третьим и вторым входами первого и второго сдвиговых регистров соответственно, с выходом второго дешифратора и первым входом второго триггера, соединенного выходом с соответствующими третьими входами нормализатора, вторым входом с выходом первого элемента ИЛИ, соединенного первым и вторым входами с соответствующими выходами первого сдвигового регистра, выходом - с первым входом первого ключа, соединенного вторым входом через генератор импульсов, одновибратор и элемент задержки со вторым выходом первого триггера, выходом - с четвертым входом первого сдвигового регистра и третьим входом второго сдвигового регистра, соединенного выходами с первыми входами соответствующих вторых ключей, выходы которых соединены через второй элемент ИЛИ с соответ13

ствующими третьими входами нормализатора, а вторые входы с соответствующими выходами второго дешифратора, соединенного входами с соответствующими третьими входами нормализатора.

Источники информации, принятые во внимание при экспертизе

}k

I 2. Экспресс-информация. Серия Контрольно-измерительная техника, №. 25, 1976, с. 25-29, рис. 3 (прототип) .

Авторы

Даты

1982-01-30—Публикация

1980-06-10—Подача