Изобретения относятся к технике связи и области кодирования цифровых сигналов и могут быть использованы в системах передачи различного назначения, в том числе и с использованием оптического волокна.

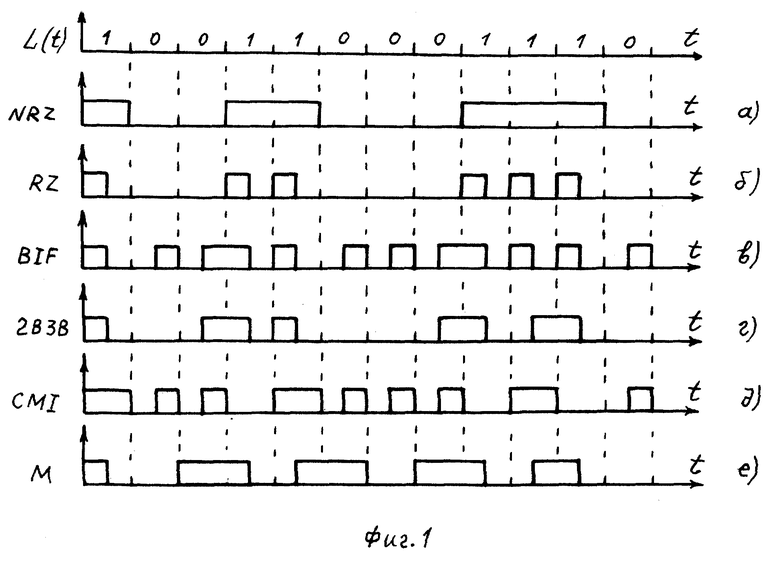

Произвольную цифровую последовательность L(t) при передаче ее по линии связи можно кодировать различными способами, как это показано на фиг. 1а-е [Цифровые и аналоговые системы передачи: Учебник для вузов /В.И. Иванов, В. Н. Гордиенко, Г. Н. Попов и др. Под ред. В.И. Иванова - М.: Радио и связь, 1995, с. 189].

На фиг. 1а показан простейший униполярный линейный код "NRZ" [non return to zero, т.е. без возвращения к нулю], в котором единичным битам цифрового сигнала при передаче соответствуют импульсы той же длительности, а нулевым битам отсутствие сигнала. В этом коде один цифровой разряд передается одним сигналом. Если же один цифровой разряд передавать двумя сигналами, то в зависимости от способа передачи единиц и нулей могут быть реализованы различные коды.

Так, если одну половину единичного символа передавать импульсом, а другую отсутствием импульса, а все нулевые биты передавать отсутствием сигнала, то получим код "RZ", т.е. с возвращением к нулю, показанный на фиг. 1б. Бифазный код "BIF" [или манчестерский] получается в том случае, если "0" передается последовательностью из паузы и импульса, а "1" - последовательностью из импульса и паузы [фиг. 1в], либо наоборот. Этот код является примером блочного кода вида: nBmB [при n = 1, m = 2], где n - означает число кодируемых цифровых разрядов, а m - число передаваемых по линии двухуровневых сигналов, соответствующих n разрядам, при этом B определяет двоичное основание системы счисления исходного кода "NRZ". Если, например, n = 2, то это означает, что кодируется сразу не один, а два разряда, а значение m тогда укажет на число разрядов, которыми заменяются исходные два разряда.

Так, при n = 2, m = 3 получаем код вида 2B3B [фиг. 1г]. Алгоритм образования его следующий: разряды "00" заменяются на 001, "01" на 010, "10" на 100, "11" на 011, что обеспечивает некоторое снижение скорости передачи в линии по сравнению с 1B2B - кодами.

Известным является также код CMI [complemented mark inversion, т.е. с полной инверсией знака] , приведенный на фиг. 1д. В этом коде для передачи единицы поочередно используются блоки "11" и "00", нули же передаются сочетанием "01" или "10".

В коде Миллера [фиг. 1е], который относится к блочным кодам вида 1B2B, кодовой посылке "0" бинарного сигнала ставится в соответствие кодовое слово "11" или "00", а кодовой посылке "1" бинарного сигнала соответственно "01" или "10", причем последовательность нулей исходного бинарного сигнала передается чередованием кодовых слов "11" или "00". При других комбинациях посылок бинарного сигнала первая кодовая посылка кодового слова должна быть такой же, как и последняя предыдущего кодового слова. Следует отметить, что в ряде публикаций, указанных далее в заявке, код Миллера помимо сокращения "M" обозначается еще и как "MFM" от слов: Modified Frequency Modulation Code.

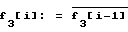

Для получения упомянутых выше кодов обычно используется сигнал тактовой частоты "C", которым тем или иным образом обрабатывают NRZ-код, как это показано на временных диаграммах фиг. 2 для случая получения манчестерского кода.

Наряду с простотой реализации перечисленных известных кодов им присущи и недостатки, перечисленные в упомянутой выше кн. В.И.Иванова [Л. 1]. Так, код "NRZ" содержит постоянную составляющую и значительную долю низкочастотных компонентов в спектре при передачах длинной последовательности единиц, что затрудняет сопряжение аппаратуры связи, расположенной вдоль линии передачи, которая, как правило, содержит реактивные элементы и трансформаторы. При передаче большой последовательности нулей возникает опасность потери синхронизации.

В коде "NRZ" невозможно также регистрировать ошибки, так как при передаче допустимы любые комбинации сигналов.

Код "RZ" практически повторяет недостатки кода "NRZ". Поэтому были разработаны еще и другие коды, в том числе и перечисленные выше.

Однако всем им присущ недостаток, связанный с тем, что когда один цифровой разряд исходного сигнала передается двумя сигналами, то относительная скорость передачи в линейном тракте оказывается в два раза выше скорости передачи символов 0, 1 цифрового сигнала, т.е. в передаваемый сигнал вносится частотная избыточность, что приводит к необходимости расширения полосы рабочих частот устройств, реализующих эти коды.

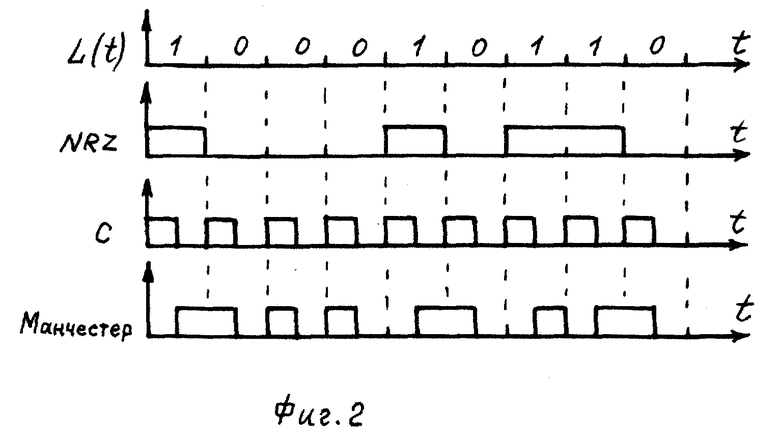

Помимо указанных выше имеются и другие коды. В частности, наряду с униполярными кодами используются также и биполярные [т.е. трехуровневые] коды, когда нулевому значению цифрового сигнала ставится в соответствие отрицательный сигнал, передаваемый по линии связи, сформированный тем или иным образом, например, как это показано на фиг. 3 для случая получения простейшего биполярного кода "NRZ" [bipolar NRZ].

Существуют и более совершенные трехуровневые коды. Так, известным является биполярный код [см. Европейский патент N 0299639, М. кл. H 03 M 5/18, H 04 L 25/49, опубл. 27.06.88] американской фирмы DAVID SYSTEMS, INC., названный его авторами, как "PMFM" [от слов: Pulsed Modified Frequency Modulation] , по аналогии с кодом Миллера "MFM", ибо он является по сути производным от кода "MFM".

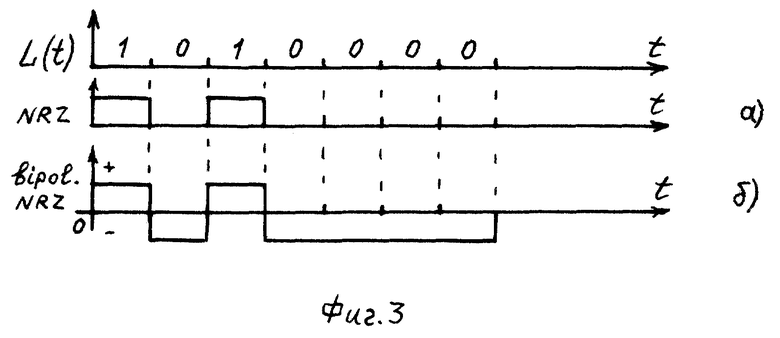

Временные диаграммы, иллюстрирующие получение кода "PMFM", приведены на фиг. 4, из которых видно, что исходный цифровой сигнал [фиг. 4a] обработкой его тактовым сигналом [фиг. 4b] преобразуют сначала в код Манчестера [фиг. 4c] , а затем из него в код Миллера "MFM" [фиг. 4d]. Дальнейшая процедуры формирования кода "PMFM" заключается в следующем. Во время положительного фронта импульсов кода "MFM" формируют новый импульс положительной полярности с длительностью, равной длительности тактового импульса [CLOCK], а во время отрицательного фронта импульса кода "MFM" формируют новый импульс отрицательной полярности с длительностью, равной длительности тактового импульса.

Основным недостатком кода "PMFM", как и всех трехуровневых кодов, является введение избыточности, приводящей к увеличению числа электрических уровней в кодированном сигнале [три вместо двух, как у однополярных кодов].

Известным является также двухфазовый код с половинчатой длиной импульсов - Half Pulse Differentially Biphase Code (HPDB), взятый за прототип, который описан в пат. Франции N 2706104, М. кл. H 03 M 5/18, опубл. 22.09.95 [автор Э.Клибанов].

Автором предложен как способ кодирования исходного цифрового сигнала, так и метод последующего преобразования полученного кода в аналоговый сигнал, способный оставаться носителем исходной цифровой информации.

Данный патент был взят за прототип, поскольку способ кодирования исходного цифрового сигнала, приводящий к реализации импульсной последовательности вполне определенного рода, описанный в патенте Франции N 2706104, имеет наибольшее число сходных признаков с заявляемым способом кодирования.

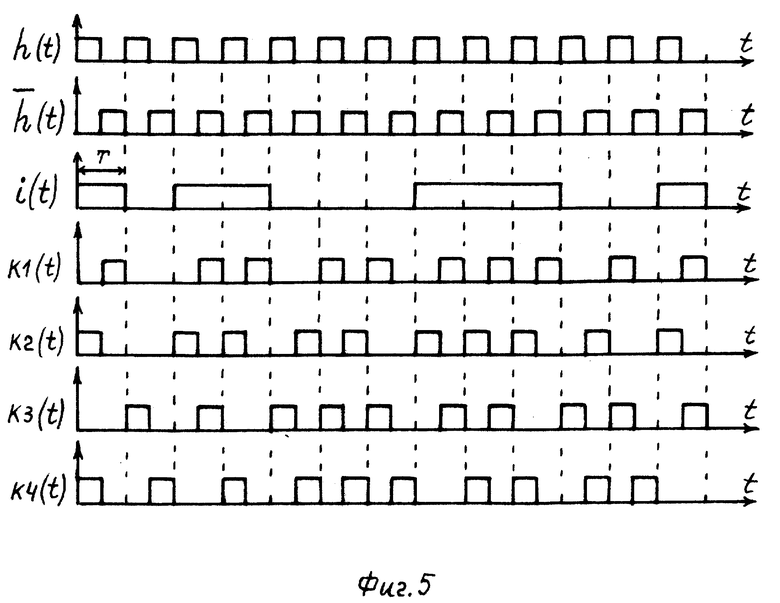

Сущность способа кодирования двоичного сигнала согласно указанному пат. Франции состоит в том, что исходный цифровой сигнал i(t) кодируется двухфазовым кодом K(t) с постоянной длительностью импульсов T/2, равной длительности одного импульса тактовой последовательности h(t) или  (t), как это показано на фиг. 5. При этом через "T" обозначена длительность одного бита исходной цифровой последовательности i(t).

(t), как это показано на фиг. 5. При этом через "T" обозначена длительность одного бита исходной цифровой последовательности i(t).

Согласно предложенному в указанном патенте способу возможны 4 [четыре] алгоритма кодирования двоичного сигнала.

Так, 1-й алгоритм получают путем представления всех символов "1" двоичного сигнала i(t) тактовым импульсом  (t) во второй фазе, а все символы "0" двоичного сигнала i(t) за исключением того, который следует непосредственно за символом "1", представлены тактовым импульсом h(t) в первой фазе.

(t) во второй фазе, а все символы "0" двоичного сигнала i(t) за исключением того, который следует непосредственно за символом "1", представлены тактовым импульсом h(t) в первой фазе.

Как видно из временных диаграмм фиг. 5 тактовые импульсные последовательности h(t) и  (t) являются инверсными по отношению друг к другу.

(t) являются инверсными по отношению друг к другу.

Полученный указанным образом кодированный сигнала обозначен на на фиг. 5 через K1(t).

Три других алгоритма реализуются аналогичным образом за счет использования того или другого тактового сигнала в соответствующей фазе при кодировании единичных и нулевых символов исходного цифрового сигнала.

Этим алгоритмам отвечают три других кодированных сигнала, обозначенных на фиг. 5 через K2(t), K3(t), K4(t). При этом для всех четырех кодированных сигналов характерным является то, что наибольшая частота следования импульсов в них получается в два раза больше, чем частота следования чередующихся символов исходного цифрового сигнала [т.е. 1 и 0], а длительность импульсов такого кодированного сигнала оказывается равной половине длительности одного бита цифрового сигнала, что естественно ухудшает частотные свойства кода по сравнению с исходным цифровым сигналом.

Дальнейшее содержание указанного патента Франции имеет отношение к последующему преобразованию полученного указанным выше образом кодированного сигнала в аналоговый с использованием симметричной лестничной функции с целью улучшения частотных свойств первичного кодированного сигнала.

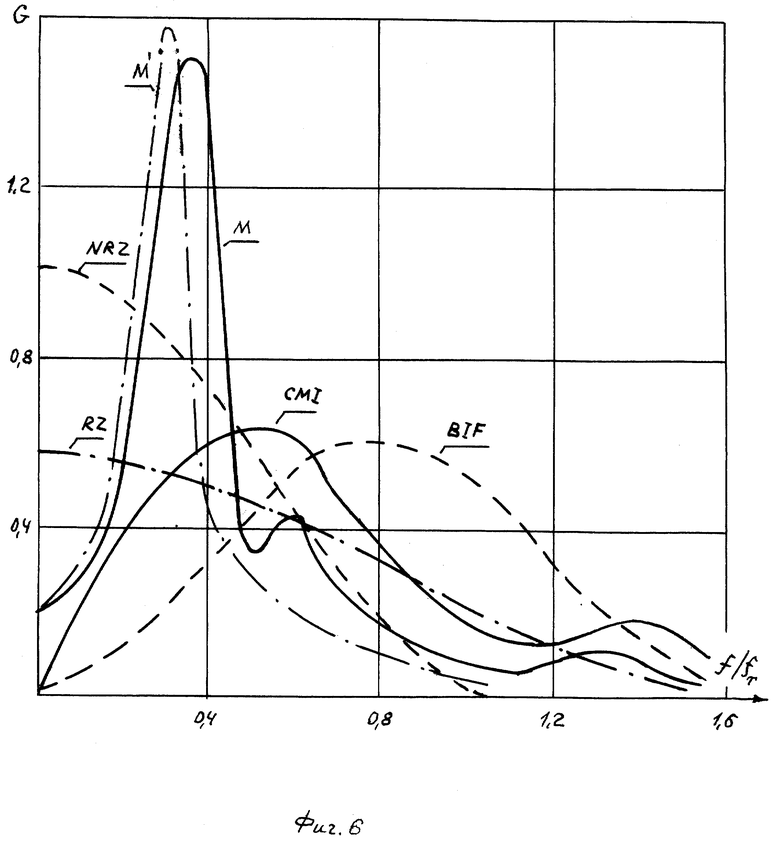

Спектры рассмотренных выше кодов, взятые из указанной ранее кн. В.И. Иванова. Цифровые и аналоговые системы передачи., и из описания патента Франции, приведены на диаграммах фиг. 6. Под индексом [M'] на этих диаграммах показан спектр кодированного сигнала, близкого по структуре к коду Миллера, но в котором наименьшая длительность импульсов равна 1,5 бита, а не 1 бит, что было характерным для кода Миллера. О том, каким образом можно получить такой кодированный сигнал, будет сказано далее.

Известен также способ представления дельта-модулированного сигнала перед его последующей какой-либо обработкой при декодировании в виде различных групп [пачек] однотипных символов: единичных, нулевых, чередующихся ["0" и "1"], который описан в заявке на изобретение N 94040884/09, решение о выдаче патента от 29.09.97 [авторы Андреев В.А., Луценко А.П.].

Согласно способу, описанному в указанной заявке, принимаемый дельта-модулированный сигнал предварительно записывают [т.е. запоминают], а затем соответствующим образом обрабатывают.

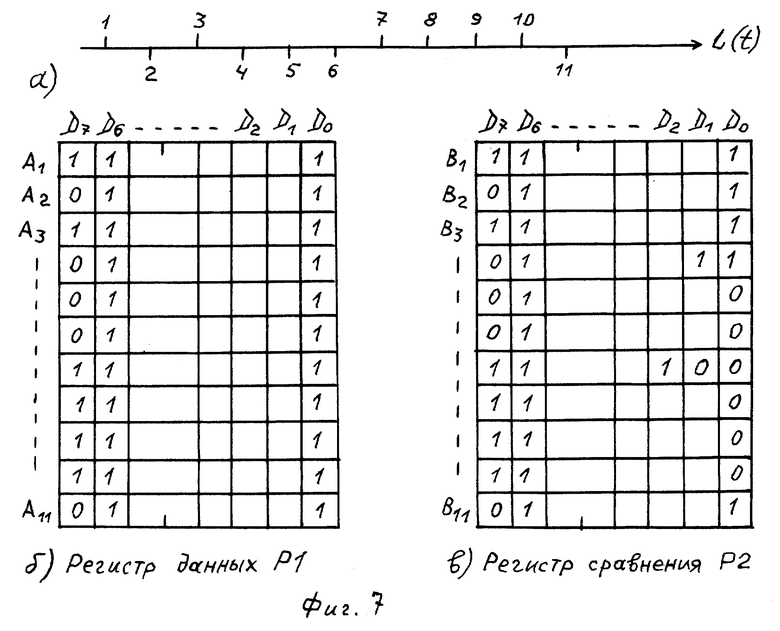

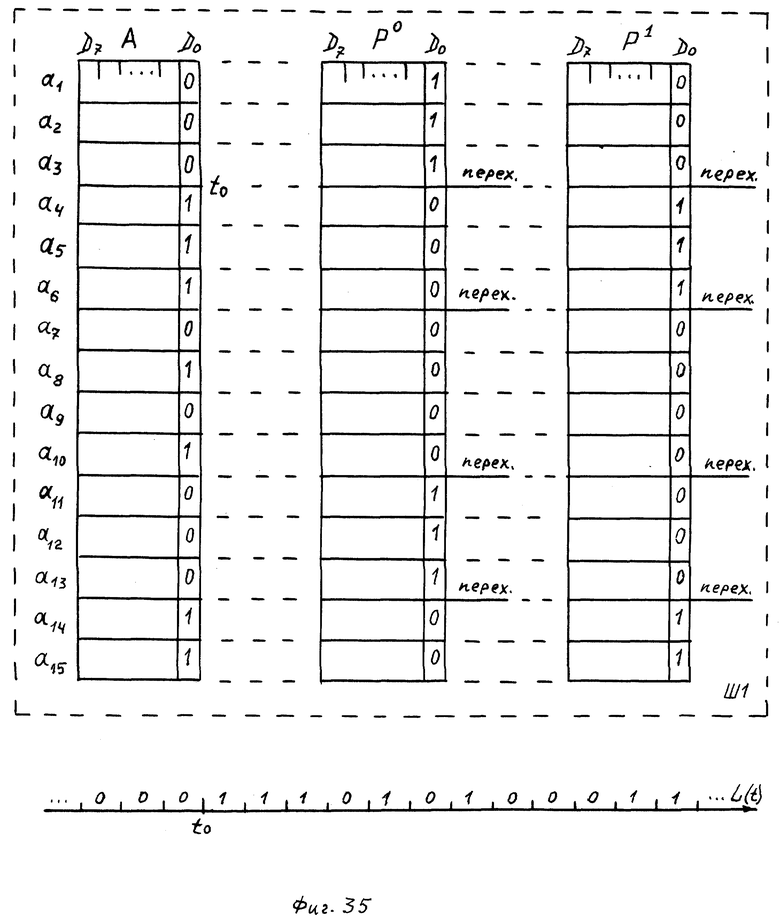

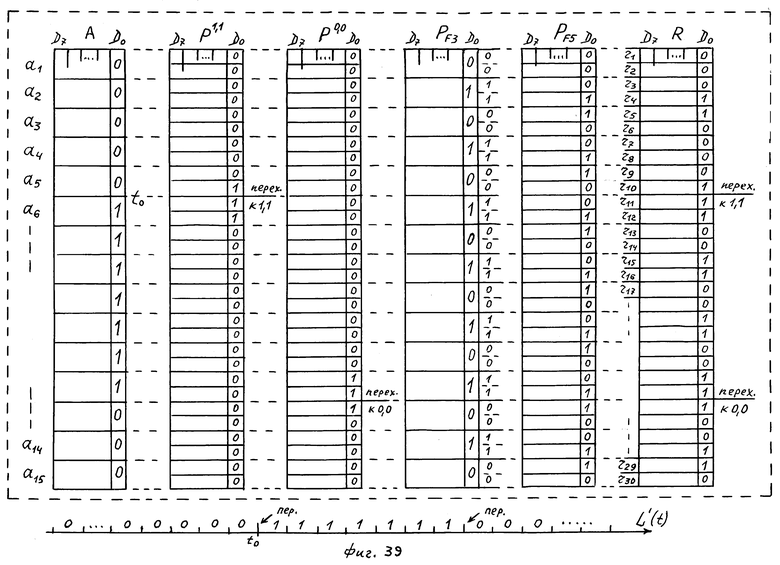

Сущность способа поясняет показ заполнения ячеек памяти регистров данных P1 [фиг. 7б] и сравнения P2 [фиг. 7в] для случая произвольно взятой цифровой последовательности L(t), приведенной на фиг. 7а.

При этом в старшем бите D7 регистра данных P1, являющимся знаковым битом, в ячейках памяти AN записывают лог. 1 тогда, когда в исходной цифровой импульсной последовательности L(t) дельта-сигнала имеют место положительные импульсы и записывают нули при наличии в дельта-сигнале отрицательных импульсов.

В младшем бите D0 и бите D6 ячеек памяти регистра P1 записывают лог. 1 при поступлении каждого очередного импульса дельта-сигнала вне зависимости от го полярности. Затем данные регистра P1 обрабатывают путем сравнения содержимого знакового бита D7 для двух соседних ячеек AN и AN+1, в результате чего в принятом дельта-сигнале выделяют пачки однотипных импульсов, либо положительных, либо отрицательных, причем записывают число импульсов в каждой пачке в той ячейке памяти регистра сравнения P2, с которой начинается эта ячейка [фиг. 7в].

В случае рассматриваемого взятого в качестве примера дельта-сигнала [фиг. 7а] имеет место пачка из трех отрицательных импульсов, что отражает запись в ячейке B4 регистра P2 в двоичном коде [т.е. "11"] и следующая за ней пачка из четырех положительных импульсов, что отражает запись в двоичном коде ["100"] в седьмой ячейке B7 регистра P2.

В дальнейшем полученный таким образом цифровой код, записанный в ячейках памяти регистра P2, в процессе его считывания из этих ячеек управляет цифроаналоговым преобразованием, в результате чего получают выходное напряжение, соответствующее двоичному числу, считываемому из ячеек памяти регистра P2. Интегрируя и фильтруя сигнал после цифроаналогового преобразования, восстанавливают аналоговый сигнал.

Как видно из изложенного, в известном решении прием выделения групп [пачек] однотипных импульсов применен к кодированному цифровому сигналу, каковым является дельта-сигнал, при осуществлении его декодирования.

Рассмотрение известных способов кодирования, в том числе и способа, взятого за прототип, показывает, что для устранения многочисленных недостатков, присущих простейшему коду "NRZ", приходится при его перекодировании использовать коды, несущие в себе избыточность, которая может быть двух видов.

1. Скорость передачи сигналов по линии связи выбирается равной скорости передачи исходной цифровой последовательности, однако при этом вводятся дополнительные электрические уровни сигналов [так называемые трехуровневые или многоуровневые коды].

2. При неизменном числе уровней электрических сигналов скорость передачи самих сигналов по линии связи делается больше, чем скорость передачи исходной цифровой последовательности. [Б. В. Шевкопляс. Микропроцессорные структуры, Инженерные решения, М., Радио и связь, 1986, стр. 94-95]. Поэтому, несмотря на свои достоинства по сравнению с простейшим кодом "NRZ" [отсутствие накопления постоянной составляющей и длительных пауз, возможность регулярной синхронизации и др.], перечисленные известные униполярные коды имеют и недостатки:

во-первых, необходимость увеличения скорости передачи сигналов по линии связи по сравнению с исходной цифровой последовательностью, что ведет к расширению спектра и увеличению рабочей полосы частот;

во-вторых, в них затруднено обнаружение и исправление ошибок, возможных при передаче кода, поскольку корреляционные связи в известных кодах распространяются по сути на два соседних импульса кода, и следовательно, восстановить кодированный сигнал при пропадании двух и более идущих подряд импульсов кода без сравнения с исходным сигналом практически невозможно.

Задачей предлагаемого способа является получение более высокого качества как частотных, так и временных характеристик кодированного сигнала.

Решение данной задачи изобретения достигается тем, что в способе кодирования цифровых сигналов, основанном на обработке исходного цифрового сигнала сигналом тактовой частоты, отличием являются то, что предварительно задерживают исходный цифровой сигнал, после чего путем сравнения между собой исходного и задержанного цифровых сигналов производят обнаружение в цифровом сигнале пачек единичных, нулевых и чередующихся между собой единичных и нулевых символов, преобразуют эти пачки символом в трехуровневый импульсный сигнал, состоящий из положительных, отрицательных и нулевых значений напряжения с длительностями этих импульсов, равными соответственно длительностям пачек единичных, нулевых и чередующихся между собой символов, формируют четыре тактовые импульсные последовательности, имеющие частоту следования импульсов, равную частоте следования чередующихся символов исходного цифрового сигнала, а длительность импульсов и пауз, равные длительности одного символа исходного цифрового сигнала, при этом сдвинутые во времени друг относительно друга на интервалы, кратные половине длительности одного символа исходного цифрового сигнала, после чего обрабатывают этими тактовыми последовательностями трехуровневый импульсный сигнал, причем в местах переходов от одних пачек к другим формируют импульсы или паузы, сдвинутые в ту или другую сторону от границы перехода, с длительностями, превышающими длительность одного символа исходного цифрового сигнала и кратными числу половин длительности одного символа, начало которых совпадает с началом той или иной тактовой последовательности, при наличии в обрабатываемом сигнале двух переходов, следующих подряд с интервалом, равным длительности одного символа, в местах этих переходов формируют импульс с длительностью, превышающей длительность импульсов других переходов и кратной числу половин длительности одного символа, начало которого совпадает с началом какой-либо тактовой последовательности, затем дополнительно задерживают сформированные импульсы на время, равное максимально возможной длительности импульсов переходов, анализируют длительность временных интервалов между импульсами переходов и, если длительность этих интервалов не превышает максимально возможной длительности импульсов переходов, то в этих интервалах формируют импульсы длительностью, равной одному биту, причем если после импульсов переходов следуют пачки единичных символов, то указанный импульс длительностью один бит формируют в те моменты времени, когда совпадают положительные значения напряжения трехуровневого сигнала с импульсами первой тактовой последовательности, если после импульсов переходов следуют пачки чередующихся между собой единичных и нулевых символов, то указанный импульс длительностью один бит формируют в те моменты времени, когда совпадают нулевые значения напряжения трехуровневого сигнала с импульсами второй тактовой последовательности, инверсной по отношению к первой, а если после импульсов переходов следуют пачки нулевых символов, то формируют указанный импульс длительностью один бит в те моменты времени, когда совпадают отрицательные значения напряжения трехуровневого сигнала с импульсами третьей тактовой последовательности, сдвинутой относительно первой на интервал, равный половине длительности одного символа исходного цифрового сигнала, причем сформированные указанным образом импульсы длительностью один бит передают в линию связи только тогда, когда между ними и импульсами переходов может быть образована пауза длительностью не менее одного символа с каждой из сторон этого импульса, в случаях же наличия в цифровом сигнале пачек символов длительностью, превышающей максимально возможную длительность сформированных импульсов переходов, во временных интервалах, отвечающим эти пачкам, между импульсами переходов формируют импульсы длительностью, превышающей длительность одного символа исходного цифрового сигнала и кратной числу полубитов, отличающихся от других сформированных импульсов либо своей длительностью, либо временным положением, начало которых совпадает с началом какой-либо тактовой последовательности и количество которых определяется длительностью обрабатываемой пачки символов, причем указанные импульсы передают в линию связи только тогда, когда между ними и импульсами переходов, или между самими этими импульсами в случаях, когда их количество превышает один импульс, может быть образована пауза длительностью, не менее одного символа с каждой из сторон указанных импульсов.

При этом способ может предусматривать обработку исходного цифрового сигнала как аппаратными средствами с помощью дискретных элементов цифровой техники, так и с помощью программных средств с использованием ЭВМ, причем в случае обработки аппаратными средствами исходный цифровой сигнал перед началом обработки предварительно задерживают на один бит цифрового сигнала, а при последующих операциях обработки задерживают еще на время, равное максимально возможной длительности сформированных импульсов переходов, а в случае осуществления обработки исходного цифрового сигнала с помощью программных средств производят задержку этого цифрового сигнала сразу же на время, равное или превышающее максимально возможную длительность формируемых в процессе обработки импульсов переходов.

Благодаря тому, что преобразованный указанным образом исходный цифровой сигнал в предлагаемом способе кодирования обрабатывается сигналами тактовых импульсных последовательностей, имеющих длительность импульсов, равную длительности одного символа исходного цифрового сигнала, а не половине этой длительности, как это имеет место в известных кодах, то тем самым частотные свойства кодированного сигнала в предлагаемом способе оказываются лучше, ибо он требует для передачи меньшую полосу рабочих частот, а его спектр становится более узким, нежели в известных кодах, рассмотренных выше.

Временные характеристики предлагаемого кода также оказываются более качественными за счет того, что здесь как самим пачкам различных символов исходного цифрового сигнала [единичных, нулевых, чередующихся], так и переходам между этими пачками в кодированном сигнале отвечают различные признаки, о которых выше говорилось, а это, в свою очередь, позволяет обнаруживать и устранять отдельные ошибки, возможные при передаче кода, приходящиеся на более длительные интервалы, нежели в известных кодах.

Действительно, если в результате ошибки [из-за действия помех] будет, например, иметь место пропадание одного-двух, или даже более импульсов кода, следующих подряд, то по виду импульсов, расположенных на краях образовавшегося в коде "пустого" интервала, можно однозначно определить продолжалась ли в этом интервале начатая пачка однотипных символов, или же здесь имел место переход к пачке других символов.

Зная особенности формирования как импульсов, кодирующих переходы, так и импульсов, кодирующих различные пачки, можно восстановить картину кодированного сигнала в обоих этих случаях, причем без обращения к исходному цифровому сигналу.

Проведенное выше рассмотрение особенностей предлагаемого способа кодирования показывает, что он позволяет обойтись без введения избыточности в отношении исходного цифрового сигнала [что имеет место в известных способах кодирования] , ибо в предлагаемом способе избыточность распространяется на уже преобразованный указанным образом исходный цифровой сигнал, а не на его первоначальный вид.

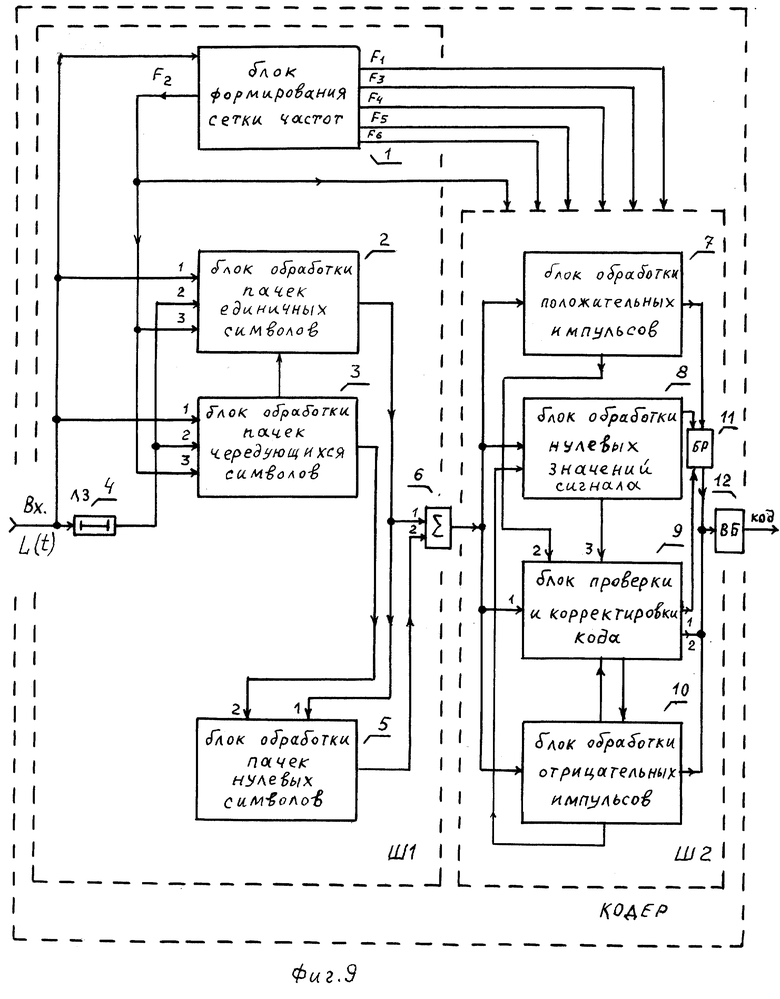

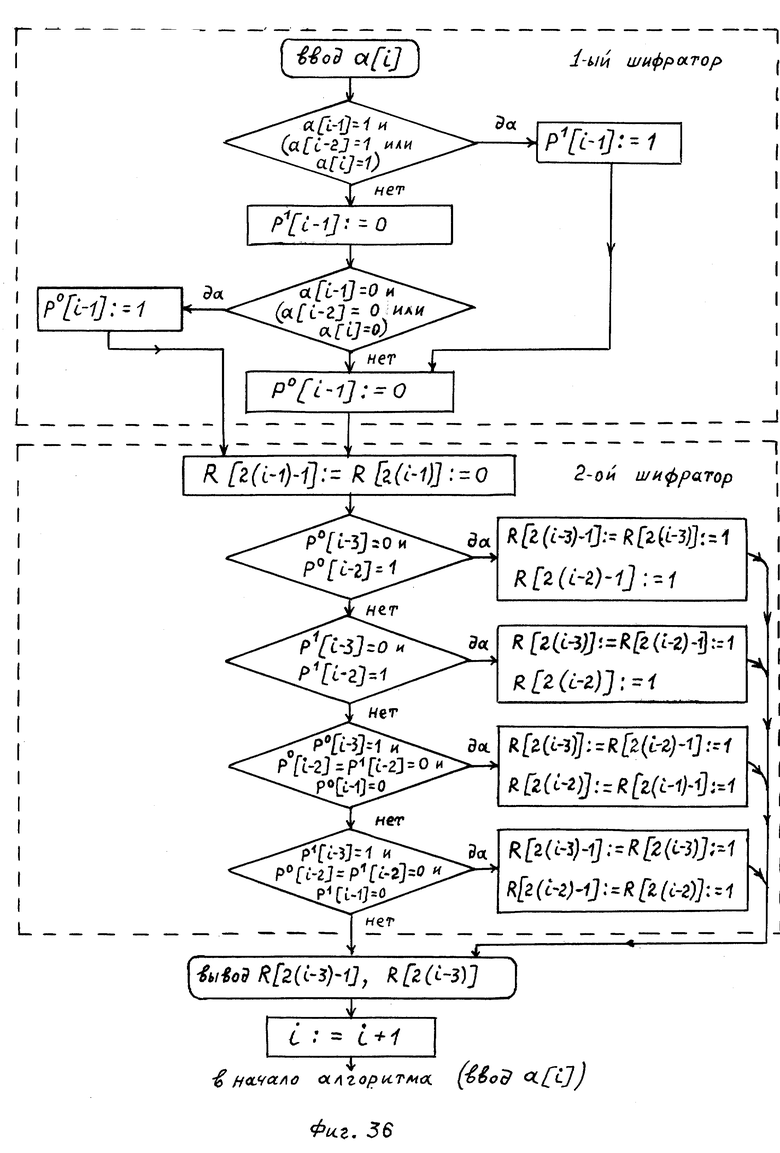

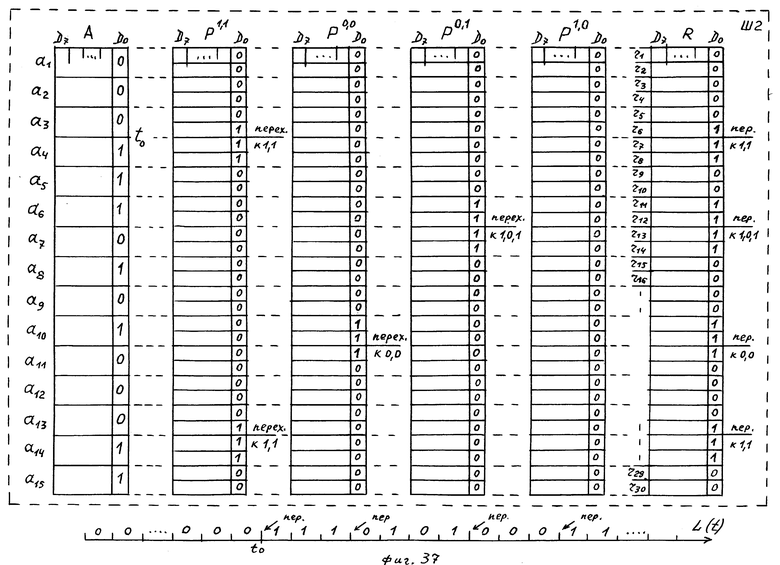

Предлагаемый способ поясняется структурной схемой [фиг. 9], в которую входят два шифратора Ш1 и Ш2. Первый шифратор Ш1 включает в себя тактовый генератор, установленный на входе блока 1 формирования сетки частот, предназначенный для получения сигналов шести тактовых последовательностей: первая и вторая из которых [F1 и F2] имеют длительности импульсов соответственно в четыре и в два раза меньше длительности одного символа цифрового сигнала и предназначены для осуществления синхронизации работы отдельных блоков, четыре другие последовательности F3...F6 имеют длительность импульсов, равную длительности одного бита, которыми и обрабатывают цифровой сигнал [они приведены на фиг. 10].

В Ш1 введены также элемент задержки в виде, например, линии задержки ЛЗ 4 с временем задержки равным 1 биту, а также блоки 2 и 3, соответственно, обработки пачек единичных и чередующихся символов и блок 5 обработки пачек нулевых символов, соединенных между собой определенным образом [о чем подробно сказано далее при рассмотрении устройства].

В Ш1 введен также сумматор 6, входы которого соединены с выходами блоков 2 и 5. Выход же сумматора соединен с входом второго шифратора Ш2, который включает в себя блоки 7 и 10 соответственно обработки положительных и отрицательных импульсов, блок 8 - обработки нулевых значений трехуровневого сигнала, блок 9 - проверки и корректировки кода [бл. П и КК].

Блоки 7, 8, 9, 10 связаны как между собой, так и с выходом блока 6, а также с блоком разрешения БР 11. Выходной блок ВБ 12 своим входом соединен с выходом блока БР 11 и выходами блоков 9 и 10 [более подробно от этом сказано при описании устройства].

Исходную цифровую последовательность L(t) подают на вход элемента линии задержки ЛЗ 4 с временем задержки, равным 1 биту входного цифрового сигнала, одновременно сигнал L(t) подают на первые входы блоков обработки пачек единичных символов [блок 2] и пачек чередующихся символов [блок 3].

Выходной сигнал ЛЗ 4 подают на вторые входы блоков 2 и 3, что позволяет провести сравнение исходного и задержанного сигналов в этих блоках и выделить пачки единичных и чередующихся символов в исходном сигнале, если они там имеются.

Входной цифровой сигнал поступает также на вход блока формирования сетки частот [блок 1] с целью синхронизации его работы в соответствии с входным сигналом, при этом сигнал тактовой частоты F2 с периодом следования импульсов, равным 1 биту, поступает на третьи входы указанных блоков 2 и 3, осуществляя синхронизацию их работы.

Выходные сигналы блоков 2 и 3 поступают на первый и второй входы блока обработки пачек нулевых символов [блок 5]. При этом при отсутствии соответствующих сигналов на входах 1 и 2 блока 5, т.е. в случае когда в цифровом сигнале нет ни пачек единиц, ни пачек чередующихся символов, на выходе блока 5 появляется сигнал, характеризующий наличие в L(t) пачек нулевых символов.

Выходные сигналы блоков 2 и 5 подают соответственно на первый и второй входы сумматора 6, на выходе которого формируется трехуровневый импульсный сигнал с длительностями импульсов, соответствующими длительностям пачек тех или иных символов в L(t).

Трехуровневый сигнал с выхода сумматора 6 подают на вход второго шифратора Ш2, который соединен с входами блоков обработки положительных импульсов [блок 7], отрицательных импульсов [блок 10], нулевых значений [блок 8] , а также с входом блока проверки и корректировки кода 9 [блок П и КК], название которого указывает на выполняемые функции этим блоком.

К соответствующим входам указанных блоков подключены также выходы блока формирования сетки частот [бл. 1], на которых формируются сигналы четырех тактовых импульсных последовательностей, имеющих длительность импульсов и пауз, равные длительности одного символа входного цифрового сигнала и сдвинутые друг относительно друга на интервалы, кратные половине длительности одного символа.

При помощи этих тактовых последовательностей осуществляют обработку трехуровневого импульсного сигнала первого шифратора, с целью формирования импульсов, кодирующих те или иные пачки символов, а также переходы между этими пачками символов исходного сигнала.

Еще один тактовый сигнал с периодом следования импульсов, равным 0,5 бита, подается с выхода блока 1 на соответствующие входы блоков, расположенных во втором шифраторе, обеспечивая синхронизацию их совместной работы.

Сформированные на выходах указанных блоков 7, 8 и на первом выходе блока 9 [блок П и КК] импульсы, представляющие собой кодированный сигнал, подают на соответствующие входы блока разрешения БР 11, выходной сигнал которого подают на вход выходного блока ВБ 12, к которому подключен также второй выход блока 9.

С выхода блока 12, согласующего выход второго шифратора с линией связи, итоговый кодированный сигнал поступает в линию передачи кода.

Устройства [кодеры], реализующие известные способы кодирования, рассмотренные выше, содержат шифратор с необходимым количеством логических элементов, связанных между собой определенным образом, с тем чтобы можно было осуществить обработку исходного цифрового сигнала сигналом тактовой частоты согласно тому или иному способу кодирования.

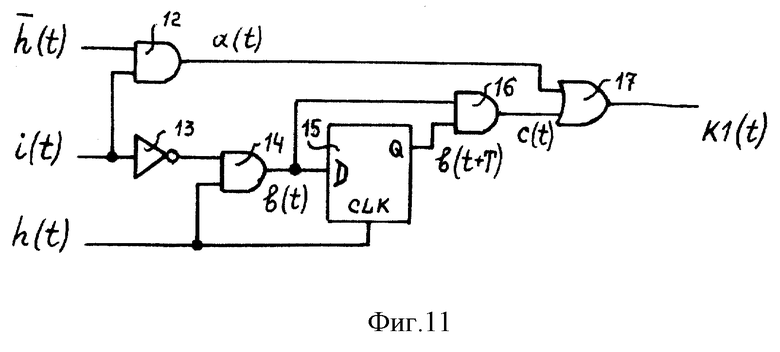

Так, например, функциональная схема кодирующего устройства, взятого за прототип [фиг. 11], реализующая алгоритм обработки исходного цифрового сигнала, рассмотренный ранее, представляет собой шифратор, который содержит схему совпадения 12, один из входов которой подсоединен к выходу источника цифрового сигнала i(t), а другой соединен с выходом тактового генератора, выдающего последовательность импульсов  (t).

(t).

Выход схемы 12 подсоединен к одному из входов схемы 17 ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход источника цифрового сигнала i(t) подключен через инвертор 13 также к одному из входов схемы совпадения 14, другой вход которой соединен с выходом тактового генератора, выдающего последовательность импульсов вида h(t), инверсную относительно  (t).

(t).

Выход схемы 14 соединен с входом D-триггера задержки 15, вход синхронизации которого подключен к выходу тактового генератора h(t). Выход Q D-триггера 15 соединен с одним из входов схемы совпадения 16, другой вход которой подключен к выходу схемы 14. Выход схемы 16 соединен с одним из входов схемы 17, другой вход которой подключен к выходу схемы 12. На выходе схемы 17 формируется кодированный сигнал вида K1(t).

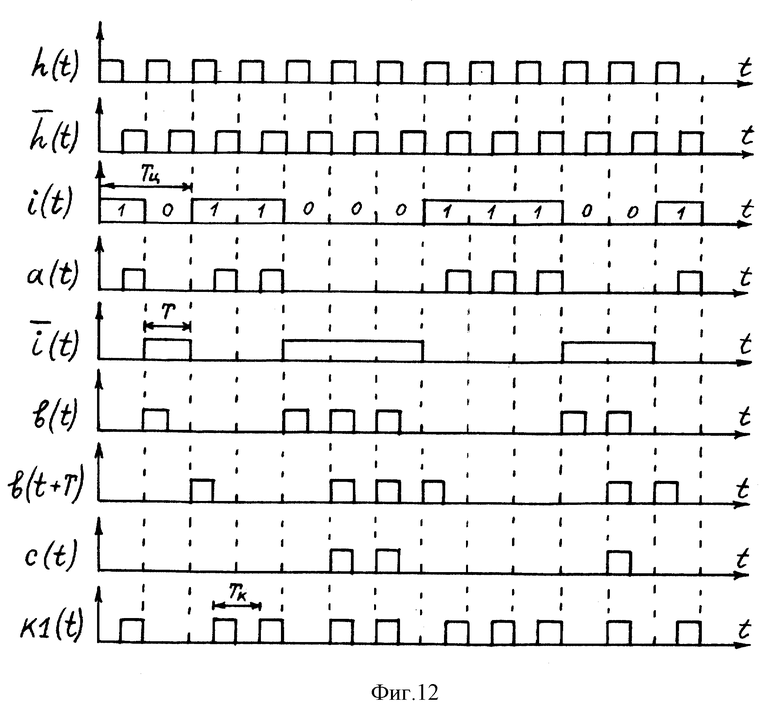

Характеризуют работу устройства временные диаграммы, приведенные на фиг. 12, не требующие особых пояснений. На них также приведены виды сигналов, имеющие место в отдельных точках схемы устройства в соответствии с обозначениями данными на фиг. 11.

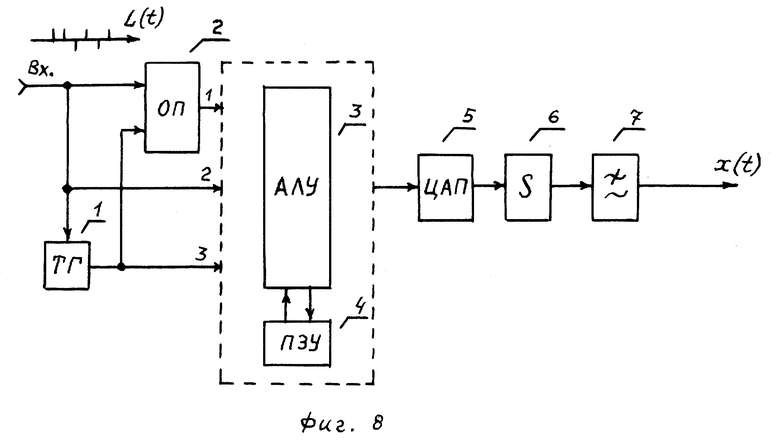

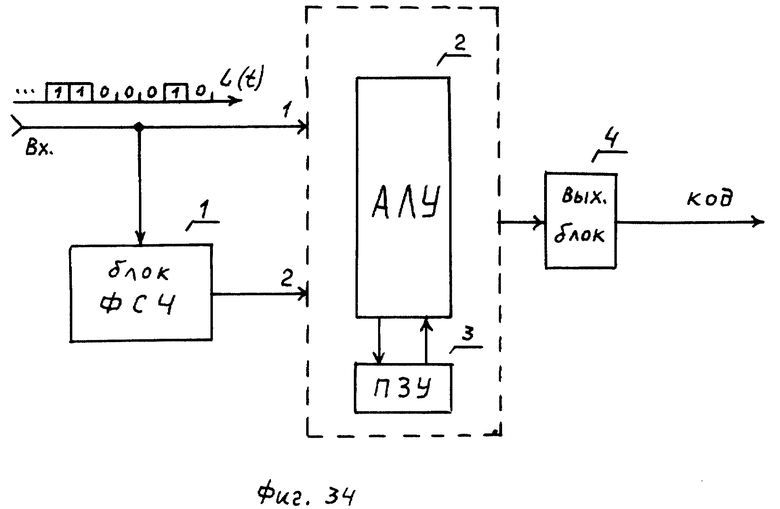

Выше был рассмотрен также способ, в котором при декодировании использован прием выделения пачек символов в цифровом сигнале. Структурная схема устройства, реализующего указанный способ восстановления исходного аналогового сигнала из цифрового дельта-сигнала, приведена на фиг. 8 и содержит определитель полярности ОП2, один из входов которого соединен со входом устройства, а другой подсоединен к выходу тактового генератора ТГ1, подключенного ко входу устройства. Выход ОП2 соединен с первым входом арифметико-логического устройства АЛУ 3, второй вход которого соединен с входом устройства, а третий вход АЛУ соединен с выходом тактового генератора ТГ1. АЛУ 3 осуществляет параллельный обмен информацией с постоянным запоминающим устройством ПЗУ 4. Совместное использование АЛУ 3 и ПЗУ 4 позволяет производить переработку и перекодирование информации, поступающей на вход устройства, с целью декодирования любых видов ДМ-сигналов при наличии в ПЗУ 4 соответствующих шин данных.

Выход АЛУ 3 соединен с входом знакопеременного цифроаналогового преобразователя ЦАП 5, выход которого соединен с входом интегратора 6, а его выход подсоединен ко входу фильтра нижних частот ФНЧ 7, выход которого является выходом устройства.

Работа устройства [фиг. 8] состоит в следующем.

Приходящие импульсы ДМ-сигнала L(t) поступают на вход тактового генератора ТГ1, на один из входов АЛУ 3, а также на один из входов определителя полярности ОП2, на другой вход которого подаются положительные импульсы с выхода ТГ1.

Таким образом выходной импульс у ОП2 появляется и поступает в АЛУ 3 лишь при наличии в ДМ-сигнале отрицательных импульсов, тогда как при наличии в ДМ-сигнале отрицательных мпульсов на выходе ОП2 будет нулевой сигнал. В знаковом бите D7 ячеек памяти регистра данных АЛУ 3 при наличии выходных импульсов ОП2 будут записываться лог. 1, в противном случае сохраняются нули.

Затем осуществляют по заданному алгоритму сравнение содержимого знакового бита [битов] для двух последовательно расположенных ячеек регистра данных, с целью обнаружения пачек однотипных импульсов в дельта-сигнале, с занесением результатов этой обработки в другой регистр [регистр сравнения], в котором таким образом будут записываться в двоичном коде числа импульсов, принадлежащие той или иной пачке. На следующем этапе обработки двоичный код подают на вход знакопеременного ЦАП 5, выходное напряжение которого, пропорциональное количеству импульсов в пачке, поступает на интегратор 6, выход которого соединен с входом фильтра нижних частот ФНЧ 7, осуществляющим фильтрацию сигнала интегратора, получая таким образом восстановленный аналоговый сигнал.

Как видно из изложенного выше, прием выделения групп [пачек] однотипных импульсов применен в известном устройстве непосредственно к кодированному сигналу, каковым является дельта-сигнал при осуществлении его декодирования.

В тоже время прием выделения пачек "однотипных" символов может быть применен и к самому исходному цифровому сигналу перед его последующим кодированием, что и имеет место в предложенном способе.

Как показывает проведенный выше анализ известных устройств по кодированию цифровых сигналов, их недостатками, обусловленными прежде всего несовершенством известных способов кодирования, являются:

во-первых, расширение полосы рабочих частот устройства в связи с введением в кодированный сигнал частотной избыточности по сравнению с исходным цифровым сигналом,

во-вторых, недостаточно высокая помехоустойчивость из-за того, что корреляционные связи в известных устройствах кодирования распространяются не более чем на один-два соседних импульса кода.

Задачей предлагаемого устройства кодирования цифровых сигналов является повышение его помехоустойчивости при одновременном снижении полосы рабочих частот в сравнении с известными устройствами.

Решение данной задачи изобретения достигается тем, что в устройство для кодирования цифровых сигналов, содержащее шифратор, вход и выход которого являются входом и выходом устройства, в который входит тактовый генератор, вход которого соединен со входом устройства, а выход подключен к соответствующему выходу шифратора, введен второй шифратор и элемент задержки, вход которого является входом устройства и подключен как и выход этого элемента задержки к соответствующим входам первого шифратора, в который введен блок формирования сетки частот, вход которого соединен с выходом тактового генератора, включенного на входе этого блока, а выходы блока формирования сетки частот подсоединены к соответствующим входам обоих шифраторов, в первый шифратор введены также блок обработки пачек единичных символов, блок обработки пачек чередующихся символов и блок обработки пачек нулевых символов, причем первый и второй входы двух первых из указанных блоков подсоединены соответственно ко входу и выходу элемента задержки, а третий их вход подсоединен к одному из выходов блока формирования сетки частот, а первый и второй входы третьего из указанных блоков обработки подсоединены к выходам блоков обработки соответственно пачек единичных и чередующихся символов, причем выход блока обработки пачек единичных символов подключен также к первому входу сумматора, ко второму входу которого подсоединен выход блока обработки пачек нулевых символов, а выход сумматора подключен ко входу второго шифратора, который содержит блок обработки положительных импульсов, блок обработки отрицательных импульсов, блок обработки нулевых значений сигнала и блок проверки и корректировки кода [блок П и КК], при этом первый вход этого блока и входы трех других указанных блоков подключены к входу второго шифратора, а второй и третий входы блока "П и КК" подсоединены к соответствующим выходам блоков обработки положительных импульсов и нулевых значений сигнала, а один из выходов блока обработки отрицательных импульсов подсоединен ко второму входу блока обработки нулевых значений сигнала, блок "П и КК" связан также шиной связи с блоком обработки отрицательных импульсов, при этом первый выход блока "П и КК" соединен с одним из входов блока разрешения, два других входа которого соединены с выходами блоков обработки положительных импульсов и нулевых значений сигнала, причем выходы блоков разрешения и обработки отрицательных импульсов, объединенные вместе со вторым выходом блока "П и КК", подключены к входу выходного блока, выход которого является выходом устройства.

Структурные и принципиальные схемы обоих шифраторов, входящих в устройство, реализующее предлагаемый способ кодирования, приведены соответственно на фиг. 9, 13, 18. Рассмотрим сначала структурные схемы первого и второго шифраторов устройства, показанные на фиг. 9.

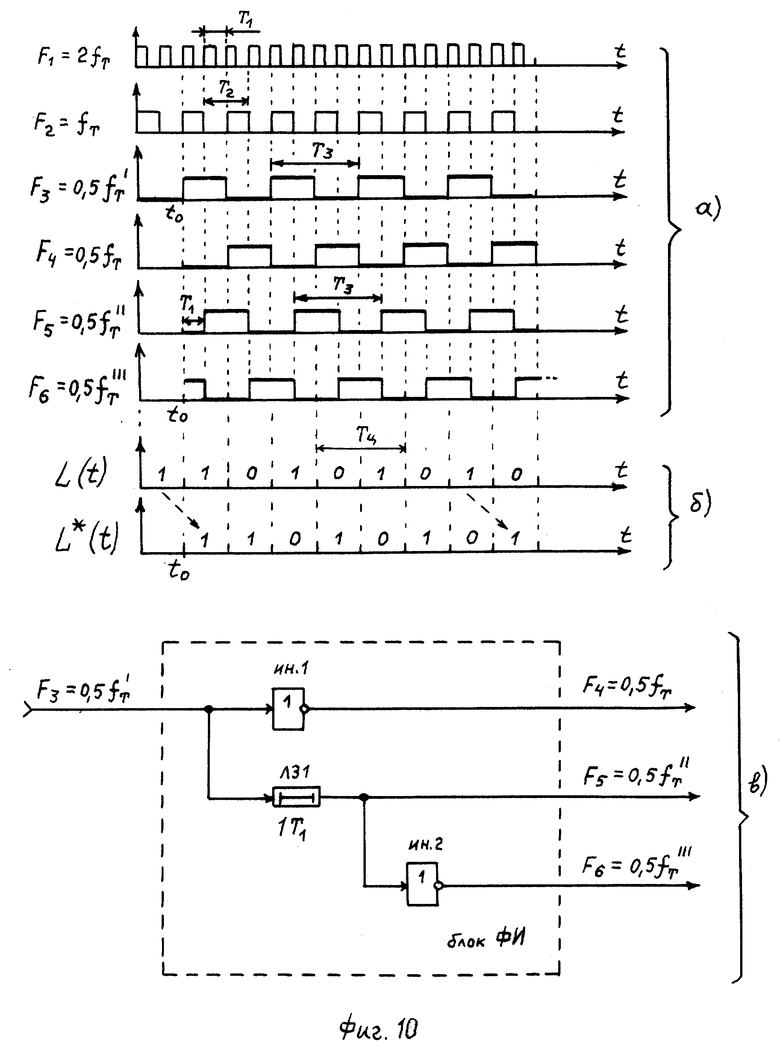

Первый шифратор Ш1 кодера содержит блок 1 формирования сетки частот, на входе которого включен тактовый генератор, предназначен для вырабатывания [т. е. получения] сигналов шести тактовых импульсных последовательностей с равными длительностями импульсов и пауз внутри каждой из них, причем первая F1 и вторая F2 тактовые последовательности имеют длительности импульсов соответственно в четыре и в два раза меньше длительности одного символа исходного цифрового сигнала, а третья F3, четвертая F4, пятая F5 и шестая F6 тактовые последовательности имеют длительность импульсов, равную длительности одного символа исходного цифрового сигнала и сдвинуты во времени относительно друг друга на интервалы, кратные 1T1 [где 1T1 - половина длительности одного символа].

Вид указанных последовательностей приведен на фиг. 10а.

При этом, как видно из рассмотрения временных диаграмм [фиг. 10а], начало первого импульса последовательности F3 совпадает с началом первого единичного символа задержанного на один бит исходного цифрового сигнала L*(t) [фиг. 10б).

Последовательность F4 является инверсной по отношению к F3, и следовательно, ее начало сдвинуто относительно начала последовательности F3 на интервал, равный 2T1.

Начало импульсов последовательности F5 сдвинуто относительно начала импульсов последовательности F3 на интервал, равный 1T1 [что соответствует половине длительности одного символа исходного цифрового сигнала].

Последовательность F6 является инверсной по отношению к F5.

Для большей наглядности рассмотрения диаграмм на фиг. 10б приведен произвольно взятый цифровой сигнал: исходный и задержанный.

При этом, если обозначить частоту следования импульсов второй тактовой последовательности F2, при помощи которой осуществляется обработка исходного цифрового сигнала L(t) в первом шифраторе Ш1, через fт [т.е. F2 = fт], то тогда частота следования импульсов первой тактовой последовательности F1, представляющей собой сигнал задающего тактового генератора ТГ синхронизированного с L(t), из которого формируются затем другие тактовые сигналы, будет равна F1 = 2fт, а частота следования импульсов третьей, четвертой, пятой и шестой импульсных последовательностей будет одинаковой и равной: F3 = F4 = F5 = F6 = 0,5fт.

Для того чтобы различать эти последовательности при указании их через fт, они обозначены соответственно как F3 = 0,5f 'т [со штрихом], F4 = 0,5fт [без штриха], F5 = 0,5f''т [с двумя штрихами] и F6 = 0,5f'''т [с тремя штрихами].

Периоды следования импульсов первой и второй последовательностей обозначены через T1 и T2, а четырех других через T3. Период следования чередующихся символов исходного цифрового сигнала обозначен через Tц, при этом T3 = Tц.

Выходы блока формирования сетки частот [с сигналами указанных выше тактовых частот] подсоединены к соответствующим входам различных блоков первого и второго шифраторов Ш1 и Ш2 устройства - кодера. Вход блока 1 соединен с входом устройства. Структурная схема Ш1 кодера помимо блока 1 содержит еще входной элемент задержки Л3 4 [фиг. 9], вход которого является входом устройства с временем задержки, равным длительности одного символа [бита] исходного цифрового сигнала, т.е. tзад = T2, согласно фиг. 10а, в качестве которого можно взять линию задержки.

В первый шифратор Ш1 также введены блок 2 обработки пачек единичных символов, блок 3 обработки пачек чередующихся символов.

При этом первый и второй входы блоков 2 и 3 подсоединены соответственно ко входу и выходу элемента задержки ЛЗ 4, а третий вход блоков 2 и 3 подсоединен к выходу блока 1, выдающему тактовый сигнал с длительностью импульсов, равной половине длительности символов исходного цифрового сигнала [выход T2], при этом блок 3 связан также с блоком 2.

В первый шифратор Ш1 введен еще блок 5 обработки пачек нулевых символов, первый и второй входы которого подсоединены соответственно к выходам блоков 2 и 3 обработки пачек единичных и пачек чередующихся символов, причем выход блока 2 Ш1 подключен также к первому входу сумматора 6, а выход блока 5 Ш1 подключен ко второму входу сумматора 6, выход же сумматора 6 является выходом первого шифратора Ш1 кодера.

Во второй шифратор Ш2 [фиг. 9] введены блок 7 обработки положительных импульсов, блок 8 обработки нулевых значений трехуровневого сигнала Ш1, блок 10 обработки отрицательных импульсов напряжения выхода Ш1, блок 9 проверки и корректировки кода [блок П и КК].

При этом первый вход блока 9 и входы блоков 7, 8, 10 подсоединены к выходу сумматора 6 первого шифратора Ш1, а второй и третий входы блока 9 подсоединены к соответствующим выходам блоков 7 и 8. Блок 9 связан двухсторонними связями с блоком 10, а также подключен к выходам всех генераторов тактовых частот F1- F6. Выход 1 блока 9 соединен с одним из входов блока разрешения БР 11 [разрешающего или запрещающего подключения блоков 7 и 8 к выходу кодера] , два других входа блока БР 11 соединены с выходами блоков 7 и 8. Один из выходов блока 10 соединен с одним из входов блока 8. Выходы блока разрешения БР 11 и блока обработки отрицательных импульсов [бл. 10], объединенные вместе со вторым выходом блока 9 [бл. П и КК], подключены ко входу выходного блока ВБ 12, который обеспечивает согласование выхода устройства с линией связи. Выход блока ВБ 12 является выходом устройства.

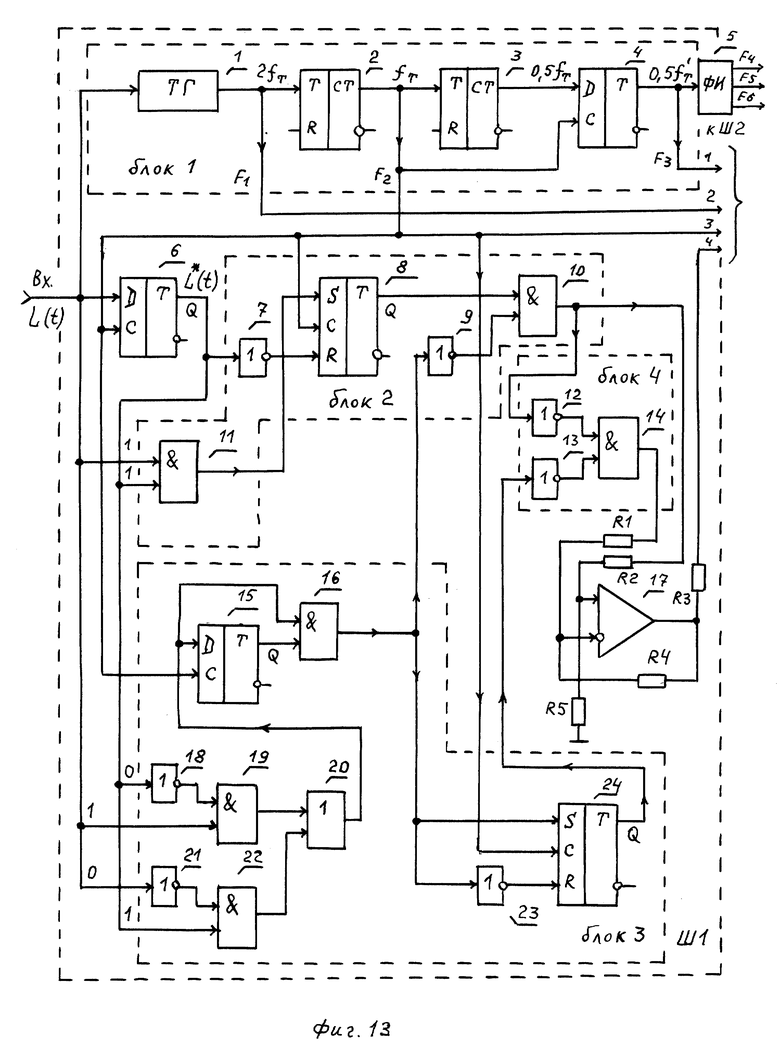

Пример конкретного выполнения принципиальной схемы первого шифратора Ш1 приведен на фиг. 13. Схема Ш1 содержит блок 1 формирования сетки частот, блок 2 обработки пачек единичных символов, блок 3 обработки пачек чередующихся символов [т.е. 1 и 0], блок 4 обработки пачек нулевых символов, а также операционный усилитель ОУ 17, который используется в качестве сумматора, и D-триггер задержки 6.

Блок 1 включает в себя расположенный на его входе задающий тактовый генератор ТГ 1 с частотой следования импульсов, равной 2fт, вход которого соединен с входом устройства. Выход ТГ 1 подключен ко входу счетного триггера СТ 2 и к одному из входов второго шифратора Ш2, а выход СТ 2 подключен ко входу аналогичного ему счетного триггера СТ 3. На выходах этих триггеров формируются тактовые импульсные сигналы с частотами следования импульсов, равными соответственно fт и 0,5fт, последняя из которых совпадает с частотой следования чередующихся символов [битов] исходного цифрового сигнала L(t).

Выход триггера СТ 3 подключен ко входу D-триггера задержки 4, на выходе которого имеет место тактовый сигнал 0,5f'т [со штрихом], т.е. задержанный на один бит выходной сигнал СТ 3.

Выход D-триггера 4 подключен к одному из входов Ш2, а также к входу блока формирования импульсов ФИ 5, на выходе которого формируют тактовые последовательности: F4, F5, F6, имеющие вид, показанный на временных диаграммах фиг. 10а. Принципиальная схема блока ФИ 5 приведена на фиг. 10в и содержит инвертор ин. 1 и линию задержки ЛЗ 1 [с tзад = 1T1], подключенные своими входами к выходу D-триггера 4, на выходах которых формируются тактовые импульсные последовательности: F4 и F5. В качестве F4 может быть использован и сигнал с выхода СТ 3.

Выход ЛЗ 1 соединен еще с входом второго инвертора ин. 2, на выходе которого формируется последовательность F6 [фиг. 10а].

Поскольку выходной трехуровневый сигнал Ш1, как далее будет показано, соответствует задержанной на один бит исходной цифровой последовательности, обозначенной через L*(t), то за начало отсчета T0 на диаграммах [фиг. 10] и всех последующих диаграмм было принято начало последовательности L*(t), совпадающее с началом первого импульса тактового сигнала 0,5f'т [со штрихом] , из которого могут быть сформированы последовательности F4, F5, F6. На входе первого шифратора Ш1 включен D-триггер задержки 6, синхронизируемый тактовым сигналом частоты fт, вход которого является входом кодера и соединен непосредственно с одним из входов двухвходовых схем совпадения 11 и 19, а также через инвертор 21 соединен с одним из входов схемы совпадения 22.

На структурной схеме кодера [фиг. 9] этот D-триггер 6 обозначен как линия задержки ЛЗ 4. Вторые входы схем совпадения 11 и 22 подключены к выходу D-триггера 6 непосредственно, а второй вход схемы совпадения 19 подсоединен к выходу D-триггера 6 через инвертор 18.

Выход D-триггера 6 подключен через инвертор 7 также и ко входу сброса R синхронного RS-триггера 8, синхронизируемого сигналом тактовой частоты fт. Вход установки S этого триггера соединен с выходом схемы совпадения 11, также входящей в состав блока 2 Ш1. Выход Q T8 подключен к одному из входов схемы совпадения 10, расположенной на выходе блока 2 Ш1. Второй вход схемы 10 через инвертор 9 соединен с выходом схемы совпадения 16, расположенной в блоке 3 Ш1.

Выход схемы 10 подключен к входу инвертора 12, а также через симметрирующий делитель напряжения R2, R5 подключен и к неинвертирующему входу операционного усилителя ОУ 17, выполняющему функцию сумматора.

Выход инвертора 12 соединен с одним из входов схемы совпадения 14, входящей вместе с этим инвертором в состав блока 4 Ш1. Второй вход схемы совпадения 14 через инвертор 13 соединен с прямым выходом Q триггера T 24, синхронизируемого сигналом тактовой частоты fт, расположенным на выходе блока 3 Ш1.

Выход схемы 14 через развязывающий резистор R1 подключен к инвертирующему входу ОУ 17 [на фиг. 9 это сумматор 6].

Выход ОУ 17 является выходом первого шифратора Ш1 и подключен к одному из входов второго шифратора Ш2 через развязывающий резистор R3.

Выходы схем совпадения 19 и 22, входящие в состав блока 3 Ш1, также соединены через схему ИЛИ 20 с входом D-триггера задержки 15 блока 3 Ш1 и с одним из входов схемы совпадения 16 этого блока, второй вход которой подсоединен к выходу D-триггера T 15, синхронизируемого тактовым сигналом частоты fт.

Выход схемы 16 соединен непосредственно с входом установки S RS-триггера Т 24, а также через инвертор 23 с входом сброса R Т 24, выход Q которого подключен непосредственно к входу инвертора 13 блока 4 Ш1.

Работа первого шифратора Ш1 кодера [фиг. 13].

При этом сначала отметим следующее.

Если бы удалось каким-либо путем в результате совместной обработки исходной L(t) и задержанной L*(t) последовательностей цифрового сигнала получить новый сигнал, имеющий период следования своих импульсов, в два [и более] раза превышающий период следования чередующихся символов исходного цифрового сигнала [т.е. получить сигнал, имеющий меньшую скорость передачи по сравнению с исходным сигналом], то для его кодирования уже мог бы быть использован тактовый сигнал частоты 0,5fт [фиг. 10а] с периодом следования импульсов, равным периоду следования чередующихся битов исходного цифрового сигнала, тогда как в известных кодах период следования тактового сигнала должен быть равен половине периода следования чередующихся битов исходного цифрового сигнала.

В указанном случае итоговый кодированный сигнал стал бы иметь скорость передачи равную скорости передачи исходного цифрового сигнала. Необходимую для этого обработку исходного цифрового сигнала и осуществляет первый шифратор Ш1 кодера.

Перед началом работы Ш1 осуществляется запуск задающего генератора тактовых импульсов ТГ 1, который может быть либо внешним, либо внутренним, синхронизированный исходной цифровой последовательностью L(t). При этом начинает функционировать весь блок сетки частот, вырабатывающий упомянутые выше тактовые последовательности [фиг. 10а]. Устройство, выдающее сигнал запуска Uзап ТГ 1, может быть и внешним по отношению к Ш1.

Далее при поступлении на вход кодера электрического сигнала, соответствующего исходному цифровому сигналу L(t), т.е. электрические уровни лог. "1" которого отвечают единичным битам, а электрические уровни лог. "0" отвечают нулевым битам L(t), входной электрический сигнал, как указывалось, предварительно задерживают на время. равное одному периоду сигнала тактовой частоты fт, что осуществляется при помощи входной линии задержки ЛЗ 4 [время задержки равно длительности одного бита]. Затем работа 1-го шифратора происходит следующим образом.

1. При наличии в исходном цифровом сигнале пачки единичных символов.

В этом случае на выходе схемы совпадения 11 появляются положительные импульсы длительностью, равной 1 биту каждый раз, когда предыдущий и последующий биты [символы] в L(t) совпадают и равны лог. 1, т.е. когда будет иметь место совпадение единичных битов в исходном L(t) и задержанном L*(t) цифровых сигналах на обоих входах схемы совпадения 11.

Выходной сигнал схемы 11 подается затем на вход установки S триггера Т8, срабатывающего по фронту входного сигнала. При этом на прямом выходе Q Т8 формируется положительный импульс длительностью, равной длительности обрабатываемой пачки единичных битов. В нулевое состояние триггер Т8 переводится сигналом лог. 1, поступающим на вход сброса R Т8 с выхода инвертора 7, включенного между выходом D-триггера задержки 6 и входом R Т8, с окончанием последнего единичного бита, присутствующего в данной пачке единичных битов у задержанной цифровой последовательности L*(t). С выхода Q Т8 сигнал поступает на один из входов схемы совпадения 10, открытой по другому ее входу сигналом лог. 1, поступающим с выхода инвертора 9, ибо с выхода схемы 16 блока 3 Ш1 сигнала в этом случае нет.

С выхода схемы 10 сигнал подается на вход инвертора 12, расположенного в блоке 4 Ш1, в результате чего нулевой выход инвертора 12 блокирует схему совпадения 14 по одному из ее входов и таким образом блок 4 Ш1 в данном случае в работе участия не принимает.

С другой стороны, выходной сигнал схемы 10 проходит на неинвертирующий вход операционного усилителя ОУ 17 [коэффициент усиления которого может быть взят близким к 1] и с его выхода импульс положительной полярности поступает на вход второго шифратора.

2. При наличии в исходном цифровом сигнале пачки чередующихся символов.

В этом случае импульсы положительной полярности будут появляться поочередно то на выходе двухвходовой схемы совпадения 19, то на выходе другой аналогичной схемы совпадения 22, далее их сигналы через схему ИЛИ 20 поступают на вход D-триггера задержки 15, синхронизируемого сигналом тактовой частоты fт.

Выход Q Т15 соединен с одним из входов схемы совпадения 16, другой вход которой соединен с выходом схемы ИЛИ 20. С выхода схемы 16 сигнал поступает на входы инверторов 9 и 23, а также на вход установки S триггера Т 24, срабатывающего по фронту импульсов и синхронизируемому сигналом тактовой частоты fт, при этом вход сброса R Т 24 соединен с выходом инвертора 23. С прямого выхода Q Т 24 сигнал поступает на вход инвертора 13 блока 4 Ш1. При этом нулевой сигнал выхода инвертора 13 блокирует схему совпадения 14 по одному из ее входов на время, равное длительности пачки чередующихся символов ["1" и "0"], присутствующих в исходном цифровом сигнале L(t).

Поэтому пачкам чередующихся символов в L(t) на выходе ОУ 17 будет соответствовать нулевой сигнал, имеющий длительность, равную длительности пачки чередующихся символов. Минимальный размер пачки чередующихся символов будет содержать таким образом два бита: либо 1 и 0, либо 0 и 1, смотря потому, после каких символов пошла пачка чередующихся битов.

3. При наличии в исходном цифровом сигнале пачки нулевых символов. В этом случае выходных сигналов не будет ни у схемы совпадения 10 блока 2 Ш1, ни на прямом выходе Q Т 24 блока 3 Ш1, и таким образом на выходах инверторов 12 и 13 блока 4 Ш1 одновременно появляются сигналы лог. 1 и, следовательно, такой же сигнал лог. 1 появится и на выходе схемы совпадения 14, на входах которой включены указанные инверторы.

С выхода схемы 14 сигнал поступает на инвертирующий вход ОУ 17, на выходе которого в этом случае формируется импульс отрицательной полярности длительностью, равной длительности пачки нулевых битов в L(t).

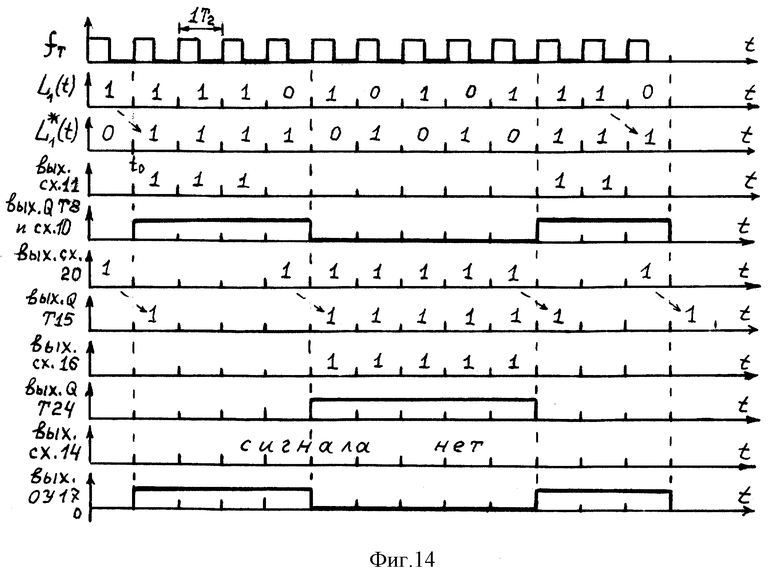

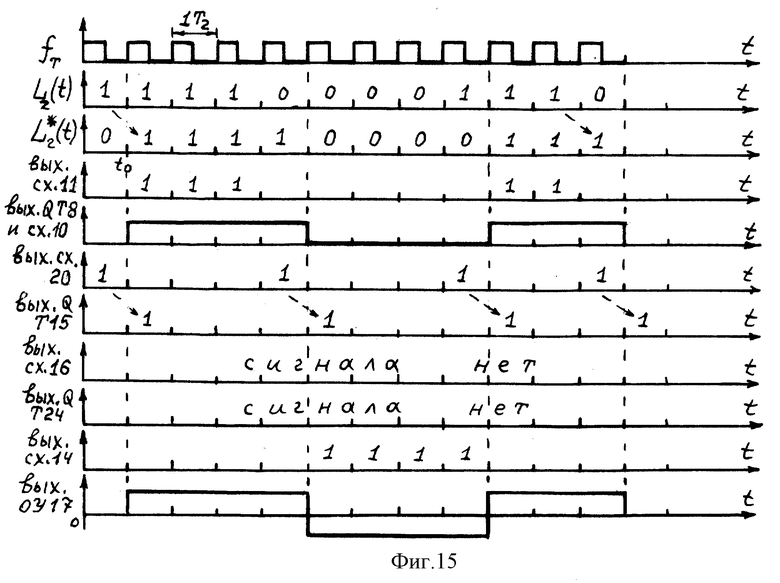

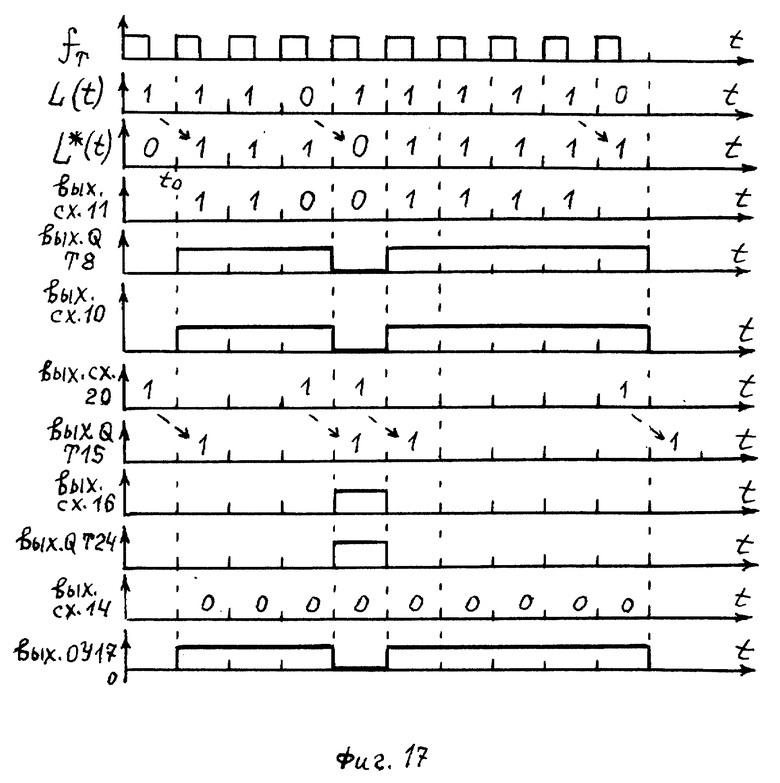

Сказанное выше поясняется временными диаграммами, приведенными на фиг. 14 и 15 для случая двух произвольно взятых в качестве примера цифровых последовательностей L1(t) и L2(t).

Таким образом, в результате работы 1-го шифратора Ш1 кодера на выходе его формируется трехуровневый импульсный сигнал, несущий в себе полную информацию об исходном цифровом сигнале L(t), а точнее о задержанном на 1 бит этом сигнале. Поэтому за начало отсчета на диаграммах "t0" и было взято начало задержанной на 1 бит исходной цифровой последовательности L*(t) [о чем выше уже говорилось].

Можно сразу же отметить, что при последующей обработке этого трехуровневого сигнала во втором шифраторе Ш2 кодера отрицательные импульсы в соответствующем блоке Ш2 снова будут преобразованы перед их обработкой в положительные той же длительности с тем, чтобы во втором шифраторе было бы возможно использование логических элементов только положительной логики, что делает схему Ш2 более простой и улучшает ее работу.

Сброс триггера Т8 на нуль осуществляется выходным сигналом инвертора 7, появляющимся с окончанием последнего единичного импульса в пачке у задержанной последовательности L*(t), что и отражают временные диаграммы [фиг. 14 и 15].

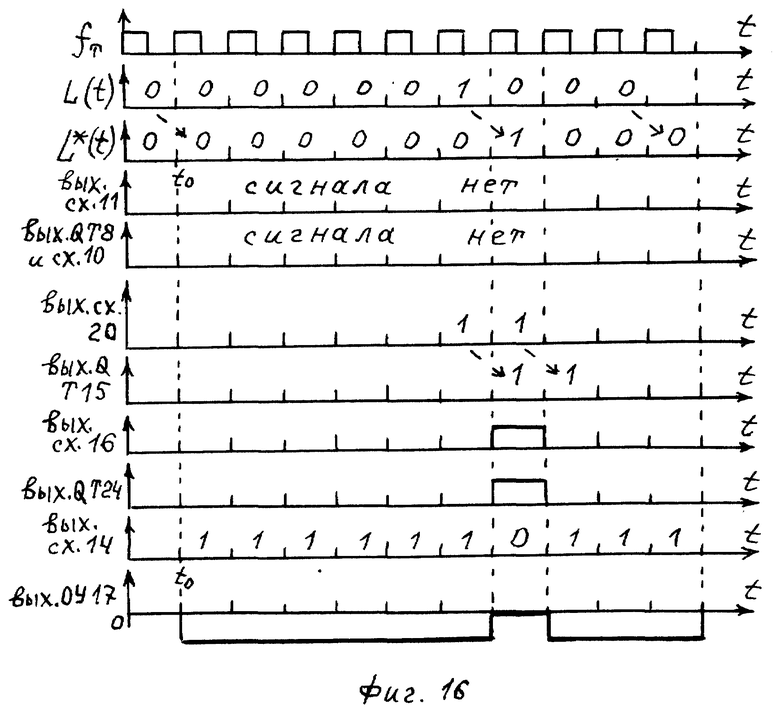

Отметим также, что когда в исходном цифровом сигнале L(t) будет присутствовать либо один единичный бит внутри пачки нулевых битов, либо наоборот, когда один нулевой бит будет находиться внутри пачки единичных битов, то это приводит в процессе работы первого шифратора Ш1 к появлению на выходе схемы совпадения 16 Ш1 одиночного импульса длительностью, равной длительности одного бита, как это показано на временных диаграммах [фиг. 16 и 17], что, в свою очередь, ведет к появлению в выходном сигнале ОУ 17, являющимся в рассматриваемых случаях либо отрицательным, либо положительным, паузы той же длительности, равной одному биту.

Как обрабатывать такие выходные сигналы ОУ 17 затем во 2-м шифраторе кодера [имеющие место при наличии в исходном цифровом сигнале двух переходов, следующих подряд с интервалом в один бит], будет показано далее при рассмотрении работы блока проверки и корректировки кода, расположенного во втором шифраторе.

Пока же отметим, что наличие полной информации об исходном цифровом сигнале L(t), имеющейся в выходном трехуровневом сигнале первого шифратора Ш1 кодера, позволяет, с одной стороны, заметно упростить схему второго шифратора Ш2 кодера, а с другой, позволяет осуществлять дополнительный контроль за работой второго шифратора Ш2 путем сравнения выходных сигналов различных блоков Ш2 с выходным сигналом первого шифратора Ш1.

Что касается построения временных диаграмм, приведенных на фиг. 14...17, то особых пояснений к ним не требуется, учитывая простоту схемы первого шифратора [фиг. 13].

Естественно, что изменяя порядок подключения выводов блоков Ш1 к инвертирующему и неинвертирующему входам ОУ 17 [выполняющим функцию сумматора] , можно изменять и сам порядок формирования импульсов, отвечающих за те, или иные пачки символов в L(t) уже при других значениях напряжения трехуровневого сигнала по сравнению с вышерассмотренным порядком формирования, что непринципиально.

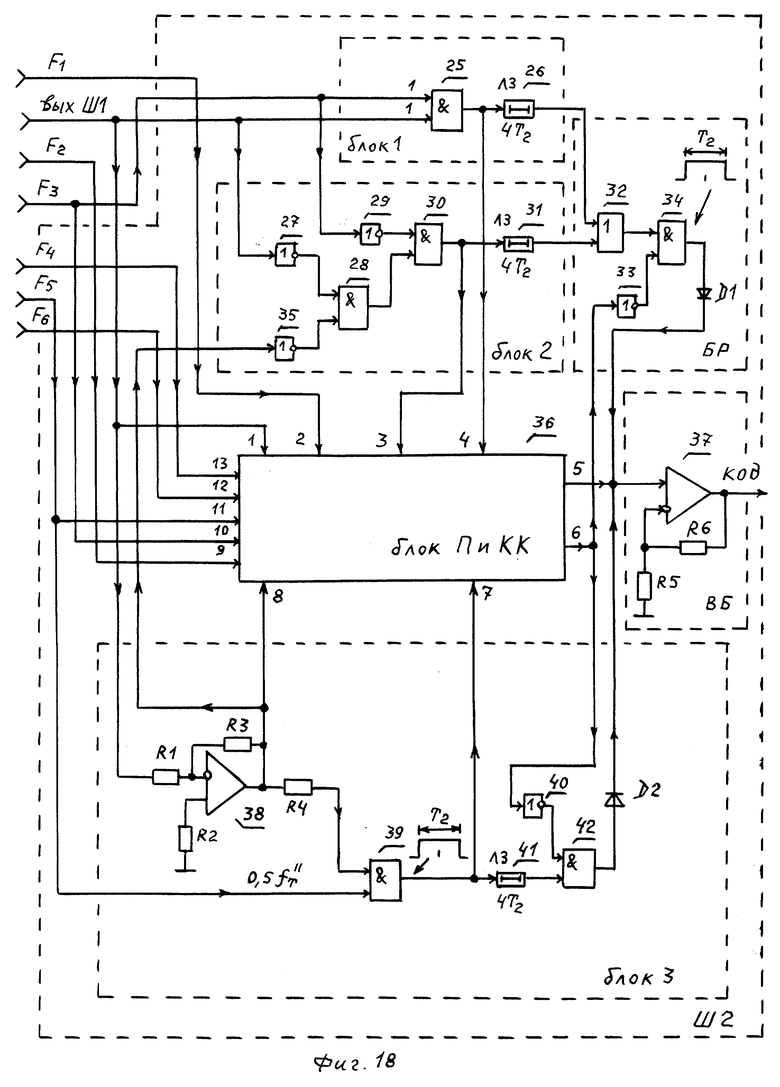

Принципиальная схема второго шифратора кодера приведена на фиг. 18 и содержит следующие элементы и блоки - блок 1, предназначенный для обработки положительных импульсов, присутствующих в трехуровневом сигнале, поступающем на вход второго шифратора Ш2 с выхода первого шифратора Ш1, включает в себя двухвходовую схему совпадения 25, один из входов которой соединен с выходом Ш1, а другой соединен с выходом D-триггера Т4 блока формирования сетки частот Ш1, выдающего тактовый сигнал с частотой следования импульсов, равной 0,5f'т [со штрихом], показанный на фиг. 10а.

Выход Ш1 соединен также с входом 1 блока проверки и корректировки кода [блок П и КК], а также с инвертирующим входом ОУ 38. Выход схемы 25 соединен с входом линии задержки ЛЗ 26 с временем задержки равным 4T2 [где T2 - период сигнала тактовой частоты fт], а выход ЛЗ 26 соединен с одним из входов схемы ИЛИ 32 и далее через разрешающий вход схемы ЗАПРЕТ 34 и развязывающий диод D1 с неинвертирующим входом выходного операционного усилителя ОУ 37, выход которого является выходом Ш2 и одновременно общим выходом кодера.

Запрещающий вход схемы 34 соединен через инвертор 33 с выходом 6 блока П и КК 36. Выход схемы 25 соединен также с входом 4 блока П и КК.

Блок 2, предназначенный для обработки нулевых значений импульсного сигнала, поступающего с выхода Ш1 кодера, включает в себя два инвертора 27 и 29, подключенных своими входами соответственно к выходу Ш1 и к выходу D-триггера задержки Т4 блока 1 Ш1, выдающему тактовый сигнала частоты 0,5f'т [со штрихом]. Выходы инверторов 27 и 29 подсоединены к первым входам соответственно схем совпадения 28 и 30, второй вход схемы 28 через инвертор 35 соединен с выходом операционного усилителя ОУ 38 блока 3 Ш2, а второй вход схемы 30 соединен с выходом схемы 28.

Выход схемы 30 подключен к входу линии задержки ЛЗ 31 с временем задержки равным 4T2 [где T2 - период сигнала тактовой частоты fт], а также ко входу 3 блока П и КК Ш2, 9-й и 2-й входы которого соединены соответственно с выходами генераторов тактовых частот fт и 2fт. Вход 10 блока П и КК соединен с выходом генератора тактовой частоты 0,5f'т [со штрихом].

Выход ЛЗ 31 подключен к одному из входов схемы ИЛИ 32, а ее выход соединен с разрешающим входом схемы ЗАПРЕТ 34, выход которой через развязывающий диод D1 соединен с неинвертирующим входом выходного операционного усилителя ОУ 37.

Элементы схемы Ш2, обозначенные номерами 32, 33, 34, а также диод D1 входят в состав блока разрешения БР 11 Ш2 [фиг. 9].

Блок 3, предназначенный для обработки отрицательных импульсов, поступающих с выхода Ш1, включает в себя операционный усилитель ОУ 38, инвертирующий вход которого через резистор R1 соединен с выходом 1-го шифратора Ш1, а также через резистор обратной связи R3 соединен с выходом этого ОУ. Коэффициент усиления ОУ 38 может быть взят близким к "1", ибо задача его состоит лишь в том, чтобы проинвертировать сигнал, поступающий на его вход с выхода Ш1, что позволяет вести обработку отрицательных значений напряжения трехуровневого сигнала в блоке 3 Ш2 в положительной логике, т.е. как и в блоках 2 и 1 Ш2. На положительные значения импульсов блок 3 Ш2 не реагирует, так как при этом отрицательный выходной сигнал ОУ 38, поступая на один из входов двухвходовой схемы совпадения 39, блокирует ее работу.

Итак, выход ОУ 38 соединен через развязывающий резистор R4 с одним из входов схемы 39, другой вход которой подключен к выходу генератора тактовой частоты 0,5f''т [с двумя штрихами]. Выход схемы 39 подсоединен к входу линии задержки ЛЗ 41, а также ко входу 7 блока П и КК.

Выход ЛЗ 41 [с временем задержки, равным 4T2, т.е. как и у ЛЗ 26 и ЛЗ 31] соединен с одним из входов схемы совпадения 42, другой вход которой подключен к выходу инвертора 40, вход которого подсоединен к выходу 6 блока П и КК 36. -Выход схемы 42 через развязывающий диод D2 соединен с неинвертирующим входом ОУ 37 и выходом 5 блока П и КК.

Блок П и КК, содержащий ряд логических элементов, образующих отдельные каналы, предназначенный во-первых, анализировать виды тех или иных комбинаций двух соседних импульсов кода в процессе его формирования с учетом как их длительностей, так и длительностей временных интервалов между ними,

во-вторых, формировать в местах переходов корректирующие импульсы в тех случаях, когда это требуется,

в-третьих, формировать импульсы, блокирующие выходы блоков 1, 2, 3 второго шифратора на время, необходимое для правильного прохождения корректирующих импульсов на выход кодера.

Более подробно о работе бл. П и КК будет сказано далее. Логические элементы, входящие в состав схем шифраторов кодера представляют собой готовые изделия, выполненные на том или ином типе логики, например на базе ТТЛ.

Цифровые линии задержки могут быть реализованы, например, на D-триггерах или на схемах памяти, регистрах сдвига.

Операционные усилители, представляющие собой стандартные изделия аналоговой схемотехники широкого применения, также являются миниатюрными, т.е. сравнимыми по размерам с логическими элементами. Таким образом, практическая реализация кодера технических трудностей не вызывает.

Работа второго шифратора Ш2 [фиг. 18].

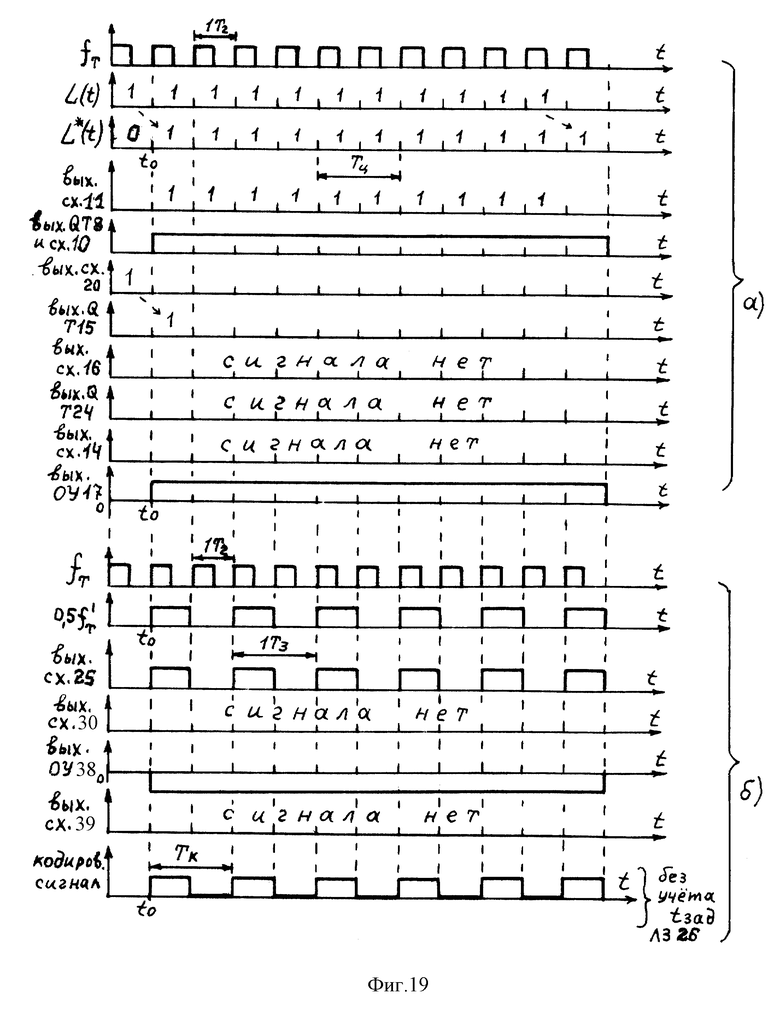

1. Работа Ш2 при поступлении на его вход импульсов положительной полярности.

В этом случае в работу включается блок 1 Ш2, при этом в коде будут формироваться однополярные импульсы также положительной полярности, причем совпадающие во времени с импульсами сигнала тактовой частоты 0,5f'т [со штрихом] и равной, как уже отмечалось, частоте следования чередующихся символов исходного цифрового сигнала L(t) и с длительностью, равной длительности импульсов этого тактового сигнала.

Сформированные импульсы кода с выхода схемы совпадения 25 поступают через линию задержки ЛЗ 26 на один из входов схемы ИЛИ 32 блока разрешения и с ее выхода на разрешающий вход схема ЗАПРЕТ 34, с выхода которой через развязывающий диод D1 подаются на неинвертирующий вход ОУ 37. С выхода этого ОУ кодированный сигнал поступает в линию передачи кода.

Сказанное поясняется временными диаграммами, приведенными на фиг. 19б. При этом для большей наглядности совместного рассмотрения диаграмм фиг. 19а [иллюстрирующих работу первого шифратора для указанного случая] и фиг. 19б [поясняющих работу Ш2] кодированный сигнал показан пока без учета действия выходной линии задержки ЛЗ 26 блока 1 Ш2, что здесь непринципиально.

Что касается ЛЗ 26, то она как и две другие линии задержки ЛЗ 31 и ЛЗ 41, расположенные соответственно на выходах блоков 2 и 3 второго шифратора, обеспечивает выравнивание времени прохождения сигналов в различных каналах Ш2, с целью их синхронной работы.

Сами же блоки 2 и 3 Ш2 на время работы блока 1 Ш2 блокируются и в работе Ш2 не участвуют. При этом блок 2 блокируется нулевым сигналом, поступающим с выхода инвертора 27 на один из входов схемы совпадения 28, поскольку на входе этого инвертора в данном случае имеет место положительный сигнал, а блок 3 Ш2 блокируется отрицательным сигналом, поступающим с выхода ОУ 38 на один из входов схемы совпадения 39, что равносильно нулевому сигналу на этом ее входе, так как входные антизвонные диоды логических схем положительной логики при этом открыты и удерживают схему от срабатывания.

Период следования сформированных в 1-м блоке Ш2 импульсов кода TК оказывается равным периоду следования Tц чередующихся символов исходного цифрового сигнала L(t), что и требуется.

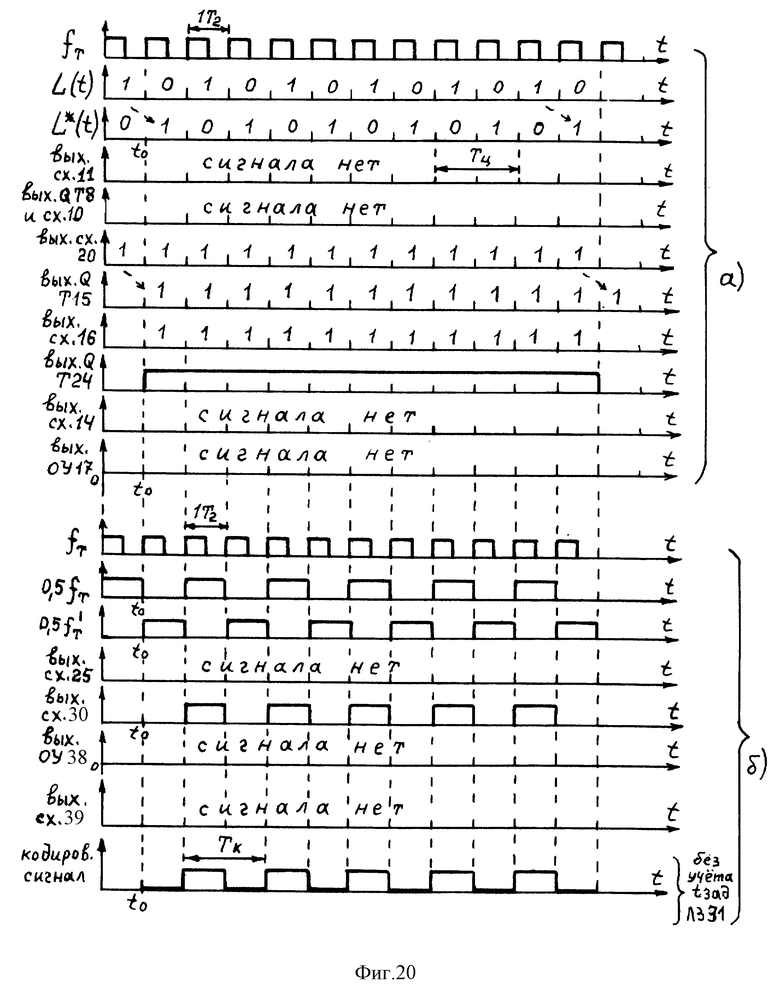

2. Работа Ш2 при поступлении на его вход с выхода Ш1 нулевого уровня импульсного сигнала.

В этом случае работа блока 1 Ш2 прекращается, ибо схема совпадения 25 блокируется по одному из входов нулевым сигналом Ш1. В тоже время начинает функционировать блок 2 Ш2, причем только в те моменты времени, когда сигнал генератора тактовой частоты 0,5f'т [со штрихом] будет также иметь нулевые значения, или иначе говоря, когда имеет место сигнал тактовой частоты 0,5fт [без штриха] , что обеспечивается выходным сигналом инвертора 29, на входе которого действует сигнал частоты 0,5f'т [со штрихом], поскольку выход этого инвертора подключен к одному из входов схемы совпадения 30.

В тоже время на второй вход схемы совпадения 30 подавать сигнал прямо с выхода Ш1 также через инвертор нельзя, ибо на выходе Ш1 имеет место не двух, а трехуровневый импульсный сигнал и потому схема совпадения 30 могла бы начать реагировать не только на нулевые, но и на отрицательные значения выходного сигнала Ш1 и что нарушило бы нормальную работу второго шифратора Ш2, поскольку наличие антизвонных диодов на входе логических элементов [о чем выше говорилось] снижает уровни отрицательных напряжений на их входе до значения, не превышающего 0,7 В, на которые схема реагирует как на нулевой сигнал.

Именно поэтому в блок 2 Ш2 дополнительно введена двухвходовая схема совпадения 28 с инверторами 27 и 35, включенными на ее входах. В этом случае сигнал лог. "1" хотя и будет возникать на верхнем входе схемы 28 при наличии на выходе Ш1 не только нулевых, но и отрицательных уровней напряжения, однако на нижнем входе схемы совпадения 28 сигнала лог. "1" при отрицательных напряжениях на выходе Ш1 возникать не будет, ибо выход Ш1 подключен к инвертирующему входу ОУ 38, с выхода которого уже не отрицательный, а положительный сигнал, будучи поданный на вход инвертора 35, подключенного к одному из входов схемы 28, будет блокировать ее работу по этому входу нулевым выходным сигналом инвертора 35. Таким образом сигнал лог. "1" на нижнем входе схемы совпадения 30 будет появляться только лишь при нулевых уровнях импульсного сигнала, поступающего с выхода Ш1, что и требуется.

При этом в коде, как и в первом рассмотренном выше случае, будут формироваться также однополярные положительные импульсы и опять же с длительностью, равной длительности одного бита исходного цифрового сигнала, следующие с частотой следования чередующихся символов этого сигнала.

Время появления этих импульсов кода соответствует нулевым значениям сигнала тактовой частоты 0,5f'т [со штрихом], или иначе совпадает с сигналом тактовой частоты 0,5fт [без штриха], поскольку сигналы этих тактовых частот сдвинуты друг относительно друга на время, равное половине периода следования их импульсов, т.е. находящимися в противофазе [фиг. 10а].

Сказанное поясняется временными диаграммами, приведенными на фиг. 20б, при этом на фиг. 20а приведены временные диаграммы, поясняющие работу 1-го шифратора кодера для рассматриваемого случая.

Действие выходной линии задержки ЛЗ 31 блока 2 Ш2 при построении диаграмм фиг. 20б для лучшей наглядности их рассмотрения совместно с диаграммами фиг. 20а во внимание пока не принято [что здесь непринципиально].

3. Работа Ш2 при поступлении на его вход импульсов отрицательной полярности. В этом случае в работу включается блок 3 Ш2, а работа блоков 1 и 2 блокируется соответственно отсутствием сигнала лог. "1" на нижнем входе схемы совпадения 25 и нулевым выходным сигналом инвертора 35, на входе которого будет присутствовать положительный сигнал, снимаемый с выхода ОУ 38, расположенного в блоке 3 Ш2.

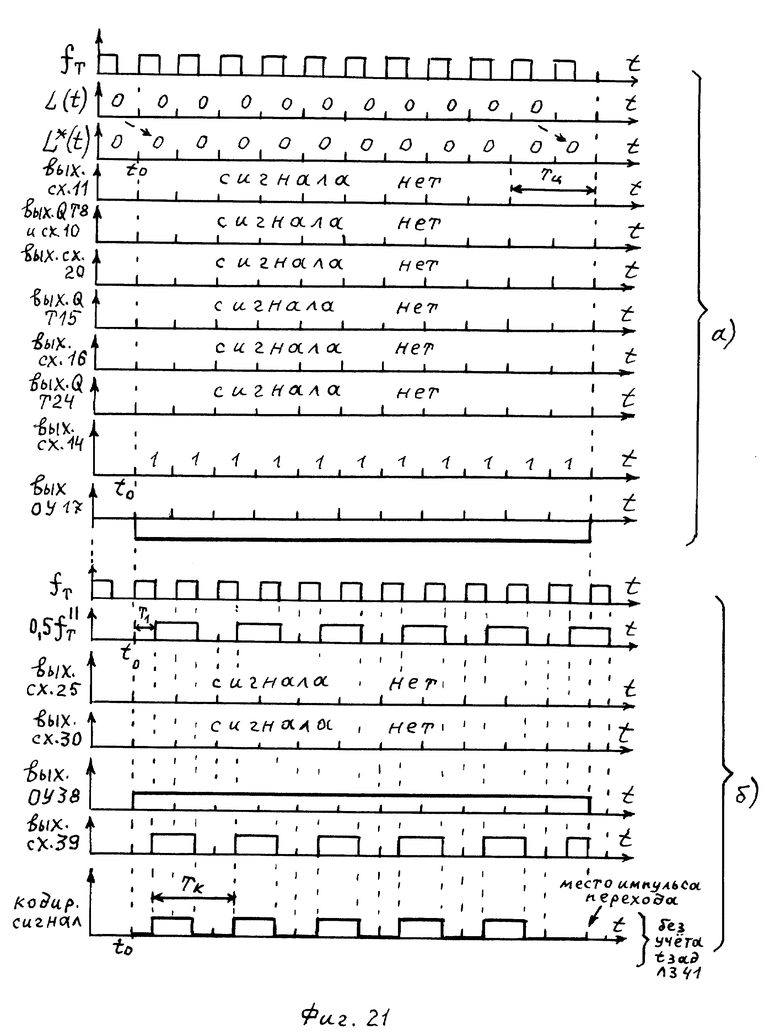

Отрицательный импульс, присутствующий на выходе Ш1, а следовательно, и на инвертирующем входе ОУ 38, создает импульс положительной полярности на выходе этого ОУ 38, в результате чего схема совпадения 39 будет разблокирована по своему верхнему входу на время, равное длительности отрицательного импульса, имеющего место на выходе Ш1. В этом случае импульсы генератора тактовой частоты 0,5f''т [с двумя штрихами] будут проходить через ЛЗ 41 и схему совпадения 42 на неинвертирующий вход ОУ 37 и с его выхода в линию передачи кода. Сказанное поясняют временные диаграммы, приведенные на фиг. 21б. На диаграммах фиг. 21а приведены сигналы отдельных блоков 1-го шифратора, отвечающие рассматриваемому случаю. Действие выходной линии задержки ЛЗ 41 блока Ш2 во внимание пока не принято для более наглядного совместного рассмотрения диаграмм, показанных на фиг. 21а и 21б [что непринципиально].

Поскольку формирование предлагаемого кода сопровождается такими операциями, как поочередная разбивка [разметка] исходного цифрового сигнала L(t), с последующим кодированием, то получающийся при этом код может быть сокращенно определен [назван] , как код "ALC", по аналогии с известными кодами типа: NRZ, AMI, CMI, MFM и др. [расшифровка которых была ранее приведена], обозначенными первыми буквами английских слов.

Действительно, если принять во внимание перевод английских слов:

Alternative - поочередный, знакопеременный,

Lay-out - разбивка, разметка,

Code - код,

то по первым буквам и получается "ALC".

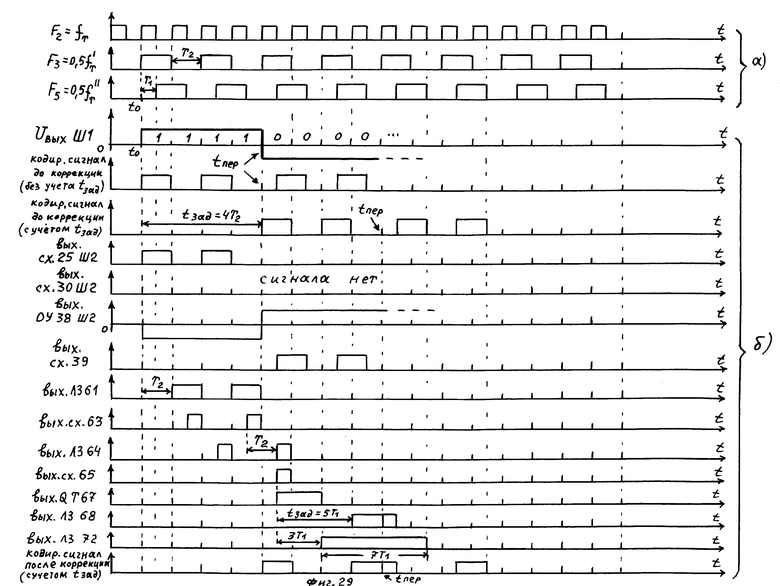

4. Работа 2-го шифратора кодера в моменты времени, соответствующие переходам в исходном цифровом сигнале от пачек одних символов к пачкам других символов.

При этом могут иметь место два характерных случая.

1. Последний символ пачки, предшествующей переходу, совпадает с сигналом тактовой частоты F3 = 0,5f'т [со штрихом], фиг. 10а.

2. Последний символ пачки, предшествующей переходу, совпадает с сигналом тактовой частоты F4 = 0,5fт [без штриха], фиг. 10а.

Или, если принять за начало отсчета [t0] время, совпадающее с моментом появления первого импульса сигнала тактовой частоты 0,5f'т [со штрихом], как это и было сделано при построении временных диаграмм и считать, что первая рассматриваемая пачка начинается в момент t0, то можно охарактеризовать указанные два случая и иначе, а именно, в зависимости от того было ли число битов в предшествующей переходу пачке, начинающейся в момент времени появления тактового сигнала F3 = 0,5f'т [со штрихом] четным, или же нечетным.

В процессе формирования импульсов кода в местах переходов также могут иметь место и два других случая: когда корректировки кода не требуется и когда возникает необходимость корректировки кода. Далее эти случаи будут рассмотрены.

Выходные сигналы блоков 1, 2, 3 Ш2 на время проверки правильности формирования импульсов кода блоком П и КК должны быть, естественно, задержаны, для чего на выходах этих блоков и размещены упомянутые выше линии задержки ЛЗ 26, 31, 41. Рассмотрение особенностей формирования кодированного сигнала при использовании четырех тактовых импульсных последовательностей F3 ...F6 показывает следующее.

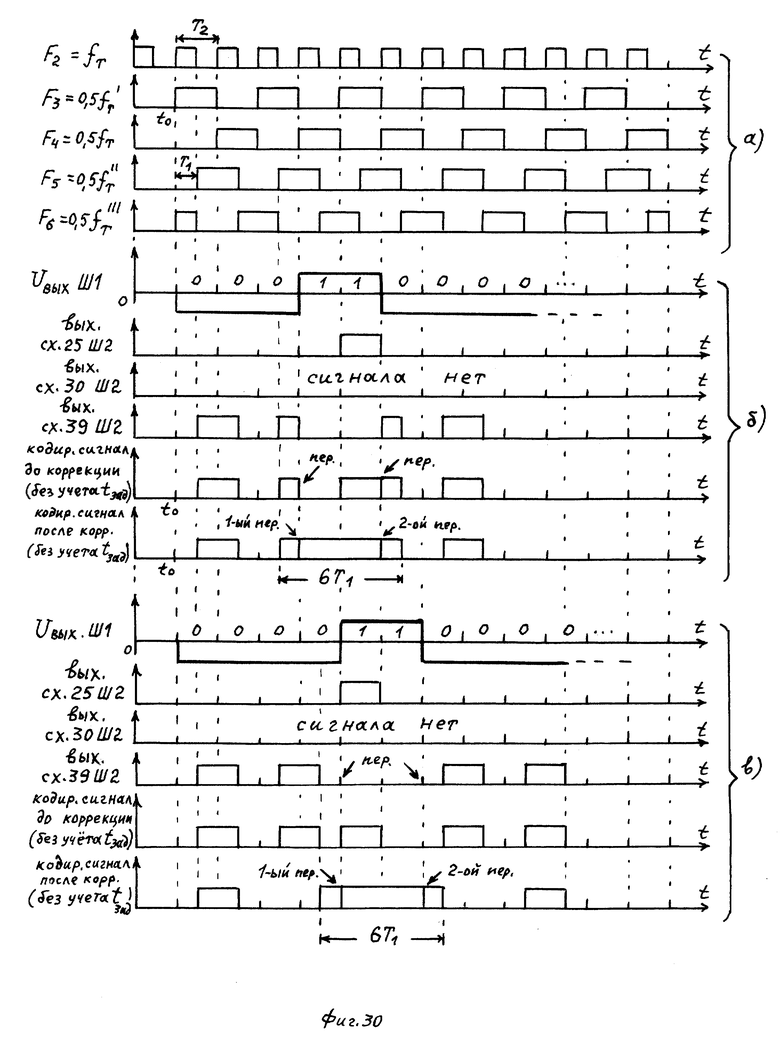

1. Так, при формировании импульсов кода в местах переходов от пачек единичных символов [битов] к пачкам нулевых битов, в случае совпадения последнего единичного бита пачки с сигналом тактовой частоты F4, корректировки получаемого кодированного сигнала не требуется, а дешифрация кода обеспечивается.

В случае, если последний бит пачки единичных символов совпадает с сигналом тактовой частоты F3, то в кодированном сигнале в месте перехода образуется импульс кода длительностью, равной 3T1, начало которого совпадает с началом импульсов тактовой последовательности F3. При этом граница перехода отстоит от начала этого импульса кода на расстоянии, равном 2T1, корректировки кода в данном случае не требуется, а его дешифрация обеспечивается.

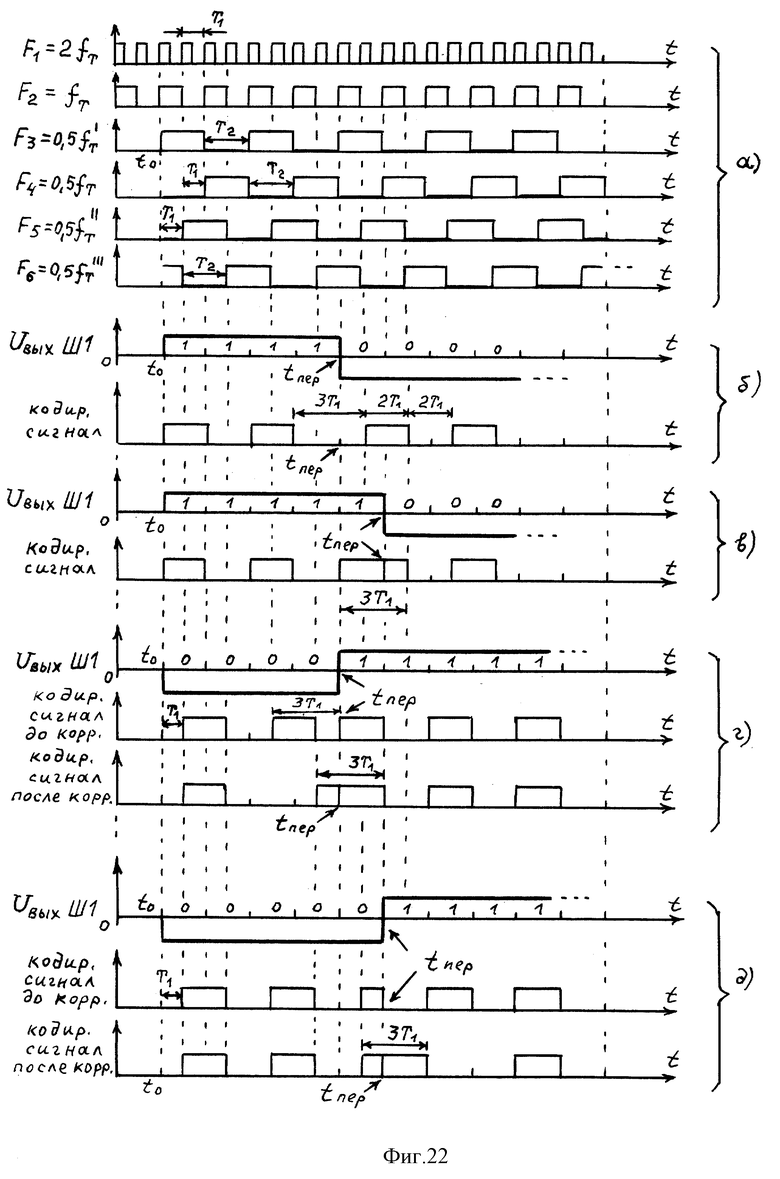

Сказанное иллюстрируют временные диаграммы, приведенные на фиг. 22б, в, на которых показан также и вид выходного напряжения первого шифратора Uвых Ш1, отвечающий рассматриваемым случаям переходов, способ получения которого выше был рассмотрен.

2. При формировании импульсов кода в местах переходов от пачек нулевых битов к пачкам единичных битов в случае, если последний нулевой бит совпадает с сигналом тактовой частоты F4, в получаемом кодированном сигнале граница перехода отражена точно, однако период следования импульсов кода в месте перехода равен значению 3T1, что ухудшает частотные свойства кода [ибо период следования импульсов кода должен быть не менее чем 4T1].

Поэтому в данном случае требуется корректировка кода, например, путем формирования импульса длительностью 3T1, начало которого совпадает с сигналом "F6", при этом дешифрация кода обеспечивается.

В случае, если последний нулевой бит пачки совпадает с сигналом тактовой частоты F3, в получаемом кодированном сигнале в месте перехода возникает импульс длительностью, равной 1T1, что также ухудшает частотные свойства кода, при этом и граница перехода точно не дешифруется. Поэтому здесь требуется корректировка кода [с использованием блока проверки и корректировки кода] , которая может быть осуществлена, например, путем формирования в месте перехода импульса кода длительностью, равной 3T1, начало которого совпадает с началом сигнала тактовой частоты F5 с границей перехода на расстоянии, равном 1T1 от его начала. Сказанное иллюстрируют временные диаграммы, приведенные на фиг. 22г, д, на которых показан также и вид выходного напряжения первого шифратора, отвечающий этим случаям.

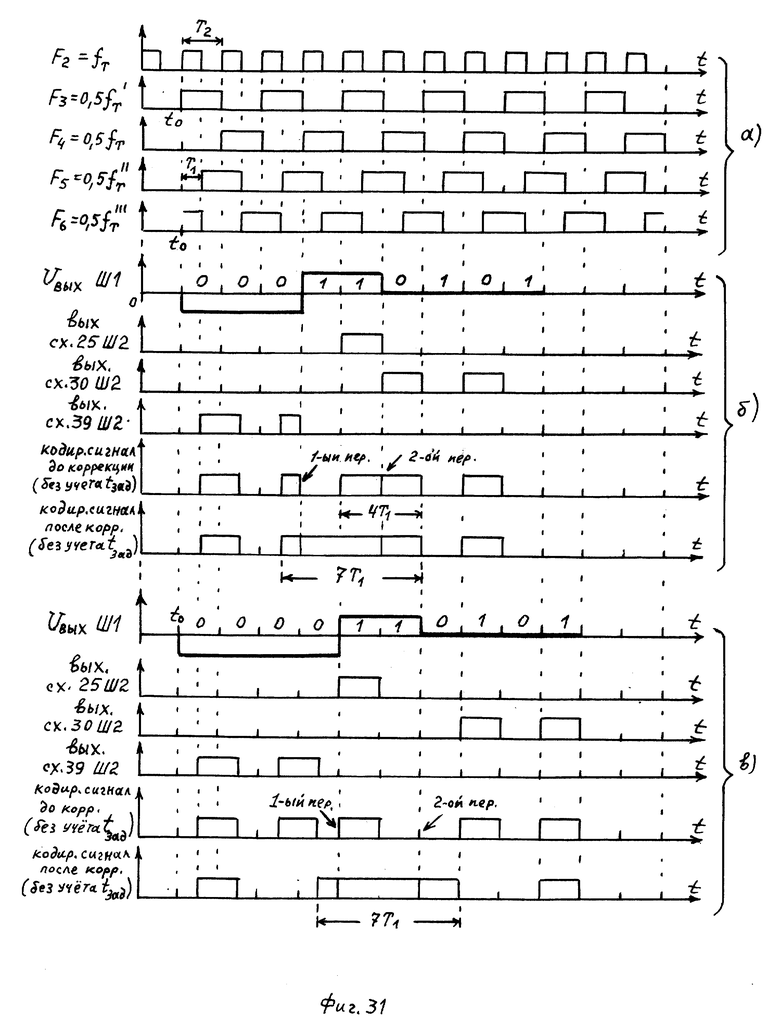

3. При формировании импульсов кода в местах переходов от пачек чередующихся битов к пачкам нулевых битов, в случае, если последний единичный бит пачки чередующихся битов совпадает с сигналом тактовой частоты F4, то в месте перехода образуются два импульса кода, имеющие длительность, равную 2T1, следующие друг за другом с периодом, равным 3T1, что по этой причине ухудшает частотные свойства кода. В этой связи требуется корректировка кода, например, путем формирования в месте перехода импульса длительностью, равной 3T1, начало которого совпадает с началом сигнала тактовой частоты F4, с границей перехода, расположенной на расстоянии 2T1 от его начала, что не трудно учесть при последующей дешифрации кода. Этот импульс заменяет собой два импульса кода в зоне перехода, присутствовавшие там до коррекции кода.

В случае, если последний единичный бит пачки чередующихся битов совпадает с сигналом тактовой частоты F3, то в месте перехода образуется импульс длительностью, равной 1T1 при формировании кода согласно рассматриваемому способу, что также ухудшает частотные свойства кода, поэтому и в данном случае требуется корректировка кода перед его отправкой в линию связи, например, путем формирования в месте перехода импульса кода длительностью, равной 3T1, начало которого совпадает с началом сигнала тактовой частоты F3, с границей перехода, расположенной на расстоянии, равном 2T1 от его начала, что не трудно учесть при дешифрации кода.

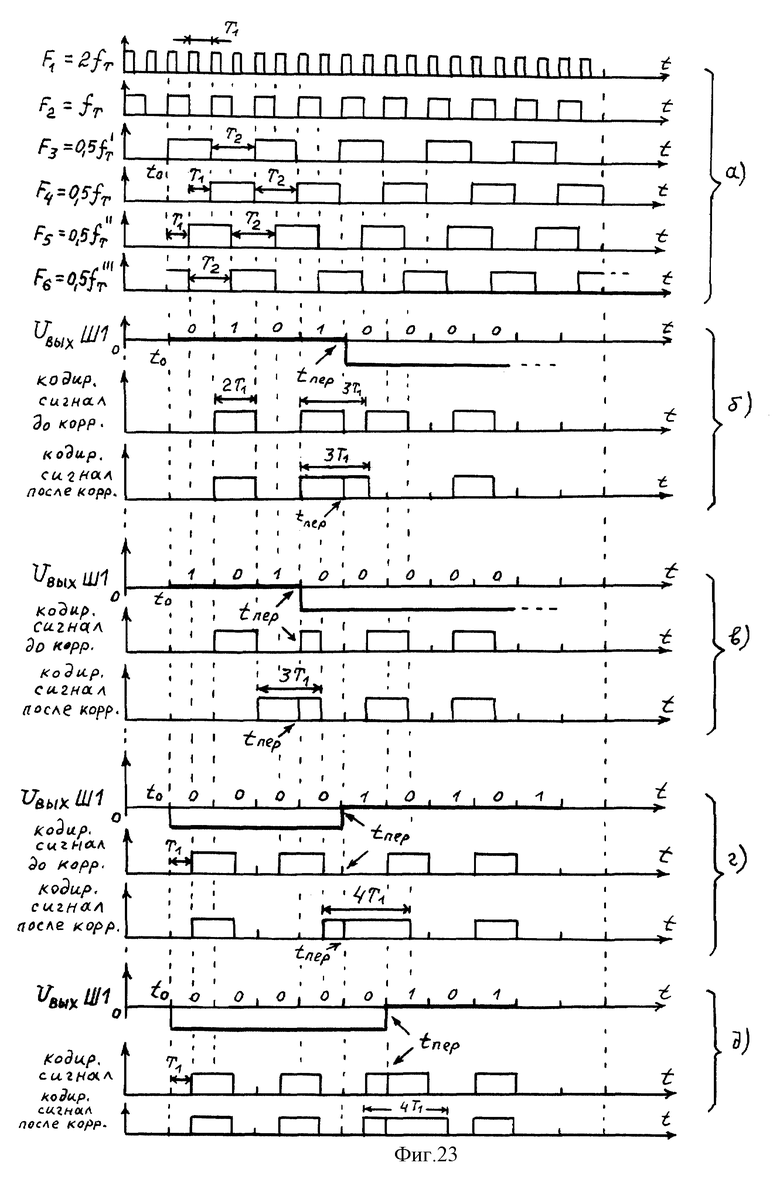

Сказанное иллюстрируют диаграммы, приведенные на фиг. 23 б, в.

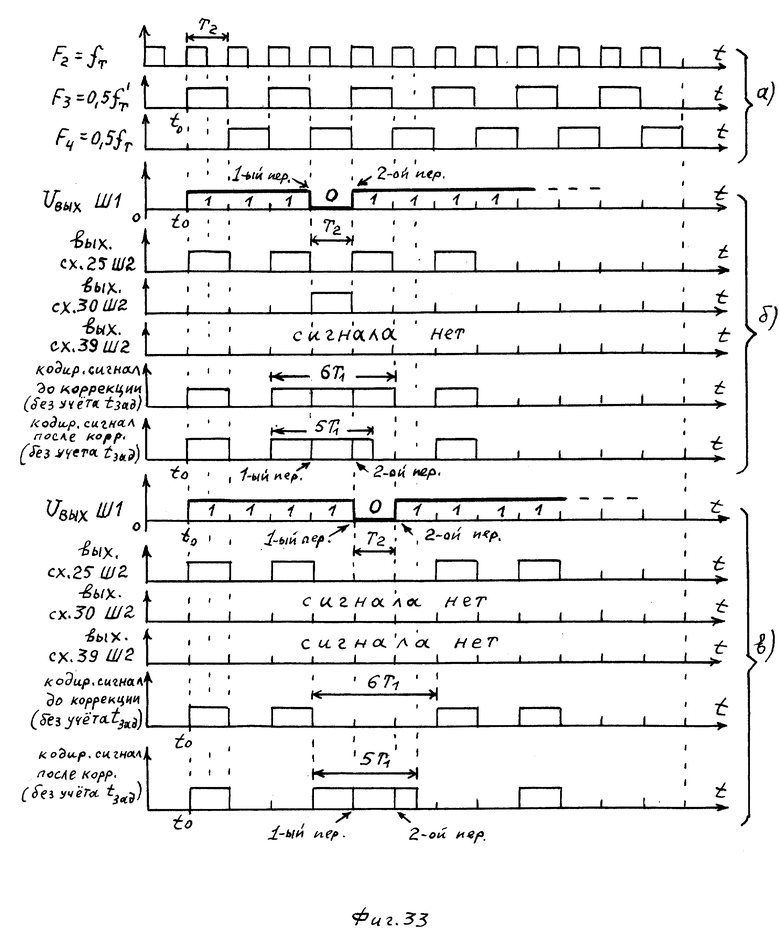

4. При формировании импульсов кода в местах переходов от пачек нулевых битов к пачкам чередующихся битов, в случае, если последний нулевой бит пачки приходится на сигнал тактовой частоты F4, то требуется корректировка кода, как это видно из диаграмм фиг. 23г, например, путем формирования в месте перехода корректирующего импульса длительностью, равной 4T1, начало которого совпадает с сигналом тактовой частоты F6, как показано на фиг. 23г. Граница перехода располагается внутри этого импульса на расстоянии, равном 1T1 от его начала, что также не трудно учесть при дешифрации кода при наличии в декодере аналогичного блока формирования сетки частот [как и в кодере] , содержащем в том числе и генератор с периодом следования импульсов, равным 1T1.

В случае, если последний нулевой бит пачки совпадает с сигналом тактовой частоты F3, в месте перехода образуется импульс с длительностью, равной 3T1, начало которого совпадает с сигналом тактовой частоты F5, т.е. как и в случае корректирующего импульса, показанного на фиг. 22д, поэтому здесь нужна корректировка, например, путем формирования импульса длительностью не 3T1, а 4T1 [фиг. 23д].

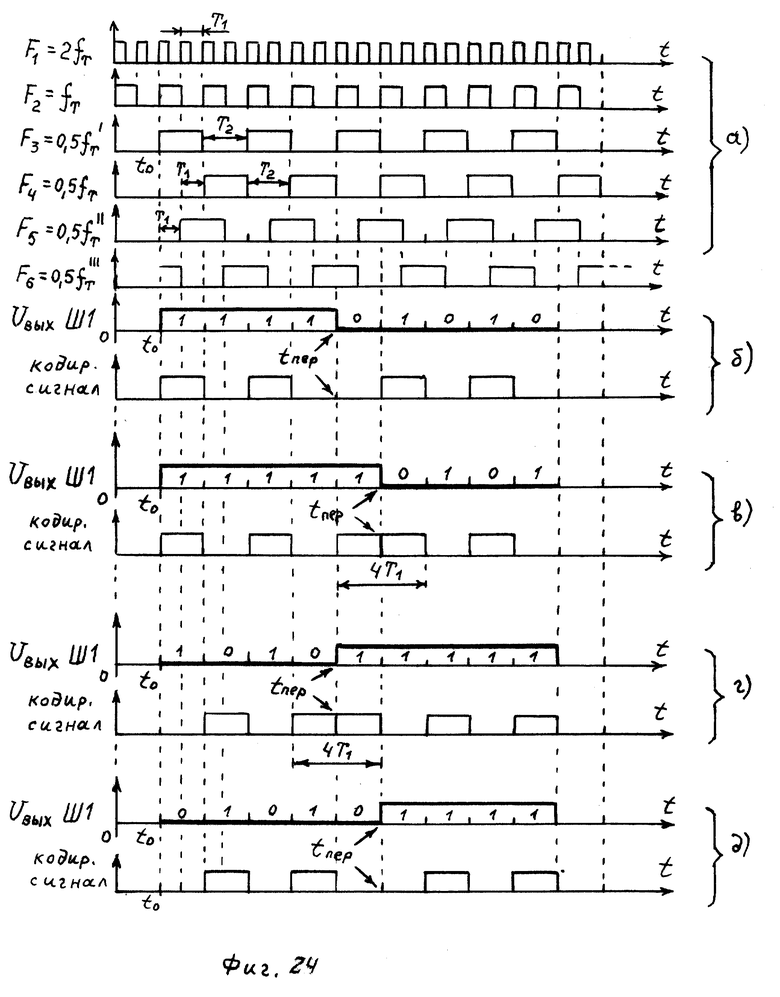

5. В процессе формирования импульсов кода в местах переходов от пачек единичных битов к пачкам чередующихся битов и наоборот, можно обойтись и без корректировки кода во всех четырех встречающихся случаях, ибо и частотные свойства кода не ухудшаются и дешифрация кода обеспечивается.

Сказанное иллюстрируют временные диаграммы, приведенные на фиг. 24б, в, г, д. На этих диаграммах, как и ранее показан также и вид выходного напряжения первого шифратора Uвых Ш1, отвечающий рассматриваемым случаям переходов, способ получения которого выше был рассмотрен.

В сравнении с двухфазовым кодом с половинчатой длиной импульсов [код HPDB] , взятому за прототип, предлагаемый код по способу его формирования [рассмотренному выше] представляет собой по аналогии с прототипом как бы трехфазовый код и уже не с половинчатой, а с полной длиной импульсов, равной длительности одного бита исходного цифрового сигнала [и более в местах переходов], что, естественно, улучшает частотные свойства кодированного сигнала.

Выделение отдельных пачек различных символов в исходном цифровом сигнале позволяет увеличить корреляционнные связи между импульсами и облегчает таким образом поиск и устранение отдельных ошибок, возможных при передаче кода.

Этому же способствует и то обстоятельство, что корректирующие импульсы могут быть сформированы таким образом, что вид каждого из них будет указывать на то, к пачке каких именно символов в исходном цифровом сигнале имеет место переход в том, или ином случае.

Как следует из вышеизложенного, в кодированном сигнале, полученном согласно предложенному способу кодирования, имеют место импульсы различной длительности, кратной половине длительности одного бита [но не меньшей, чем длительность одного бита]: 2T1, 3T1, 4T1 [где T1 - длительность половины бита].

При этом в случае следующих подряд различных переходов в исходном цифровом сигнале импульсы, их кодирующие, могут соединяться друг с другом, образуя более длительные импульсы, например, вида 6T1 [при слиянии двух импульсов длительностью, равной 3T1], или 7T1 [при слиянии импульсов вида 3T1 и 4T1].

При этом следует отметить, что за счет соответствующего выбора видов самих корректирующих импульсов тех или иных переходов удается избежать появления в коде импульсов нежелательных длительностей.

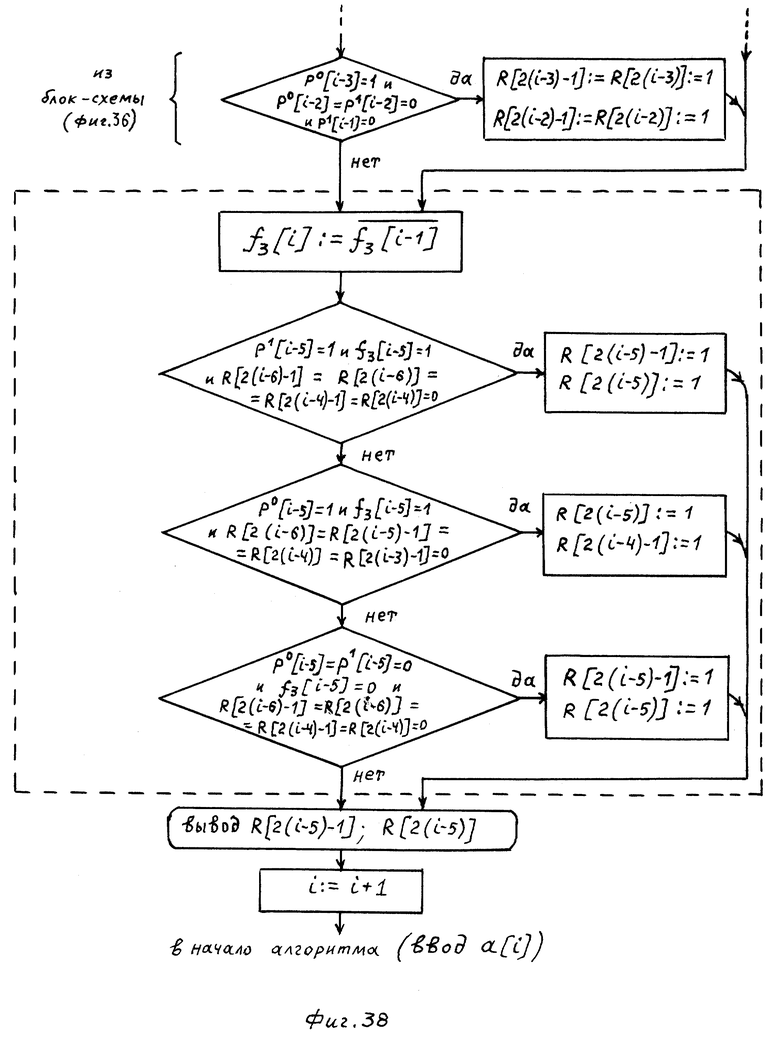

Переходим теперь к рассмотрению построения и работы блока П и КК.

Блок проверки и корректировки кода [блок П и КК]

Как ранее уже отмечалось блок П и КК предназначен для проверки процесса формирования импульсов кода в местах переходов от пачек одних символов, присутствующих в исходном цифровом сигнале, к пачкам других символов и осуществления необходимой корректировки кода перед передачей его в линию связи, в том числе и с чередующейся полярностью импульсов в тех случаях, когда это требуется.

Сущность процесса корректировки при различных типах переходов была также рассмотрена выше.

Что касается конкретных схемных решений по реализации блока П и КК, то и они могут быть различными.

В этой связи авторы обращают внимание экспертизы на то, что ими заявляется как способ, так и общая структурная схема устройства [а не какая-то отдельно взятая схемная реализация предложенной структуры устройства], позволяющая осуществить рассматриваемый способ кодирования.

В структурной схеме устройства [фиг. 9], содержащей два шифратора, присутствует и блок П и КК с указанием его электрических связей с другими блоками.

В заявке рассмотрен также пример конкретной схемной реализации устройства, включающий принципиальные схемы блоков обоих шифраторов [фиг. 13 и 18], за исключением блока П и КК, данного на фиг. 18 в общем виде, но с приведением в описании временных диаграмм [фиг. 22-24], поясняющих его работу, что было достаточно для рассмотрения сущности и особенностей предложенного способа кодирования.

Теперь о том, что касается построения схемы самого блока П и КК.

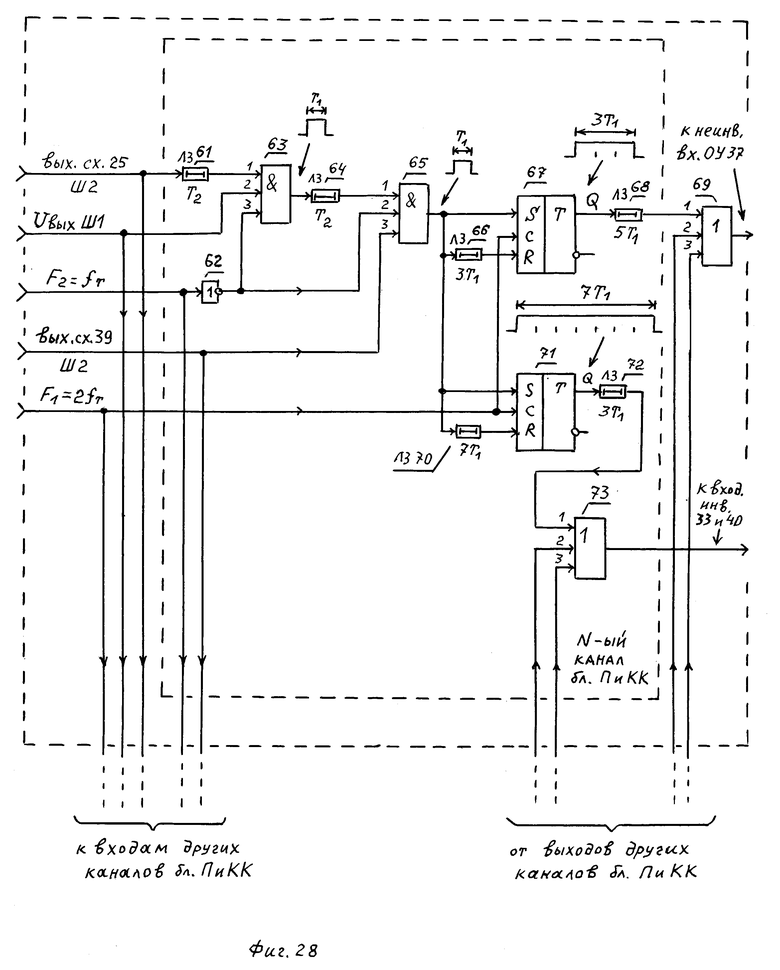

При этом следует отметить, что для осуществления корректировки кода блок П и КК должен включать в себя ряд логических схем, образующих вместе отдельные каналы, каждый из которых отвечает за формирование того или иного корректирующего импульса.

Следует также подчеркнуть, что построение схем каналов блока П и КК однотипно, а потому вполне достаточно рассмотреть схемную реализацию одного-двух каналов этого блока.

Схема каждого из каналов блока П и КК включает в себя одну или несколько входных схем совпадения, обеспечивающих распознание той или иной наперед заданной комбинации импульсов кода, а также два триггера, один из которых формирует корректирующий импульс заданной длительности, начало которого совпадает с началом той или иной тактовой импульсной последовательности блока формирования сетки частот.

Другой триггер формирует блокирующий импульс необходимой длительности, зависящей от расположения импульсов кода, подвергаемых корректировке в зоне перехода.

Этот импульс должен своевременно начать блокировать выходы блоков второго шифратора кодера на время, необходимое для правильного прохождения корректирующего импульса на выход кодера.

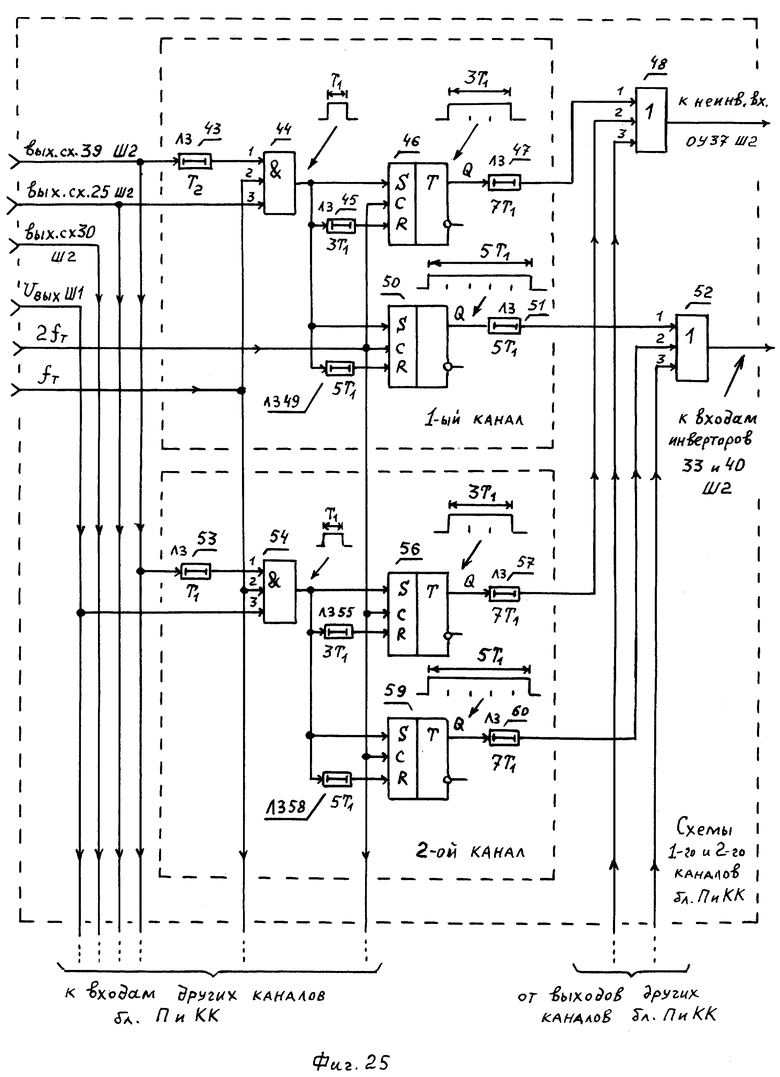

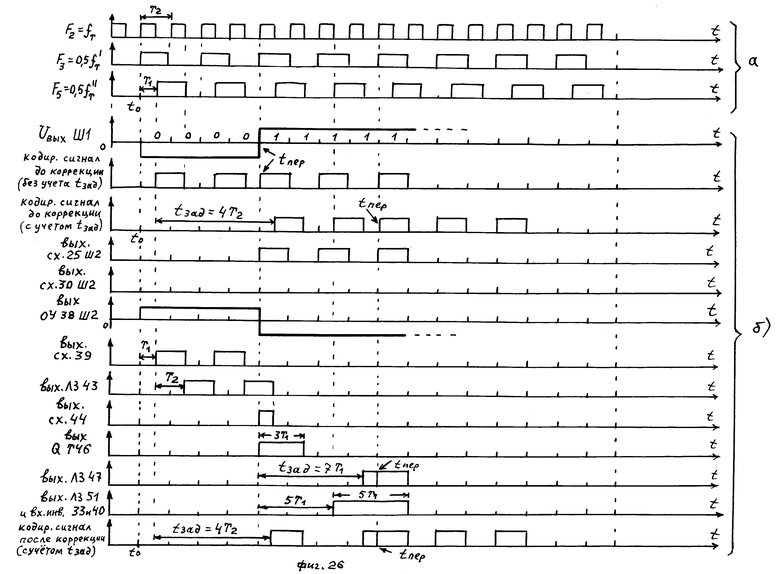

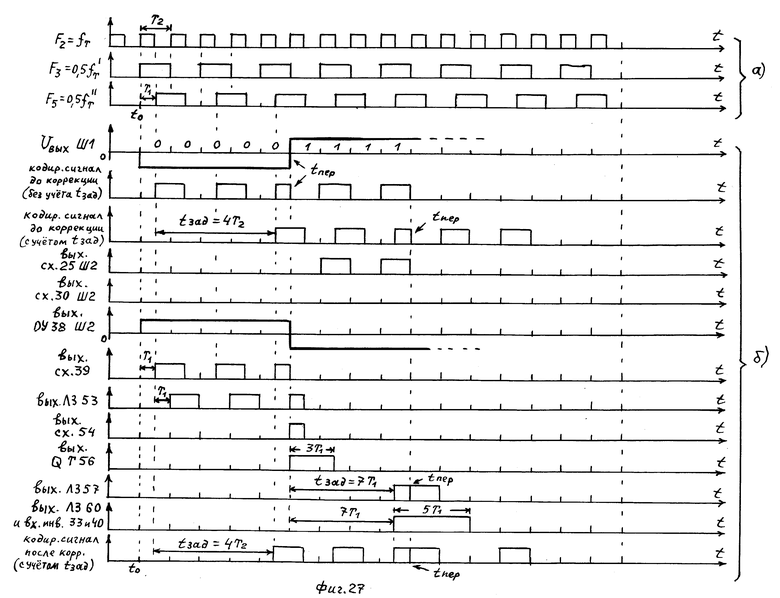

Согласованное во времени действие указанных импульсов обеспечивают линии задержки, расположенные в каналах блока П и КК. Схемы 1-го и 2-го каналов блока П и КК приведены на фиг. 25. 1-й канал блока П и КК содержит трехвходовую схему совпадения 44, первый вход которой через линию задержки 43 с временем задержки, равным 1T2, подсоединен к выходу схемы 39 блока 3 Ш2 [фиг. 18] , в котором формируются импульсы кода, отвечающие за кодирование пачек нулевых символов, присутствующих в исходном цифровом сигнале. Второй вход схемы совпадения 44 соединен с выходом генератора тактовой частоты fт блока формирования сетки частот, а третий вход сх. 44 подсоединен к выходу схемы 25 блока 1 Ш2, в котором формируются импульсы кода, отвечающие за кодирование пачек единичных символов.

Выход схемы 44 соединен с входом установки S RS-триггера T 46, а также через линию задержки ЛЗ 45 [с временем задержки, равным 3T1] с входом сброса этого триггера.

Прямой выход Q T 46, на котором формируется корректирующий импульс длительностью, равной в данном случае 3T1, соединен через ЛЗ 47 [с временем задержки, равным 7T1] с первым входом схемы ИЛИ 48, выход которой соединен с неинвертирующим входом операционного усилителя ОУ 37 Ш2.

Выход схемы 44 блока П и КК соединен также с входом установки S RS-триггера T 50, а также через ЛЗ 49 [с временем задержки, равным 5T1] с входом сброса R этого триггера. [напомним, что T1 - это половина длительности одного бита исходного цифрового сигнала].