Изобретение относится к электросвязи я может использоваться для приема цифрового сигнала с амплитудно- фазовой модуляцией и одной боковой полосой (АФМ ОБП).

Цель изобретения - повьшение достоверности приема.

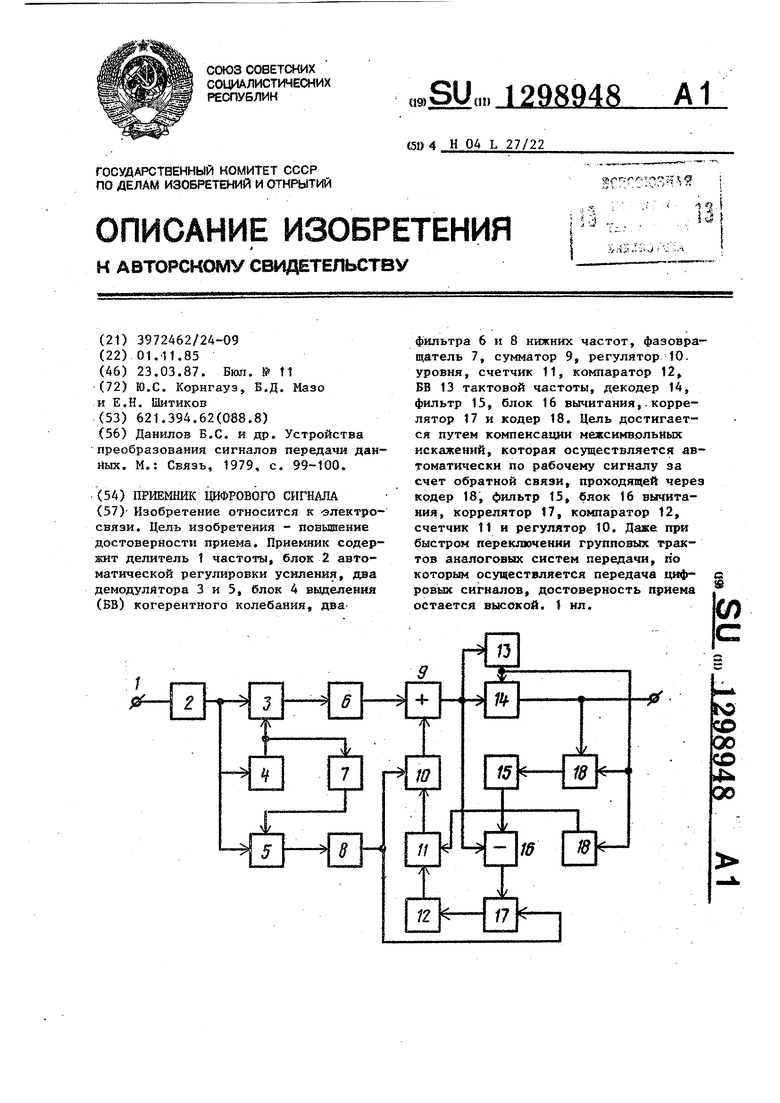

На чертеже изображена структурная электрическая схема предложенного приемника.

Приемник содержит делитель 1 частоты, блок 2 автоматической регулировки усиления, демодулятор 3, блок 4 вьщеления когерентного колебания, дополнительный демодулятор 5, фильтр 6 нижних частот, фазовращатель 7, дополнительный фильтр 8 нижних частот, сумматор 9, регулятор 10 уровня счетчик 11, компаратор 12, блок 13 вьщеления тактовой частоты, декодер 14, фильтр 15, блок 16 вычитания, коррелятор 17, кодер 18.

Приемник работает следующим об- разом.

Цифровой сигнал, передаваемый в спектре типовой группы аналоговых : систем передачи (АСП) методом АФМ ОБЦ, поступает на вход блока 2. С выхода блока 2 цифровой сигнал поступает на входы демодулятора 3 и дополнительного колебания, который вьщеляет пилот-сигнал несущей частоты, кото$1ЬЙ замешан на передающей стороне. С выхода блока 4 несущая частота поступает на другой вход демодулятора 3 и через фазовращател ,7 на 90 - на другой вход дополнительного демодулятора 5. Сигнал с выхода демодулятора 3 подается на вход фильтра 6, а.с выхода дополнительного демодулятора 5 на вход дополнительного фильтра 8. Таким образом иа выходе фильтра 6 выделяется огибающая- синфазной составляющей цифрового сигнала, передаваемог в спектре типовой группы АСП, а на выходе фильтра 8 нижних частот - огибающая квадратурной составляющей

В предлагаемом устройстве для декоди- Qрегулятора 10. Цикличность управлерования используется сумма огибающейкия регулятором 10 осуществляется с

синфазной Составляющей и части оги-помощью синхроимпульсов, подаваемых

бающей квадратурной составляющейна второй вход счетчика с выхода децифрового сигнала. Для этого сигналлителя 1 частоты. На вход делителя 1

с выхода фильтра 6 подается на второйсгчастоты поступают импульсы тактовой

вход сумматор 9, а на первый входчастоты с выхода блока 13. сумматора 9 подается сигнал с выхода В предлагаемом устройстве компендополнительного фильтра 8, прошедпшйсация межсимвольных искажений осущедискретный регулятор 10 уровня с циф-ствляется автоматически по рабочему

ровым управлением. На второй (управ- ляюпщй) вход регулятора 10 подается сигнал управления затуханием регулятора, формируемый с помощью коррелятора 17. Использование части огибающей квадратурной составляющей при декодировании цифрового сигнала АФМ ОБП позволяет существенно уменьшить межсимвольные искажения, возникающие в простых трактах АСП.

Демодулированный многопозиционный цифровой сигнал с выхода сумматора 9 подается на первый вход декодера 14,

5 вход блока 13 вьзделения тактовой частоты и второй вход блока 16. На выходе декодера 14 формируется двоичный цифровой сигнал, подаваемый на выход.

0 На выходе блока 13 формируется

тактовая частота, необходимая для работы декодера 14, которая подается на его второй вход.

На выходе блока 16 формируется

5 сигнал ошибки, который показывает насколько многопозиционный цифровой Сигнал на входе декодера 14 отличается от идеального .многопозиционного цифрового сигнала на первом входе

0 блока 16. Этот идеальный цифровой сигнал формируется из выходного двоичного сигнала с помощью последовательно включенных кодера 18 и фильтра 15. Сигнал ошибки с выхода блока

5 16, подаваемый на первый вход коррелятора 17, сравнивается с огибающей квадратурной составляющей цифрового сигнала, подаваемой на второй вход коррелятора 17. На выходе коррелятора 17 формируется управляющее напряжение, знак которого показывает, в какую сторону необходимо изменять затухание дискретного регулятора 10. Знак управляющего напряжения на выходе коррелятора 17 определяется с помощью компаратора 12 (нуль-компаратора). .Логические уровни с выхода компаратора 12 додаются на первый вход счетчика 11, управляющего работой

0

5

сигналу за счет обратной , проходящей через кодер 18, фильтр 15, блок 1.6, коррелятор 17, компаратор 12, счетчик 11 и регулятор 10. Поэтому даже при быстром переключении групповых трактов АСП, по которым осуществляется передача цифровых сигналов, достоверность приема остается высокой.

Формула изобретения

Приемник цифрового сигнала, содержащий блок автоматической регулировки усиления, последовательно соединенные блок в1еделения когерентного f5 колебания, демодулятор и фильтр нижних частот, блок выделения тактовой частоты, выход которого соединен с первым входом декодера, отличав- ю щ и и с я тем, что, с целью повы- 20 шения достоверности приема, введены последовательно соединенные фазовращатель, дополнительный демодулятор, дополнительный фильтр нижних частот, коррелятор, компаратор, счетчик, регу- 5

Составитель Н. Лазарева Редактор Л. Гратилло Техред А.Кравчук

Кор Под

901/61 Тираж 639

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

O

5 0 5

лятор уровня и сумматор, делитель частоты, последовательно соединенные кодер, фильтр и блок вычитания,причем выход блока автоматической регулировки усиления соединен с входом блока вьщеления когерентного колебания, вторым входом демодулятора и первым входом дополнительного демодулятора, второй вход которого соединен с выходом блока вьщеления когерентного колебания через фазовращатель, выход фильтра .нижних частот соединен с другим входом сумматора, выход которого JC.oeдинeн с входом блока вьщепе- ния тактовой частоты и вторыми входами декодера и блока вычитания,выход которого соединен с другим входом коррелятора, выход декодера соединен с первым входом кодера, выход блока выделения тактовой частоты соединен с вторым входом-кодера и через делитель частоты с другим входом счетчика, причем выход дополнительного фильтра нижних частот соединен с другим вхо- . дом регулятора уровня.

Корректор и. Муска Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации сигнала несущей частоты | 1984 |

|

SU1195467A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И УСТРАНЕНИЯ ФАЗОВОЙ НЕОДНОЗНАЧНОСТИ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2002 |

|

RU2232474C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И УСТРАНЕНИЯ ФАЗОВОЙ НЕОДНОЗНАЧНОСТИ СИГНАЛОВ СИСТЕМ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2010 |

|

RU2444849C2 |

| ЦИФРОВОЙ МОДЕМ | 2001 |

|

RU2218666C2 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Устройство синхронизации несущей частоты | 1985 |

|

SU1356249A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК МОДУЛИРОВАННЫХ СИГНАЛОВ СО СМЕЩЕНИЕМ (OQPSK) МНОГОКАНАЛЬНОЙ СИСТЕМЫ СВЯЗИ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2003 |

|

RU2254679C1 |

| Цифровая система связи с квадратурной модуляцией | 1989 |

|

SU1626411A1 |

Изобретение относится к -электросвязи. Цель изобретения - повышение достоверности приема. Приемник содержит делитель 1 частоты, блок 2 автоматической регулировки усиления, два демодулятора 3 и 5, блок 4 выделения (ВВ) когерентного колебания, двЗ фильтра 6 и 8 нижних частот, фазовращатель 7, сумматор 9, регулятор 10. уровня, счетчик 11, компаратор 12, БВ 13 тактовой частоты, декодер 14, фильтр 15, блок 16 вычитания,. коррелятор 17 и кодер 18. Цель достигается путем компенсации мехсимврльных искажений, которая осуществляется автоматически по рабочему сигналу за счет обратной связи, проходящей через кодер 18, фильтр 15, блок 16 вычитания, коррелятор 17, компаратор 12, счетчик 11 и регулятор 10. Даже при быстром переключении групповых трактов аналоговых систем передачи, по которым осуществляется передача ровых сигналов, достоверность приема остается высокой. 1 ил. сл с: ю ;о 00

| Данилов B.C | |||

| и др | |||

| Устройства преобразования сигналов передачи дан- йых | |||

| М.: Связь, 1979, с | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-01—Подача