Изобретение относится к электросвязи и может быть использовано в аппаратуре образования основного цифрового канала.

Целью изобретения является повышение помехоустойчивости передачи сигналов данных.

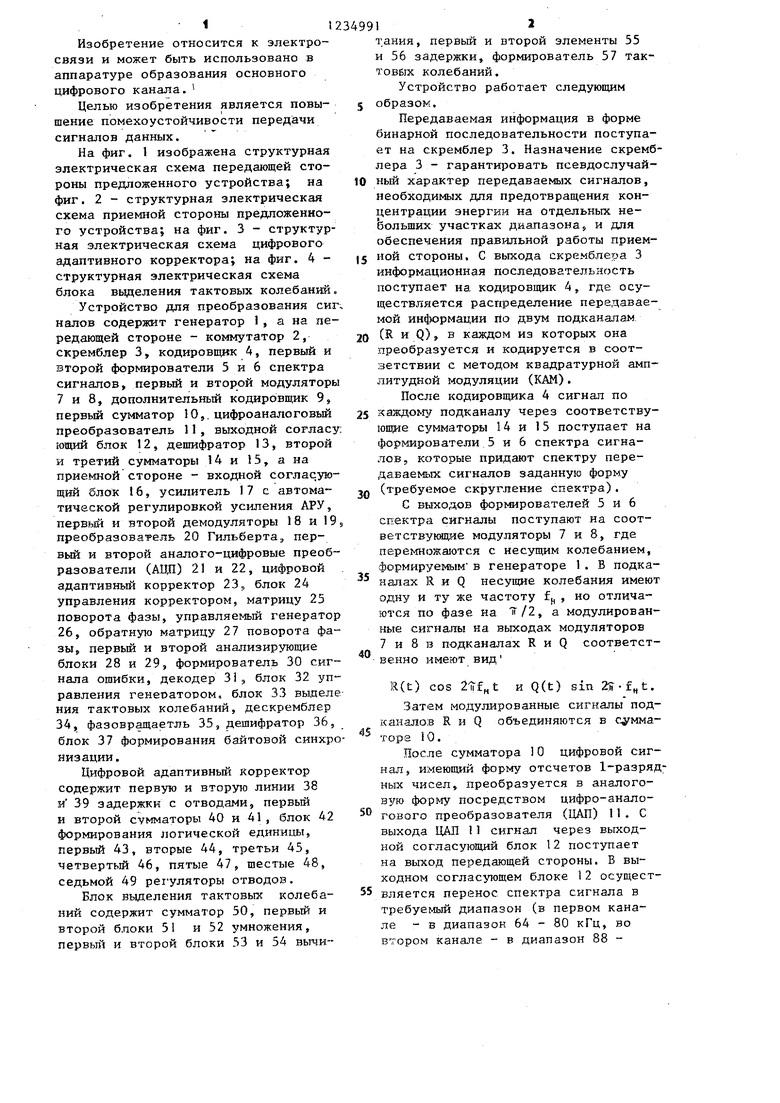

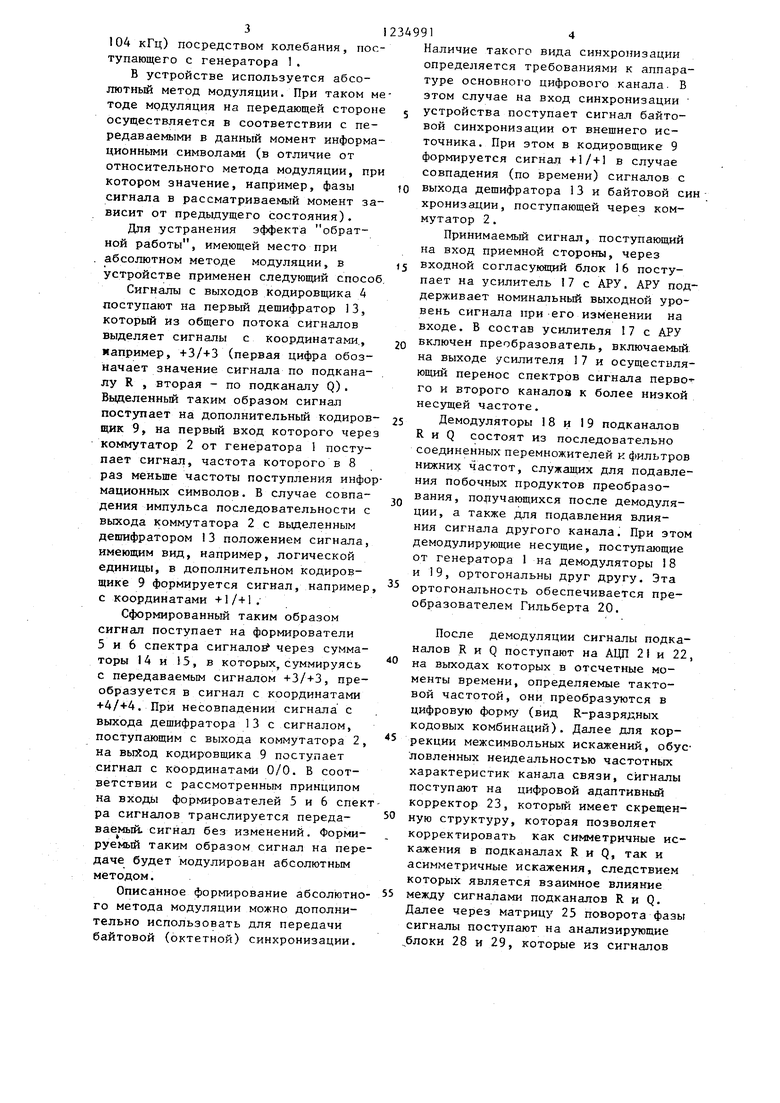

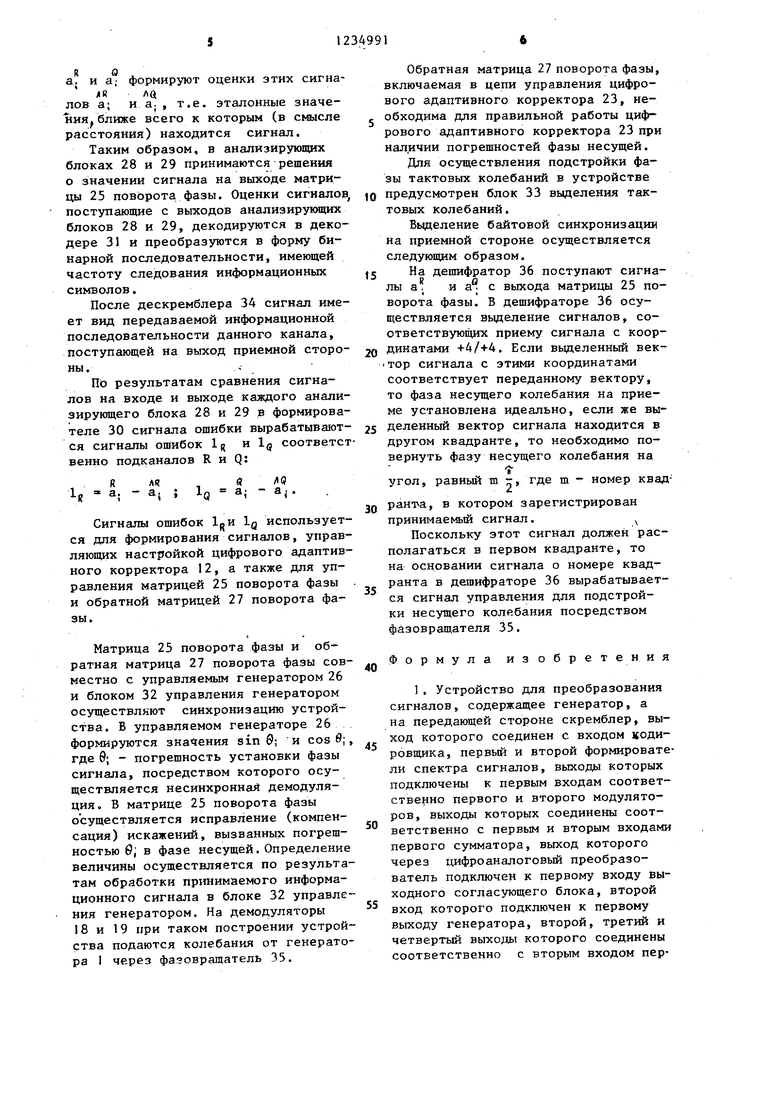

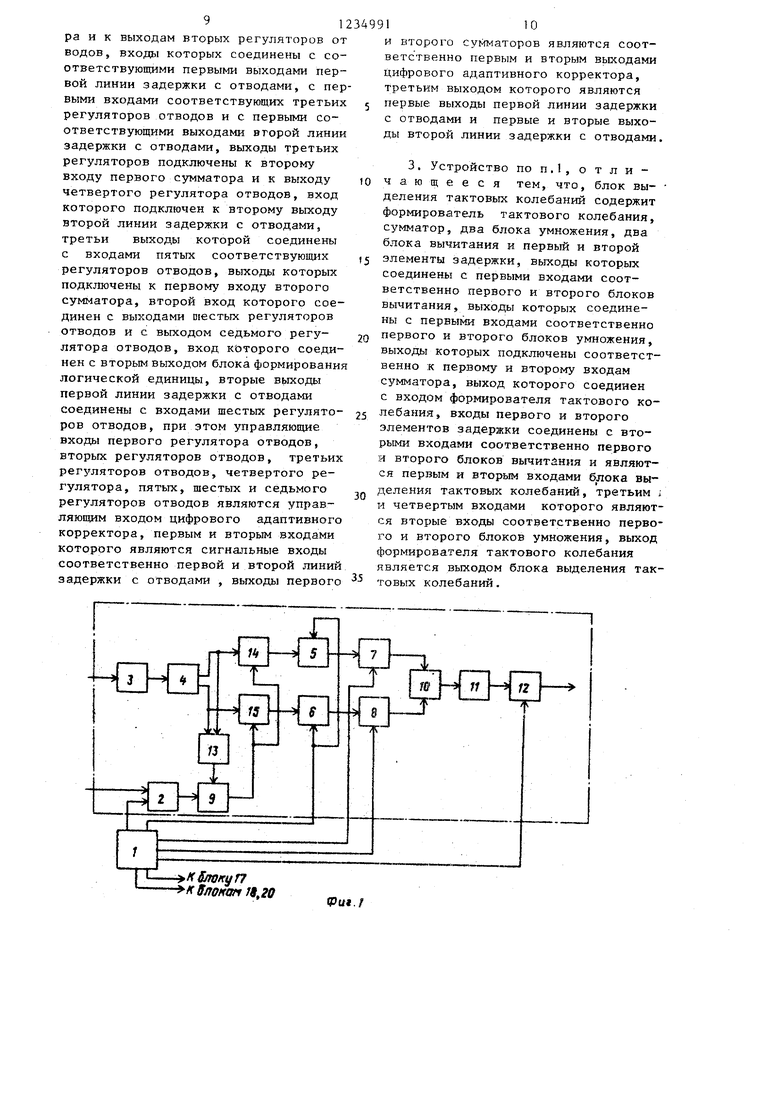

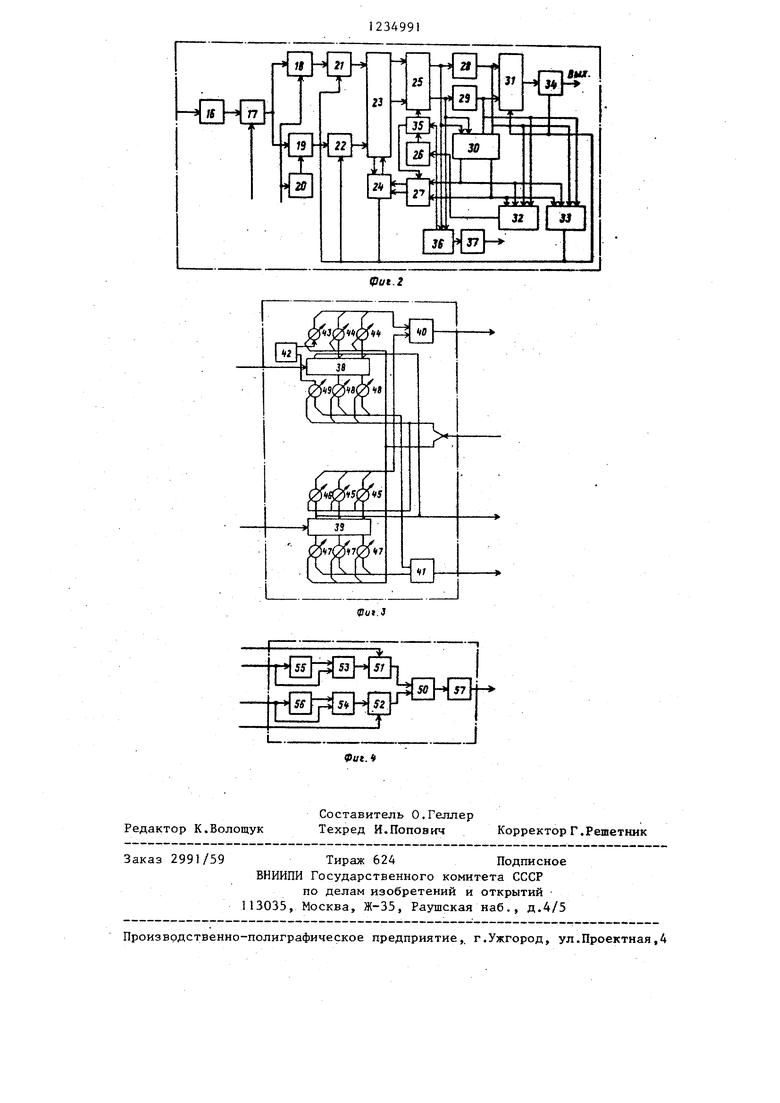

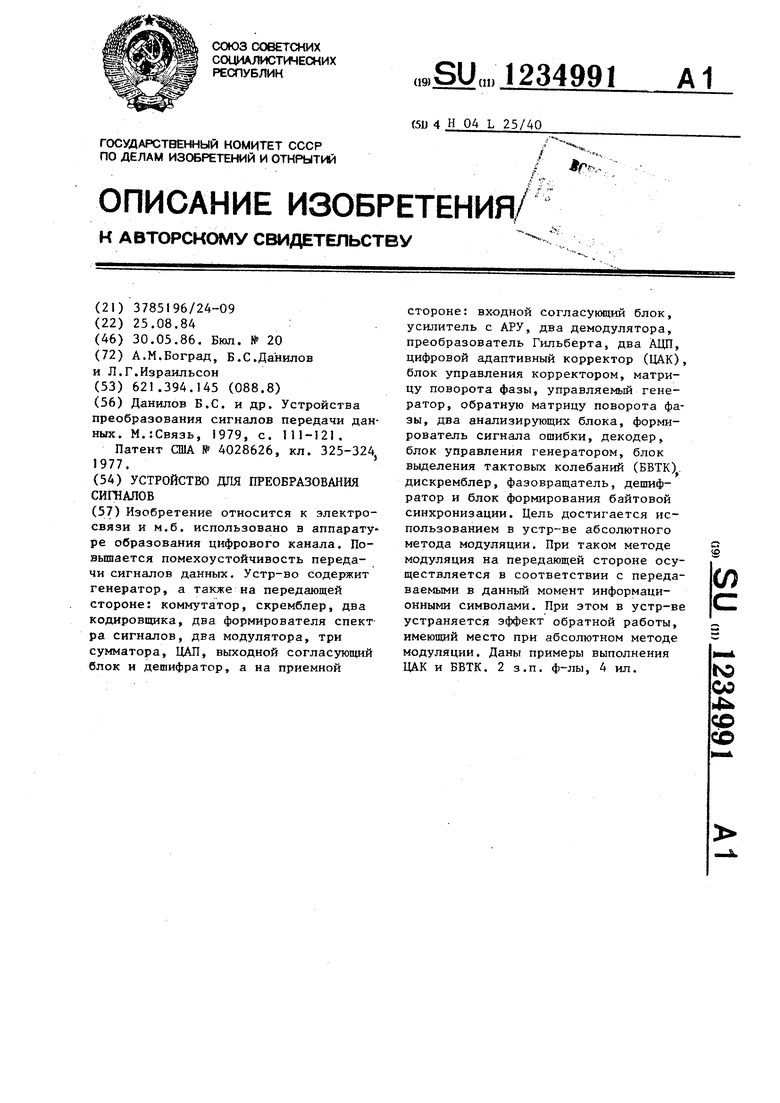

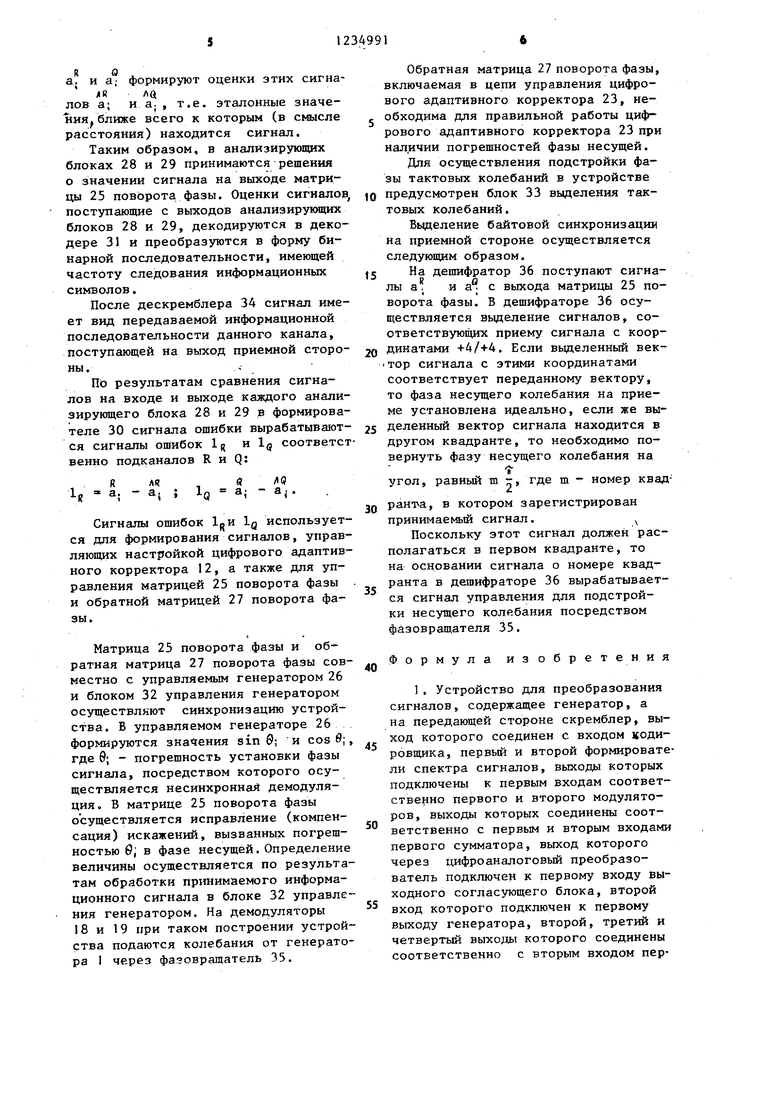

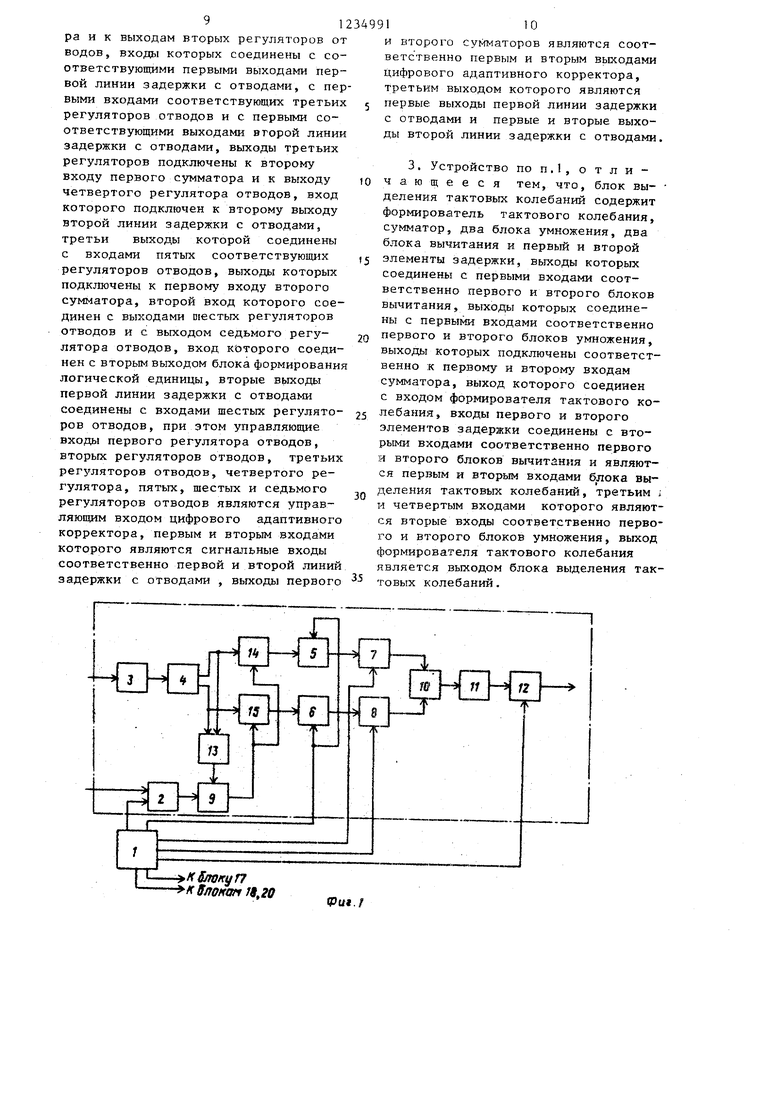

На фиг. 1 изображена структурная электрическая схема передающей стороны предложенного устройства; на фиг. 2 - структурная электрическая схема приемной стороны предложенного устройства; на фиг. 3 - структурная электрическая схема цифрового адаптивного корректора; на фиг. 4 - структурная электрическая схема блока вьщеления тактовых колебаний

Устройство для преобразования сиг налов содержит генератор 1, а на передающей стороне - коммутатор 2, скремблер 3, кодировщик 4, первый и второй формирователи 5 и 6 спектра сигналов, первый и второй модуляторы 7 и 8, дополнительный кодировщик 9, первый сумматор 50,. цифроаналоговый преобразователь 11, выходной согласу ющий блок 12, дешифратор 13, второй и третий сумматоры 14 и 15, а на приемной стороне - входной согласующий блок 16 5 усилитель 17 с автоматической регулировкой усиления АРУ, первый и второй демодуляторы 18 и 19 преобразова релъ 20 Гильберта„ первый и второй аналого-цифровые преобразователи (АЦП) 21 и 22, цифровой адаптивный корректор 23, блок 24 управления корректором, матрицу 25 поворота фазы, управляемый генератор 26, обратную матрицу 27 поворота фазы, первый и второй анализирующие блоки 28 и 29, формирователь 30 сигнала ошибки, декодер 31, блок 32 управления генератором, блок 33 выделения тактовых колебаний, дескремблер 34, фазовращаетль 35, дешифратор 36, блок 37 формирования байтовой синхронизации.

Цифровой адаптивный корректор содержит первую и вторую линии 38 и 39 задержки с отводами, первый и второй сумматоры 40 и 41, блок 42 формирования логической единицы, первый 43, вторые 44, третьи 45, четвертьй 46, пятые 47, шестые 48, седьмой 49 регуляторы отводов.

Блок выделения тактовых колебаний содержит сумматор 50, первый и второй блоки 51 и 52 умножения, первьп и второй блоки 53 и 54 вьгаитания, первый и второй элементы 55 и 56 задержки, формирователь 57 так- TOB6IX колебаний.

Устройство работает следующим

образок.

Передаваемая информация в форме бинарной последовательности поступает на скремблер 3. Назначение скремб- лера 3 - гарантировать псевдослучайный характер передаваемых сигналов, необходиьмх для предотвращения концентрации энергии на отдельных небольших участках диапазона, и для обеспечения правильной работы приемной стороны. С выхода скремблера 3 информационная последовательность поступает на кодировщик 4, где осуществляется распределение передаваемой ин4зормации rto двум подканалам

(Т и Q), в каждом из которых она злреобразуется и кодируется в соответствии с методом квадратурной амплитудной модуляции (КАМ).

После кодировщика 4 сигнал по

каждому; подканалу через соответствующие сумматоры I4 и 15 поступает на формирователи 5 и 6 спектра сигналов, которые придают спектру передаваемых сигналов заданную форму

(требуемое скругление спектра).

С выходов формирователей 5 и 6 спектра сигналы поступают на соот- ветствукйцие модуляторы 7 и 8, где перемножаются с несущим колебанием, формируемым в генераторе 1. В подканалах R и Q несущие колебания имеют одну и ту же частоту f, , но отличаются по фазе на , а модулированные сигнапЕЫ на вьпсодах модуляторов 7 и 8 в подканалах Кир соответст

венно имеют вид

R(t) cos и Q(t) sin .

Затем модулированные сигналы подканалов R и Q объединяются в с мматоре 10.

После сумматора 10 цифровой сигнал , имеющий форму отсчетов 1-разрядных чисел, преобразуется в аналого- зую форму посредством цифро-аналогового преобразователя (ЦАП) 11. С выхода ЦАП 1 сигнал через выходной согласующий блок 12 поступает на выход передающей стороны. В выходном согласующем блоке 12 осуществляется перенос спектра сигнала в требуемый диапазон (в первом канале - в диапазон 64 - 80 кГц, во втором канале - в диапазон 88 3

104 кГц) посредством колебания, поступающего с генератора 1.

В устройстве используется абсо- лютньй метод модуляции. При таком методе модуляция на передающей стороне осуществляется в соответствии с передаваемыми в данный момент информационными символами (в отличие от относительного метода модуляции, при котором значение, например, фазы сигнала в рассматриваемый момент зависит от предьщущего состояния).

Для устранения эффекта обратной работы, имеющей место при абсолютном методе модуляции, в устройстве применен следующий способ

Сигналы с выходов кодировщика А поступают на первый дешифратор 13, который из общего потока сигналов выделяет сигналы с координатами., например, +3/+3 (первая цифра обозначает значение сигнала по подкана- лу R , вторая - по подканалу Q). Выделенный таким образом сигнал поступает на дополнительный кодировщик 9, на первый вход которого через коммутатор 2 от генератора 1 поступает сигнал, частота которого в 8 раз меньше частоты поступления информационных символов. В случае совпадения импульса последовательности с выхода коммутатора 2 с выделенным дешифратором 13 положением сигнала, имеющим вид, например, логической единицы, в дополнительном кодировщике 9 формируется сигнал, например с координатами ,

Сформированный таким образом сигнал поступает на формирователи 5 и 6 спектра сигналов через сумматоры 14 и 15, в которых, суммируясь с передаваемым сигналом +3/+3, преобразуется в сигнал с координатами +4/+4. При несовпадении сигнала с выхода дешифратора 13 с сигналом, поступающим с выхода коммутатора 2, на вьпЖод кодировщика 9 поступает сигнал с координатами О/О. В соответствии с рассмотренным принципом на входы формирователей 5 и 6 спек ра сигналов транслируется передаваемый, сигнал без изменений. Формируемый таким образом сигнал на передаче будет модулирован абсолютным методом.

Описанное формирование абсолютного метода модуляции можно дополнительно использовать для передачи байтовой (октетной) синхронизации.

49914

Наличие такого вида синхронизации определяется требованиями к аппаратуре основного цифрового канала. В этом случае на вход синхронизации

5 устройства поступает сигнал байтовой синхронизации от внешнего источника. При этом в кодировщике 9 формируется сигнал +1/+1 в случае совпадения (по времени) сигналов с

0 выхода дешифратора 13 и байтовой син хронизации, поступающей через коммутатор 2.

Принимаемый сигнал, поступающий на вход приемной стороны, через

5 входной согласующий блок 16 поступает на усилитель 17 с АРУ. АРУ поддерживает номинальный выходной уровень сигнала при его изменении на входе. В состав усилителя 17 с АРУ

Q включен преобразователь, включаемый, на выходе усилителя 17 и осуществляющий перенос спектров сигнала перво- го и второго каналов к более низкой несущей частоте.

5 Демодуляторы 18 и 19 подканалов R и Q состоят из последовательно соединенных перемножителей к фильтров нижних частот, служащих для подавления побочных продуктов преобразо- - вания, получающихся после демодуляции, а также для подавления влияния сигнала другого канала. При этом демодулирующие несущие, поступающие от генератора 1 на демодуляторы 18 и 19, ортогональны друг другу. Эта

ортогональность обеспечивается преобразователем Гильберта 20.

После демодуляции сигналы подканалов R и Q поступают на АЦП 21 и 22, на выходах которых в отсчетные моменты времени, определяемые тактовой частотой, они преобразуются в цифровую форму (вид R-разрядных кодовых комбинаций). Далее для коррекцИи межсимвольных искажений, обусловленных неидеальностью частотньк характеристик канала связи, сигналы поступают на цифровой адаптивный корректор 23, который имеет скрещенную структуру, которая позволяет

корректировать как сиь(Метричные искажения в подканалах R и Q, так и асимметричные искажения, следствием которых является взаимное влияние

между сигналами подканалов R и Q. Далее через матрицу 25 поворота фазы сигналы поступают на анализирующие блокн 28 и 29, которые из сигналов

R о a, и Я; формируют оценки этих сигна

Аи ЛС1

лов а; ив;, т.е. эталонные значе- tiHH ближе всего к которым (в смысле расстояния) находится сигнал.

Таким образом, в анализирующих блоках 28 и 29 принимаются решения о значении сигнала на выходе матрицы 25 поворота фазы. Оценки сигналов поступающие с выходов анализирующих блоков 28 и 29, декодируются в декодере 31 и преобразуются в форму бинарной последовательности, имеющей частоту следования информационных символов.

После дескремблера 34 сигнал имеет вид передаваемой информационной последовательности данного канала, поступающей на выход приемной стороны.

По результатам сравнения сигналов на входе и выходе каждого анализирующего блока 28 и 29 в формирователе 30 сигнала ошибки вырабатываются сигналы ошибок 1ц и 1 соответственно подканалов Кир:

R А« а. - а,

и

У((

LQ а; - aj

Сигналы ошибок Ig используется для формирования сигналов, управляющих настройкой цифрового адаптивного корректора 12, а также для управления матрицей 25 поворота фазы и обратной матрицей 27 поворота фазы.

Матрица 25 поворота фазы и обратная матрица 27 поворота фазы совместно с управляемым генератором 26 и блоком 32 управления генератором осуществляют синхронизацию устройства. В управляемом генераторе 26 формируются значения sin 0; и cos б;, где 0; - погрешность установки фазы сигнала, посредством которого осуществляется несинхронна демодуляция . В матрице 25 поворота фазы осуществляется исправление (компенсация) искажений, вызванньпс погрешностью 0; в фазе несущей. Определение величины осуществляется по результатам обработки принимаемого информационного сигнала в блоке 32 управления генератором. На демодуляторы 18 и 19 при таком построении устройства подаются колебания от генератора 1 через фазовращатель 35.

Обратная матрица 27 поворота фазы, включаемая в цепи управления цифрового адаптивного корректора 23, не- обходима для правильной работы цифрового адаптивного корректора 23 при наличии погрешностей фазы несущей.

Для осуществления подстройки фазы тактовых колебаний в устройстве предусмотрен блок 33 выделения тактовых колебаний.

Вьщеление байтовой синхронизации на приемной стороне осуществляется следующим образом.

На дешифратор 36 поступают сигналы а . и а, с выхода матрицы 25 поворота фазы. В дешифраторе 36 осуществляется выделение сигналов, соответствующих приему сигнала с коор- динатами +4/+4. Если выделенный век- Тор сигИала с этими координатами соответствует переданному вектору, то фаза несущего колебания на приеме установлена идеально, если же вы- деленный вектор сигнала находится в другом квадранте, то необходимо повернуть фазу несущего колебания на

Т УГОЛ, равньй m -, где m - номер квадранта, в котором зарегистрирован принимаемый сигнал.

Поскольку этот сигнал должен располагаться в первом квадранте, то на основании сигнала о номере квадранта в дешифраторе 36 вырабатывается сигнал управления для подстройки несущего колебания посредством фазовращателя 35.

Формула изобретения

1, Устройство для преобразования сигналов, содержащее генератор, а на передающей стороне скремблер, выход которого соединен с входом кодировщика, первый и второй формирователи спектра сигналов, выходы которых подключены к первым входам соответственно первого и второго модуляторов, выходы которых соединены соответственно с первым и вторым входами первого сумматора, выход которого через цифроаналоговый преобразователь подключен к первому входу выходного согласующего блока, второй вход которого подключен к первому выходу генератора, второй, третий и четвертый выходы которого соединены соответственно с вторым входом перого модулятора, с вторым входом второго модулятора и с вторыми объе иненными входами первого и второго ормирователей спектра сигналов, а на приемной стороне - входной согласующий блок, выход которого соедиен с первым входом усилителя с автоматической регулировкой усиления, выход которого соединен с первыми входами первого и второго демодуляторов, выходы которых подключены к первым входам соответственно первого и второго аналото-цифровых преоб- разователей, выходы которых соединены соответственно с первым и вторым входами цифрового адаптивного корректора, первый и второй выходы которого подключены соответственно к первому и второму входам матрицы поворота фазы, первый выход которой соединен с входом первого анализирующего блока и с первым входом формирователя сигнала ошибки, второй вход которого подключен к второму выходу матрицы поворота фазы и к входу второго анализирующего блока, выход которого соединен с третьим входом формирователя сигнала ошибки, с первым входом блока вьоделения тактовых колебаний, с первым входом блока управления генератором и с первым входом декодера, второй вход которого подключен к выходу первого анаизирующего блока, к четьертому входу формирователя сигнала ошибки, к второму входу блока выделения тактовых колебаний и к второму входу блока управления генератором, третий четвертый входы которого соединены соответственно с третьим и четвертым входами блока выделения тактовых колебаний, соответственно с первым и вторым выходами формировате я сигнала ошибки и соответственно . с первым и вторым входами обратной матрицы поворота фазы, первый и второй вьжоды которой подключены соответственно к первому и второму входам блока управления корректором, выход которого соединен с управляющим входом цифрового адаптивного корректора, третий выход которого соединен с третьим входом блока управления корректором, тактовый вход которого подключен к выходу блока выделения тактовых колебаний, к вторым входам первого и второго аналого-цифровых преобразователей, к тактовому входу дескремблера и к тактовому входу декодера, выход которого соединен с сигнальным входом дескремблера, выход блока управления генератором подключен к входу управляе- мого генератора, второй вход второго демодулятора подключен к выходу преобразователя Гильберта, вход которого соединен с вторым входом первого демодулятора и с пятым выходом

генератора, шестой выход которого соединен с вторым входом усилителя с автоматической регулировкой усиления, отличающееся тем, что, с целью повьш1ения помехоустойчивости

передачи сигналов данных, введены на передающей стороне втор ой и третий сумматоры, дешифратор, дополнительный кодировщик и коммутатор, выход которого соединен с первым входом

дополнительного кодировщика, второй вход которого подключен к выходу дешифратора, первый и второй входы которого подключены соответственно к первому и второму выходам кодировщика и к первым входам соответственно второго и третьего сумматоров, вторые входы которых соединены с выходом дополнительного кодировщика, выходы второго и третьего сумматброь соединены с вторыми входами соответственно первого и второго формирователей спектра сигналов, седьмой выход генератора соединен с первым BXI дом коммутатора, а на приемной стс. роне введены фазовращатель, дешифратор и блок формирования байтовой синхронизации, вход которого подключен к первому выходу дешифратора, второй выход которого соединен с первым входом фазовращателя, первый выход которого соединен с третьим входом матрицы поворота фазы, первый и второй выходы которой соединены соответственно с первым и вторым входами дешифратора, выход управляемого генератора соединен с вторым входом фазовращателя, второй выход которого подключен к третьему входу обратной матрицы поворота фазы. 2, Устройство по П.1, о т л и ч а ю щ е е с я тем, что цифровой адаптивный корректор содержит перву и вторую линии задержки с отводами, регуляторы отводов, первый и второй сумматоры и блок формирования логической единицы, первый выход которого соединен с входом первого регулятора отводов, выход которого подключен к первому входу первого суммато

pa и к выходам вторых регуляторов от водов, входы которых соединены с соответствующими первыми выходами первой линии задержки с отводами, с первыми входами соответствующих третьих регуляторов отводов и с первыми соответствующими выходами второй линии задержки с отводами, выходы третьих регуляторов подключены к второму входу первого сумматора и к выходу четвертого регулятора отводов, вход которого подключен к второму выходу второй линии задержки с отводами, третьи выходы которой соединены с входами пятых соответствующих регуляторов отводов, выходы которых подключены к первому входу второго сумматора, второй вход которого соединен с выходами DiecTbDc регуляторов отводов и с выходом седьмого регулятора отводов, вход которого соединен с вторым выходом блока формирования логической единицы, вторые вьпсоды первой линии задержки с отводами соединены с входами шестых регуляторов отводов, при этом управляющие входы первого регулятора отводов, вторых регуляторов отводов, третьих регуляторов отводов, четвертого регулятора, пятых, шестых и седьмого регуляторов отводов являются управляющим входом цифрового адаптивного корректора, первым и вторым входами которого являются сигнальные входы соответственно первой и второй линий задержки с отводами , выходы первого

L.- KSffOKuT 9 К Илонап 79,гО

tpui.f

0

5

0

5

0

И второго сумматоров являются соответственно первым и вторым вьгходами цифрового адаптивного корректора, Третьим выходом которого являются первые выходы первой линии задержки с отводами и первые и вторые выходы второй линии задержки с отводами.

3. Устройство по п.1, о т л и - чающееся тем, что, блок вы- - деления тактовых колебаний содержит формирователь тактового колебания, сумматор, два блока умножения, два блока вычитания и первый и второй элементы задержки, выходы которых соединены с первыми входами соответственно первого и второго блоков вычитания, выходы которых соединены с первыми входами соответственно первого и второго блоков умножения, выходы которых подключены соответственно к первому и второму входам сумматора, выход которого соединен с входом формирователя тактового колебания, входы первого и второго элементов задержки соединены с вто- рьп-ш входами соответственно первого и второго блоков вычитания и являются первым и вторым входами блока выделения тактовых колебаний, третьим i и четвертым входами которого являются вторые входы соответственно первого и второго блоков умножения, выход формирователя тактового колебания является выходом блока выделения тактовых колебаний.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с адаптивной коррекцией межсимвольной интерференции | 1979 |

|

SU866757A1 |

| Двухканальное устройство приема сигналов данных | 1986 |

|

SU1415451A1 |

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| Адаптивный приемник сигналов данных | 1989 |

|

SU1672580A1 |

| Адаптивный корректор | 1979 |

|

SU866756A2 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1981 |

|

SU951724A1 |

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Устройство приема дискретных сигналов | 1984 |

|

SU1223371A1 |

| Устройство для приема сигналов с парциальным откликом | 1983 |

|

SU1117855A1 |

Изобретение относится к электросвязи и м.б. использовано в аппаратуре образования цифрового канала. Повышается помехоустойчивость передачи сигналов данных. Устр-во содержит генератор, а также на передающей стороне: коммутатор, скремблер, два кодировщика, два формирователя спектра сигналов, два модулятора, три сумматора, ЦАП, выходной согласующий блок и дешифратор, а на приемной стороне: входной согласующий блок, усилитель с АРУ, два демодулятора, преобразователь Гильберта, два АЦП, цифровой адаптивный корректор (ЦАК), блок управления корректором, матрицу поворота фазы, управляемый генератор, обратную матрицу поворота фазы, два анализирующих блока, формирователь сигнала ошибки, декодер, блок управления генератором, блок выделения тактовых колебаний (ББТК). дискремблер, фазовращатель, дешифратор и блок формирования байтовой синхронизации. Цель достигается использованием в устр-ве абсолютного метода модуляции. При таком методе модуляция на передающей стороне осуществляется в соответствии с передаваемыми в данный момент информационными символами. При этом в устр-ве устраняется эффект обратной работы, имеющий место при абсолютном методе модуляции. Даны примеры выполнения ЦАК и БВТК. 2 з.п. ф-лы, 4 ил. (Л ю оо 4iik СО CD

| Данилов Б.С | |||

| и др | |||

| Устройства преобразования сигналов передачи данных | |||

| М.:Свяэь, 1979, с | |||

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Патент США № 4028626, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

Авторы

Даты

1986-05-30—Публикация

1984-08-25—Подача