держки,причем вход делителя частоты и вы- но первым вхолом и выходом блока опреде.ход коммутатора является соответствен1195467

ления скачка фазы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации несущей частоты | 1985 |

|

SU1356249A1 |

| Устройство для компенсации дрожания фазы сигнала в системах передачи данных | 1985 |

|

SU1243135A1 |

| Устройство для полосовой адаптивной коррекции сигналов относительной фазовой модуляции | 1982 |

|

SU1100736A1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ НЕСУЩЕЙ ЧАСТОТЫ ДЕМОДУЛЯТОРА СИГНАЛОВ С ШЕСТНАДЦАТИПОЗИЦИОННОЙ АМПЛИТУДНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2013 |

|

RU2550548C2 |

| Устройство для анализа спектра радиосигнала | 1984 |

|

SU1213430A1 |

| Цифровое устройство фазовой синхронизации | 1984 |

|

SU1225034A1 |

| Автокорреляционный демодулятор сигналов с фазоразностной модуляцией первого порядка | 1987 |

|

SU1425869A1 |

| АНАЛИЗАТОР ПЛОТНОСТИ ВЕРОЯТНОСТИ ФАЗЫ СИГНАЛА | 2006 |

|

RU2313101C1 |

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛА | 2016 |

|

RU2626332C1 |

УСТРОЙСТВО СИНХРОНИЗАЦИИ СИГНАЛА НЕСУЩЕЙ ЧАСТОТЫ, содержащее, объединенные по входу устройства первый блок выборки и хранения сигнала, блок вьщеления сигнала тактовой частоты и преобразователь по Гильберту, выход которого, подключен к первому входу второго блока выборки и хранения сигнала, к второму входу которого, а также к второму входу первого блока выборки и хранения сигнала подключен выход блока выделения сигнала тактовой частоты, при этом выходы первого и второго ,блоков выборки и хранения сигналов, а также вькоды блока памяти синусов-косинусов подключены к входам предварительного демодулятора, выходы которого подключены к входам решающего блока, первый и второй выходы которого являются выходами устройства, а третий выход через усредняющий блок подключен к входу накопительного элемента, отличающееся тем, что, с целью повышения помехоустойчивости при скачкообразном изменении фазы колебания несущей частоты, введены сумматор, вычислитель квадратической ошибки и блок определения скачка фазы, к первому и второму входам которого подключены соответственно выход блока выделения сигнала тактовой частоты и выход вычислителя среднеквадратической ошибки, к входам которого подключены выходы решающего блока и предварительного демодулятора, при этом к входу блока памяти синусов-косинусов подключен выход сумматора, к первому и второму входам которого подключены выходы накопительного элемента и блока определения скачка фазы, содержащего S элемент памяти дискретных значений фаз, выходы которого подключены к (Л первой группе входов коммутатора, к второй группе входов которого подключены выходы счетчика, при этом выход делителя частоты ;подключен к первому входу накопительного сумматора непосредственно и через элемент задержки к первому входу элемента совпадения, выход которого :С подключен к входу счетчика, а к втоСП рому входу элемента совпадения подN b ключен выход компаратора, к первому о: и второму входам которого подключе | ны соответственно выходы порогового элемента и накопительного сумматора вьшолненного в виде последовательно соединенных многоотводной линии задержки, многовходового cywiarbpa и блока выборки и хранения сигнала, второй вход и выход которого является соответственно первым входом и выходом накопительного сумматора, вторым входом которого и вторьш входом блока определения скачка фазы является вход многоотводной линии за

Изобретение относится к электросвязи и может использоваться для выделения колебания несущей частоты в системах передачи данных с многопозиционными сигналами фазовой модуляцией ОФМ, амплитудно-фазовой модуляцией АФМ, амплитудной модуляцией и одной боковой полосой AM ОБП.

Цель изобретения - повьшение помехоустойчивости при скачкообразном изменении фазы колебаний несущей частоты.

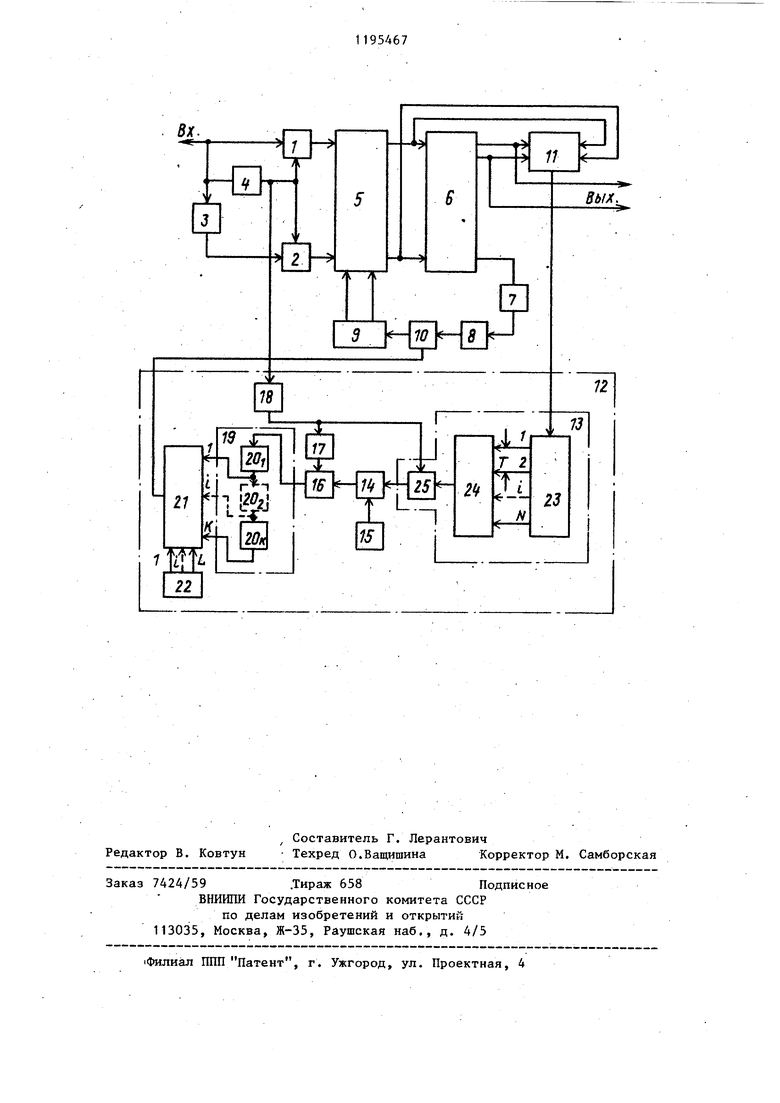

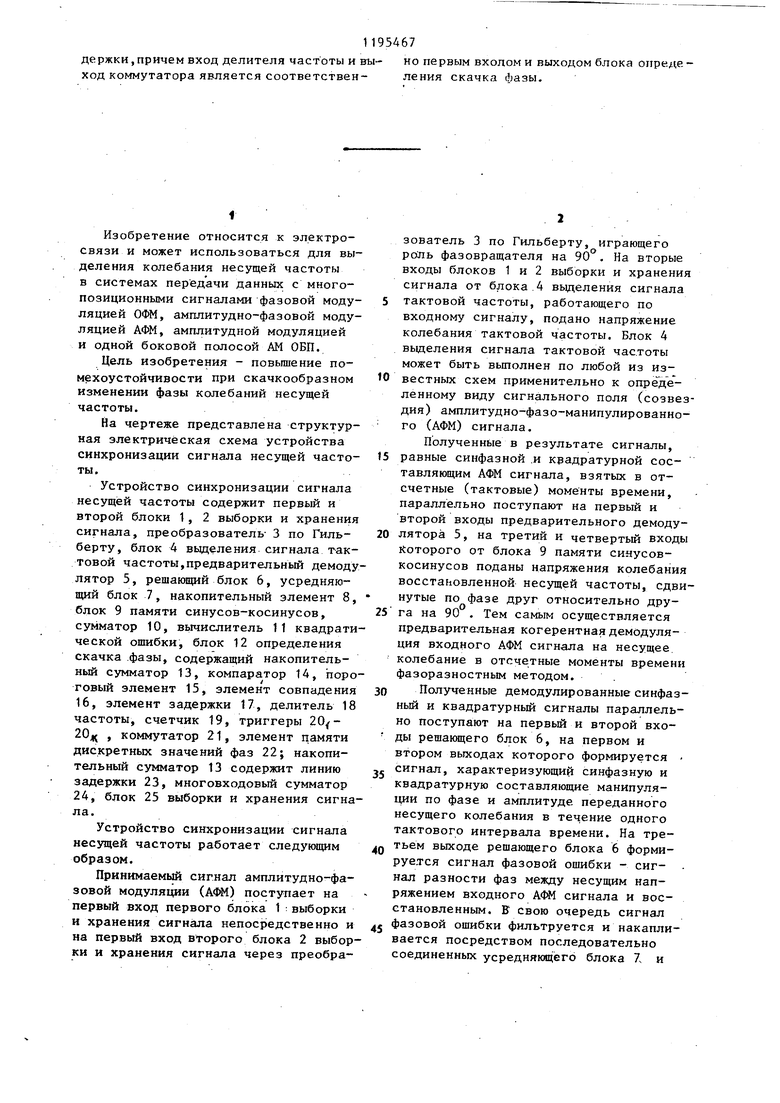

На чертеже представлена структурная электрическая схема устройства синхронизации сигнала несущей частоты.

Устройство синхронизации сигнала несущей частоты содержит первый и второй блоки 1, 2 выборки и хранения сигнала, преобразователь- 3 по Гильберту, блок 4 вьщеления сигнала тактовой частоты,предварительный демодулятор 5, решающий блок 6, усредняющий блок 7, накопительный элемент 8, блок 9 памяти синусов-косинусов, сумматор 10, вь1числитель 11 квадратической ошибки, блок 12 определения скачка .фазы, содержащий накопительный сумматор 13, компаратор 14, пороговый элемент 15, элемент совпадения 16, элемент задержки 17, делитель 18 частоты, счетчик 19, триггеры , коммутатор 21, элемент памяти дискретных значений фаз 22; накопительный сумматор 13 содержит линию задержки 23, многовходовый сумматор 24, блок 25 выборки и хранения сигнала.

Устройство синхронизации сигнала несущей частоты работает следующим образом.

Принимаемый сигнал амплитудно-фазовой модуляции (АФМ) поступает на первый вход первого блока 1 : выборки и хранения сигнала непосредственно и на первый вход второго блока 2 выборки и хранения сигнала через преобразователь 3 по Гильберту, играющего роль фазовращателя на 90. На вторые входы блоков 1 и 2 выборки и хранения сигнала от блока.4 выделения сигнала

тактовой частоты, работающего по входному сигналу, подано напряжение колебания тактовой частоты. Блок 4 вьщеления сигнала тактовой частоты может быть вьшолнен по любой из известных схем применительно к опрёделенному виду сигнального поля (созвездия) амплитудно-фазо-манипулированного (АФМ) сигнала.

Полученные в результате сигналы,

равные синфазной .и квадратурной составляющим АФМ сигнала, взятых в отсчетные (тактовые) моменты времени, параллельно поступают на первый и второй входы предварительного демодулятора 5, на третий и четвертый входы Которого от блока 9 памяти синусовкосинусов поданы напряжения колебания восстановленной несущей частоты, сдвинутые по фазе друг относительно друга на 90 . Тем самым осуществляется предварительная когерентная демодуляция входного АФМ сигнала на несущее, колебание в отсчетные моменты времени фазоразностным методом. .

Полученные демодулированные синфазньй и квадратурный сигналы параллельно поступают на первый и второй входы решающего блок 6, на первом и втором выходах которого формируется

сигнал, характеризующий синфазную и квадратурную составляющие манипуляции по фазе и амплитуде переданного несущего колебания в течение одного тактового интервала времени. На третьем выходе решающего блока 6 формируется сигнал фазовой ошибки - сиг- . нал разности фаз между несущим напряжением входного сигнала и восстановленным. Е свою очередь сигнал

фазовой ошибки фильтруется и накапливается посредством последовательно соединенных усредняющего блока 7, и

накопительного элемента 8, состоящего из последовательно соединенных линий задержки и сумматора.

Отфильтрованный и накопительный сигнал фазовой ошибки поступает на первый вход сумматора 10, на второй вход которого от блока 12 определения скачка фазы подается сигнал оценки скачкообразного изменения фазы колебания несущей частоты в кангше связи.

Для получения сигнала оценки скачка фазы синфазный и квадратурный сигналы на первом и втором выходах решающего блока 6, характеризующие манипуляцию по фазе и амплитуде переданного несущего колебания, поступают на первые и вторые входы вычислителя ,11 квадратической ошибки, на третий и четвертый входы которого подаются демодулированные синфазный и квадратурный сигналы с первого и второго выходов предварительного демодулятора 5. Вычислитель 11 квадратической ошибки - устройство, определяющее мгновенную мощность суммарной помехи на входе решающего блока 6.

Сигнал с выхода вычислителя 11 квадратической ошибки поступает на вход блока 12 определения скачка фазы - на вход многоотводной линии задержки 23 накопительного сумматора 13. Длина многоотводной линии задержки 23 равна ft-Т . Сигналы с вькодов отводов многоотводной линии задержки 23, взятые через тактовые интервалы времени Т, объединены с помощью многовходового ( N - входового) сумматора 24. Полученный суммарный сигнал поступает на первый вход блока 25 выборки и хранения сигнала, на второй вход которого через делитель 18 частоты на N поступает сигнал с выхода блока 4 вьщеления сигнала тактовой частоты. Блок 5 выборки, и хранения сигнала представляет собой устройство, стробирующее суммарный сигнал в НТ моменты времени и запоминающее его отсчетные значения на длительности интервала времени, равного N-T .

Накопленньй сигнал с выхода блока 25 выборки и хранения сигнала, являющийся выходом накопительного сумматора 13,поступает на второй вход компаратора 14, на первый вход которого

подано напряжение с выхода порогового элемента 15. Если напряжение сигнала на выходе накопительного сумматора 13 превышает пороговое (неверна оценка скачка фазы несущего колебания) на выходе компаратора 14 формируется уровень 1 на М-Т интервале времени, в противном случае (скачок фазы несущего колебания оценен верно) - уровень О.

Полученный сигнал подается на второй вход злемента совпадения 16, который открывает его (либо закрывает) для прохождения импульса,

поступающего с выхода делителя 1C частоты, через элемент задержки 17. Элемент задержки 17 необходим для временного согласования сигналов, поступающих на входы элемента совпадения 16. При этом постоянная

времени элемента задержки 17 С намного меньше N-T интервала времени () .

Сигнал с выхода элемента совпадения 16 поступает на вход счетчика 19 и управляет его состоянием. Счетчик 19 состоит из К последовательного соединенных триггеров 20, сигналы

с выходов которых поступают на вторую группу входов коммутатора 21. На первую группу входов коммутатора 21 поступают сигналы с соответствующих выходов элемента памяти дискретных значений фаз 22. При этом количество дискретных значений фаз I, связано с длиной счетчика 19 (количеством триггеров К) следующим соотношением h 2 .

Тем самым, на выходе коммутатора 21, являющимся выходом блока 12 определения скачка фазы, формируется сигнал оценки скачка фазы путем дешифрирования состояния счетчика 19. Сигнал оценки скачка фазы поступает на второй вход сумматора 10, результирующий суммарный сигнал на выходе которого подается на вход блока 9 памяти синусов-косинусов. Блок 9 памяти синусов-косинусов ставит в соответствие сигналу, поступающему на еГо вход, сигналы, равные функции синуса восстановленного несущего колебания на первом выходе, и косинуса на втором, необходимые для

когерентной предварительной демодуляции входного сигнала.

| Устройство фазирования | 1979 |

|

SU788410A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ приготовления вакцин из бактерий | 1924 |

|

SU4174A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-30—Публикация

1984-04-11—Подача