тор 2 включает в себя (фиг.2) п триг геров 22, где п - разрядность числа, считываемого из блока 1, п элементов И 23 первой группы, п элементов И 24 второй группы, п элементов И 25 трет ей группы, п-1 элементов И 26 четвертой группы, п-1 элементов И 27 пятой группы, rpyitny из п элементов ИЛИ 28, первый и второй элементы

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки результатов, получаемых в мно- годатчиковых экспериментах ядерной физики (МЭЯФ).

Цель изобретения - повышение быстродействия.

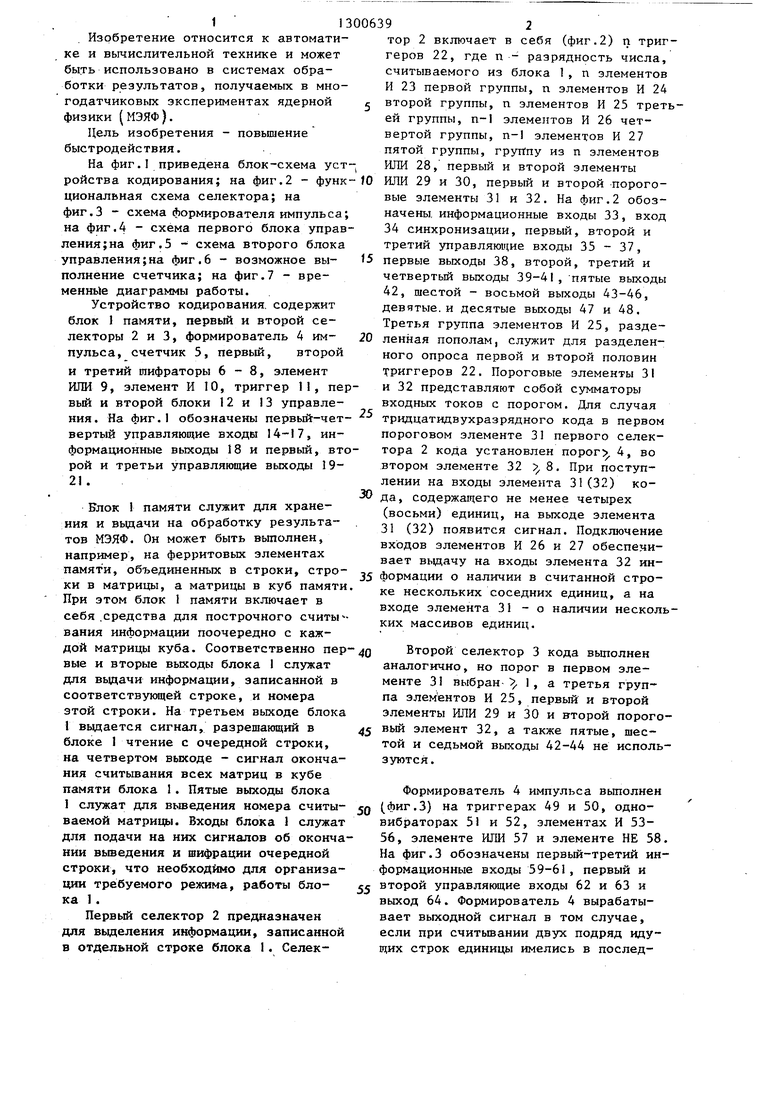

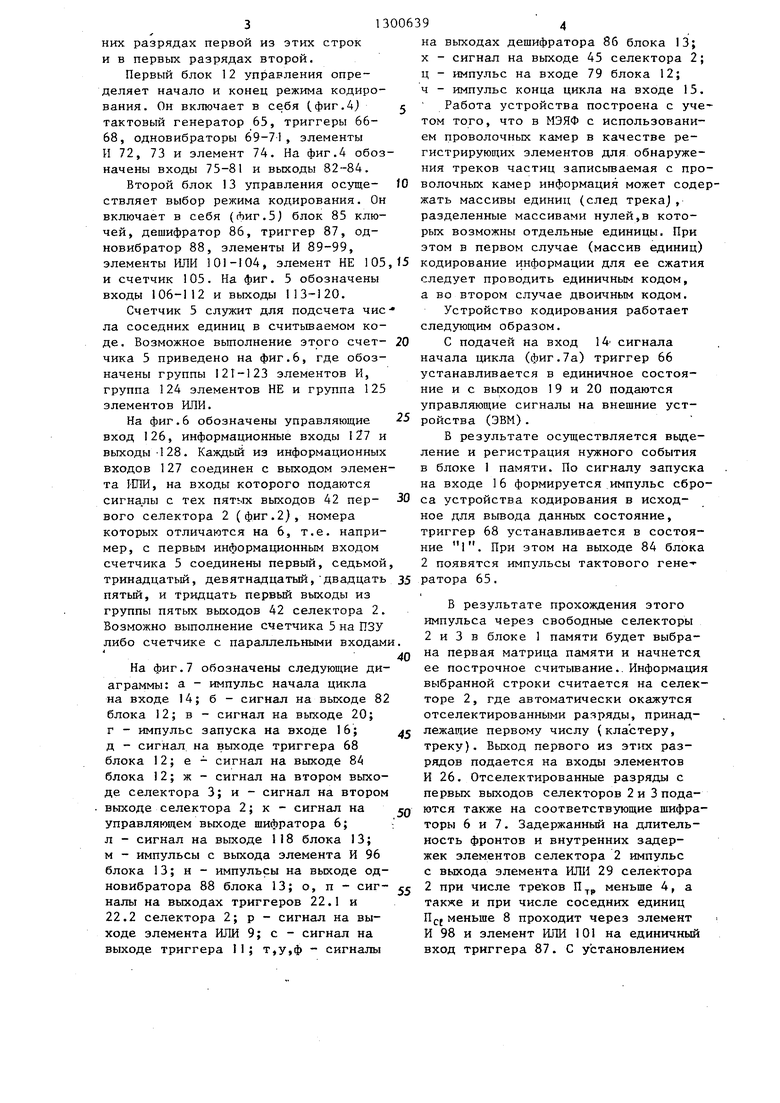

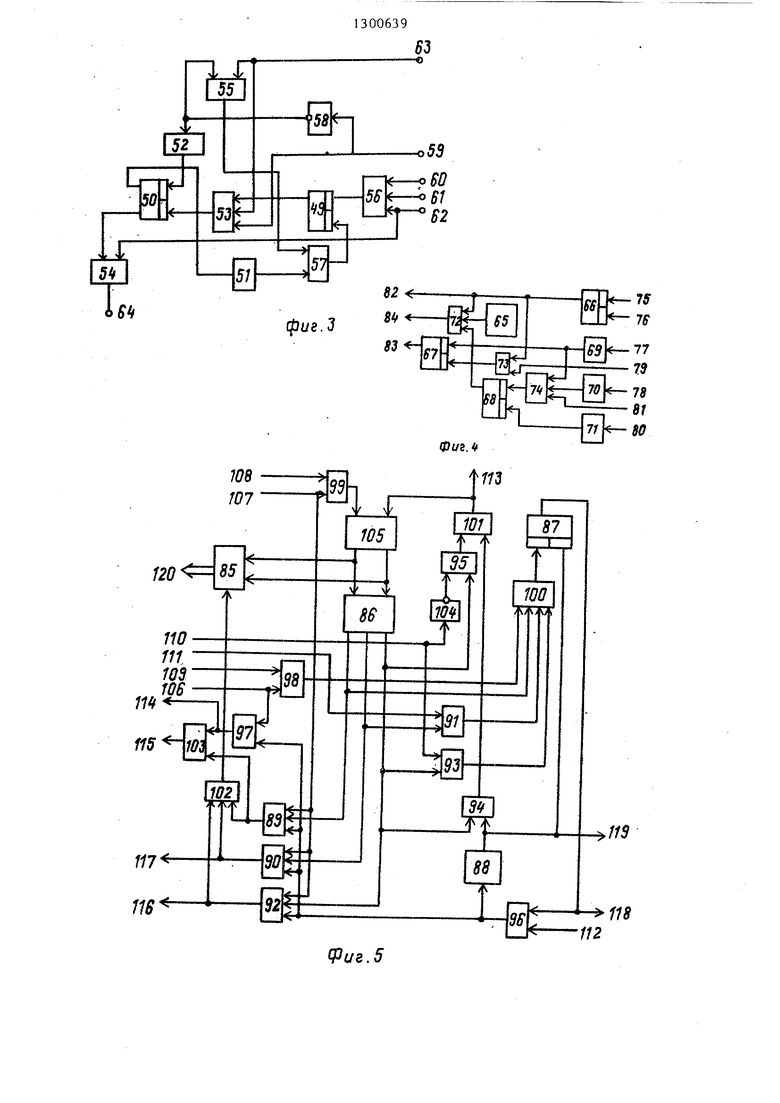

На фиг.1 приведена блок-схема устройства кодирования; на фиг.2 - функ-10 ИЛИ 29 и 30, первый и второй порого- ционалвная схема селектора; на вые элементы 31 и 32. На фиг.2 обоз- фиг. 3 - схема формирователя импульса; начены, информационные входы 33, вход на фиг.4 - схема первого блока управ- 34 синхронизации, первый, второй и

третий управляющие входы 35 - 37, 15 первые выходы 38, второй, третий и четвертый выходы 39-41, пятые выходы 42, шестой - восьмой выходы 43-46, девятые, и десятые выходы 47 и 48. Третья группа элементов И 25, разде- 20 ленная пополам, служит для разделенного опроса первой и второй половин триггеров 22. Пороговые элементы 31 и 32 представляют собой сумматоры

ления;на фиг.5 - схема второго блока управления;на фиг.6 - возможное выполнение счетчика; на фиг.7 - вре- меннйе диаграммы работы.

Устройство кодирования, содержит блок 1 памяти, первый и второй селекторы 2 и 3, формирователь 4 импульса, счетчик 5, первый, второй и третий шифраторы 6-8, элемент ИЛИ 9, элемент И 10, триггер П, пер 2

вый и второй блоки 12 и 13 управления. На фиг.1 обозначены первый-чет вертый управляющие входы 14-17, информационные выходы 18 и первый, второй и третьи управляющие выходы 19- 21.

Елок 1 памяти служит для хранения и вьщачи на обработку результатов МЭЯФ. Он может быть вьшолнен, например, на ферритовых элементах

памяти, объединенных в строки, стро- ,,. л,

„„ „ 35 формации о наличии в считанной строки в матрицы, а матрицы в куб памяти.

входных токов с порогом. Для случая тридцатидвухразрядного кода в первом пороговом элементе 31 первого селектора 2 кода установлен порогу 4, во втором элементе 32 :, 8. При поступлении на входы элемента 31(32) кода, содержшцего не менее четырех (восьми) единиц, на выходе элемента 31 (32) появится сигнал. Подключение входов элементов И 26 и 27 обеспечивает вьщачу на входы элемента 32 инке нескольких соседних единиц, а на входе элемента 31 - о наличии несколь ких массивов единиц.

При этом блок 1 памяти включает в себя .средства для построчного считы--- вания информации поочередно с каждой матрицы куба. Соответственно первые и вторые выходы блока 1 служат для информации, записанной в соответствующей строке, и номера этой строки. На третьем выходе блока 1 выдается сигнал, разрешающий в блоке 1 чтение с очередной строки, на четвертом выходе - сигнал окончания считывания всех матриц в кубе памяти блока I. Пятые выходы блока 1 служат для выведения номера считываемой матрицы. Входы блока 1 служат для подачи на них сигналов об окончании вьшедения и шифрации очередной строки, что необходимо для организации требуемого режима, работы блока 1 .

Первый селектор 2 предназначен для выделения информации, записанной в отдельной строке блока 1. Селек

тор 2 включает в себя (фиг.2) п триггеров 22, где п - разрядность числа, считываемого из блока 1, п элементов И 23 первой группы, п элементов И 24 второй группы, п элементов И 25 третьей группы, п-1 элементов И 26 четвертой группы, п-1 элементов И 27 пятой группы, rpyitny из п элементов ИЛИ 28, первый и второй элементы

ИЛИ 29 и 30, первый и второй порого- вые элементы 31 и 32. На фиг.2 обоз- начены, информационные входы 33, вход 34 синхронизации, первый, второй и

25

30

,,. л,

входных токов с порогом. Для случая тридцатидвухразрядного кода в первом пороговом элементе 31 первого селектора 2 кода установлен порогу 4, во втором элементе 32 :, 8. При поступлении на входы элемента 31(32) кода, содержшцего не менее четырех (восьми) единиц, на выходе элемента 31 (32) появится сигнал. Подключение входов элементов И 26 и 27 обеспечивает вьщачу на входы элемента 32 ин

о

ке нескольких соседних единиц, а на входе элемента 31 - о наличии нескольких массивов единиц.

Второй селектор 3 кода вьшолнен аналогично, но порог в первом элементе 31 выбран I, а третья группа элементов И 25, первый и второй элементы ИЛИ 29 и 30 и второй порого- вьй элемент 32, а также пятые, шестой и седьмой выходы 42-44 не используются.

Формирователь 4 импульса вьтолнен (фиг.З) на триггерах 49 и 50, одно- вибраторах 51 и 52, элементах И 53- 56, элементе ИХШ 57 и элементе НЕ 58. На фиг.З обозначены первый-третий информационные входы 59-61, первый и второй управляющие входы 62 и 63 и выход 64. Формирователь 4 вырабатывает выходной сигнал в том случае, если при считывании двух подряд идущих строк единицы имелись в последних разрядах первой из этих строк и в первых разрядах второй.

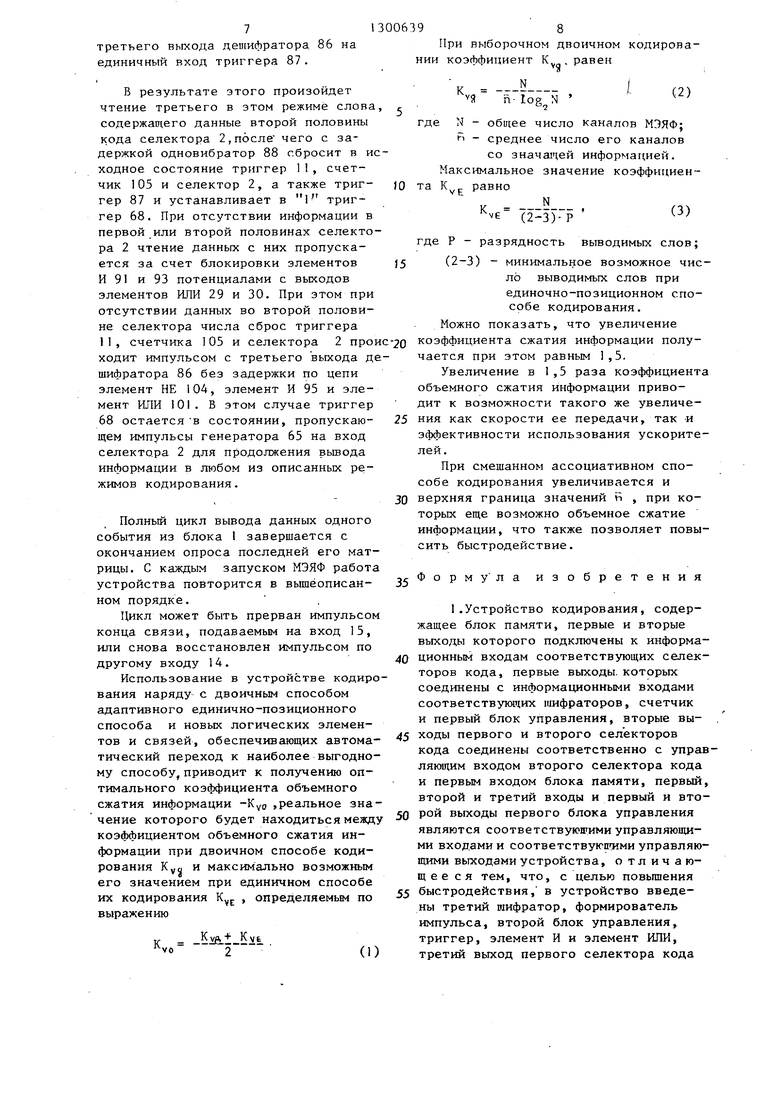

Первый блок 12 управления определяет начало и конец режима кодирования. Он включает в себя (фиг.4) тактовый генератор 65, триггеры 66- 68, одновибраторы 69-71, элементы И 72, 73 и элемент 74. На фиг.4 обозначены входы 75-81 и выходы 82-84.

Второй блок 13 управления осуществляет выбор режима кодирования. Он включает в себя (Лиг.5) блок 85 ключей, дешифратор 86, триггер 87, од- новибратор 88, элементы И 89-99,

элементы ИЛИ 101-104, элемент НЕ 105,15 кодирование информации для ее сжатия

20

30

и счетчик 105. На фиг. 5 обозначены входы 106-112 и выходы 113-120.

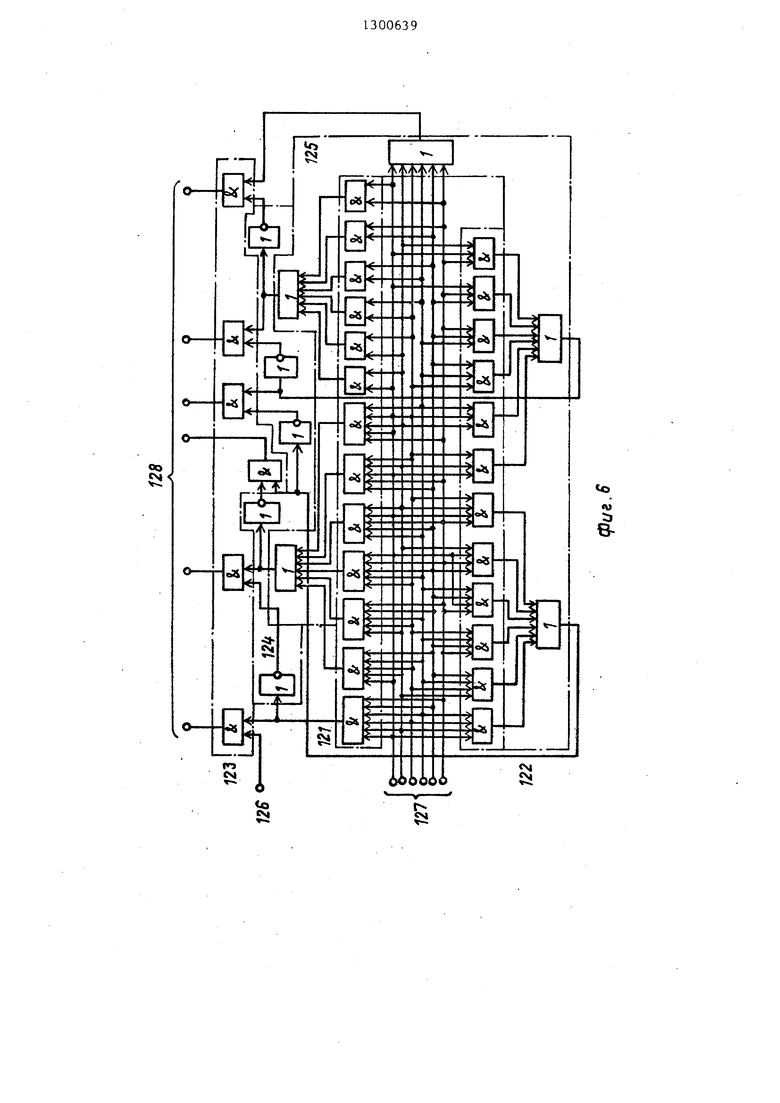

Счетчик 5 служит для подсчета чис ла соседних единиц в считьюаемом коде. Возможное вьшолнение этого счетчика 5 приведено на фиг.6, где обозначены группы I21-123 элементов И, группа 124 элементов НЕ и группа 125 элементов ИЛИ.

На фиг.6 обозначены управляющие вход 126, информационные входы 127 и выходы -128. Каждый из информационных входов 127 соединен с выходом элемента 1-ШИ, на входы которого подаются сигналы с тех пятых выходов 42 первого селектора 2 (фиг.2), номера которых отличаются на 6, т.е. например, с первым информационным входом счетчика 5 соединены первый, седьмой, тринадцатый, девятнадцатый, двадцать 35 ратора 65. пятый, и Тридцать первый выходы из группы пятых выходов 42 селектора 2. Возможно выполнение счетчика 5 на ПЗУ либо счетчике с параллельными входами.

40

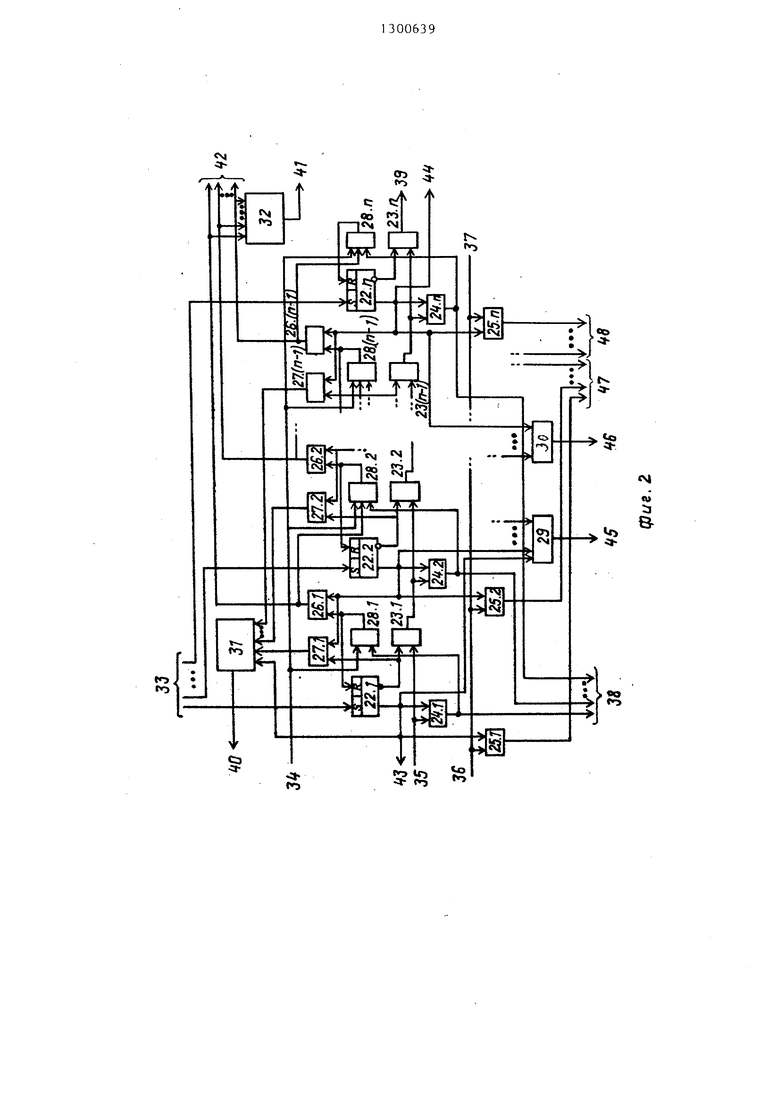

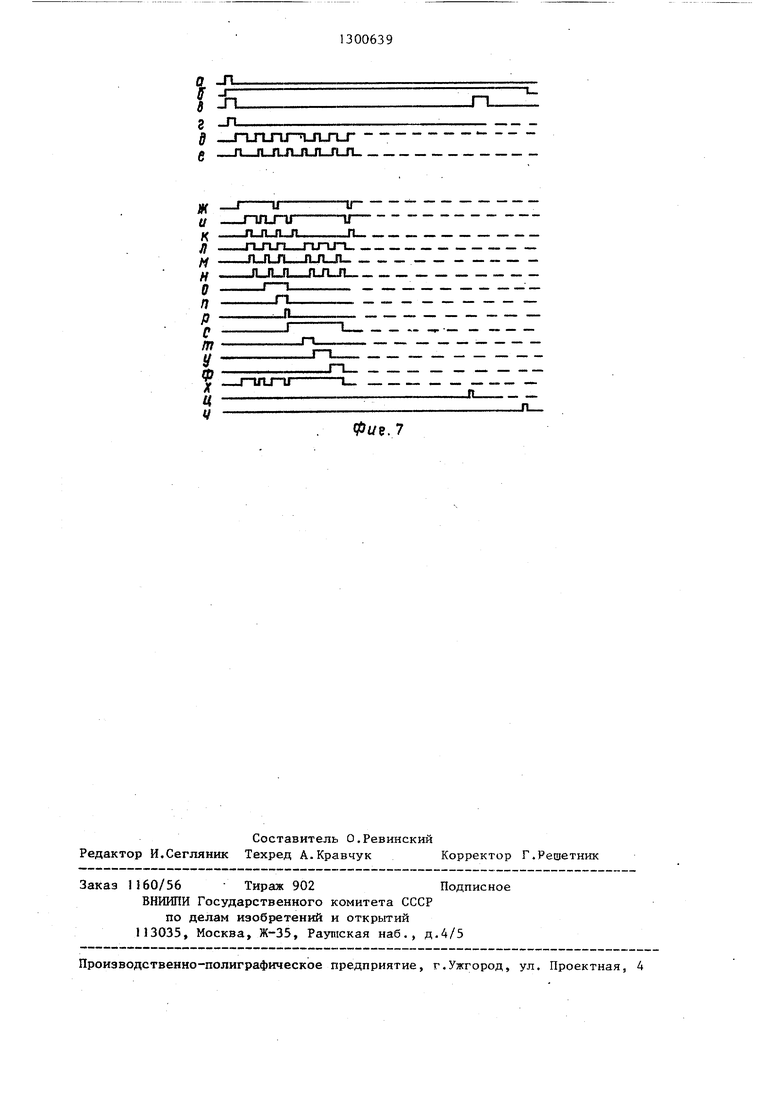

На фиг.7 обозначены следующие диаграммы: а - импульс начала цикла на входе 14; б - сигнал на выходе 82 блока 12; в - сигнал на выходе 20; г - импульс запуска на входе 16; д - сигнал на выходе триггера 68 блока 12; е - сигнал на выходе 84 блока 12; ж - сигнал на втором выходе селектора 3; и - сигнал на втором выходе селектора 2; к - сигнал на управляющем выходе шифратора 6; л - сигнал на вьпсоде 118 блока 13; м - импульсы с выхода элемента И 96 блока 13; н - импульсы на выходе одследует пр а во второ

Устройс следующим

С подач начала цик устанавлив ние и с вы управляющи 25 ройства (Э

В резул ление и ре в блоке 1 на входе 1 са устройс ное для вы триггер 68 ние 1. П 2 появятся

В резул импульса ч 2 и 3 в бл на первая ее построч выбранной торе 2, гд отселектир 45 лежащие пе треку). Вы рядов пода И 26. Отсе первых вых ются также торы 6 и 7 ность фрон жек элемен с выхода э

50

новибратора 88 блока 13; о, п - сиг- 2 при числе треков П меньше 4, а

налы на выходах триггеров 22.1 итакже и при числе соседних единиц

22.2 селектора 2; р - сигнал на вы-n jменьше 8 проходит через элемент

ходе элемента ИЛИ 9; с - сигнал наИ 98 и элемент ИЛИ 101 на единичный

выходе триггера 11; т,у,ф - сигналывход триггера 87. С установлением

06394

на выходах дешифратора 86 блока 13; X - сигнал на выходе 45 селектора 2; ц - импульс на входе 79 блока 12; ч - импульс конца цикла на входе 15.

Работа устройства построена с учетом того, что в МЭЯФ с использованием проволочных камер в качестве регистрирующих элементов для обнаружения треков частиц записываемая с про- 10 волочных камер информация может содержать массивы единиц (след TpeKaJ, разделенные массивами нулей,в которых возможны отдельные единицы. При этом в первом случае (массив единиц)

ратора 65.

следует проводить единичным кодом, а во втором случае двоичным кодом.

Устройство кодирования работает следующим образом.

С подачей на вход 14 сигнала начала цикла (фиг.7а) триггер 66 устанавливается в единичное состояние и с выходов 19 и 20 подаются управляющие сигналы на внешние уст- ройства (ЭВМ).

В результате осуществляется вьще- ление и регистрация нужного события в блоке 1 памяти. По сигналу запуска на входе 16 формируется импульс сброса устройства кодирования в исходное для вывода данных состояние, триггер 68 устанавливается в состояние 1. При этом на выходе 84 блока 2 появятся импульсы тактового генератора 65.

В результате прохождения этого импульса через свободные селекторы 2 и 3 в блоке 1 памяти будет выбрана первая матрица памяти и начнется ее построчное считывание.. Информация выбранной строки считается на селекторе 2, где автоматически окажутся отселектированными разряды, принад- лежащие первому числу (кластеру, треку). Выход первого из этих разрядов подается на входы элементов И 26. Отселектированные разряды с первых выходов селекторов 2 и 3 подаются также на соответствующие шифраторы 6 и 7. Задержанный на длительность фронтов и внутренних задержек элементов селектора 2 импульс с выхода элемента ШЕ1 29 селектора

этого триггера 87 в единичное состояние через одновибратор 71 сбрасьша- ет.ся в О триггер 68, благодаря чему открьтается элемент И 96.

В результате этого блокируется ра- бота тактового -генератора 65, а на выходы 18 поступает выходной код. Затем через время задержки одновибрато- ра 88 сбросится в О триггер 87 и установит в триггер 68. В этом состоянии триггера 68 очередной импульс тактового генератора 65 пройдет через на вход селектора 2 и по своему переднему фронту сбросит в О разряды селектора 2, принадлежащие данным выведенного трека, а по заднему фронту осуществит вьщеление его разрядов, содержащих данные следующего по порядку трека. В описанном порядке будет происходить вьшод всех

П

тр

меньше 4 и П

се

слоев, в которых меньше 8.

Однако при выводе из регистра числа последнего числа возможно распределение его единиц в конце выведенной и в начале следующей строки. Вьщеление признака такого события осуществляется формирователем 4 импульса. Триггер 49 запоминает единицу в последнем разряде числа до проверки единицы в первом его разряде после считывания данных следующей строки. При совпадении сигналов на всех входах 59-61 триггер 50 устанавливается в состояние 1, которое в выходном слове является признаком, требующим объединения данных слова с этим признаком и предыдущего ему слова. Сброс триггеров 49 и 50 в исходное состояние осуществляется как после чтения, так и при отсутствии совпадений сигналов на входах

элементов И 53 и 56. I

При считьшании на селектор 2 данных строки, содержащей больше 3 треков и при числе соседних единиц в числах больше 7, происходит срабатывание пороговых элементов 31 и 32. При этом сигналом с их выходов триггер 11 устанавливается в единичное состояние и происходит переключение режима двоичного кодирования на единичный. В этом состоянии триггера 11 для импульсов тактового генератора 65 запирается элемент И 10, а для пропускания импульсов вьщачи признака готовности числа к выводу и импульсов чтения соответственно пере

ключаются элементы И 97, 98 на .элементы И 89-93. переключения триггера I1 в единичное состояние через одновибратор 70 и элемент ИЛИ 74 подтверждает единичное состоя ние триггера 68, при котором очередной импульс с генератора 65 пройдет на вход двухразряд ного счетчика 105 с дешифратором 86 и блоком 85 ключей. При этом появится сигнал на первом выходе дешифратора 86 и через элемент 100 ИЛИ установится в единичное состояние триггер 87, потенциалом с выхода которого, как и в описанном режиме откроется элемент И 96 и через одновибратор 71 сбросится в О триггер 68, блокирующий импульсы генератора 65.

В результате этого осу1цествится вывод числа (первого слова) в этом режиме с выходов шифратора 7 и с выходов 21 (из блока 1 памяти). Затем как и в первом режиме сбросится в О триггер 87 и установится в 1 триггер 68.

С установлением в 1 триггера 68 второй в этом режиме импульс генератора 65 пройдет на вход счетчика

105 и тем самьм переключит первый выход дешифратора 86 на второй. Если при этом не будет свободна от инфорации первая половина селектора 2, то потенциалом с выхода элемента

ИЛИ 29 будет открыт элемент И 91, который пропустит импульс со второго выхода дешифратора 86 через элеент ИЛИ 100 на единичный вход триггера 87. В результате сработает

одновибратор 88 и сбрасывает в О триггер 68. Элемент И 96 открыт для импульсов со входа 112. Первая половина кода в селекторе 2 считывается в позиционном коде,после чего сбросится в О триггер 87 и далее через элемент ИЛИ 74 установит в I триггер 68.

С деблокировкой импульсов генератора 65 очередной третий его импульс снова пройдет на вход счетчика 105 и осуществит переключение второго выхода дешифратора 86 на третий. И снова, как и при включенном втором выходе дешифратора 86, при наличии информации теперь уже во второй половине кода селектора 2, с выхода элемента ИЛИ 30 будет открыт элемент И 93, который пропустит сигнал с

третьего выхода дешифратора 86 на единичный вход триггера 87.

В результате этого произойдет чтение третьего в этом режиме слова содержащего данные второй половины кода селектора 2, после чего с задержкой одновибратор 88 сбросит в иходное состояние триггер 1, счетчик 105 и селектор 2, а также триг- гер 87 и устанавливает в триггер 68. При отсутствии информации в первой или второй половинах селектора 2 чтение данных с них пропускается за счет блокировки элементов И 91 и 93 потенциалами с выходов элементов ИЛИ 29 и 30. При этом при отсутствии данных во второй половине селектора числа сброс триггера 1 1 , счетчика 1 05 и селектора 2 про ходит импульсом с третьего вьгхода дшифратора 86 без задержки по цепи элемент НЕ 104, элемент И 95 и элемент ИЛИ 101. В этом случае триггер 68 остается В состоянии, пропускаю- щем импульсы генератора 65 на вход селектора 2 для продолжения вьшода информации в любом из описанных режимов кодирования.

-

Полный цикл вывода данных одного события из блока 1 завершается с окончанием опроса последней его матрицы. С каждым запуском МЭЯФ работа устройства повторится в вышеописан- ном порядке.

Цикл может быть прерван импульсом конца связи, подаваемым на вход 15, или снова восстановлен импульсом по другому входу 14.

Использование в устройстве кодирования наряду с двоичным способом адаптивного единично-позиционного способа и новых логических элементов и связей, обеспечивающих автома- тический переход к наиболее выгодному способу, приводит к получению оптимального коэффициента объемного сжатия информации -Кур ,реальное значение которого будет находиться межд коэффициентом объемного сжатия информации при двоичном способе кодирования Куа и максимально возможным его значением при единичном способе их кодирования К. , определяемьм по выражению

V- -

vo 2

При выборочном двоичном кодировании коэффициент К равен

3

; (2

где N - общее число каналов МЗЯФ; FI - среднее число его каналов

со значшцей информацией. Максимальное значение коэффициента К равно

К N

6 (2-3)-Р

(3)

, )о J5с-2025 30

35

где Р - разрядность вьшодимых слов;

(2-3) - минимальное возможное число выводимых слов при единочно-позиционном способе кодирования. Можно показать, что увеличение коэффициента сжатия информации получается при этом равным 1,5.

Увеличение в 1,5 раза коэффициента объемного сжатия информации приводит к возможности такого же увеличения как скорости ее передачи, так -и эффективности использования ускорителей.

При смешанном ассоциативном способе кодирования увеличивается и верхняя граница значений Fi , при которых еще возможно объемное сжатие информации, что также позволяет повысить быстродействие.

Форму ла изобретения

1.Устройство кодирования, содержащее блок памяти, первые и вторые выходы которого подключены к информа- ционньм входам соответствующих селекторов кода, первые выходы, которых соединены с информационными входами соответствующих шифраторов, счетчик и первый блок управления, вторые выходы первого и второго селекторов кода соединены соответственно с управляющим входом второго селектора кода и первым входом блока памяти, первый, второй и третий входы и первый и второй выходы первого блока управления являются соответствующими управляющими входами и соответствуюп нми управляющими выходами устройства, о т л и ч а ю- щ ее с я тем, что, с целью повышения быстродействия, в устройство введены третий шифратор, формирователь импульса, второй блок управления, триггер, элемент И и элемент ИЛИ, третий выход первого селектора кода

соединен с первым входом элемента ИЛИ, четвертый выход первого селектора кода подключен ко второму вход элемента ИЛИ и управляющему входу счетчика, выход которого соединен с первым входом триггера, инверсный выход которого подключен к первым входам элемента И и второго блока управления, прямой выход триггера соединен с четвертым входом первого и вторым входом второго блоков упраления, первый выход второго блока управления подключен к первому управляющему входу первого селектора кода и второму входу триггера, второй и третий выходы второго блока управления соединены соответственно с объединенными управляющими входам первого и третьего шифраторов и с объединенными первьм управлякщим входом формирователя импульса и управляющим входом второго шифратора, пятые выходы первого селектора кода подключены к информационным входам счетчика, выходы которого соединены с информационными входами третьего шифратора, третий выход первого блока управления соединен с третьим входом второго блока управления и вторым входом элемента И, выход которого подключен к входам синхронизации селекторов кода, шестой и седьмой выходы первого и третий выход второго селекторов кода подключены соответственно к первому, второму и третьему информационным входам формирователя импульса, управляющие выходы первого и второго шифраторов соединены соответственно с четвертым входом второго блока управления и вторым входом блока памяти, третий и четвертый выходы которого соединены соответственно с вторым управляющим входом формирователя импульса и пятым входом первого блока управления, четвертый и пятый выходы второго блока управления подключены соответственно к второму и третьему управляющим входам первого селектора кода, восьмой и девятый выходы которого соединены соответственно с пятым и шестым входами второго блока управления, шестой и седьмой выходы которого подключены соответственно к шестому и седьмому входам первого блока управления, седьмой вход второго блока управления и третий вход блока памяти являются соот- ветственно вторым и третьим управляющими входами устройства, выходы первого, второго и третьего шифраторов, девятые и десятые выходы первого селектора кода, выход формирователя

импульса и восьмые выходы второго блока управления являются первыми - седьмыми информационными выходами устройства, пятые выходы блока памяти являются третьими управляющими

0 выходами устройства.

2. Устройство по п., о т л и - чающееся тем, что селектор кода выполнен на группе элементов ИЛИ, первой-пятой группах элементов

5 И, первом и втором пороговых элементах, первом и втором элементах ИЛИ и п триггерах (где п - разрядность , первые входы которых являются информационными входами селектора

0 кода, первые входы элементов ИЛИ группы объединены и являются входом синхронизации селектора кода, первые входы первых элементов И первой и второй групп объединены и являются первым управляющим входом селектора, выход i-ro элемента И первой группы, кроме последнего, подключен к первым входам ()-x элементов И первой и второй групп, инверсные выходы триггеров соединены с вторыми входами соответствукнцих элементов И первой группы и первыми входами соответствующих элементов И пятой группы, прямой выход первого триггера подключен

5 к второму входу первого элемента И второй группы, первому входу первого элемента И третьей группы и первому входу первого элемента ИЛИ, прямой

5

0

выход каждого триггера со второго

,п - „ по (2-)-и подключен ко второму входу

одноименного элемента И второй группы, первым входом одноименного элемента И третьей и предшествующего элемента И четвертой групп , второму входу предшествукндего элемента И пятой группы и одноименному входу первого элемента ИЖ, прямой выход

каждого триггера с ( 1)-го по -и подключен к второму входу одноименного элемента И второй группы, первым входам одноименного элемента И третьей и предшествующего элемента

И четвертой групп, второму входу предшествующего элемента И пятой группы и соответствующему входу второго элемента ИЛИ, выход каждого элемента И второй группы соединен с вторым входом соответствующего элемента Ш1И группы, выход которого подключен к вторьм входам соответствующих триггера и элемента И четвертой группы, выходы элементов И пятой и четвер той групп соединены с входами соответственно первого и второго пороговых элементов, выход каждого элемента И четвертой группы соединен с третьим входом последующего элемента ИЛИ группы, вторые входы элементов И третьей группы соответственно с

первого по

/ II „ (-2-)-и и

(f- Опервого четвертого элементов И объединены и являются первым управляющим входом формирователя импульса, первый вход ч твертого и второй вход второго элементов И объединены и являются вторым управляющим входом формирователя импульса, вход элемента НЕ и третий вход первого элемента И объединены и являются первым информационным входом формирователя импульса, второй и третий входы четвертого элемента И являются вторым и третьим информационными входами фор

мирователя импульса, выход второго го по п-й объединены и являются соот- 5 элемента И являются выходом формиро- ветственно вторым и третьим управляю- цпми входами селектора кода, выходы элементов И второй группы являются соответствующими первыми выходами селектора кода, выход прследне- 20 го элемента И первой группы и выход второго порогового элемента являются соответственно вторым и

вателя импульса.

4. Устройство по п.1, о т л и - чающееся тем, что первый блок управления вьтолнен на триггерах, одновибраторак, элементах И, элементе ИЛИ и тактовом генераторе, выход которого соединен с первым входом .первого элемента И, выход первого триггера подключен к второму входу первого и первому входу в то рого элементов И, выход второго элемента И соединен с первым входом второго триггера, выход первого одно вибратора подключен ко второму входу второго триггера и первому входу элемента ИЛИ, выход которого соединен с первым входом третьего триггера, выход которого подключен к треть ему входу первого элемента И, выходы

третьим выходами селектора кода, выходы элементов И четвертой группы являются соответствующими четвертыми выходами селектора кода, прямые выходы первого и п-го триггеров и выходы первого и второго элементов ИЛИ являются соответственно пятым-восьмым выходами селектора кода, выходы элементов И третьей группы с первого по

/ п , „ (-2-)-и

и с (-2- +1)-го

п-и являются соответствекно-девятыми 35 второго и третьего одновибраторов и десятыми выходами селектора кода. 3. Устройство по П.1, о т л исоединены с вторыми входами соотве ственно элемента ИЛИ и третьего триггера, входы первых триггера и одновибратора являются первыми вхо

чающееся тем, что формирователь импульса выполнен на триггерах,

одновибраторах, элементах И, элемен- 40 ми блока, вход второго одновибрато- те НЕ и элементе ШШ, вьобод которого

соединены с вторыми входами соответ ственно элемента ИЛИ и третьего триггера, входы первых триггера и одновибратора являются первыми вход

ра, второй вход второго элемента И, вход третьего одновибратора и третий вход элемента ИЛИ являются вторым- пятьм входами блока, выходы первого 45 и второго триггеров и выход первого элемента И являются соответственно первым-третьим выходами блока.

соединен с первым входом первого триггера, выход которого подключен к первому входу первого элемента И, выход первого элемента И соединен с первым входом второго триггера, первый и второй выходы которого подключены соответственно ко входу первого одновибратора и первому входу второго элемента И, выход элемента НЕ подключен к первому входу третьего элемента И и входу второго одновибратора, выход которого соединен с вторым входом второго триггера, выход первого одновибратора и выход третьего элемента И подключены ко входам элемента ИЛИ, выход четвертого элемента И соединен с вторым входом первого триггера, вторые входы

063912

первого четвертого элементов И объединены и являются первым управляющим входом формирователя импульса, первый вход ч твертого и второй вход второго элементов И объединены и являются вторым управляющим входом формирователя импульса, вход элемента НЕ и третий вход первого элемента И объединены и являются первым информационным входом формирователя импульса, второй и третий входы четвертого элемента И являются вторым и третьим информационными входами форW

мирователя импульса, выход второго оот- 5 элемента И являются выходом формиро- ляю- ды ся и е- 20 и нта

выытыми выхоыхоЛИсьодыво25

30

о

вателя импульса.

4. Устройство по п.1, о т л и - чающееся тем, что первый блок управления вьтолнен на триггерах, одновибраторак, элементах И, элементе ИЛИ и тактовом генераторе, выход которого соединен с первым входом .первого элемента И, выход первого триггера подключен к второму входу первого и первому входу в то- рого элементов И, выход второго элемента И соединен с первым входом второго триггера, выход первого одно- вибратора подключен ко второму входу второго триггера и первому входу элемента ИЛИ, выход которого соединен с первым входом третьего триггера, выход которого подключен к третьему входу первого элемента И, выходы

второго и третьего одновибраторов

ми блока, вход второго одновибрато-

соединены с вторыми входами соответственно элемента ИЛИ и третьего триггера, входы первых триггера и одновибратора являются первыми входа40 ми блока, вход второго одновибрато-

ра, второй вход второго элемента И, вход третьего одновибратора и третий вход элемента ИЛИ являются вторым- пятьм входами блока, выходы первого 45 и второго триггеров и выход первого элемента И являются соответственно первым-третьим выходами блока.

5. Устройство по п.1, о т л и - 50 чающееся тем, что второй блок управления выполнен на элементах. И, элементах ИЛИ, элементе НЕ, одновиб- раторе, триггере, дешифраторе, блоке ключей и счетчике, выходы которого 55 подключены к соответствующим информационным входам блока ключей и дешифратора, первый вьпсод которого соединен с первыми входами первых элементов И и ИЛИ, второй выход дешифратора соединен с первыми входами второго и третьего элементов И, третий выход дешифратора подключен к первым входам четвертого, пятого и шестого элементов И, выход элемента НЕ соединен с вторым входом седьмого элемента И, выходы шестого и седьмого элементов И подключены к входам второго элемента ИЛИ, выход которого соединен с первым входом счетчика, выходы третьего и пятого элементов И подключены к второму и третьему входам первого элемента ИЛИ, выход которого соединен с первым входом триггера, выход триггера соединен с пер- вьн входом восьмого элемента И, выход которого подключен к вторым входам первого,второго и четвертого и первому входу девятого элементов И и входу одновибратора, выход которо- го соединен с вторыми входами шестого элемента И и триггера, выход первого элемента И подключен к первым входам третьего и четвертого элементов ИЛИ, выход третьего элемента ИЛИ соединен с управляющим входом блока ключей, выход девятого элемента И соединен с вторым входом четвертого

элемента ШИ, выход десятого эл.емен- та И соединен с четвертым входом первого элемента ИШ, выход одиннадцатого элемента И соединен с вторым входом счетчика, второй вход девятого и первый вход десятого элементов И объединены и являются первым входом блока, первый вход одиннадцатого и третьи входы первого,второго и четвертого элементов И объединены и являются вторым входом блока, вторые входы одиннадцатого и десятого элементов И являются соответственно третьим и четвертым входами блока, вход элемента НЕ и второй вход пятого элемента И объединены и являются пятым входом блока, вторые входы третьего и восьмого элементов И являются соответственно шестым и седьмым входами блока, выходы второго элемента ИЛИ, девятого элемента И, четвертого элемента ИЛИ,, четвертого и второго элементов И, триггера и одновибратора являются сооветственно первым - седьмым выходами блока, выходы блока ключей являются восьмыми выходами блока.

м

n

:j &

63

e

-

52

f3

Pi

LJ«t- -i I

5Bit

(pus.

55

55 / B2

7/

-75

7577 7.9

78 8J

80

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для передачи и приема кодоимпульсных сигналов | 1982 |

|

SU1257685A1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246799C1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| СИСТЕМА ЦИФРОВОГО ТЕЛЕВИДЕНИЯ | 2001 |

|

RU2208917C2 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах обработки результатов, получаемых в многодат- чиковых экспериментах ядерной физики, позволяет повысить быстродействие . Устройство кодирования содержит блок 1 памяти, селекторы 2,3 кода, счетчик 5, шифраторы 6,7 и блок 12 управления. Введение формирователя 4 импульса, шифратора 8, элемента ИЖ 9, элемента Н 10, триггера 11 и блока 13 управления обеспечивает адаптивное кодирование информации двоичным либо единичным кодом в зависимости от распределения единиц в строке. этой информации. 4 з.п. ф-лы, 7 ил. hсо лл ф1/г. f

(риг.5

А Ъ

ВО -П.

Ifi

3 -л.

д j- nj-u TjijTLi

g .

Фи. 7

| Приборы и техника эксперимента, 1973, № 1, с.101-104 | |||

| УСТРОЙСТВО для СЕЛЕКТИВНОГО ВЫВОДА ИНФОРМАЦИИ ИЗ ПРОВОЛОЧНЫХ ИСКРОВЫХ КАМЕР | 0 |

|

SU202581A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-30—Публикация

1985-05-17—Подача