Изобретение относится к вычислительной технике, может найти применение в вычислительных системах для сопряжения общего ресурса внешних устройств - абонентов (ВА) с электронными вычислительными машинами (ВМ), и является усовершенствованием устройства по авт. св. № 1257655.

Цель изобретения - сокращение потерь времени при обращениях по некорректным адресам.

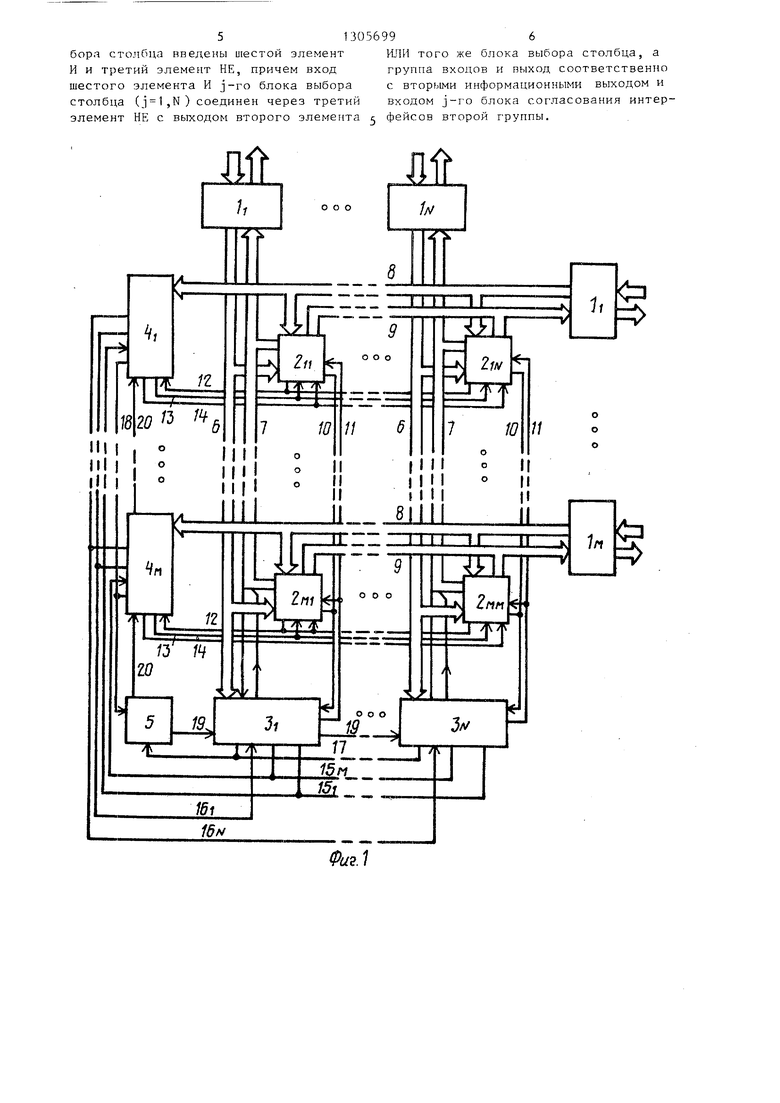

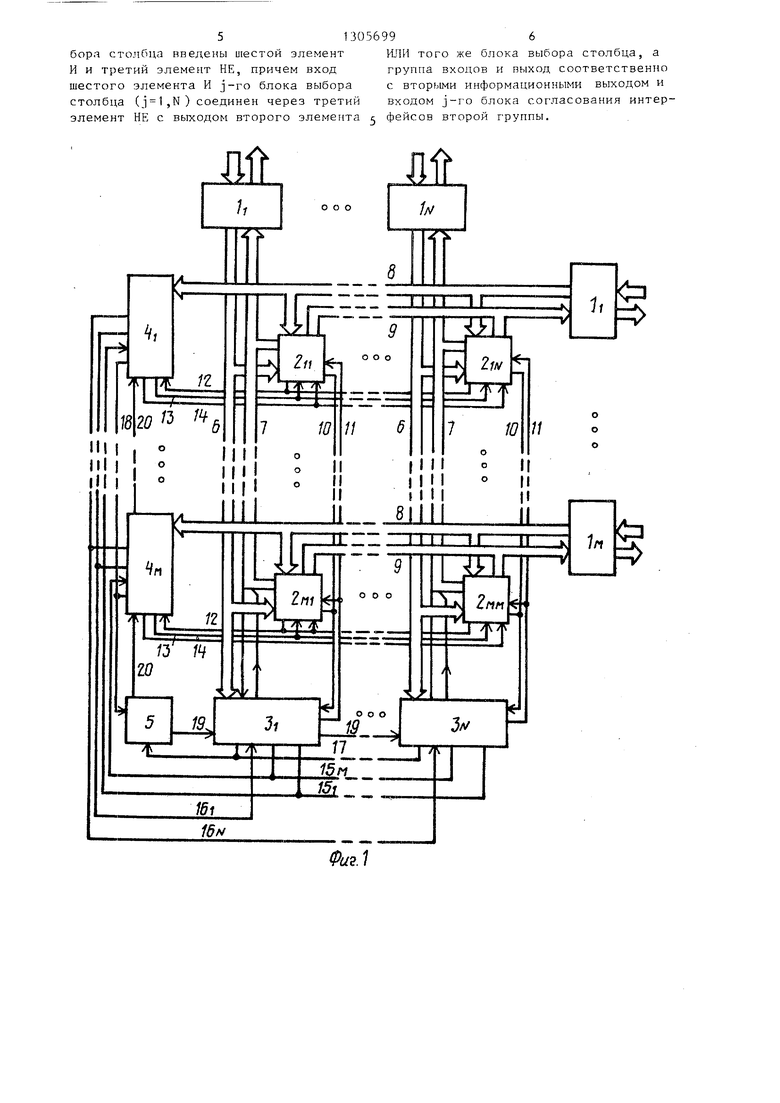

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2-4 функциональные схемы соответственно блоков коммутации, выбора столбца и выбора строки.

Устройство содержит (фиг. 1 ) объединенные в матрицу блоки 1 согласования интерфейсов первой и второй ГРУПП, блоки 2 коммутации, блоки 3 выбора столбца, блоки 4 выбора стро-: ки группы, генератор 5 импульсов опроса, линии 6 и 7 информационных выходов и входов (интерфейс со стороны ЭВМ), линии 8 и 9 информационных выходов и входов (интерфейс со стороны ВА), -линии 10 готовности столбцов (сигналы СТЛБ.ВКЛ.), линии 11 выбора столбцов (сигналы ПОДКЛ. СТОЛБ.), линии 12 готовности строк (сигналы СТР.ВКЛ.), линии 13 выбора строк (сигналы ПОДКЛ.СТР.), линии 14 сброса (сигнал СВР.СТР.), линии 15 выборки строк (сигналы ВБР.СТР.),линии 16 выборки столбцов (сигналы ВБР. СТЛБ.), линии 17 включения опроса столбцов (сигнал ВКЛ.ОПР.СТЛБ.), линии 18 включения опроса строк (сигнал ВКЛ.ОПР.СТР.), линии 19 импульсов опроса столбцов (сигналы ОПР, СТЛБ.) и линии 20 импульсов опроса строк (сигнал ОПР.СТР.).

Блоки 2 коммутации матрицы (фиг.2) состоят из триггера 21, элементов И 22 и 23 первой и второй групп, элемента И 24 и двух .элементов 25 развязки.

Блок 3 выбора столбца (фиг.З) содержит триггер 26, дешифратор 27, первый 28, второй 29, третий 30,четвертый 31 и пятый 32 элементы И,первый 33 и второй 34 элементы ИЛИ,первый 35 и второй 36 элементы НЕ и элементы 37 развязки.

Блок 4 выбора строки (фиг.4) содержит триггер 38, дешифратор 39, первый 40, второй 41, третий 42,четвертый 43, пятый 44 и шестой 45 элементы И, первый 46 и второй 47 элементы ИЛИ, первый 48, второй 49, третий 50 и четвертый 51 элементы НЕ, элеме.нты 52 развязки, третий элемент

НЕ 53 и шестой элемент И 54.

Блоки 1 согласования интерфейсов представляют собой наборы усилителей- приемников и усилителей-передатчиков, предназначенных для согласования на

физическом уровне элементов блоков 2-4 устройства с линиями интерфейса между ВМ и ВА. Генератор 5 импульсов опроса при наличии разрешающих сигналов ВКЛ.ОПР.СТЛБ., ВКЛ.ОПР.СТР. вьщает по соответствующим линиям 19 и 20 последовательности импульсов ОПР. СТЛБ. или ОПР.СТР.

Интерфейс ВМ-ВА может соответствовать, например, стандартному интерфейсу ввода-вывода ЕС-ЭВМ.

Устройство работает следующим образом.

В исходном состоянии триггеры 21 блоков 2 находятся в нулевом состоянии и блокируют элементы И 22 и 23, которые разъединяют линии интерфейсов ВМ-ВА. В нулевом состоянии находятся также триггеры 26 и 38 блоков 3 и 4.

Обмен информацией по инициативе

ВМ между, например, j-й ВН и i-й ВА начинается с вьщачи ВМ по линии 6 адреса выбираемого ВА и соответствующего идентификационного сигнала,

которые поступают на входы соответствующего блока 3 и дешифратор 27. При этом сигнал с соответствующего выхода дешифратора 27 поступает на элемент 37 развязки и на соответствующую линию 15 выборки строки, а также через элемент ИЛИ 34 на элемент 37 развязки, линию 17 сигнала ВКЛ. ОПР.СТЛБ. и на вход генератора 5.Если к этому моменту имеется разрешающий сигнал - отсутствие импульса

ОПР.СТЛБ. на линии 19, то триггер 26 устанавливается в единичное состояние и разрешает прохождение импульса ОПР.СТЛБ. с линии 19 через элементы

И 29 и ИЛИ 33 на линию 11 сигнала

ПОДКЛ.СТЛБ. j-ro столбца, одновременно блокируя прохождение импульсов ОПР.СТЛБ. через элемент И 32 и на следующие блоки 3.

Сигнал ПОДКЛ.СТЛБ. присутствует на линии 11 и готовит элементы И 24 всех блоков 2 заданного столбца, в том числе и блока 2 строки, на другой

вход элемента И 24 которого поступае сигнал ПОДКЛ.СТР. по линии 13 с блок 4. , где он формируется на элементах ИЛИ 46, И 40, НЕ 48 сигналами СТР. ВКЛ. с линии 12 и сигналом ВБР.СТР., поступившим по линии 15 из блока 3. Таким образом, происходит выбор блок 2 в J-M столбце и i-й строке, триггер 21 которого устанавливается в единичное состояние и разрешает че- рез элементы И 22 и 23 прохождение информации по линиям интерфейса между соответствующими ВМ и ВА. Процедура логического подключения ВА и БМ заканчивается вьщачей- заданным ВА сигнала логического подключения, по которому ВМ снимает идентификационный сигнал адреса и адрес выбираемого ВА и начинает обмен информацией с i-M BAJ Сигнал логического подклю- чения i-ro ВА поступает также по линии 7 в блок 3J на элемент И 30, разрешая сброс в нулевое состояние триггера 26, а также поступает в блок 4- на вход элемента НЕ 50, блокируя вы- дачу сигнала СВР.СТР, с элемента И 45 до окончания операции с данным ВА После окончания обмена и снятия ВА сигнала логического подключения производится сброс триггера 21 блока 2-; сигналом СВР.СТР., вьщаваемым на линию 14 элементом И 45 блока 4.

Если одновременно несколько ВМ инициируют операции ввода-вывода и выдают на соответствуюпще линии 6 коды адреса, необходимых для обмена ВА, то триггеры 26 в соответствующих блоках 3 устанавливаются в единичное состояние. Логическое подключение ВА и ВМ в этом случае осуществляется поочередно в соответствии с приоритетом блоков 3 по линии 19 импульсов ОПР.СТЛБ. Попытка БМ подключиться к уже подключенному ВА блокируется сигналом СТР.ВКП, выдаваемым тригге- ром 21 соответствующего блока 2 через элемент 25 развязки на линию 12 в соответствующий блок 4 на элемент НЕ 48.

Привьщаче БМнекорректного кода адреса БА (ВА с данным адресом отсутствует) на выходах дешифратора 27 блока 3 и выходе элемента ИЛИ 34 сигналы отсутствуют и установка тригге- ра 26 в единичное состояние не производится. При этом на входе элемента И 54 устанавливается разрешающий уровень, вьщаваемый с выхода элемента НЕ 53. С поступлением на группу входов элемента И 54 сигнала выборки от канала ВМ и сигнала идентификации адреса на его выходе формируется сигнал выборки абонента, который поступает через соответствующий выход блока 3 -на линию сигнала выборки абонента в канал БМ, инициировавшей операцию ввода-вывода, обеспечивая возможность идентификации данной ситуации с некорректным заданием адреса ВА.

В случае инициативы ВА установление связи, например, между i-м ВА и JM ВМ начинается с выдачи ВА адреса ВМ и сигнала требования абонента по линиям 8 в блок 4, где адрес БМ дешифрируется. Работа элементов блока 4 по обеспечению логического подключения i-ro ВА аналогична работе соответствующих элементов блока 3. После осуществления коммутации в блоке 2.. сигнал требования i-ro ВА выдается в j-ю ВМ и процедура логическо- го подключения завершается вьщачей сигнала логического подключения заданного ВА в j-ю ВМ, который поступает и в блок 4 на элемент И 42,разрешая сбрбс триггера 38.

При одновременной выдаче сигналов требования несколькими БА логическое подключение ВА осуществляется поочередно в соответствии с приоритетом блоков 4 по линии 20 импульсов ОПР. СТР. Попытка БА подключить к ВМ, уже работающей с другим ВА, блокируется сигналом СТЛБ.ВКЛ, выдаваемьм триггером 21 соответствуицего блока 2 через элемент 25 развязки на линию 10 в соответствующий блок 3 на элемент НЕ 35.

Для обеспечения разрешения конфликтов при одновременной попытке БА и ВМ инициировать операцию ввода- вьшода импульсы ОПР.СТЛВ. сдвинуты относительно импульсов ОПР.СТР. на время, необходимое для установления в линиях 10 сигналов СТЛБ.БКЛ. или в линиях 12 сигналов СТР.ВКП.

Формула изобретения

Устройство для сопряжения электронных вычислительных машин с внеш-. ними устройствами по авт. св. № 1257655, отличающееся тем, что, с целью сокращения потерь времени при обращениях по некорректным адресам, в него в каждый блок вы513056996

бора столбца введены шестой элемент ИЛИ того же блока выбора столбца, а И и третий элемент НЕ, причем вход группа входов и выход соответственно шестого элемента И j-ro блока выбора с вторыми информационными выходом и столбца (,N) соединен через третий входом j-ro блока согласования интерэлемент НЕ с выходом второго элемента 5 Фейсов второй группы.

м

Л1

7

22

W10

12

(

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронных вычислительных машин с внешними устройствами | 1985 |

|

SU1257655A1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Устройство для сопряжения | 1983 |

|

SU1118993A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для сопряжения | 1982 |

|

SU1038933A1 |

| Устройство для сопряжения | 1990 |

|

SU1784984A1 |

| Устройство для подключения внешних устройств к общей магистрали | 1986 |

|

SU1343420A1 |

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

Изобретение касается вычислительной техники и может найти применение в вычислительных системах для сопряжения общего ресурса внешних устройств с ЭВМ, Цель изобретения - сокращение потерь времени при обращениях со стороны ЭВМ по некорректным адресам внешних устройств. Цель достигается тем, что в каждый блок выбора столбца введены шестой элемент И 54 и третий элемент НЕ 53. При некорректном задании адреса выбираемого абонента из-за программной ошибки или неисправности адресных шин интерфейса сигнал возвращается по линии 7 в ЭВМ через открытый элемент И 54. 4 ил. ГЧ)

2

--t

11

Составитель В.Вертлиб Редактор Н.Гунько Техред А.Кравчук .

.1. г..

ЗакаГиЗЗМ Тираж

ВНИИПИ Государственного комитета uLLF

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно

-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

11 3

;v

Фиг. 2

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-11-20—Подача