ратор 4, блок выборки и хранения. 5, запоминающий конденсатор 7, нуль-орган 8, первый, второй, третий и четвертый триггеры 9, 22, 23 и 30, элемент ИЛИ 10, первый, второй, третий, четвертый, пятый,-шестой, седьмой и восьмой элементы И 12, 13, 24, 25, 26, 27, 28 и 29, генератор импульсов 14, первый, второй и третий счетчики 16, 17 и 32, первый и второй вычитающие счетчики 18 и 19, первый и второй дешифраторы 20 и 21, блок запрета прохождения первого импульса 31.

1

Изобретение относится к электрическим вычисли.тельным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повышение быстродействия и расширение области применения за счет возможности работы с одиночными времяимпульсными сигналами .

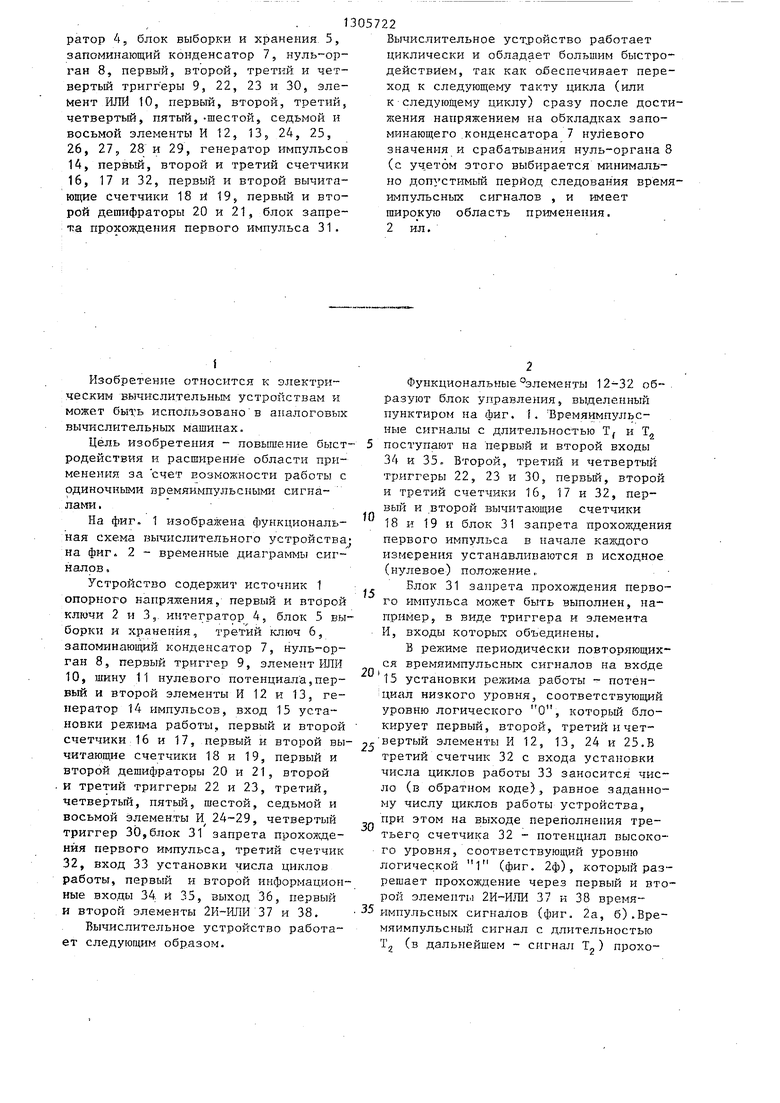

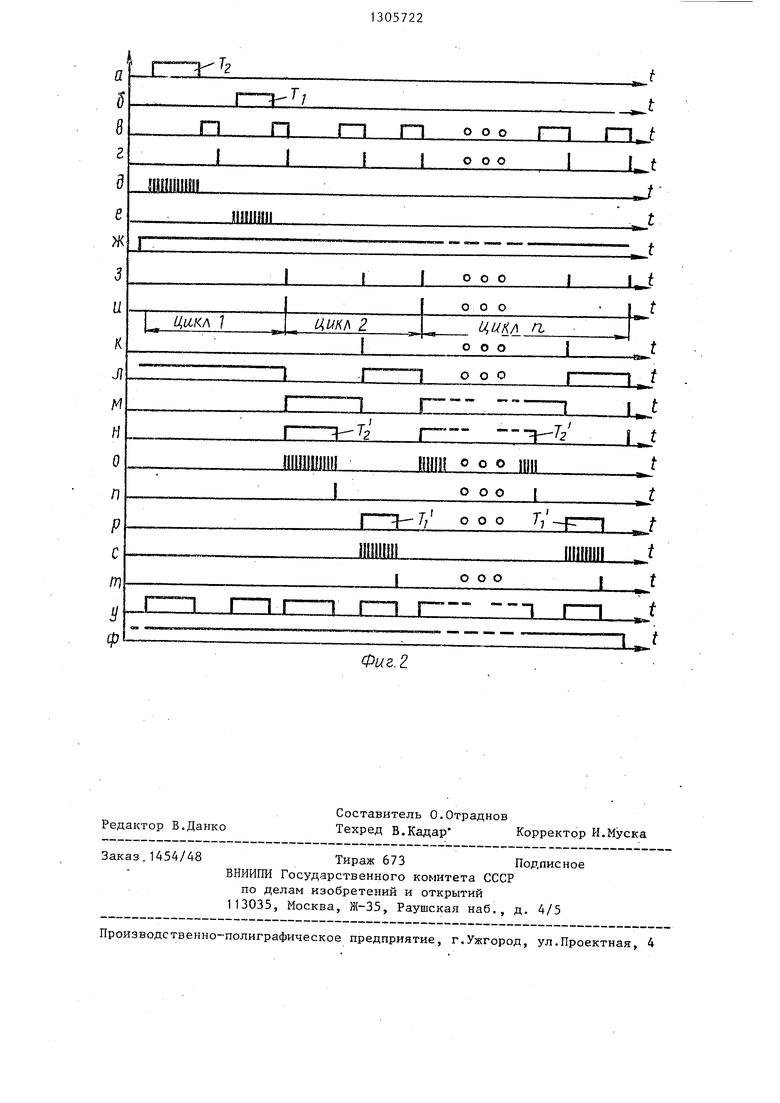

Иа фиг. 1 изображена функциональная схема вычислительного устройства

у

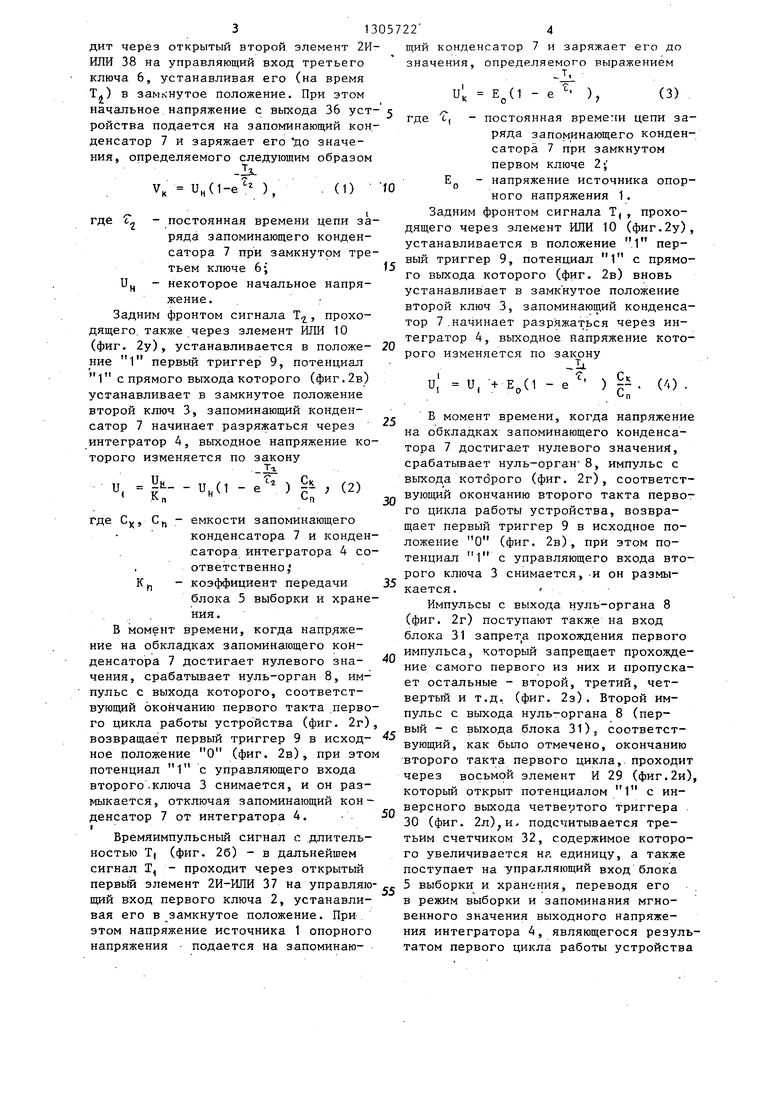

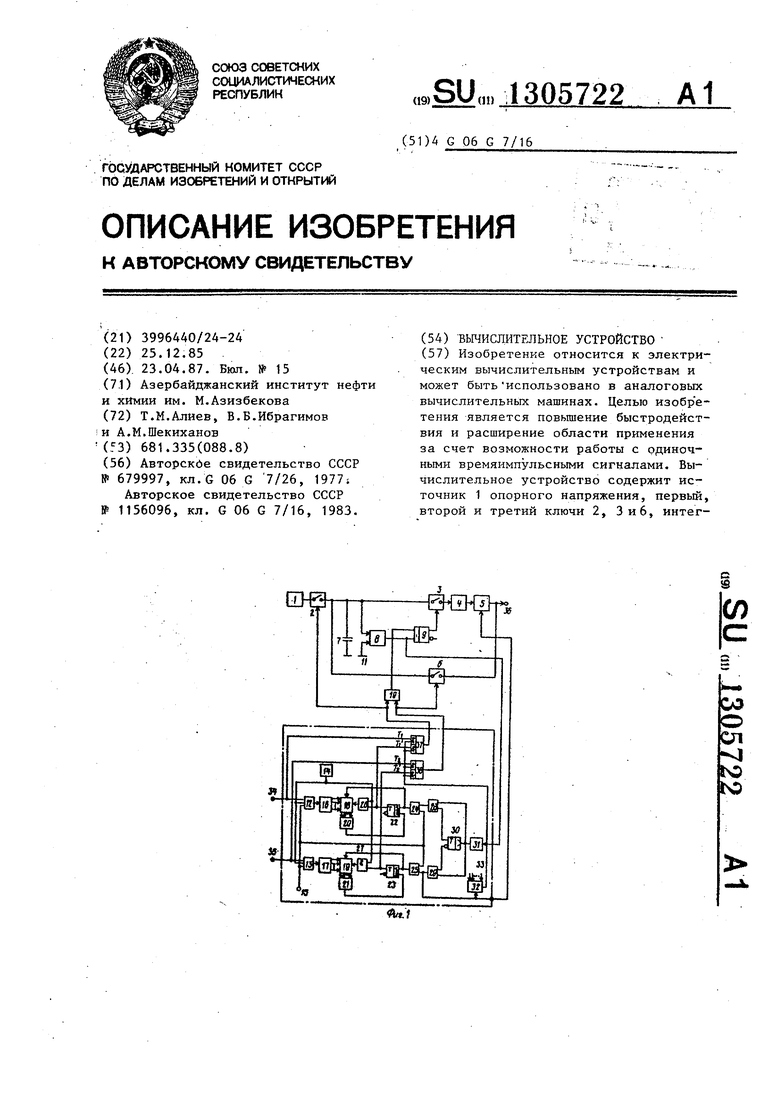

на фиг. 2 вре.менные диаграммы сигналов .

Устройство содержит источник 1 опорного напряжения, первый и второй ключи 2 и 3,- интегратор 4, блок 5 выборки и хранения, третий ключ 6, запоминающий конденсатор 7, нуль-орган 8, первый триггер 9, элемент ИЛИ 10, шину 11 нулевого потенциала,первый и второй элементы И 12 и 13, генератор 14 импульсов, вход 15 установки режима работы, первый и второй счетчики 16 и 17, первый и второй вычитающие счетчики 18 и 19, первый и второй дешифраторы 20 и 21, второй и третий триггеры 22 и 23, третий, четвертый, пятый, шестой, седьмой и восьмой элемен.ты И 24-29, четвертый триггер 30,блок 31 запрета прохолоде- нйя первого импульса, третий счетчик 32, вход 33 установки числа циклов работы, первый и второй информационные входы 34. и 35, выход 36, первый и второй элементы 37 и 38.

Вычислительное устройство работает следующим образом.

Вычислительное уст)ойство работает циклически и обладает большим быстродействием, так как обеспечивает переход к следующему такту цикла (или к следующему циклу) сразу после достижения напряжением на обкладках запоминающего .конденсатора 7 нулевого значения и срабатывания нуль-органа 8 (с уч,ет6м этого выбирается минимально допустимый период следования время- импульсных сигналов , и имеет широкую область применения. 2 ил.

10

f5

Функциональные элементы 12-32 об-, разуют блок ухтравления, выделенный пунктиром на фиг. 1. Времяимпульс- ные сигналы с длительностью Tj и Т 5 поступают на первый и второй входы 34 и 35 Второй, третий и четвертый триггеры 22, 23 и 30, первьй, второй и третий счетчики 16, 17 и 32, первый и второй вычитающие счетчики 18 и 19 и блок 31 запрета прохояодения первого импульса в начале каждого измерения устанавливаются в исходное (нулевое) положение,.

Блок 31 запрета прохождения первого импульса может быть выполнен, например, в виде триггера и элемента И, входы которых объединены.

В режиме периодически повторяющихся времяимпульсных сигналов на вхбде 15 установки режима работы - потенциал низкого уровня, соответствующий уровню логического О, который блокирует первый, второй, третий ичет- , вертый элементы И 12, 13, 24 и 25.В третий счетчик 32 с входа установки числа циклов работы 33 заносится число (в обратном коде), равное заданному числу циклов работы устройства, при этом на выходе переполнения третьего счетчика 32 - потенциал высоко- I o уровня, соответствующий уровню логической 1 (фиг. 2ф), котор1)1й разрешает прохождение черев первый и второй элементы 2И-ИЛИ 37 и 38 время- 35 импульсных сигналов (фиг, 2а, б).Вре- мяимпульсный сигнал с длительностью Т,, (в дальнейшем - сигнал Т ) прохо01

30

дит через открытый второй элемент 2И- ИЛИ 38 на управляющий вход третьего ключа 6, устанавливая его (на время Т) в замкнутое положение. При этом начальное напряжение с выхода 36 устройства подается на запоминающий конденсатор 7 и заряжает его до значения,

определяемого следующим образом т.

V, и„(1-е ),

(1)

где t.

- постоянная времени цепи заряда запоминающего конденсатора 7 при замкнутом третьем ключе 6;

Оц некоторое начальное напряжение. . : Задним фронтом сигнала Т, проходящего, также через элемент ИЛИ 10 (фиг. 2у), устанавливается в положе- ние 1 первый триггер 9, потенциал 1 с прямого выхода которого (фиг.2в) устанавливает в замкнутое положение второй ключ 3, запоминающий конденсатор 7 начинает разряжаться через интегратор 4, выходное напряжение ко

торого изменяется по закону

т.

и, г.- - и,(1 де С

К

К

К

с„ е М -- - Сп

(2)

30

п

п

емкости запоминающего конденсатора 7 и конден- .сатора интегратора 4 соответственно,

коэффициент передачи 35 блока 5 выборки и хранения.

В момент времени, когда напряжеие на обкладках запоминающего коненсатора 7 достигает нулевого знаения, срабатьшает нуль-орган 8, им40

уг

Импульсы с выхода нуль-органа 8 (фиг. 2г) поступают также на вход блока 31 запретна прохождения первого импульса, который запрещает прохожде ние самого первого из них и пропуска ет остальные - второй, третий, четвертый и т.д. (фиг. 2з). Второй импульс с выхода нуль-органа 8 (перпульс с выхода которого, соответствующий окончанию первого такта .первого цикла работы устройства (фиг. 2г) , въгкор(а блока 31), соответст- возвращает первый триггер 9 в исход- - „ ,

ное положение О (фиг. 2в), при этом It 411

потенциал

с управляющего входа

вующий, как было отмечено, окончанию второго такта первого цикла, проходит через восьмой элемент И 29 (фиг.2и который открыт потенциалом 1 с инверсного выхода четвертого триггера 30 (фиг. 2л)и. подсчитывается третьим счетчиком 32, содержимое которого увеличивается HP. единицу, а также поступает на упраг.ляющий вход блока

второго .ключа 3 снимается, и он размыкается, отключая запоминающий конденсатор 7 от интегратора 4.

вующий, как было отмечено, окончани второго такта первого цикла, проход через восьмой элемент И 29 (фиг.2 который открыт потенциалом 1 с ин версного выхода четвертого триггера 30 (фиг. 2л)и. подсчитывается третьим счетчиком 32, содержимое котор го увеличивается HP. единицу, а такж поступает на упраг.ляющий вход блока

Времяимпульсный сигнал с длительностью Т( (фиг. 2б) - в дальнейшем сигнал Т, - проходит через открытый первьй элемент 2И-ИЛИ 37 на управляю- - 5 выборки и хранения, переводя его щий вход первого ключа 2, устанавли- в режим выборки и запоминания мгно- вая его в замкнутое положение. При этом напряжение источника 1 опорного напряжения подается на запоминаювенного значения выходного напряжения интегратора 4, являющегося резул татом первого цикла работы устройст

22

щий конденсатор значения.

4

и

заряжает его до

определяемого выражением т,

Ес(1 С-,

),

(3)

5

O

5

0

где

- постоянная времени цепи заряда запоминающего конденсатора 7 при замкнутом первом ключе 2;

EJ, - напряжение источника опорного напряжения 1. Задним фронтом сигнала Т(, проходящего через элемент ИЛИ 10 (фиг.2у), устанавливается в положение 1 первый триггер 9, потенциал 1 с прямого выхода которого (фиг. 2в) вновь устанавливает в замкнутое положение второй ключ 3, запоминающий конденсатор 7.начинает разряжаться через интегратор 4, выходное напряжение которого изменяется по закону

11

и. Ч

Ео(1 ) -- .

Сп

(4) .

В момент времени, когда напряжение на обкладках запоминающего конденсатора 7 достигает нулевого значения, срабатывает нуль-орган 8, импульс с выхода котброго (фиг. 2г), соответствующий окончанию второго такта первого цикла работы устройства, возвращает первый триггер 9 в исходное положение О (фиг. 2в), при этом потенциал 1 с управляющего входа второго ключа 3 снимается, -и он размыкается.

Импульсы с выхода нуль-органа 8 (фиг. 2г) поступают также на вход блока 31 запретна прохождения первого импульса, который запрещает прохождение самого первого из них и пропускает остальные - второй, третий, четвертый и т.д. (фиг. 2з). Второй импульс с выхода нуль-органа 8 (пер въгкор(а блока 31), соответст- „ ,

въгкор(а блока 31), соответст- - „ ,

50

вующий, как было отмечено, окончанию второго такта первого цикла, проходит через восьмой элемент И 29 (фиг.2и), который открыт потенциалом 1 с инверсного выхода четвертого триггера 30 (фиг. 2л)и. подсчитывается третьим счетчиком 32, содержимое которого увеличивается HP. единицу, а также поступает на упраг.ляющий вход блока

- 5 выборки и хранения, переводя его в режим выборки и запоминания мгно-

5 выборки и хранения, переводя его в режим выборки и запоминания мгно-

венного значения выходного напряжения интегратора 4, являющегося результатом первого цикла работы устройства

ь. и:К, 5дС,Е,.(.-Т,, ,

г-1ь 1

и„ 1 - йСк-СГ е )1(5)

.

и

Задним фронтом указанного (второ- То) выходного импульса нуль-органа 8, кроме того, четвертый триггер 30

В режиме однократных времяимпульсПо счетному входу устанавливается в

Положение 1, при этом потенциал 1 jg ных сигналов, подаваемых на первый

с его инверсного выхода снимается (восьмой элемент И 29 блокируется) и появляется на прямом выходе (фиг. 2м), открывая седьмой элемент И 28, Через этот элемент в конде первого такта второго дикла работы устройства пройдет следующий (третий) выходной импульс нуль-органа 8 (фиг. 2к), который задним фронтом вернет четвертый триггер 30 в положение О, при .этом потенциал 1 с прямого в гхода четвертого триггера 30 будет .снят (седьмой элемент И 29 блокируется) и появится на инверсном выходе (фиг. 2л)5 открывая восьмой элемент И 29, чере который в конце второго такта данного цикла пройдет следующий (четвертый) выходной импульс нуль орга- на 8 (фиг. 2и), и т.д. образом,

и второй информационные входы ЗА и 35 устройства (фиг, 2а, б), на входе 15 установки режима работы потенциала 1, подготавливающий первый, рой, третий и четвертый элементы И 12, 13, 24 и 25 (фиг. 2ж). Второй и первый элементы И 13 и 12, открытые на время Т и. Т, соответственно,пропускают тактовые импульсы генератора 14 на счетные входы второго и первого счетчиков 17 и 16 (фиг. 2д, е), оторые путем подсчета этих ймпульСов формируют коды, пропорциональные Tg и Т соответственно. Остальные опера25 дии первого цикла работы устройства для двух исходных времяимпульсных сигналов (фиг. 2а, б) аналогичны рассмот- реным в. первом режиме: на время Т

20

минающего конденсатора 7, а затем (после установки третьего ключа 3 в замкнутое положение потендиалом 1

устанавливается в замкнутое положение

восьмой элемент И 29 селектирует чет- -jg третий kлюч 6, начинается заряд запо- ные выходные импульсы нуль-органа 8, каждый из Которых фиксирует окончание соответствующего цикла работы устройства (фиг. 2и).

Второй и последующие циклы работы устройства осуществляются аналогично

После п циклов работы устройства, подсчитав очередной импульс с выхода восьмого элемента И 29, третий счет40

чик 32 переполнится, потенциал на его входе переполнения скачком изменится 5° уровня логического О (фиг. 2ф) и заблокирует первый и второй элементы 2И-ИЛИ 37 и 38. Измерительно-вычислительный процесс на этом с заканчивается, а на выходе 36 устройства аналогично (5) фиксируется напс выхода первого триггера 9) его раз- ,„ ряд до момента достижения напряжением нулевого значения и т.д. После первого- цикла работы устройство переходит к формированию собственных времянмпульсных сигналов с той же длительностью (Т чтобы обеспечить измерительно-вычислительньй процесс в последующих циклах работы.

Второй импульс нуль-органа 8 (фиг. 2г), или первый с выхода блока 31 (фиг. 2в), появляющийся на выходе восьмого элемента И 29 (фиг. 2и) и

ряжение

.«.,.f §;-- - Ф

, , - .. (, -,-% )-,

.„.,.К.. (,./..,

при выполнении условия

Ii

« г Сп

-(1 - е

)

приводится к следу-ющему виду

вых .ll-S ивыхСп) Е l-:-E5EillL/SL .

(7)

о 1 - ехрС-Тг/Т)

Выражение (7) является уравнением преобразования устройства.

В режиме однократных времяимпульсных сигналов, подаваемых на первый

ных сигналов, подаваемых на первый

второй информационные входы ЗА и 35 устройства (фиг, 2а, б), на входе 15 установки режима работы потенциаа 1, подготавливающий первый, второй, третий и четвертый элементы И 12, 13, 24 и 25 (фиг. 2ж). Второй и первый элементы И 13 и 12, открытые на время Т и. Т, соответственно,пропускают тактовые импульсы генератора 14 на счетные входы второго и первого счетчиков 17 и 16 (фиг. 2д, е), оторые путем подсчета этих ймпульСов формируют коды, пропорциональные Tg и Т соответственно. Остальные операдии первого цикла работы устройства для двух исходных времяимпульсных сигналов (фиг. 2а, б) аналогичны рассмот- реным в. первом режиме: на время Т

минающего конденсатора 7, а затем (после установки третьего ключа 3 в замкнутое положение потендиалом 1

-jg третий kлюч 6, начинается заряд запо

третий kлюч 6, начинается заряд запо-

с выхода первого триггера 9) его раз- ряд до момента достижения напряжением нулевого значения и т.д. После первого- цикла работы устройство переодит к формированию собственных времянмпульсных сигналов с той же длительностью (Т чтобы обеспечить измерительно-вычислительньй процесс в последующих циклах работы.

Второй импульс нуль-органа 8 (фиг. 2г), или первый с выхода блока 31 (фиг. 2в), появляющийся на выходе восьмого элемента И 29 (фиг. 2и) и

фиксирующий окончание первого цикла работы устройства, проходит далее через четвертый элемент И 25 и, поступая на управляющий вход второго вычитающего счетчика 19, разрешает пе- . резапись в него содержимого второго

счетчика 17, а также устанавливает третий триггер 23 в положение 1,при котором потенциал 1 с его прямого выхода (фиг. 2н) открывает шестой элемент И 27, и тактовые .импульсы генератора 14 через этот элемент начи7. 13

нают поступать на счетный вход вто- рого вычитающего счетчика 19 (фиг.2о) описывая его содержимое. В момент .времени, соответствующий обнулению второго вычитающего счетчика 19, ераёатывает второй дешифратор 21, импульс с выхода которого (фиг. 2п) воз ,вращает третий триггер 23 в исходное положение О. Таким образом, на выходе указанного триггера формируется времяимпульсный сигнал (фиг. 2н), как бы имитирующий второй из периодически повторяющихся сигналов предыдущего режима, который через второй элемент 2И-ИЛИ 38 и элемент ИЛИ поступает на первый триггер 9 (фиг.2у и управляющий вход третьего ключа 6, устанавливая его в замкнутое положение и задавая последовательность опе

Вычислительное устройство, содержащее соединенные последовательно источник опорного напряжения, первый и второй ключи, интегратор, блок выборки и хранения, выход которого является выходом вычислительного уст- ррйства, запоминающий конденсатор, первая обкладка которого подключена к выходу первого ключа, выход блока выборки и хранения соединен с информационным входом третьего ключа, выход которого подключен к первой обкладке запоминающего конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, элемент ИЛИ, первый и второй входы которого соединены соответственно с.управляючеи, отличающееся тем, что, с целью повышения быстродей-;- ствия и расш1репия области менения, в него введены нуль-орган, первый, второй, третий и четвертьш триггеры, генератор импульсов, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой элементы И, первый, второй и третий счетраций, характерную для первого такта 20 %1ми входами первого и третьего клю- второго цикла работы устройства. Третий импульс нуль-органа 8 (фиг. 2г) или второй с выхода блока 31 (фиг. Зз), появляющийся на выходе седьмого элемента И 28 (фиг. 2к) и 25 фиксирующий окончание первого такта второго 1щкла работы устройства, проходит далее через третий элем ент И 24 и, поступая на управляющий вход первого вычитающего счетчика 18, раз-30 чики, первый и второй вычитающие счет- решает перезапись в него содержимого первого счетчика 16, а также устанавливает второй триггер 22 в положение 1,- при котором потенциал 1 с его прямого выхода (фиг. 2р) открывает 35 пятый элемент И 26, и тактовые импульсы генератора 14 через этот элемент начинают поступать на счетный вход первого вычитающего счетчика 18 (фиг. 3с), описывая его содержимое. 40

чики, первый и второй дешифраторы, первый и .второй элементы 2И-1-ШИ,блок запрета прохождения первого импульса, причем выход первого ключа соединен с первым входом нуль-органа, второй вход которого подключен к шине нулевого потенциала, выход нуль-органа соединен с единичным входом первого триггера, к входу установки в О которого подключен выход элемента ИЛИ, прямой выход первого триггера соединен с управляющим входом второго ключа, первый вход первого элемента И является первьм информационным вхоВ момент времени, соответствующий обнулению первого вычитающего счетчика 18, срабатывает первый дешифратор 20, импульс с выхода которого (фиг.2т) возвращает второй триггер 22 в исход- дом устройства и соединен с первым ное положение О. Таким образом, на входом первого элемента 2И-ИЛИ, выход выходе указанного триггера формируется время-импульсньй сигнал (фиг. 2р) как бы имитирующий второй из периокоторого подключен к первому входу . элемента ИЛИ, первый вход второго элемента И является вторым информадически повторяющихся сигналов пре- 50 ционным входом устройства и соединен дыдущего ре;кима, который через первый элемент 2И-1ШИ 37 и элемент ИЛИ 10 поступает на первый триггер 9 (фиг. 2у) и управляющий вход первого ключа 2, устанавливая его в замкнутое55 входами первого и второго элементов положение и, задавая последовательность . операций,характернуюдля второго такта- второго цикла работы устройства.

с первым входом второго элемента 2И- ИЛИ, выход которого подключен к второму входу элемента ИЛИ, выход генератора импульсов соединен с вторыми

И и с первыми входами пятого и шесто- го элементов И, третьи входы первого и второго элементов И соединены соотрмула изобретения

Вычислительное устройство, содержащее соединенные последовательно источник опорного напряжения, первый и второй ключи, интегратор, блок выборки и хранения, выход которого является выходом вычислительного уст- ррйства, запоминающий конденсатор, первая обкладка которого подключена к выходу первого ключа, выход блока выборки и хранения соединен с информационным входом третьего ключа, выход которого подключен к первой обкладке запоминающего конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, элемент ИЛИ, первый и второй входы которого соединены соответственно с.управляючеи, отличающееся тем, что, с целью повышения быстродей-;- ствия и расш1репия области менения, в него введены нуль-орган, первый, второй, третий и четвертьш триггеры, генератор импульсов, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой элементы И, первый, второй и третий счет%1ми входами первого и третьего клю- чики, первый и второй вычитающие счет-

%1ми входами первого и третьего клю- чики, первый и второй вычитающие счет-

чики, первый и второй дешифраторы, первый и .второй элементы 2И-1-ШИ,блок запрета прохождения первого импульса, причем выход первого ключа соединен с первым входом нуль-органа, второй вход которого подключен к шине нулевого потенциала, выход нуль-органа соединен с единичным входом первого триггера, к входу установки в О которого подключен выход элемента ИЛИ, прямой выход первого триггера соединен с управляющим входом второго ключа, первый вход первого элемента И является первьм информационным входом устройства и соединен с первым входом первого элемента 2И-ИЛИ, выход

дом устройства и соединен с первым входом первого элемента 2И-ИЛИ, выхо

которого подключен к первому входу . элемента ИЛИ, первый вход второго элемента И является вторым информационным входом устройства и соединен входами первого и второго элементов

с первым входом второго элемента 2И- ИЛИ, выход которого подключен к второму входу элемента ИЛИ, выход генератора импульсов соединен с вторыми

ционным входом устройства и соединен входами первого и второго элементов

И и с первыми входами пятого и шесто- го элементов И, третьи входы первого и второго элементов И соединены соответственно с первыми входами третьего и четвертого элементов И и являются входом установки режима работы устройства, выходы третьего и четвертого элементов И подключены к единичным входам соответственно второго и третьего триггеров, прямые выходы которых Соединены соответственно с вторыми входами, пятого и шестого элементов И, выходы первого и второго элементов И подключены к счетным входам соответственно первого и второго счетчиков , выходы которых соединены с информационными входами разрядов соответственно первого и второго вычитающих счетчиков, выходы которых подключены к входам соответственно первого и второго дешифраторов, выход первого дешифратора соединен с входом установки в О второго триггера, выход второго дешифратора соединен с входом установки в О третьего триггера, выходы пятого и шестого элементов И подключены к счетным входам соответственно первого и второго вычитающих счетчиков, входы запуска которых соединены с выходами соответст

5

0

5

венно третьего и четвертого элементов И, вторые входы которых подключены к выходам соответственно седьмого и восьмого элементов И, первые входы которых подключены к счетному входу четвертого триггера, прямой и инверсный выходы которого соединены с вторыми входами соответственно седьмого и восьмого элементов И, выход восьмого И подключен к счетному входу третьего счетчика и к управляющему входу блока выборки и хранения, вторые и четвертые входы первого и второго элементов 2И-ИЛИ соединены с выходом переполнения третьего счетчика, третьи входы первого и второго элементов 2И-ИЛИ подключены к прямым выходам соответственно второго и третьего триггеров, выход нуль-органа соединен с входом блока запрета прохождения первого импульса, выход которого подключен к счетному входу четвертого триггера, информационные входы разрядов третьего счетчика являются входами установки числа циклов работы устройства.

Редактор В.Данко

Составитель О.Отраднов

Техред В.Кадар Корректор И.Муска

Заказ.1454/48Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947958A1 |

| Устройство для контроля электромагнита | 1986 |

|

SU1348776A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Интегрирующий аналого-цифровой преобразователь с автоматической коррекцией погрешности | 1984 |

|

SU1334372A1 |

| Способ детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи и устройство для его осуществления | 1991 |

|

SU1793461A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Способ определения температуры и влажности воздуха и устройство для его осуществления | 1990 |

|

SU1783400A1 |

| Устройство для определения одномерных начальных моментов К-го порядка случайного сигнала | 1983 |

|

SU1108464A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобр е- тения является повьшение быстродействия и расширение области применения за счет возможности работы с одиночными времяимпульсными сигналами. Вычислительное устройство содержит источник 1 опорного напряжения, первый, второй и третий ключи 2, Зиб, интег(Л u

| Функциональный преобразователь | 1977 |

|

SU679997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-25—Подача