Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи цифровых данных.

Цель изобретения - повьппенке точности преобразования.

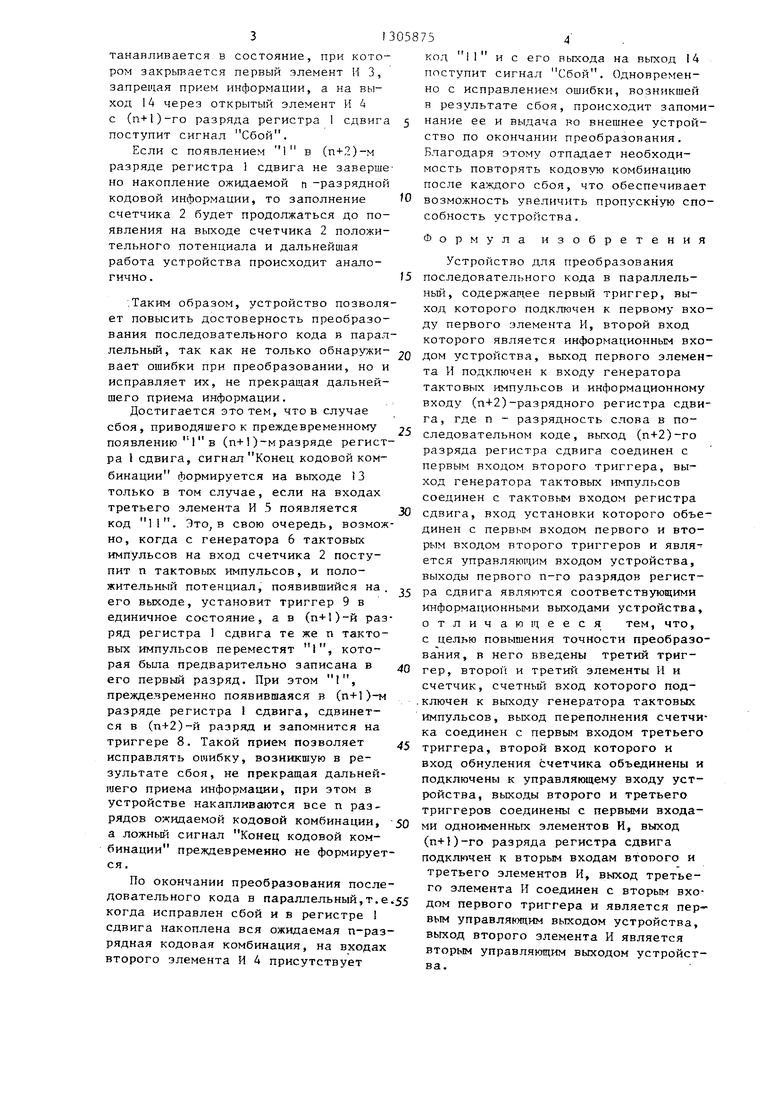

На чертеже приведена функциональная схемч устройства.

Устройство для преобразования последовательного кода в параллельный содержит регистр 1 сдвига, счетчик 2, nepBbtfi, второй и третий элементы И 3-5, генератор 6 тактовых импульсов, первый, второй и третий триггеры 7-9. На чертеже обозначены информационный О и управляющий 11 входы, информдпионные выходы 12, первый 13 и второй 14 управляющие выходы,

Регистр 1 сдвига выполнен (п+2)- разрядньм, где п - длина слова в последовательном коде.

Счетчик 2 имеет емкость п-1,т.е. сигнал на его выходе переполнения появляется при поступлении п-го импульса на вход счетчика 2.

На чертеже приведен вариант подключения триггеров 7-9, в котором их первыми входами являются S-входы, а вькодами - прямые выходы. В случае, если первыми входами триггеров 7-9 являются их R-входь, то в качестве выходов используются их инверсные выходы,

Устройство для преобразования последовательного кода в параллельный работает следующим образом

На вход 11 поступает управ1шющий сигнал, свидетельствующий о начале сообщения. По этому сигналу обнуляется счетчик 2, триггеры 8 и 9 и вс кроме первого, разряды регистра 1 - сдвига, а в первый разряд этого регистра записывается единица;, кроме того, перебрасывается в единично состояние триггер 7. В отсутствие кодового слова на информационном входе О присутствует уровень логической единицы. Благодаря этому при перебросе триггера 7 по сигналу с входа 1 на вход генератора 6 поступает положительный перепад, которым запускается генератор 6. Единичные импульсы входного слова осуществляю синхронизацию работы этого генератора 6 . По мере поступления кодовых импульсов с входа 10 регистр 1 сдвига осуществляет прием поступающей

0

информации, а тактовь е импульсы с генератора 6 тактовых импульсов заполняют счетчик 2.

В случае приема ожидаемых п разрядов последовательного кода без сбоя по окончании преобразования в (п+1)-1 разряд регистра 1 сдвига записывается 1, а на выходе счетчика 2 появляется положительный потенциал, которьш устанавливает триггер 9 в единичное состояние. Триггер 9 формирует сигнал разрешения, открывающий третий элемент И 5, и с (п+1)-го разряда регистра 1 сдвига через открытый элемент И 5 на выход 13 поступает сигнал Конец кодовой комбинации. Этим же сигналом триггер 7 устанавливается в состояние, при котором закрывается первый элемент И 3,

запрещая прием информации.

1

Если в процессе сдвига единицы, предварительно записанной в первый разряд регистра 1 сдвига, в этом ре5 гистре происходит сбой, приводящий к преждевременному появлению 1 в (n-t-l)-M разряде, то сигнал Конец кодовой комбинации на выходе 13 не формируется, так как на счетчик 2 не поступает п тактовых импульсов и элемент И 5 закрыт выходным сигналом триггера 9. При этом генератор 6 тактовых импульсов продолжает вырабатывать тактовые и шyльcы, так как первый элемент И 3 открыт и поступление кодовых импульсов с входа 10 не закончилось. Поэтому сдвиг информации в регистре 1 сдвига и заполнение счетчика 2 продолжается. При появлении 1 в (п-«-2)-м разряде регистра 1 сдвига триггер 8 устанавливается в единичное состояние и формирует на входе второго элемента И 4 сигнал разрешения. Если к этому моменту в

5 регистре 1 сдвига заверщено накопление ожидаемой п-разрядной кодовой комбинации, то на выходе счетчика 2 появится положительный потенциал, а в (п+)-м разряде регистра 1 сдвига

Q ПОЯВИТСЯ та I, которая была предварительно записана в его первый разряд и сдвигалась по мере накопления информации.

Триггер 9 устанавливается в еди ничное состояние и формирует сигнал на входе элемента И 5, разрешающий прохождение с ()-го разряда регистра 1 сдвига появившейся 1 на выход 13 и триггер 7. Триггер 7 ус0

5

0

313

тананливается в состояние, при котором закрывается первый элемент И 3, запрещая прием информации, а на выход 14 через открытый элемент И 4 с (п+1)-го разряда регистра 1 сдвига поступит сигнал Сбой.

Если с появлением 1 в (п+2)-м разряде регистра 1 сдвига не завершено накопление ожидаемой ti -разрядной кодовой информации, то заполнение счетчика 2 будет продолжаться до появления на выходе счетчика 2 положительного потенциала и дальнейшая работа устройства происходит аналогично.

.Таким образом, устройство позволяет повысить достоверность преобразования последовательного кода в параллельный, так как не только обнаружи- вает ошибки при преобразовании, но и исправляет их, не прекращая дальнейшего приема информации.

Достигается это тем, ЧТОБ случае сбоя, приводящего к преждевременному появлению 1 в (п+1)-мразряде регистра 1 сдвига, сигнал Конец кодовой комбинации формируется на выходе 3 только в том случае, если на входах третьего элемента И 5 появляется код П. Это, в свою очередь, возможно, когда с генератора 6 тактовых импульсов на вход счетчика 2 поступит п тактовых импульсов, и положительный потенциал, появившийся на. его выходе, установит триггер 9 в единичное состояние, а в ()-й разряд регистра 1 сдвига те же п тактовых импульсов переместят 1, которая была предварительно записана в его первый разряд. При этом 1, преждевременно появившаяся в (п+1)-м разряде регистра I сдвига, сдвинется в (п+2)-й разряд и запомнится на триггере 8. Такой прием позволяет исправлять ошибку, возникшую в результате сбоя, не прекращая дальнейшего приема информации, при этом в устройстве накапливаются все п разрядов ожидаемой кодовой комбинации, а ложный сигнал Конец кодовой комбинации преждевременно не формируется,

По окончании преобразования последовательного кода в параллельный,т.е когда исправлен сбой и в регистре 1 сдвига накоплена вся ожидаемая п-раз рядная кодовая комбинация, на входах второго элемента И 4 присутствует

754

код 11 и с его выхода на выход 14 поступит сигнал Сбой. Одновременно с исправлением ошибки, возникшей н результате сбоя, происходит запоминание ее и выдача во внешнее устройство по окончании преобразования. Благодаря этому отпадает необходимость повторять кодовую комбинацию после каждого сбоя, что обеспечивает возможность увеличить пропускную способность устройства.

Формула изобретения

Устройство для преобразования последовательного кода в параллельный, содержащее первый триггер, выход которого подключен к первому входу первого элемента И, второй вход которого является информационным входом устройства, выход первого элемента И подключен к входу генератора тактовых импульсов и информационному входу (п+2)-разрядного регистра сдвига, где п - разрядность слова в последовательном коде, выход (п+2)-го разряда регистра сдвига соединен с первым входом второго триггера, выход генератора тактовых и тульсов соединен с тактовым входом регистра сдвига, вход установки которого обье- динен с первым входом первого и вторым входом второго триггеров и является управляющим входом устройства, выходы первого п-го разрядов регистра сдвига являются соответствующими информационными выходами устройства, отличающееся тем, что, с целью повышения точности преобразования, в него введены третий триггер, второй и третий элементы 1 и счетчик, счетный вход которого под- .ключей к выходу генератора тактовых импульсов, выход переполнения счетчика соединен с первым входом третьего триггера, второй вход которого и вход обнуления счетчика объединены и подключены к управляющему входу устройства, выходы второго и третьего триггеров соединены с первыми входами одноименных элементов И, выход (п+{)-го разряда регистра сдвига подключен к вторым входам ВТОРОГО и третьего элементов И, выход третьего элемента И соединен с вторым входом первого триггера и является первым управляющим выходом устройства, выход второго элемента И является вторым управляющим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования последовательного кода в параллельный | 1986 |

|

SU1417193A1 |

| Динамический шифратор позиционного кода | 1988 |

|

SU1545328A1 |

| Устройство для преобразования последовательного кода в параллельный | 1990 |

|

SU1790032A1 |

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Устройство для преобразования последовательного кода в параллельный | 1986 |

|

SU1403378A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418912A1 |

| Устройство для преобразования последовательного кода в параллельный | 1985 |

|

SU1297234A1 |

| Преобразователь кодов | 1988 |

|

SU1649676A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство слежения за задержкой кодовой последовательности | 1985 |

|

SU1338093A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи цифровых данных позволяет повысить точность преобразования. Устройство содержит регистр I сдвига, элемент ИЗ, триггеры 7,8 и генератор 6 тактовых 1шпульсов. Введение счетчика 2, триггера. 9 и элементов И 4,5 обеспечивает исправление ошибки, возникающей в процессе преобразования вследствие сбоя в регистре 1 сдвига. 1 ил. 13 с сл со о сл 00 C7I

| Устройство для преобразования после-дОВАТЕльНОгО КОдА B пАРАллЕльНый | 1979 |

|

SU809160A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-23—Публикация

1985-08-13—Подача