Изобретение относится к вычислительной технике, а именно к технике преобразования .информации, и может быть использовано в системах передачи данных по цифровым каналам для преобразования последовательного кода в параллельный,

Целью изобретения является повьше- ние достоверности преобразуемой информации за счет контроля ее потерь.

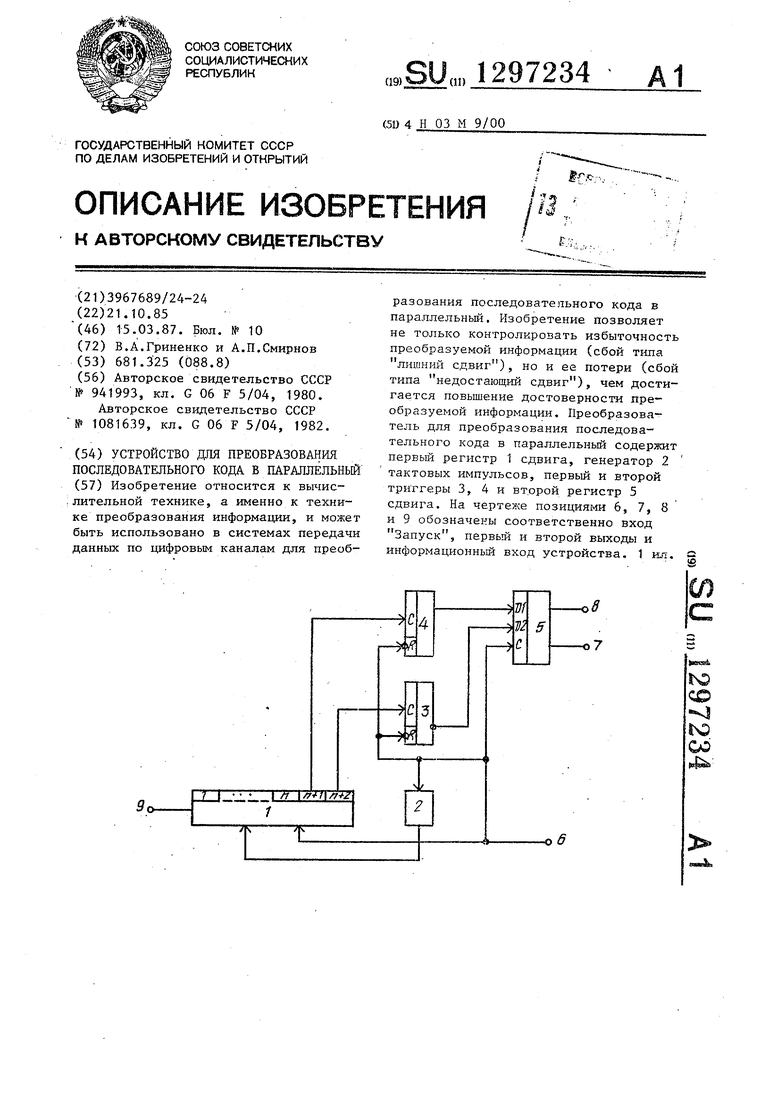

На чертеже представлена структурная схема устройства для преобразования последовательного кода в параллельный .

Устройство содержит первьй регистр )5 ся в регистр 5 и с первого и второго

информационных выходов поступает на второй выход 8 и на первый выход 7, Код 10 на выходах 7 и 8 сигнализи1 сдвига, генератор 2 тактовых импульсов, первый и второй триггеры 3 и 4 и второй регистр 5 сдвига. На чертеже обозначены соответственно вход

6 Запуск, первьй и второй выходы 20

7и 8 и информационный вход 9 устройства.

Устройство работает следующим образом.

На вход 6 поступает сигнал, кото- 25 дов не появляется. При этом триггеры рый записывает 1 в первьш разряд 3 и 4 остаются в нулевом состоянии регистра 1 сдвига, а в остальные раз- и ряды - О, переписьшает содержимое триггеров 3,4 в регистр 5, устанавливает триггеры 3 и 4 в исходное (ну- 30 в регисРгр 5, а с его выходов поступа- левое) состояние и запускает генера- ет на.выходы 7 и 8, при этом на пос- тор 2 тактовых импульсов, выходные импульсы с которого поступают на так- товьй вход регистра 1 сдвига. По мере

рует о сбое типа лишний сдвиг. При сбое типа недостающий сдвиг на одли или более тактов тактовой частоты 1, предварительно записанная в первьш разряд регистра 1 сдвига, на выходах (п+1)-го и (п+2)-го разряс приходом следующего сигнала с входа 6 код 01 с соответствующих выходов триггеров 3 и 4 записывается

ледних также присутствует код 01, сигнализирующий о сбое типа недостающий сдвиг.

35

поступления кодовых импульсов произвольной последовательности по входу 9 регистр 1 осуществляет прием поступающей информации,. В случае приема ожидаемых п-разрядов последовательного кода без сбоя в (п+1)-ом (предпос-40 содержащее первый регистр сдвига, ге- леднем) и в (п+2)-ом (последнем) раз- нератор тактовых импульсов и тригге- рядах оегистра 1 оказывается записанным код 10, появившись в (п+1)-ом разряде регистра 1 сдвига, он поступает на вход синхронизации триггера 45 пуск устройства, выход генератора 4 и передним фронтом устанавливает его вьпсод , так как на D-входах триггеров 3,4, зафиксирован сигнал 1 (не показано), а на выходе тригФормула изобретения

Устройство для преобразования последовательного кода в параллельньш,

ра, входы установки нуля которых объединены с входом записи первого регистра сдвига и являются входом Затактовых импульсов соединен с тактовым входом первого регистра сдвига, выход последнего разряда которого соединен с выходом синхронизации пергера 4 осталось исходное (единичное) 50 вого триггера, от личающе- состояние, С приходом следйпощего сигнала по входу 6 уровни сигналов, находящиеся на выходах триггеров 3 и 4, переписываются в регистр 5, На выходных шинах 7 и 8 появляется код 11, свидетельствующий о правильном приеме информации.

Если в процессе сдвига 1, предварительно записанной в первый разряд

е с я тем, что, с целью повышения достоверности преобразуемой информа- щш за счет контроля ее потерь, в него введен второй регистр сдвига, 55 первый и второй выходы которого являются соответственно первым и вторым выходами устройства, выход предпоследнего разряда первого регистра сдвига соединен с входом синхрониза1297234

регистра 1 сдвига, в последнем происходит сбой типа лишний сдвиг, то 1 перемещается с (п+1)-го разряда регистра 1 сдвига в (п+2)-й разряд или далее (при сбое более чем на один такт тактовой частоты). При этом, проходя через (п+1)-й разряд, 1 устанавливает триггер 4 в единичное состояние, а проходя через (п+2)-й разряд устанавливает триггер 3 в единичное состояние. С приходом следующего сигнала по входу 6 потенциал 1 с прямого выхода триггера 4 и инверсного выхода триггера 3 переписываетинформационных выходов поступает на второй выход 8 и на первый выход 7, Код 10 на выходах 7 и 8 сигнализирует о сбое типа лишний сдвиг. При сбое типа недостающий сдвиг на одли или более тактов тактовой частоты 1, предварительно записанная в первьш разряд регистра 1 сдвига, на выходах (п+1)-го и (п+2)-го разрядов не появляется. При этом триггеры 3 и 4 остаются в нулевом состоянии и в регисРгр 5, а с его выходов поступа- ет на.выходы 7 и 8, при этом на пос-

с приходом следующего сигнала с входа 6 код 01 с соответствующих выходов триггеров 3 и 4 записывается

дов не появляется. При этом триггеры 3 и 4 остаются в нулевом состоянии и в регисРгр 5, а с его выходов поступа- ет на.выходы 7 и 8, при этом на пос-

ледних также присутствует код 01, сигнализирующий о сбое типа недостающий сдвиг.

35

40 содержащее первый регистр сдвига, ге- нератор тактовых импульсов и тригге- 45 пуск устройства, выход генератора

Формула изобретения

Устройство для преобразования последовательного кода в параллельньш,

содержащее первый регистр сдвига, ге- нератор тактовых импульсов и тригге- пуск устройства, выход генератора

ра, входы установки нуля которых объединены с входом записи первого регистра сдвига и являются входом Засодержащее первый регистр сдвига, ге- нератор тактовых импульсов и тригге- пуск устройства, выход генератора

тактовых импульсов соединен с тактовым входом первого регистра сдвига, выход последнего разряда которого соединен с выходом синхронизации пер50 вого триггера, от личающе-

е с я тем, что, с целью повышения достоверности преобразуемой информа- щш за счет контроля ее потерь, в него введен второй регистр сдвига, 55 первый и второй выходы которого являются соответственно первым и вторым выходами устройства, выход предпоследнего разряда первого регистра сдвига соединен с входом синхрониза312972344

ции второго триггера, выход которогорого объединен с входом генератора соединен с первым информационным вхо-тактовых импульсов и соединен с входом второго регистра сдвига, инверс-дом Зайуск устройства, информационный выход первого триггера соединенный вход первого регистра сдвига яв- с вторым информационным входом второ- 5ляется информационным входом устрой- го регистра сдвига, вход записи кото-ства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля и аргумента вектора | 1985 |

|

SU1249510A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Устройство преобразования параллельного кода в последовательный | 1987 |

|

SU1474853A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Устройство для преобразования последовательного кода в параллельный | 1990 |

|

SU1790032A1 |

| Устройство для преобразования последовательного кода в параллельный | 1988 |

|

SU1520668A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1983 |

|

SU1156057A1 |

| Преобразователь кодов | 1988 |

|

SU1649676A1 |

| Преобразователь напряжения в код | 1987 |

|

SU1427568A1 |

Изобретение относится к вычис; лительной технике, а именно к технике преобразования информации, и может быть использовано в системах передачи данных по цифровым каналам для преобразования последовательного кода в параллельньш. Изобретение позволяет не только контролировать избыточность преобразуемой информации (сбой типа лишнтш сдвиг), но и ее потери (сбой типа недостающий сдвиг), чем достигается повышение достоверности преобразуемой информации. Преобразователь для преобразования последовательного кода в параллельный содержит первьш регистр 1 сдвига, генератор 2 тактовых импульсов, первый и второй триггеры 3, 4 и второй регистр 5 сдвига. На чертеже позициями 6, 7, 8 и 9 обозначены соответственно вход Запуск, первый и второй выходы и информационный вход устройства. 1 ил. 1C го со -.J К5. СО

| Преобразователь последовательного кода в параллельный | 1980 |

|

SU941993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для преобразования последовательного кода в параллельный | 1982 |

|

SU1081639A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-21—Подача