Изобретение относится к электросвязи и может быть использовано при испытании аппаратуры линейного тракта цифровых систем передачи, паспортизации регенераторов и их выходного контроля.

Цель изобретения - повышение точности испытания.

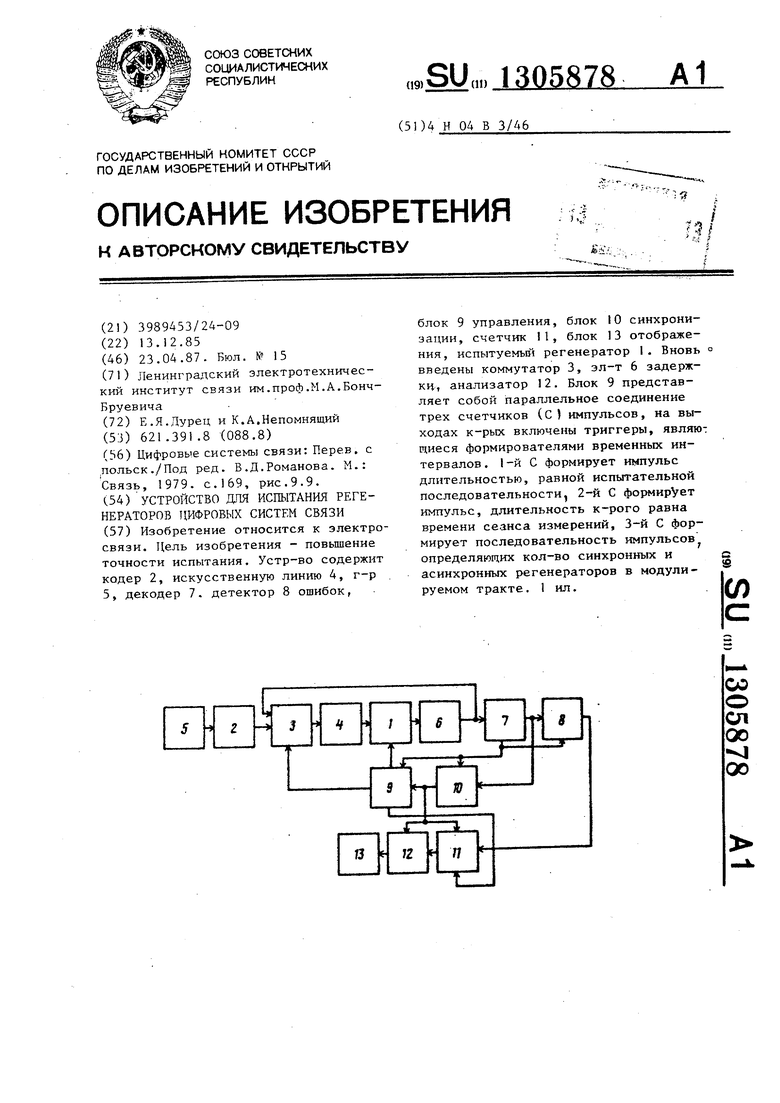

На чертеже представлена структурная электрическая схема устройства для испытания регенераторов цифровых систем связи.

Устройство содержит испытуемый регенератор 1, кодер 2, коммутатор 3,15 искусственную линию 4, генератор 5, элемент 6 задержки, декодер 7, детектор 8 ошибок, блок 9 управления, блок 10 синхронизации, счетчик 11, анализатор 12 и блок 13 отображения. 20

Устройство работает следующим образом.

Двоичный испытательный сигнал с выхода генератора 5 через кодер 2 поступает на вход коммутатора 3, с 25 выхода которого линейньй сигнал подается на вход искусственной линии 4. Там он искажается за счет воздействия тепловых шумов и межсимвольных искажений и поступает на вход испыту- ЗО емого регенератора . С выхода испытуемого регенератора 1 восстановленный линейный сигнал через элемент 6 задержки подается на вход декодера . 7.

а также детектора 8 ошибок на их ответствуюп1ие входы подается напр жение тактовой частоты с выхода д кодера 7. Элемент 6 задержки пред назначен для задержки сигнала на время, равное разности длительнос цикла испытательного сигнала и вр мени распространения сигнала в ко таторе 3, искусственной линии 4 и пытуемого регенератора I. Детекто ошибок производит выявление ошибо декодированном сигнале, число кот рых подсчитывается счетчиком 11. I

Работа счетчика I1 возможна то ко во время прохож,цения цикла исп тельного сигнала, для чего на его разрешающий вход подается сигнал выхода блока 9 управления длитель ностью равной периоду испытательн го сигнала, и сформированный из им пульса с выхода блока 10 синхрони ции. Этим же импульсом производит запись числа выявленных ошибок в анализатор 12 после анализа каждо цикла испытательного сигнала, а т же производится обнуление счетчик II после каждого такого цикла.

Таким образом, после проведени испытаний в анализаторе 12 хранит информация, характеризующая число ошибок в каждом из i измерений, где i - общее число циклов измерен

После проведен} я испытаний в з

анализатор I2 может вычислять час ность ошибок в i-M регенераторе I которая равна разности числа ошибо на i-M цикле измерений и i-1-н чис деленной на число символов в J-M цикле испытательной последовательности,, согласно выражению

от- i

N.

выхода которого восстановленный ,-- - .

j- висимости от требуемой информации двоичньи испытательный сигнал поступает на вход детектора 8 ошибок и на вход блока 10 синхронизации, в котором осуп ествляется выделение импульса, характеризующего начало цик- 40 ла испытательной последовательности. Этот импульс поступает на вход блока 9 управления, который вырабатывает сигнал управления работой коммутатора 3, который производит отключение 45 выхода кодера 2 от входа искусственной линии 4 и подключает выход элемента 6 задержки к входу искусственной линии 4 на время испытаний, которое пропорционально числу регенера-50 коэффициент ошибки равен Р торов в модулируемом тракте. Кроме того, блок 9 управления вырабатьша- ет сигнал управления регенератором, который определяет структуру регенератора и количество асинхронных ре- ,5 генераторов, включенных между двумя

СИНХрОННЬЕМИ.

Кроме того, анализатор 12 вычи ляет общий коэффициент ошибок для всего модулируемого тракта, при э

NE

OU1

N

где Ng - суммарное количество оши

N

- общее количество контрол руемых позиций испытател ного сигнала. Вычисленные коэффициенты ошиб выводятся на блок 13 отображения.

Для синхронной работы блока 9 управления и блока 10 синхронизации.

5 0

5 О

а также детектора 8 ошибок на их со- ответствуюп1ие входы подается напряжение тактовой частоты с выхода декодера 7. Элемент 6 задержки предназначен для задержки сигнала на время, равное разности длительности цикла испытательного сигнала и времени распространения сигнала в коммутаторе 3, искусственной линии 4 и испытуемого регенератора I. Детектор 8 ошибок производит выявление ошибок в декодированном сигнале, число которых подсчитывается счетчиком 11. I

Работа счетчика I1 возможна только во время прохож,цения цикла испытательного сигнала, для чего на его разрешающий вход подается сигнал с выхода блока 9 управления длительностью равной периоду испытательного сигнала, и сформированный из импульса с выхода блока 10 синхронизации. Этим же импульсом производится запись числа выявленных ошибок в анализатор 12 после анализа каждого цикла испытательного сигнала, а также производится обнуление счетчика II после каждого такого цикла.

Таким образом, после проведения испытаний в анализаторе 12 хранится информация, характеризующая число ошибок в каждом из i измерений, где i - общее число циклов измерение

После проведен} я испытаний в - .

анализатор I2 может вычислять частность ошибок в i-M регенераторе I, которая равна разности числа ошибок на i-M цикле измерений и i-1-н числе, деленной на число символов в J-M цикле испытательной последовательности,, согласно выражению

висимости от требуемой информации коэффициент ошибки равен Р

от- i

N.

ти от требуемо иент ошибки ра

исимости от требуемой информации коэффициент ошибки равен Р

Кроме того, анализатор 12 вычисляет общий коэффициент ошибок для всего модулируемого тракта, при этом

тре оши

NE

ти от т иент ош

OU1

N

висимости от требуемой информации коэффициент ошибки равен Р

где Ng - суммарное количество ошибок;

исимости от требуемой информации коэффициент ошибки равен Р

N

- общее количество контролируемых позиций испытательного сигнала. Вычисленные коэффициенты ошибок выводятся на блок 13 отображения.

Блок управления представляет собой параллельное соединение трех счетчиков импульсов, на выходах которых включены триггеры, являющиеся формирователями временных интервалов. Пер- вый счетчик формирует импульс длительностью, которая равна испытательной последовательности; второй счетчик формирует импульс, длительность которого равна времени сеанса изме- рений; третий счетчик формирует последовательность импульсов, определяющих количество синхронных и асинхронных регенераторов в модулируемом тракте, при этом при поступлении на вход регенератора импульсов с выхода третьего счетчика производится отключение блока вьделителя тактовой частоты в регенераторе 5, т.е. он переводится в режим асинхронной регене- рации.

Формула изобретения

Устройство для испытания регене- раторов цифровых систем связи, содержащее блок отображения, генератор, кодер, искусственную линию, детектор ошибок, блок управления, счетчик и последовательно соединенные декодер

Составитель В.Камалягин Редактор А.Шандор Техред В.Кадар Корректор Л.Патай

Заказ 1466/56 Тираж 639Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

и блок синхронизации, при- этом выход генератора подключен к входу кодера, а первый выход блока управления подключен к первому входу счетчика, отличающееся тем, что, с целью повышения точности испытания, введены анализатор, элемент задержки и коммутатор, первый вход которого соединен с выходом кодера, второй вход соединен с выходом элемента задержки и входом декодера, третий вход соединен с вторым выходом блока управления, а выход - через последовательно соединенные искусственную линию, испытуемый регенератор подключен к входу элемента задержки, третий выход блока управления подключен к управляющему входу испытуемого регенератора, первый вход соединен с выходом блока синхро низации, с вторым входом счетчика и через анализатор подключен к блоку отображения, второй вход соединен с другим выходом декодера, другим входом блока синхронизации и с первым входом детектора ошибок, второй вход которого соединен с выходом декодера а выход подключен к третьему входу счетчика, выход которого подключен к другому входу анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1986 |

|

SU1385303A1 |

| Устройство для измерения коэффициента ошибок в цифровых системах передачи аналоговой информации | 1981 |

|

SU1020998A1 |

| Устройство для определения достоверности передачи двоичной информации | 1988 |

|

SU1670794A1 |

| Устройство для телеконтроля регенераторов | 1982 |

|

SU1140254A1 |

| Приемопередающее устройство данных | 1988 |

|

SU1628215A1 |

| УСТРОЙСТВО ТЕЛЕКОНТРОЛЯ ДЛЯ ЛИНИЙ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2119251C1 |

| Широкополосное приемопередающее устройство | 2016 |

|

RU2628328C1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Устройство для настройки и контроля параметров регенератора цифровых систем связи | 1982 |

|

SU1042195A1 |

Изобретение относится к электросвязи. Цель изобретения - повьшение точности испытания. Устр-во содержит кодер 2, искусственную линию 4, г-р . 5, декодер 7. детектор 8 ошибок, блок 9 управления, блок 10 синхронизации, счетчик П, блок 13 отображения , испытуемый регенератор 1 . Вновь : введены коммутатор 3, эл-т 6 задерж- K1V, анализатор 12. Блок 9 представляет собой параллельное соединение трех счетчиков (С импульсов, на выходах к-рых включены триггеры, являют щиеся формирователями временных интервалов . 1-и С формирует импульс длительностью, равной испытательной последовательности, 2-й С формирует импульс, длительность к-рого равна времени сеанса измерений, 3-й С формирует последовательность импульсов определяющих кол-во синхронных и асинхронных регенераторов в модулируемом тракте. 1 ил. (Л оо о ел оо 00

| Цифровые системы связи: Перев, с польск./Под ред | |||

| В.Д.Романова | |||

| М.: Связь, 1979 | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-13—Подача